Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных вычислительных системах для организации обмена информацией между процессорами, в состав которых входит буферная память, каналами ввода-вывода, модулями оперативной памяти.

Цель изобретения - повьшение пропускной способности устройства..

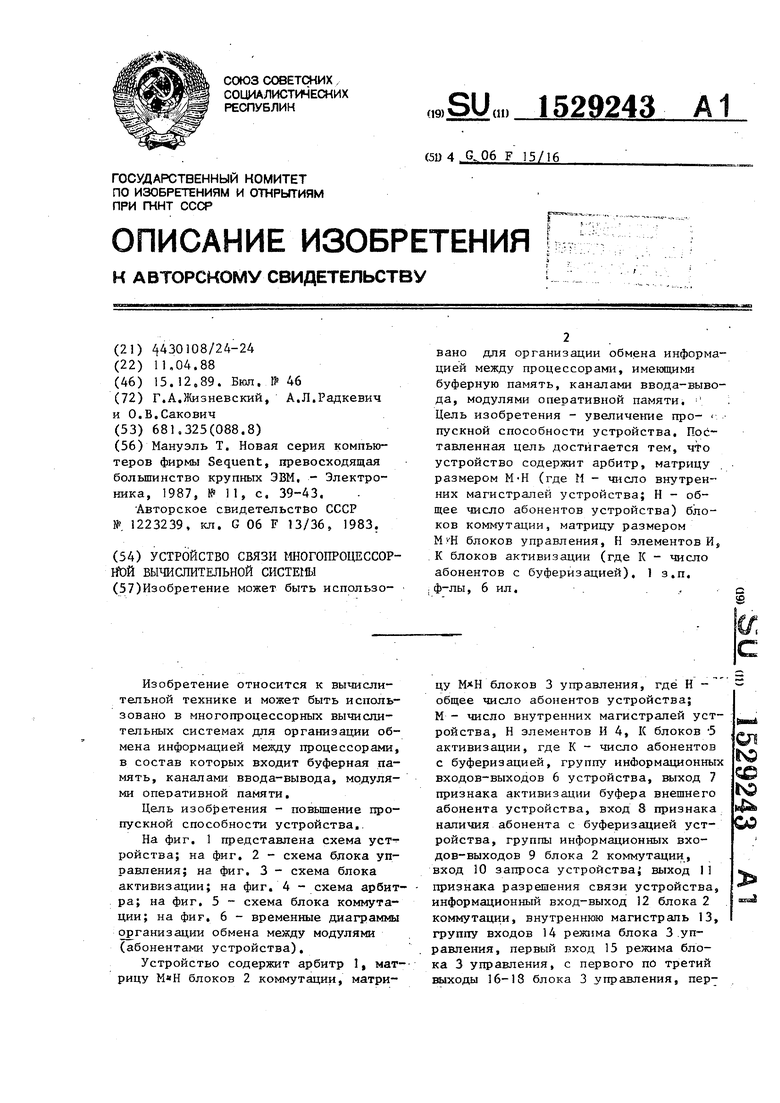

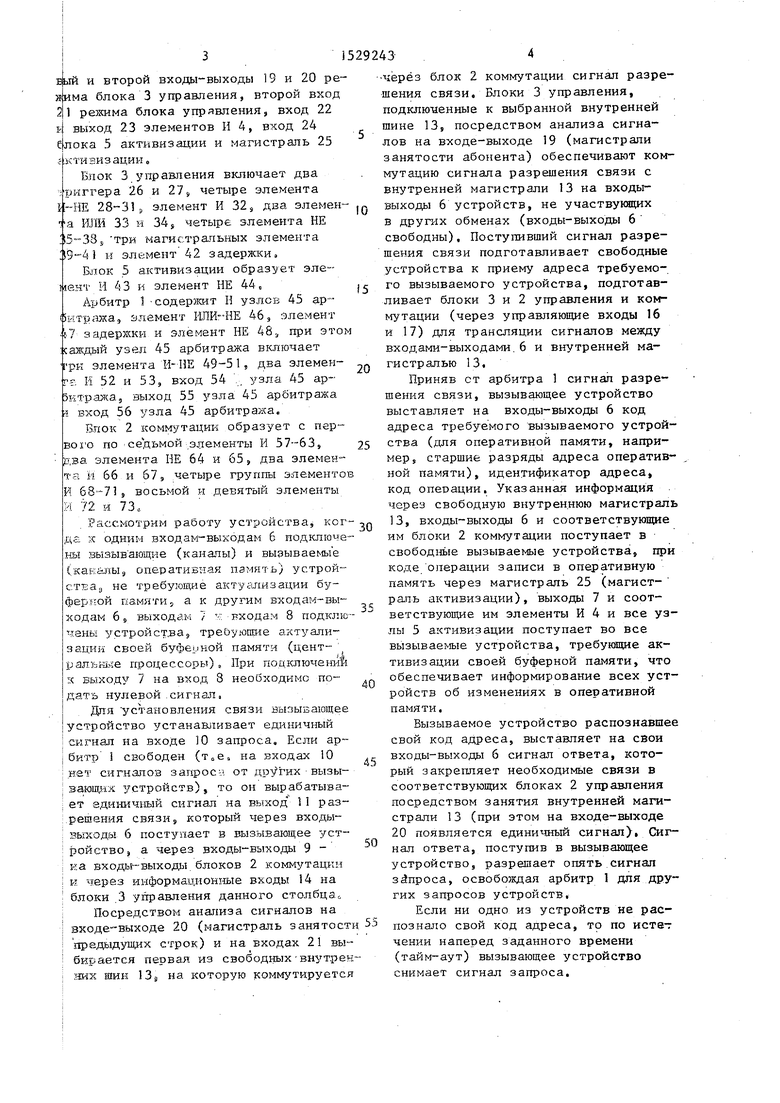

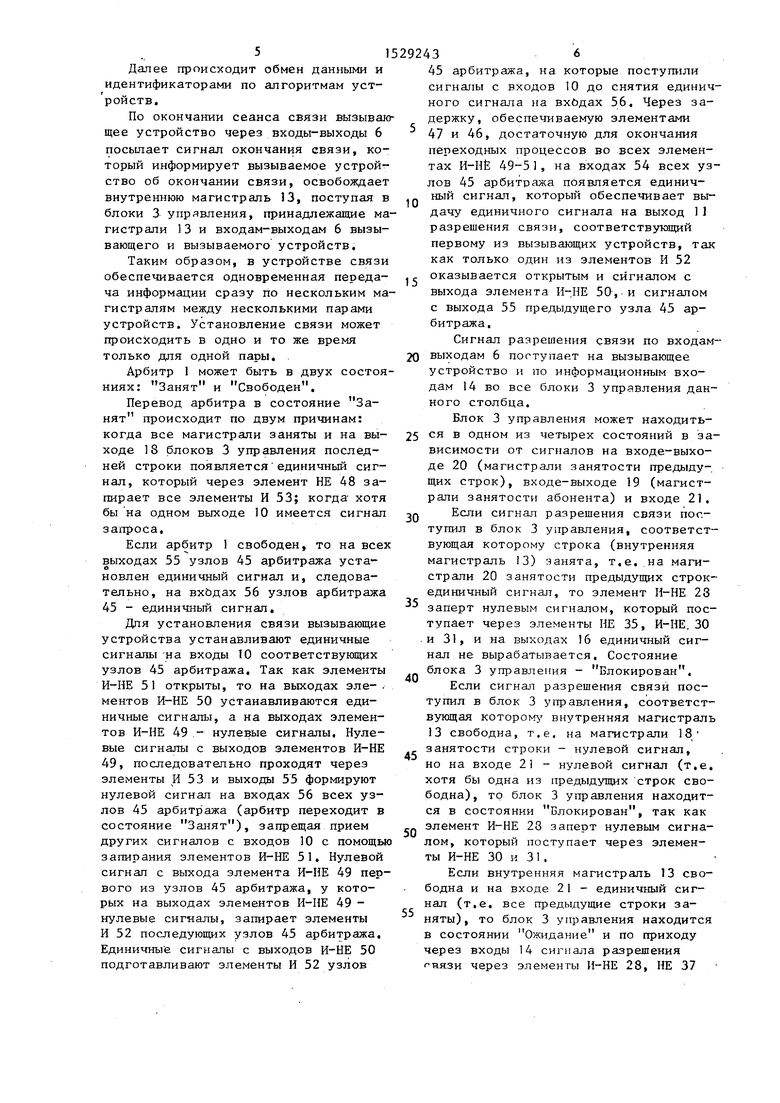

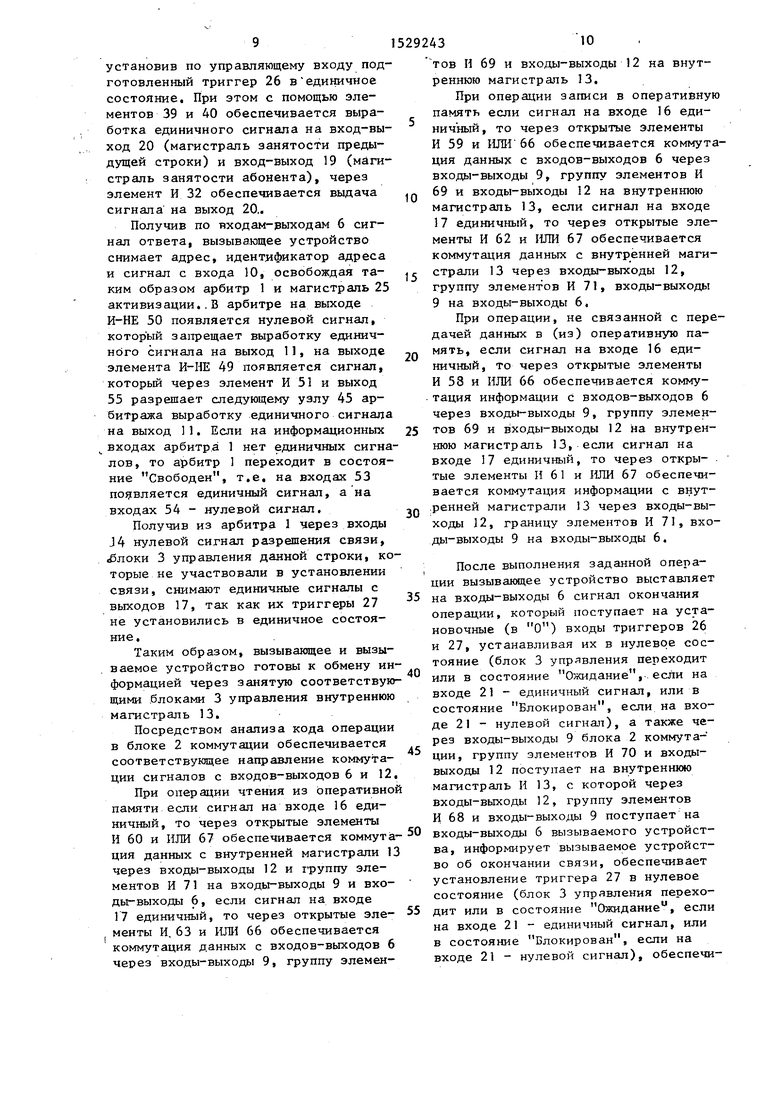

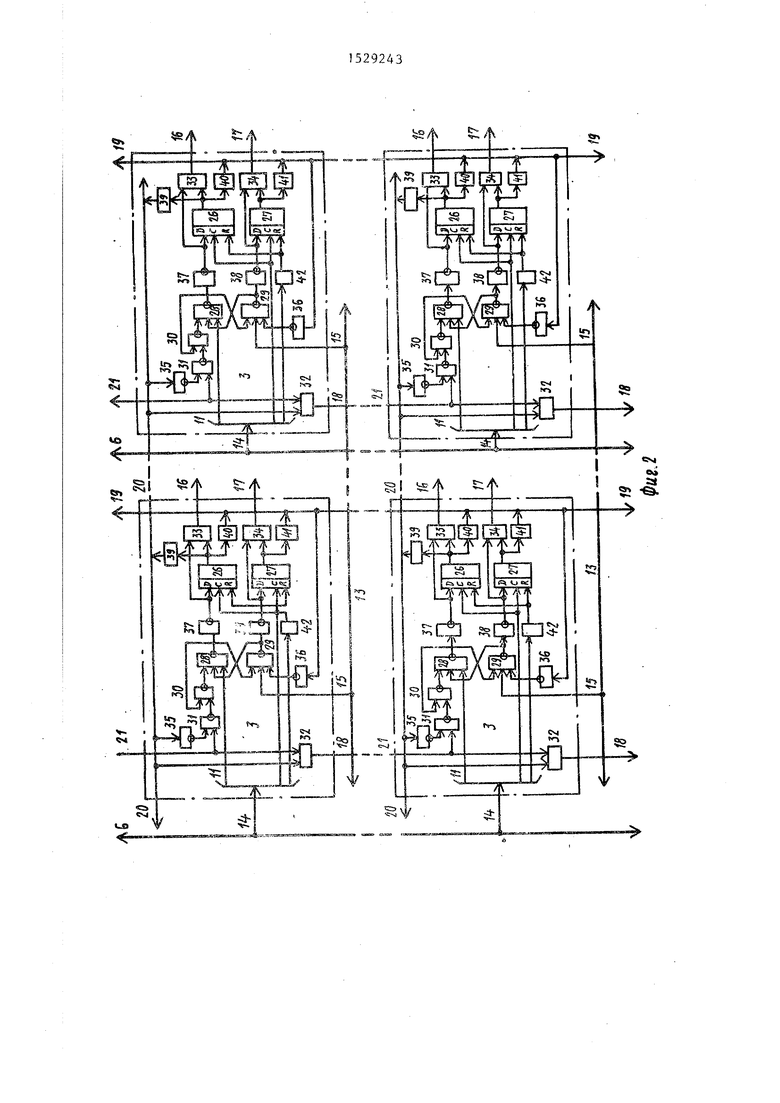

На фиг. 1 представлена схема уст- ройства; на фиг. 2 - схема блока управления; на фиг. 3 - схема блока активизации; на фиг. 4 - схема арбитра; на фиг. 5 - схема блока коммутации; на фиг, 6 - временные диаграммы организации обмена между модулями (абонентами устройства).

Устройство содержит арбитр 1, матрицу МвН блоков 2 коммутации, матрицу блоков 3 управления, где Н - общее число абонентов устройства; М - число внутренних магистралей устройства, Н элементов И 4, К блоков 5 активизации, где К - число абонентов с буферизацией, группу информационных входов-выходов 6 устройства, выход 7 признака активизации буфера внешнего абонента устройства, вход 8 признака наличия абонента с буферизацией устройства, группы информационных входов-выходов 9 блока 2 коммутации, вход 10 запроса устройства; выход 11 признака разрешения связи устройства, информационный вход-выход 12 блока 2 коммутации, внутреннюю магистрапь 13, группу входов 14 режима блока 3 .управления, первый вход 15 режима блока 3 управления, с первого по третий выходы 16-18 блока 3 управления, перО1

IsD

и второй входы-выходы 19 и 20 ре- )в1има блока 3 управления, второй вход 211 реясима блока упрявления, вход 22 к| выход 23 элементов Н 4, вход 24 е|лока 5 активизации и магистраль 25 летивизации.

Блок 3 управления включает два триггера 26 и 27j четыре элемента К-НЕ 28-31э элемент И 32, два элемен

а ИЛИ 33 и 34J четыре элемента НЕ три магистральных элемента (9-41 и элемент 42 задержки.

Блок 5 активизации образует эле- tieHT И 43 и элемент НЕ 44,

Арбитр 1 -содерзшт Н узлов 45 ар 5итр;аха, элемент 1 ШИ-НЕ 46, элемент Т задержки и элемент НЕ 48з при этом саждь1Й узел 45 арбитража включает рк элемента И-НЕ 49-51, два элемен- . И 52 и 53, вход 54 ., узла 45 ар- эктрая а, выход 55 узла 45 арбитража вход 56 узла 45 арбитража.

Блок 2 коммутации образует с пер- Boi o по : седьмой элементы И 57--63, два элемента НЕ 64 и 65, два элемента И 66 и 675 четыре группы элементо 1. 68-71, восьмой и девятый элементы А 72 и 73.

Рассмотрим работу устройства ког да ;:с одним входам-выходам 6 подключе ны вызыв шощие (канапы) и вызываемые (K;aB:aj)bis оперативная память) устрой- ггзаз не требующие актубшизадии буферной ггамяти, а к другим входам-выходам 6s выходам 7 :: Бходам 8 подключены устройст,ва5 треОуюш е актуализации своей буфеукой памяти (цент- ральш ш процессоры) г При подключени ;х выходу 7 на вход 3 необходимо подать нулевой .сигнал,

I Для установления связи вызывающее I устройство устанавливает единичный i сигнал на входе 10 запроса. Если ар- iбктр 1 свободен (т„ео на входах 10 ; нет сигналов запрос-л от дру г их вызы- i зающ-их устройств), то он вырабатыва- I ет адиш1чный сигнал на выход 1 раз- :,решения связи, который через входы- выходы 6 поступает в вызывающее уст- 1зойство, а через входы-выходь 9 - ; на входь --выходы блоков 2 коммутации : и через информационные входы 14 на : блоки 3 управления данного столбца,, ; Посредством анализа сигналов на I входе-выходе 20 (магистраль занятост предыдущих строк) и на входах 21 вы- бирается первая из свободных-внутрен ; НИХ ШИН 13s на которую коммутируется

10

15

20

25

-,. 53--

292434

-через блок 2 коммутации сигнал разрешения связи. Блоки 3 управления, подклю-иенные к выбранной внутренней шине 139 посредством анализа сигналов на входе-выходе 19 (магистрали занятости абонента) обеспечивают коммутацию сигнала разрешения связи с внутренней магистрали 13 на входы- выходы 6 устройств, не участвукяцих в других обменах (входы-выходы 6 свободны). Поступивший сигнал разрешения связи подготавливает свободные устройства к приему адреса требуемого вызываемого устройства, подготавливает блоки 3 и 2 управления и коммутации (через управляющие входы 16 и 17) для трансляции сигналов между входами-выходами. 6 и внутренней магистралью 13,

Приняв от арбитра 1 сигнал разрешения связи, вызывающее устройство выставляет на входы-выходы 6 код адреса требуемого вызываемого устройства (для оперативной памяти, например $ старшие разряды адреса оперативной памяти), идентификатор адреса, код операции. Указанная информация через свободную внутреннюю магистраль 13, входы-выходы 6 и соответствующие им блоки 2 коммутации поступает в свободнь1е вызываемые устройства, при коде операции записи в оперативную память через магистраль 25 (магист- рапь активизации), выходы 7 и соответствующие им элементы И 4 и все узлы 5 активизации поступает во все вызываемые устройства, требующие активизации своей буферной памяти, что обеспечивает информирование всех устройств об изменениях в оперативной памяти.

Вызываемое устройство распознавшее свой код адреса, выставляет на свои входы-выходы 6 сигнал ответа, который закрепляет необходимые связи в соответствующих блоках 2 управления посредством занятия внутренней магистрали 13 (при этом на входе-выходе 20 появляется едини шый сигнал). Сигнал ответа, поступив в вызывающее устройство, разрешает опять сигнал запроса, освобозкдая арбитр 1 для других запросов устройств.

Если ни одно из устройств не распознало свой код адреса, то по истечении наперед заданного времени (тайм-аут) вызывающее устройство снимает сигнал запроса.

35

40

45

50

Далее происходит обмен данными и идентификаторами по алгоритмам уст- ройств.

По окончании сеанса связи вызывающее устройство через входы-выходы 6 посылает сигнал окончания связи, который информирует вызываемое устройство об окончании связи, освобождает внутреннюю магистраль 13, поступая в блоки 3 упрявления, принадлежащие магистрали 13 и входам-выходам 6 вызывающего и вызываемого устройств.

Таким образом, в устройстве связи обеспечивается одновременная передача информации сразу по нескольким магистралям между несколькими парами устройств. Установление связи может происходить в одно и то же время только для одной пары.

Арбитр 1 может быть в двух состояниях: Занят и Свободен.

Перевод арбитра в состояние Занят происходит по двум причинам: когда все магистрали заняты и на выходе 18 блоков 3 управления последней строки появляется единичный сигнал, который через элемент НЕ 48 запирает все элементы И 53; когда хотя бы на одном выходе 10 имеется сигнал запроса.

Если арбитр 1 свободен, то на всех выходах 55 узлов 45 арбитража устаО

новлен единичный сигнал и, следовательно, на вхйдах 56 узлов арбитража 45 - единичный сигнал.

Для установления связи вызывающие устройства устанавливают единичные сигналы -на входы ТО соответствующих узлов 45 арбитража. Так как элементы И-НЕ 51 открыты, то на выходах эле- ментов И-НЕ 50 устанавливаются единичные сигналы, а на выходах элементов И-НЕ 49 - нулевые сигналы. Нулевые сигналы с выходов элементов И-НЕ 49, последовательно проходят через элементы И 53 и выходы 55 формируют нулевой сигнал на входах 56 всех узлов 45 арбитража (арбитр переходит в состояние Занят), запрещая прием других сигналов с входов 10 с помощью запирания элементов И-НЕ 51, Нулевой сигнал с выхода элемента И-НЕ 49 первого из узлов 45 арбитража, у которых на выходах элементов И-НЕ 49 - нулевые сигналы, запирает элементы И 52 последующих узлов 45 арбитража. Единичные сигналы с выходов И-НЕ 50 подготавливают элементы И 52 узлов

0

5

0

5

0

5

0

5

0

5

45 арбитража, на которые поступили сигналы с входов 10 до снятия единичного сигнала на вхйдах 56, Через задержку, обеспечиваемую элементами 47 и 46, достаточную для окончания переходных процессов во всех элементах И-НЁ 49-51, на входах 54 всех узлов 45 арбитража появляется единичный сигнал, который обеспечивает выдачу единичного сигнала на выход 11 разрешения связи, соответствующий первому из вызывающих устройств, так как только один из элементов И 52 оказывается открытым и сигналом с выхода элемента И-НЕ 50, и сигналом с выхода 55 предыдущего узла 45 арбитража.

Сигнал разрешения связи по входам- выходам 6 поступает на вызывающее устройство и по информационным входам 14 во все блоки 3 управления данного столбца.

Блок 3 управления может находиться в одном из четырех состояний в зависимости от сигналов на входе-выходе 20 (магистрали занятости предыдущих строк), входе-выходе 19 (магистрали занятости абонента) и входе 21,

Если сигнал разрешения связи поступил в блок 3 управления, соответствующая которому строка (внутренняя магистраль 13) занята, т,е,,на магистрали 20 занятости предыдущих строк- единичный сигнал, то элемент И-НЕ 28 заперт нулевым сигналом, который поступает через элементы НЕ 35, И-НЕ. 30 и 31, и на выходах 16 единичный сигнал не вырабатывается. Состояние блока 3 управления - Блокирован,

Если сигнал разрешения связи поступил в блок 3 управления, соответствующая которомз внутренняя магистраль 13 свободна, т.е. на магистрали 18 занятости строки - нулевой сигнал, но на входе 21 - нулевой сигнал (т,е. хотя бы одна из предыдущих строк свободна), то блок 3 управления находится в состоянии Блокирован, так как элемент И-НЕ 28 заперт нулевым сигналом, который поступает через элементы И-НЕ 30 и 31.

Если внутренняя магистраль 13 свободна и на входе 21 - единичный сигнал (т,е, все предыдущие строки заняты), то блок 3 управления находится в состоянии Ожидание и по приходу через входы 14 сигнала разрешения г-в.язи через элементы И-НЕ 28, НЕ 37

и ИЛИ 33 вырабатывает на выход 16 единичный сигнал (блок 3 управления переходит в состояние Вызывающий), При этом элемент Н-НЕ 29 запирается нулевым сигналом с выхода элемент;а И-НЕ 28, подготавливает триггер 26, на информационном входе которого - единичный сигнал. Таким образом -в столбце, соответствующем вызывающему устройствуJ в состоянии Вызывающий оказывается один блок 3 управления, соответствующий первой свободной строке s а остальные - находятся в состоянии Блокирован,

Получив единичный сигнал на вход 6j блок 2 коммутации посредством элемента И 72 обеспечивает цию сигнала разрешения связи .с вхо10

15

кадии адреса запирает элементы И 58- 60, открывает элемент И 57, группу элементов И 69, через которую адрес вызываемого устройства, идентификатор адреса и код операции коммутируются через входы-выходы 12 на внутреннюю магистраль 13,

Через входы 22 адрес, идентификатор адреса, сигнал разрешения связи и сигнал операции записи поступают на входы элементов Н 4, которые обеспечивают передачу адреса и идентификатора адреса на магистраль 25 активизации через выход 23. Если для устройств необходима активизация буферной памяти, то устройства постоянно поддер кивают на входах 8 нулевой сигнал, который через элемент НЕ 44

дом 9 на входы-выходы 12, Распростра- д открывает группу элементов И 43, конкясь по внутренней магистрали 13, сигнал разрешения связи поступает через входы 15 во все блоки 3 управления данной строки. Блоки 3 управления 3, которые находятся в состоянии Ожидание (т,е, элементы Н-НЕ 29 открыты как выходом элемента И-ПЕ 28s так и выходом элемента НЕ 36), обеспечивают выработку посредством элементов И-НЕ 29, НЕ 38 и HJQi 34 единичных сигналов на выход 17 (блоки 3 управления переходят в состояние Вызываемый) и подготавливают триггер 27, так как на информационных входах - еди ни чный си г и ал,

Если вызываемое угтвойство занято, т.е..на соответствующем входе-выходе 19 (магистрали занятости абонента) - единичный сигнал, то блок 3 утфавле ния находятся в состоянии Блокирован посредством нулевого сигнала с выхода элемента НЕ 36.

Таким образома в первой свободной строке блок 3 управления в состоянии

25

30

35

40

торая обеспечивает коммутацию адреса и .кода адреса на выходы 7, Адрес изменяемой информации, таким образом, становится доступным всем устройствам на Время установления связи,

В блоках 2 коммутации, соответствующие которым блоки 3 управления находгтся в состоянии Вызываемый, сигнал идентификатора адреса с внутренней магистрали 13 через входы-выходы 12 запирает элемент И 61-63, открывает элемент Н 73 и группу элементов И 71, через которую адрес вызываемого устройства, идентификатор адреса и код операции коммутируются на входы-выходы 6 через входы-выходы 9 блоков 2 коммутации.

Вызываемое устройство, с которым устанавливает связь вызывающее,- в ответ на свой распознанный адрес выставляет на входы-выходы 6 сигнал ответа, который через входы 14 поступает на входы триггеров 27, а через входы-выходы 9 - на группу эле Вызывающий вырабатывает в свой блок .г ментов И 70, При этом подготовленный

2 кoм Iyтaции единичзый сигнал на вход ,1&5 3. все остальные блоки 3 управления данной строки, находящиеся в состоянии Вызываемый 5 - единичный сигнал на вход 17 своих блоков 2 коммутации ,

Вызывающее устройство, получив из арбитра 1 сигнал разрешения связи, выставляет на щины адрес вызываемого устройства, сопровождает его идентификатором адреса и операцией, которые- -f-iepes входы-выходы 9 поступают в блок 2 коммутации и через входы 22 на входы элемента И 4 Сигнал идентифи50

55

триггер 27 устанавливается в единичное состояние, сигнал ответа с входов-выходов 9 через границу элементов И 70 коммутируется через входы- выходы 12 на внутреннюю магистраль 13 Блок 2 коммутации, блок 4 управления которого находится в состоянии Вызывающий 5 через открытую группу элементов 68 коммутирует сигнал ответа с внутренней магистрали 13 на входы-выходы 6 через входы-выходы 9, а через входы 14 сигнал ответа закрепляет выработку единичного сигнала на выход 16 через элемент 1ШИ 33,

5

кадии адреса запирает элементы И 58- 60, открывает элемент И 57, группу элементов И 69, через которую адрес вызываемого устройства, идентификатор адреса и код операции коммутируются через входы-выходы 12 на внутреннюю магистраль 13,

Через входы 22 адрес, идентификатор адреса, сигнал разрешения связи и сигнал операции записи поступают на входы элементов Н 4, которые обеспечивают передачу адреса и идентификатора адреса на магистраль 25 активизации через выход 23. Если для устройств необходима активизация буферной памяти, то устройства постоянно поддер кивают на входах 8 нулевой сигнал, который через элемент НЕ 44

открывает группу элементов И 43, ко

торая обеспечивает коммутацию адреса и .кода адреса на выходы 7, Адрес изменяемой информации, таким образом, становится доступным всем устройствам на Время установления связи,

В блоках 2 коммутации, соответствующие которым блоки 3 управления находгтся в состоянии Вызываемый, сигнал идентификатора адреса с внутренней магистрали 13 через входы-выходы 12 запирает элемент И 61-63, открывает элемент Н 73 и группу элементов И 71, через которую адрес вызываемого устройства, идентификатор адреса и код операции коммутируются на входы-выходы 6 через входы-выходы 9 блоков 2 коммутации.

Вызываемое устройство, с которым устанавливает связь вызывающее,- в ответ на свой распознанный адрес выставляет на входы-выходы 6 сигнал ответа, который через входы 14 поступает на входы триггеров 27, а через входы-выходы 9 - на группу эле

триггер 27 устанавливается в единичное состояние, сигнал ответа с входов-выходов 9 через границу элементов И 70 коммутируется через входы- выходы 12 на внутреннюю магистраль 13, Блок 2 коммутации, блок 4 управления которого находится в состоянии Вызывающий 5 через открытую группу элементов 68 коммутирует сигнал ответа с внутренней магистрали 13 на входы-выходы 6 через входы-выходы 9, а через входы 14 сигнал ответа закрепляет выработку единичного сигнала на выход 16 через элемент 1ШИ 33,

10

15

20

25

установив по управляющему входу подготовленный триггер 26 в единичное состояние. При этом с помощью элементов 39 и 40 обеспечивается выработка единичного сигнала на вход-выход 20 (магистраль занятости предыдущей строки) и вход-выход 19 (магистраль занятости абонента), через элемент И 32 обеспечивается выдача сигнала на выход 20,.

Получив по пходам-рыходам б сигнал ответа, вызывающее устройство снимает адрес, идентификатор адреса и сигнал с входа 10, освобождая таким образом арбитр 1 и магистраль 25 активизации..В арбитре на выходе И-НЕ 50 появляется нулевой сигнал, который запрещает выработку единичного сигнала на выход 11, на выходе элемента И-НЕ 49 появляется сигнал, который через элемент И 51 и выход 55 разрешает следующему узлу 45 арбитража выработку единичного сигнала на выход П. Если на информационных входах арбитр.а 1 нет единичных сигналов, то арбитр 1 переходит в состояние Свободен, т.е. на входах 53 появляется единичный сигнал, а на входах 54 - нулевой сигнал.

Получив из арбитра 1 через входы J4 нулевой сигнал разрешения связи, блоки 3 управления данной строки которые не участвовали в установлении связи, снимают единичные сигналы с выходов 17, так как их триггеры 27 не установились в единичное состояние.

Таким образом, вызывающее и вызываемое устройство готовы к обмену информацией через занятую соответствующими блоками 3 управления внутреннюю магистраль 13.

Посредством анализа кода операции в блоке 2 коммутации обеспечивается соответствующее направление коммутации сигналов с входов-выходов 6 и 12.

При операции чтения из оперативной памяти если сигнал на входе 16 единичный, то через открытые элементы И 60 и ИЛИ 67 обеспечивается коммута- ция данных с внутренней магистрали 13 через входы-выходы 12 и тфуппу элементов И 7 на входы-выходы 9 и вхо- ды-выходь1 6, если сигнал на входе 17 единичный, то через открытые элементы И.63 и ИЛИ 66 обеспечивается коммутация данных с входов-выходов 6 через входы-выходы 9, группу элемен30

35

40

45

55

10

15

20

25

29243 10

тов и 69 и входы-выходы 12 на внутреннюю магистраль 13.

При операции записи в оперативную память если сигнал на входе 16 еди- нич ный, то через открытые элементы И 59 и lUBi 66 обеспечивается коммутация данных с входов-выходов 6 через входы-выходы 9, группу элементов И 69 и входы-выходы 12 на внутреннюю магистраль 13, если сигнал на входе 17 единичный, то через открытые элементы И 62 и 1ШИ 67 обеспечивается коммутация данных с внутренней магистрали 13 через входы-выходы 12, группу элементов И 71, входы-выходы 9 на входы-выходы 6,

При операции, не связанной с передачей данных в (из) оперативную память, если сигнал на входе 16 единичный, то через открытые элементы И 58 и ИЛИ 66 обеспечивается коммутация информации с входов-выходов 6 через входа.1-выходы 9, группу элементов 69 и входы-выходы 12 на внутреннюю магистраль 13, если сигнал на входе 17 единичный, то через откры- тые элементы И 61 и ИЛИ 67 обеспечивается коммутация информации с внут- .ренней магистрали 13 через входы-выходы 12, границу элементов И 71, входы-выходы 9 на входы-выходы 6.

30

После выполнения заданной операции вызывающее устройство выставляет на входы-выходы 6 сигнал окончания операции, который поступает на установочные (в О) входы триггеров 26 и 27, устанавливая их в нулевое состояние (блок 3 упрявления переходит или в состояние Ожидание,.если на входе 21 - единичный сигнал, или в состояние Блокирован, если на входе 21 - нулевой сигнал), а также через входы-выходы 9 блока 2 коммута- ции, группу элементов И 70 и входы- выходы 12 поступает на внутреннюю магистраль И 13, с которой через входы-выходы 12, группу элементов И. 68 и входы-выходы 9 поступает на входы-выходы 6 вызываемого устройства, информирует вызываемое устройство об окончании связи, обеспечивает установление триггера 27 в нулевое состояние (блок 3 управления перехо- дит или в состояние Ожидание, если на входе 21 - единичный сигнал, или в состояние Блокирован, если на входе 21 - нулевой сигнал), обеспечифая освобождение столбца через эле- фент 41,

; Таким образом, освобождаются оба Устройства и внутренняя магистраль рЗ, причем освободжение может проис- содить сразу на нескольких магистра- 1ЯХ, Обмен информацией и окончание :вязи могут происходить сразу через ecкoлькo внутренних магистралей и 1ежду несколькими парами устройств. Установление связи возможно толбко между одной парой устройства. Одновременно с последовательностью установления связи производится и переда ча информации для активизации данных в буферной памяти устройств многопроцессорной вычислительной системы.

Формула изобретения

I. Устройство связи многопроцессорной вычислительной системы, содержащее арбитр и матрицу размером M«fH блоков коммутации., где И - общее чис ло абонентов устройства, 11 - число внутренних магистралей устройства, причем р-й вход запроса устройства, где р 1,...,Н и подключен к р-му информационному входу арбитра, р-й выход которого подключен к р-му выходу признака разрешения связи устройства, информационные входы-выходы группы блоков коммутации р-го столбца матрицы блоков коммутации объединены и подключены соответственно к информационным входам- зых о дам р-й группы устройства, информационный вход-выход первого блока коммутации е-й строки матрицы блоков коммутации где С 1,0.. ,М , подключен к информационным входам-выходам блоков коммутации С-й строки с второго по Н-й столбцов матрицы блоков коммутации, отличающее с. Я тем, что, с целью увеличения пропускной способности устройства, оно содержит матрицу размером Н«Н блоков управления, Н элементов И и К блоков активизации где К - число абонентов с буферизацией, при этом информационные входы- выходы р-й группы устройства подключены к входам режима группы блоков управления р-го столбца матрицы бло-. ков управления и к входам р-го элемента И, а-й вход признака наличия абонента с буферизацией устройства,

где а . 1К, подключен к первому

входу а-го блока активизации, выход

j5

10

20

25

30

35

40

45

50

55

которого подключен к а-му выходу признака активизаЬ;ии буфера абонента устройства, информационньш вход-выход Н-го блока коммутации С-й строки матрицы блоков коммутации подключен к первым входам режима блоков управления С-й строки матриць блоков управления, первый вход-выход режима блока управления С-й строки первого столбца матри1дь1 блоков управления подключен к первым входам-выходам режима блоков управления С-й строки столбцов с второго по , второй вход-выход режима блока управления первой строки р-го столбца матрицы блоков управления подключен к вторым входам-выходам режима блоков управления с второй на М-ю строки р-го столбца матрицы блоков управления, р-й вход режима устройства подключен к второму входу режима блока управлений первой строки р-го столбца матрицы блоков управления, первый выход блока управления Ь-й строки р-го столбца матрицы блоков управления, где b 1,.,.,М-1, подключен к второму входу режима блока управления (Ъ+1)-.строки р-го столбца матрицы блоков .управления, второй и третий выходы блока управления С-й строки р-го столбца матрицы блоков управления подключен к первому и .второму управляющим входам блока коммутации С-й строки р-го столбца матрицы блоков коммутации, первый выход блока управления первого столбца М-й строки матрицы блоков управления подключен к входу блокировки арбитра,- ходы элементов И с первого по Н-й объединены с помощью MOHTAJIfflOFO 11ПИ и подключены к вторым входам блоков активизации.

2. Устройство по п. 1, о т л и - чающееся тем, что блок управления содержит два триггера, четыре элемента НЕ, четыре элемента И-НЕ, два элемента РШН, три магистральных элемента, элемент И и элемент задержки причем первый вход- выход режима блока управления подключен к первому входу элемента И, к входу первого элемента НЕ и к выходу первого магистрального элемента, второй вход-выход режима блока управления подключен к входу второго эле- . мента НЕ и к выходам второго и третьего магистральных элементов, первый вход режима блока управления

подключен к первому входу первого элемента И-НЕ, выход которого подключен к входу третьего элемента НЕ и к первому входу второго элемента И-НЕ, выход которого подключен к второму входу первого элемента Н-НЕ, к входу четвертого элемента НЕ и к первому входу третьего элемента И-НЕ выход которого подключен к второму входу второго элемента И-НЕ, второй вход режима блока управления подключен к первому входу четвертого элемента И-НЕ и к второму входу элемента И, выход которого подключен к первому выходу блока управления, первый вход режима группы которого подключен к третьему входу второго элемен- ; та И-НЕ, второй вход режима группы блока управления подключен к синхро- входам первого и второго триггеров, третий вход режима группы блока управления подключен к входу элемента задержки, выход которого подключен к входам установки в О первого и вто- рого триггеров, выход первого элемента НЕ подключен к второму входу четвертого элемента И-НЕ, выход которого подключен к второму входу третьего

элемента И-НЕ, выход второго элемента НЕ подключен к третьему входу первого элемента И-НЕ, выход третьего элемента НЕ подключен к информационному входу первого триггера и к первому входу первого элемента ИЛИ, выход четвертого элемента НЕ подключен к информационному входу второго триггера и к первому входу второго элемента ИЛИ, выход- первого триггера, подключен к второму входу первого элемента ИЛИ и к входу третьего магистрального элемента, выход второго триггера подключен к второму входу второго элемента ИЛИ и к входам первого и второго магистральных элементов, выходы второго и первого эле-- ментов ИЛИ подключены соответственно к второму и третьему блока управления, причем каждый блок активизации содержит элемент НЕ и элемент И, первый и второй входы блока активизации подключены соответственно к входу элемента НЕ и к первому элементу И, второй вход которого подключен к выходу элемента НЕ, выход элемента И подключен к выходу блока активизации.

«V

«л

8

f7

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство связи многопроцессорной вычислительной системы | 1988 |

|

SU1501081A1 |

| Микроэлектронная вычислительная машина | 1979 |

|

SU1061606A1 |

| Устройство для сопряжения ЭВМ с абонентами | 1988 |

|

SU1640702A1 |

| Устройство для сопряжения каналов ввода-вывода с внешними устройствами | 1985 |

|

SU1277128A1 |

| Устройство для сопряжения цифровых вычислительных машин | 1991 |

|

SU1800460A1 |

| Устройство для сопряжения цифровых вычислительных машин | 1990 |

|

SU1783531A1 |

| Устройство для сопряжения цифровых вычислительных машин | 1988 |

|

SU1571603A1 |

| Устройство для обмена информацией | 1979 |

|

SU842773A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ ПОДКЛЮЧЕНИЯ АБОНЕНТОВ К ОБЩЕЙ МАГИСТРАЛИ | 1991 |

|

RU2018938C1 |

Изобретение может быть использовано для организации обмена информацией между процессорами, имеющими буферную память, каналами ввода-вывода, модулями оперативной памяти. Цель изобретения - увеличение пропускной способности устройства. Поставленная цель достигается тем, что устройство содержит арбитр, матрицу размером M.H (где M - число внутренних магистралей устройства, H - общее число абонентов устройства) блоков коммутации, матрицу размером M.H блоков управления, H элементов И, K блоков активизации (где K - число абонентов с буферизацией). 1 з.п. ф-лы, 6 ил.

25

55

Г--

I иЛL

w

Фие.д

,55

5

.Я

0t/e

/0

7/

cu.zHuf,cKOMMtjmui}o6uHHt,iLL с входа 11 не мину 13 НОЛ KOHei{ операции.

Фиг. 6

| Мануэль Т | |||

| Новая серия компьютеров фирмы Sequent, превосходящая большинство крупных ЭВМ | |||

| - Электроника, 1987, № 11, с | |||

| Машина для изготовления проволочных гвоздей | 1922 |

|

SU39A1 |

| Авторское свидетельство СССР № | |||

| Устройство для сопряжения абонентов с общей магистралью вычислительной системы | 1984 |

|

SU1223239A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-12-15—Публикация

1988-04-11—Подача