Изобретение относится к вычислительной технике и может быть использовано в многопроцессорной вычислительной системе для организации обмена информацией между процессорами, каналами ввода-вывода и модулями .оперативной памяти.

Цель изобретения - повьшениё пропускной способности устройства.

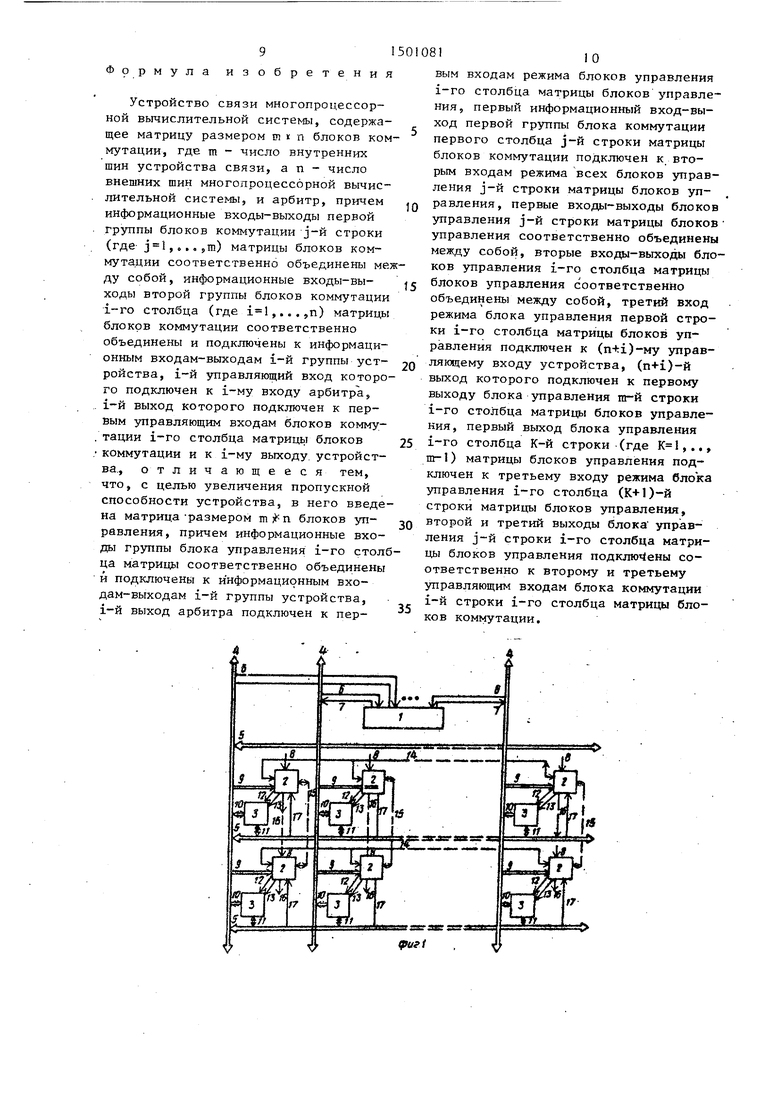

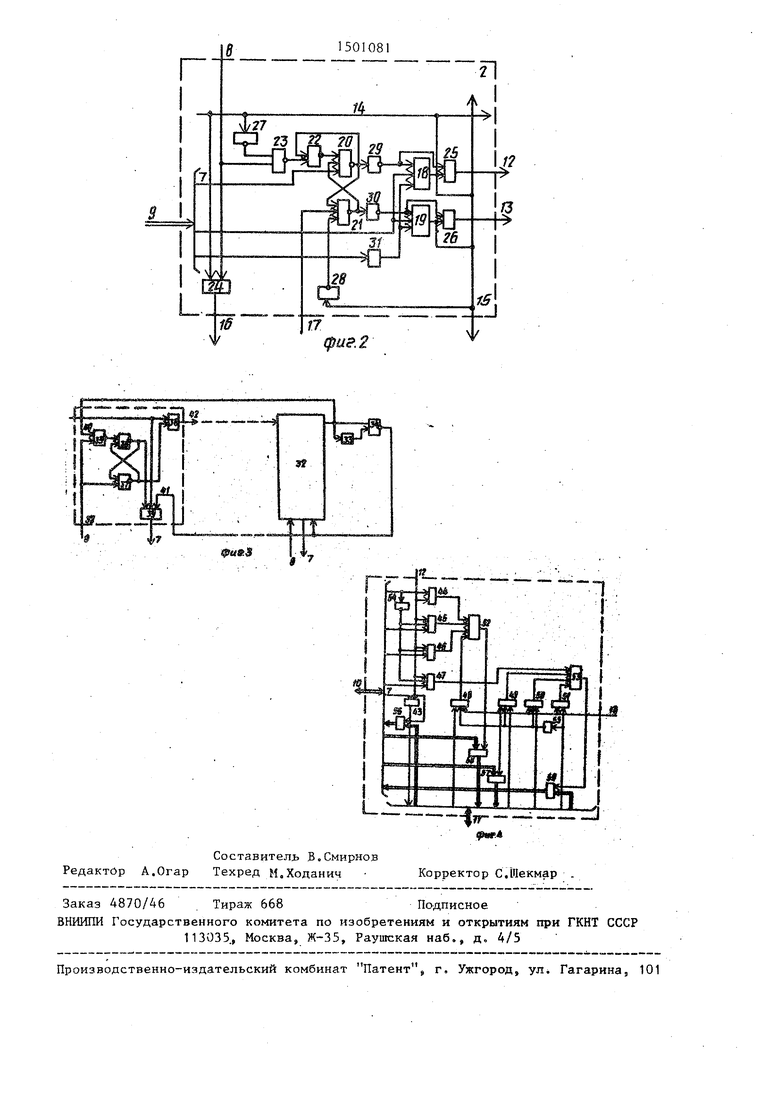

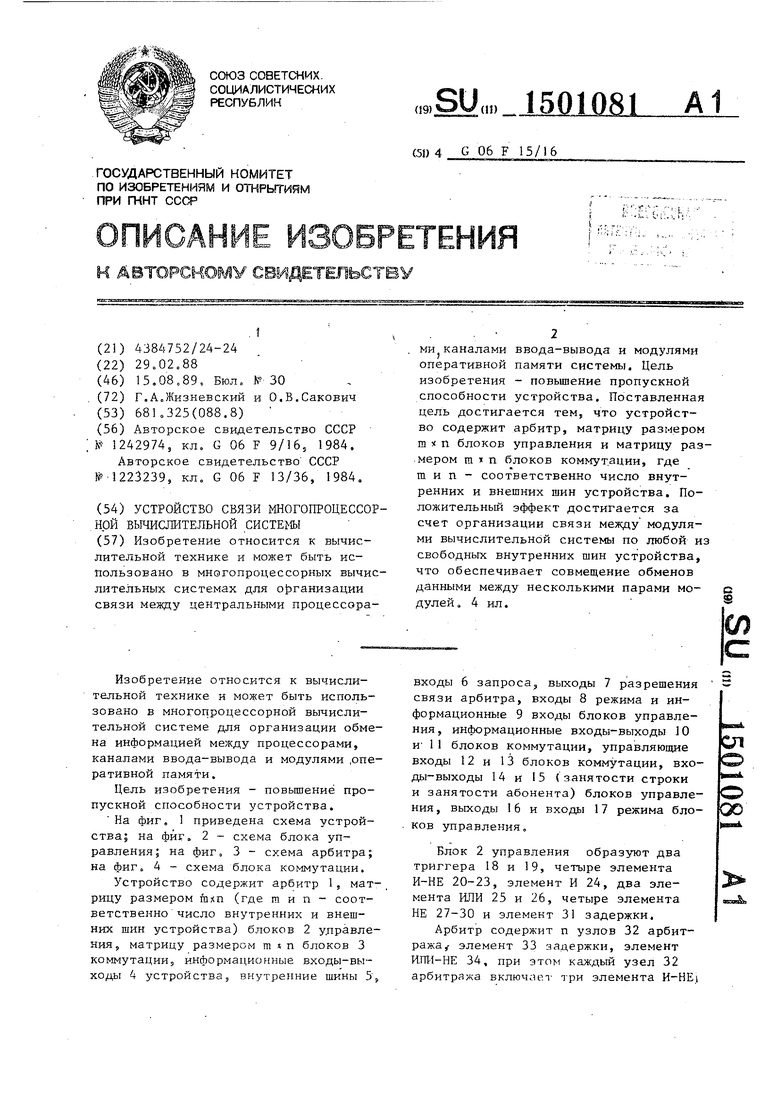

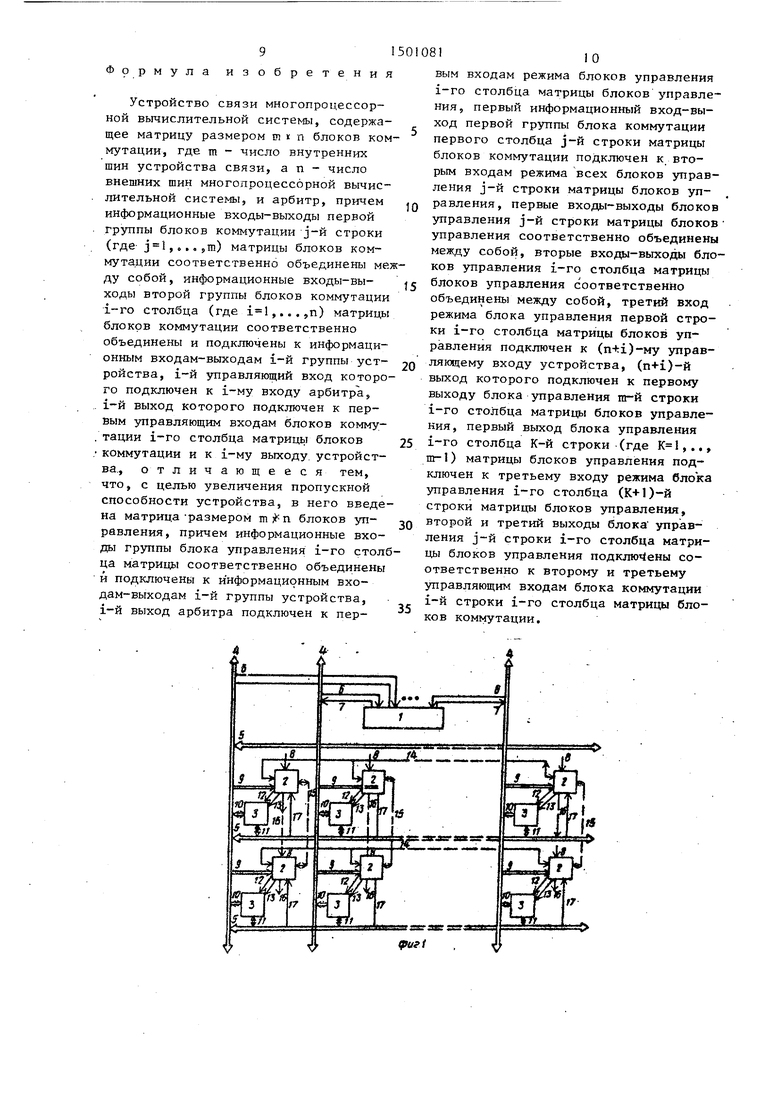

На фиг. 1 приведена схема устройства; на фиг. 2 схема блока управления; на фиг, 3 - схема арбитра; на фиг 4 - схема блока коммутации.

Устройство содержит арбитр 1, мат-. рицу размером (где тип- соответственно число внутренних и внешних шин устройства) блоков 2 управления, матрицу размером m « п блоков 3 коммутации, информационные входы-выходы 4 устройства, внутренние шины 5 j

входы 6 запроса, выходы 7 разрешения связи арбитра, входы 8 режима и информационные 9 входы блоков управления, информационные входы-выходы JO И 1 1 блоков коммутации, управляющие входы 12 и 13 блоков коммутации, входы-выходы 14 и 15 (занятости строки и занятости абонента) блоков управления , выходы I6 и входы 17 режима блоков управления.

Блок 2 управления образуют два триггера 18 и 19, четыре элемента И-НЕ 20-23, элемент И 24, два элемента ИЛИ 25 и 26, четыре элемента НЕ 27-30 и элемент 31 задержки.

Арбитр содержит п узлов 32 арбитража элемент 33 задержки, элемент ИШ-НЕ 34, при этом каждый узел 32 арбитража включает три элемента И-НЕ)

оо

3150

35-37, два элемента И 38 и 39, входы 40 и 41 и выход 42 узла 32 арбитража Блок 3 коммутации выполнен в виде одиннадцати элементов И 43-53, дру- гих элементов НЕ 54 и 55 и четырех .групп элементов И 56-59.

Рассмотрим работу устройства в случае, котда к входным шинам 4 подключены вызыван5щие устройства (цент- ральные процессоры, каналы) и вызываемые устройства (оперативная памят каналы, центральные процессоры),Для установления связи вызывающее устройство устанавливает сигнал запроса на линию 6, который поступает в арбитр 1. Если арбитр 1 свободен (на линиях 6 нет сигналов запроса от других вызывающих устройств), то он вырабатывает сигнал разрешения связи на линию 7 и посылает его в вызывающее устройство и блоки 2 управления данного столбца. Последством блоков 2 управления выбирается первая свободная внутренняя шина 5, на которую и коммутируется сигнал разрешения связи. Блоки 3, подключенные к выб- ранной внутренней шине 5, коммутируют сигнал разрешения связи на те входные шины 4, устройства которых не участвуют в других обменах (свобо ныв входные шины 4).Поступивший сигнал разрешения связи подготавливает блоки 2 и 3 для транслирования сигналов между шинами 4 и 5.

Приняв от арбитра 1 сигнал разрешения связи, вызывающее устройство выставляет на шины 4 код адреса требуемого вызываемого устройства, идентификатор Адрес и код операции, которое через свободную внутреннюю шину 5 и входные шины 4 поступают в свободные устройства.

Вызываемое устройство, распознавшее свой код адреса, посылает в шину 4 сигнал Ответ, которьй закрепляет необходимые связи в соответствующих блоках 2 управления посредством занятия внутренней шины 5.

Сигнал ответа, поступив в вызыва- ющее устройство, разрешает снять сигнал запроса, освобождая арбитр 1 для запросов других устройств.

Далее происходит обмен данными и идентификаторами по алгоритмам уст-

РОЙСТБ.

Если ни одно из имеющихся уст- .ройств не распознало свой код адреса, то по истечении определенного

интервала времени (времени ответа) вызывающее устройство снимает сигнал запроса.

По окончании сеанса вызывающее устройство через шины 4 посылает сигнал окончания связи, которьй информирует вызываемое устройство об окончании связи; освобождает внутреннюю шину 5, поступая в блоки 2 управлени принадлежащие шине 5 и шинам 4 вызывающего и вызываемого устройств участвующих в сеансе связи.

Таким образом, обеспечивается одновременная передача информации сразу по нескольким шинам,, между несколкими парами устройств. Установление связи одновременно может происходить только для одной пары..

Арбитр 1 может быть в двух состояниях: занят и свободен.

Если арбитр 1 свободен, то.на все выходах 42 узлов 32 арбитража устанолен единичньш сигнал и, следовательно, на входах 40 узла 32 арбитража - единичный сигнал. Для установления связи вызывающие устройства устанавливают единичные сигналы на входы 6 соответствующих узлов 32 арбитража. Поскольку элементы И-НЕ 35 открыты, то на выходах элементов 36 уста навливаются -единичные сигналы, а на- выходах элементов И-НЕ 37 -.нулевые сигналы. Нулевые сигналы с выходов элементов И-НЕ 37, последовательно проходя через элементы И 38 и выходы 42, формируют нулевой сигнал на входах 40 всех узлов 32 арбитража (ар- i битр 1 переходит в состояние занят), запрещая .прием других сигналов с входов 6 посредством запирания элементов И-НЕ 35. Выход элемента И-НЕ 37 первого из узлов 32 арбитража запирает элемент И 39 последующих узлов 32 арбитража.

Единичные сигналы с выходов И-НЕ 36 подготавливают элементы И 39 узлов 32 арбитража, на которые поступили сигналы с входов 6 до снятия единичного сигнала с входов 40, Через задержку, обеспечиваемую элементами. 33 задержки и элементами ИЛИ-НЕ 34 и достаточную для окончания переходных процессов во всех элементах И-НЕ 35-37, на входах 41 всех узлов 32 арбитража появляется единичньй сигнал, который обеспечивает выдачу единичного сигнала на выход 7 разрешения связи первого из вызывающих устройств, так как только один из элементов И 39 оказывается открытым и си гналом с выхода элемента И-НЕ 36 и сигналом с выхода 42 предыдущего узла 32 арбитража. Сигнал разреше- Нин связи по шинам,4 постз пает в вызывающее устройство и по информационным входам 9 во все блоки 2 управления данного столбца.

Блок 2 управления может находиться в одном из четырех состояний в зависимости от сигналов на линии 14 занятости строки, линии 15 занятости абонента и вх оде 8.

Если сигнал разрешения связи поступил в блок 2 управления и на линии i 4 занятости строки - единичный сигнал, то элемент И-НЕ 20 заперт нулевым сигналом, который поступает через элементы НЕ 27, 23 и 22, и на выходах 12 единичный сигнал не вырабатывается. Если сигнал разрешения связи поступил в блок 2 управлё- ния, соответствующая которому внутренняя шина 5 свободна (т.е. на линии занятости строки 14 - нулевой сигнал), но на входе 8 присутствует нулевой сигнал (т.е. хотя бы одна из предыдущих строк свободна), то блок 2 управления находится в состоянии Блокирован, так как элемент И-НЕ 20 заперт нулевым сигналом, который поступает через элементы И-НЕ 23 и 22.

Если внутренняя шина 5 свободна и на входе 8 - единичный сигнал (т.е. все предыдущие строки заняты),- то блок 2 управления находится в состоянии ожидания и по приходу через входы 9 сигнала разрешения связи через элементы И-НЕ 20, НЕ 29 и ИЛИ 25 на управляющий вход 12 подается единич

010816

строки. Блоки управления 2, которые находятся в состоянии ожидания (т.е. элeмeнт I И-НЕ 21 открыты), обеспечивают выработку единичных сигналов на выход 13 (блоки 2 управления пе- .реходят в состояние Вызываемьш) и подготавливают триггеры 19, так как на информационных входах триг10 геров 19 - единичный сигнал.

Если вызываемое устройство занято, т.е. на соответствующей шине 15 занятости абонента - единичный сигнал, то блок 2 управления находит15 ся в состоянии Блокирован, так как на выходе элемента НЕ 28 - нулевой сигнал .

Таким образом, в первой свободной строке блок 2 управления в состоянии

20 Вызывающий вырабатывает в свой блок 3 коммутации единичный сигнал на управляющий вход 12, а все остальные блоки 2 управления данной строки, находящиеся в состоянии Вызываемый -25 единичный сигнал на управляющий вход 13 своих блоков 3 коммутации. Вызывающее устройство, получив из арбитра 1 разрешение связи, выставляет на шины адрес вызываемого устройства, со30 провождаёт его идентификатором Адрес и кодом операции, которые через входы-выходы 10 поступают в,блок 3 коммутации. Сигнал идентификации адреса, пройдя через элемент НЕ 54,

25 запирает элементы И 47, открывает элемент И 44, который через элемент ИЛИ 52 открывает группу элементов И 58, через которую адрес вызываемого устройства, идентификатор Адрес и код операции коммутируется через входы- выходы 11 на внутреннюю шину 5.

В блоках 3 ком 1утации, соответствующие блоки 2 управления которых находятся в. состоянии Вызываемьпй,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство связи многопроцессорной вычислительной системы | 1988 |

|

SU1529243A1 |

| Устройство для сопряжения каналов ввода-вывода с внешними устройствами | 1985 |

|

SU1277128A1 |

| Устройство для сопряжения группы каналов ЭВМ с группой периферийных устройств | 1987 |

|

SU1520529A1 |

| Коммутационное устройство | 1985 |

|

SU1285486A1 |

| Устройство для сопряжения многопроцессорной вычислительной системы | 1983 |

|

SU1160423A1 |

| Устройство для сопряжения многопроцессорной вычислительной системы с внешними устройствами | 1984 |

|

SU1241245A2 |

| Устройство для сопряжения группы из М вычислительных машин с группой из К абонентов | 1986 |

|

SU1310830A1 |

| Устройство для сопряжения | 1981 |

|

SU964622A1 |

| Устройство связи для вычислительной системы | 1982 |

|

SU1062678A1 |

| Микроэлектронная вычислительная машина | 1979 |

|

SU1061606A1 |

Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных вычислительных системах для организации связи между центральными процессорами, каналами ввода-вывода и модулями оперативной памяти системы. Цель изобретения - повышение пропускной способности устройства. Поставленная цель достигается тем, что устройство содержит арбитр, матрицу размером M X N блоков управления и матрицу размером M X N блоков коммутации, где M и N - соответственно число внутренних и внешних шин устройства. Положительный эффект достигается за счет организации связи между модулями вычислительной системы по любой из свободных внутренних шин устройства, что обеспечивает совмещение обменов данными между несколькими парами модулей. 4 ил.

ньй сигнал. Таким образом, в столбце, 45 сигнал идентификатора Адрес, посту-

соответствующем вызывающему устройству в состоянии Вызывающий,. оказывается один блок 2 управления, соответствующий первой свободной строке, а остальные - в состоянии Блокирован. Единичный сигнал на входе 12 блока 3 коммутации с помощью элемента И 43 обеспечивает кoм ryтaцию сигнала разрешения связи с информацион-

ных входов-выходов 10 на информацион-55

ные входы-выходы 11. РаспространяясьВызываемое устройство, с которым

по внутренней шине 5, сигнал разре-устанавливает связь вызывающее, в отшения связи поступает через входывет на свой распознанный адрес вы17 во все блоки 2 управления данной ставляет на входную тину 4 сигнал

пая с внутренней шины 5 через входы- выходы 11, запирает элементом НЕ 55 элементы И 48-50 и открывает элемент И 51, который через элемент ИЛИ 53 gQ открывает группу элементов И 59, через которую адрес вызываемого устройства, идентификатор Адрес и код операции коммутируются на шину 4 через входы-выходы 10 блоков 3 коммута715

Ответ , который через входы 9 поступает на управляющие входы триггеров 19, В результате один из этих триггеров (блок 2 управления которого в состоянии Вызываемый) устанавливается в единичное состояние, захватив шину 15 занятости абонента. Сигнал Ответ с входов-выходов 10 через группу элементов И 57, открытую единичным сигналом с управляющего входа 13, коммутируется через входы-выходы I1на внутреннюю шину 5.

Блок 3 коммутации, соответствующий блок 2 управления которого нахо

дится в состоянии Вызываюш;ий, че- рез открытую группу, элементов И 56 коммутирует сигнал Ответ с внутренней шины 5 на входную шину 4 через входы-выходы 10,

Получив на входных шинах 4 сигнал Ответ, вызывающее устройство снимает адресу идентификатор Адрес и сигнал с входа 6,. освобождая таким образом арбитр I о

В -арбитре 1 на выходе элемента И-НЕ 3.6 появляется нулевой сигнал, который запрещает выработку единичного сигнала на выход 7 разрешения связи, на выходе элемента Й-НЕ 37 появляется, единичный сигнал, который через элемент И 38 и выход 42 разрешает следующему узлу арбитража . выработку единичного сигнала на выход 7 разрешения связи. Если на входах арбитра 1 нет единичных сигналов то арбитр 1 переходит в состояние свободен, т.е. на входах 40 появляется единичный сигнал, а на входах 41 - нулевой.

Получив из арЬитра 1 через входы 9 нулевой сигнал разрешения связи, блоки 2 управления данно строки, которые не участвовали в установлении связи, снимают единичные сигналы с выходов 13 (так как их триггеры 19 не установились в единичное состоя-. ние - не получен сигнал Ответ на управляющих входах триггерор).

Таким образом, вызывающее и вызываемое устройство готовы к обмену информацией через занятую соответствующими блоками 2 управления внутреннюю шину 5.

Посредством анализа кода операции в блоке 3 коммутации о беспечивается соответствующее направление коммутации сигналов с входной шины 4 и внутренней шины 5, .

5

0

5

При операции чтения из оперативной памяти если сигнал на входе 12 единичный, то через открытые элементы И 47 и ИЛ 53 обеспечивается коммутация данных с внутренней шины 5 через входы-выходы 11, группу элементов И 59 и входы-выходы 10 на входные шины 4; если сигнал на входе 13 еди- ничный, то через открытые элементы И 48 и ИЛИ 52 обеспечивается коммутация данных с входных шин 4 через входы-выходы ГО, группу элементов И 58 и входы-выходы 11 на внутреннюю шину 5.

При операции записи в оперативную память если сигнал на входе 12 единичный, то через открытые элементы И 46 и ИЛИ 52 обеспечивается коммутация данных с входных шин 4 через входы-выходы 10, группу элементов И 58 и входы-выходы 11 на внутреннюю шину 5; если сигнал на входе 13 еди- . ничный, то через открытые элементы И 49 и ИЛИ 53 обеспечивается коммутация данных с внутренней шины 5 чеI

рез входы-выходы 11, группу элементов И 59 и входы-выходы 10 на входные шины 4.

При выполнении операции, не связанной с передачей данных в оперативную память если сигнал на управляющем входе 12 единичньй, то-.через открытые элементы И 45 и ИЛИ 52 обеспе5 чивается коммутация информации с

входных шин 4 через входы-выходы 10, группу элементов И 58 и входы-выходы 11 на внутреннюю шину 5; если сигнал на управляющем входе 13 единичный, то через открытые элементы И 50 и ИЛИ 53 обеспечивается коммутация информации с внутренней шины 5 через входы-выходы 1I, группу элементов И 59 и входы-выходы 10 на входные ши5 ны 4..

После выполнения заданной операции вызывающее устройство выставляет на шины 4 сигнал окончания операции, который через входы 9 блока 2 управления и элемент 31 задержки поступает на установленные в О входы триггеров 18 и 19 (блок 2 управления переходит в состояние ожидания, если на управляющем входе 8 - единичньй сигнал, или в состояние Блокирован, если на входе 8 - нулевой сигнал), обеспечивая освобождение соответствующих строк и столбца.

0

0

0

Формула из

9 о б

р е т е н и я

Устройство связи многопроцессорной вычислительной системы, содержащее матрицу размером m « п блоков коммутации, где m - число внутренних шин устройства связи, an- число внешних шин многопроцессорной вычислительной системы, и арбитр, причем информационные входы-выходы первой группы блоков коммутации j-й строки (где- j l,,.,pm) матрицы блоков ком- мутадии соответственно обг единены ме ду собой, информационные входы-выходы второй группы блоков коммутации 1-го столбца (где ,...,п) матрицы блоков коммутации соответственно объединены и подключены к информационным входам-выходам i-й группы устройства, i-й управляющий вход которого подключен к i-му входу арбитра, i-й выход которого подключен к первым з равляющим входам блоков коммутации i-ro столбца матрицы блоков коммутации и к i-му выходу, устройства., отличающееся тем, что, с целью увеличения пропускной способности устройства, в него введена матрица-размером блоков управления, причем информационные входы группы блока управления i-ro столца матрицы соответственно объединены и подключены к и нформационным входам-выходам i-й группы устройства, i-и выход арбитра подключен к пер1501081

10

0

5

0

5

0

5

вым входам режима блоков управления i-ro столбца матрицы блоков управления, первый информационный вход-выход первой группы блока коммутации первого столбца j-й строки матрицы блоков коммутации подключен к вторым входам режима всех блоков управления j-й строки матрицы блоков управления, первые входы-выходы блоков управления j-й строки матрицы блоков управления соответственно объединены между собой, вторые входы-выходы блоков управления i-ro столбца матрицы блоков управления соответственно объединены между собой, третий вход режима блока управления первой строки i-ro столбца матрицы блоков управления подключен к ()-му управляющему входу устройства, (п+1)-й выход которого подключен к первому выходу блока управления п-й строки i-ro столбца матрицы блоков управления, первый выход блока управления i-ro столбца К-й строки (где ,.,, т-1) матрицы блоков управления подключен к третьему входу режима блока управления i-ro столбца (К+1)-й строки матрицы блоков управления, второй и третий выходы блока управления j-й строки i-ro столбца матрицы блоков управления подклю ены соответственно к второму и третьему управляющим входам блока коммутации i-й строки i-ro столбца матрицы блоков коммутации.

г

g)ue.2

л

1

| Устройство для сопряжения электронно-вычислительной машины с общей магистралью вычислительной системы | 1984 |

|

SU1242974A1 |

| Устройство для сопряжения абонентов с общей магистралью вычислительной системы | 1984 |

|

SU1223239A1 |

Авторы

Даты

1989-08-15—Публикация

1988-02-29—Подача