и{

СО

to

СП

оо о

Изобретение относится к вычислительной технике, в частности к сложным цифровым системам обработки информации с множеством быстродействующих устройств ввода-вьтода.

Цель изобретения - повышение производительности системы.

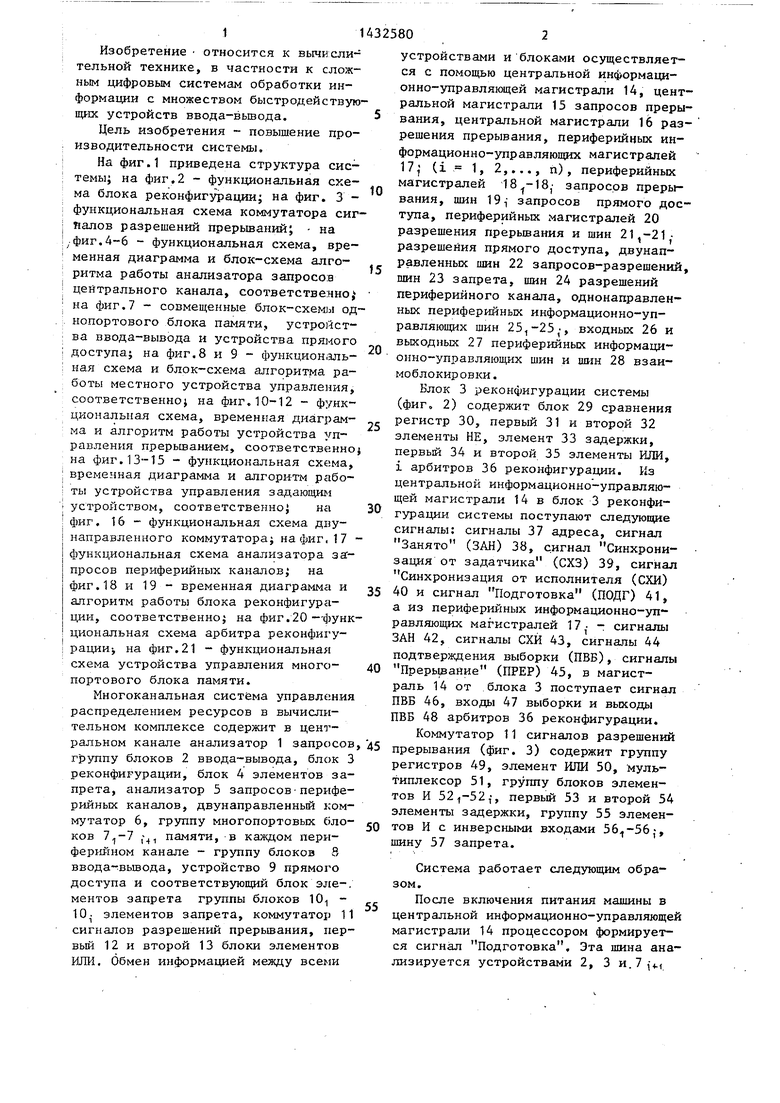

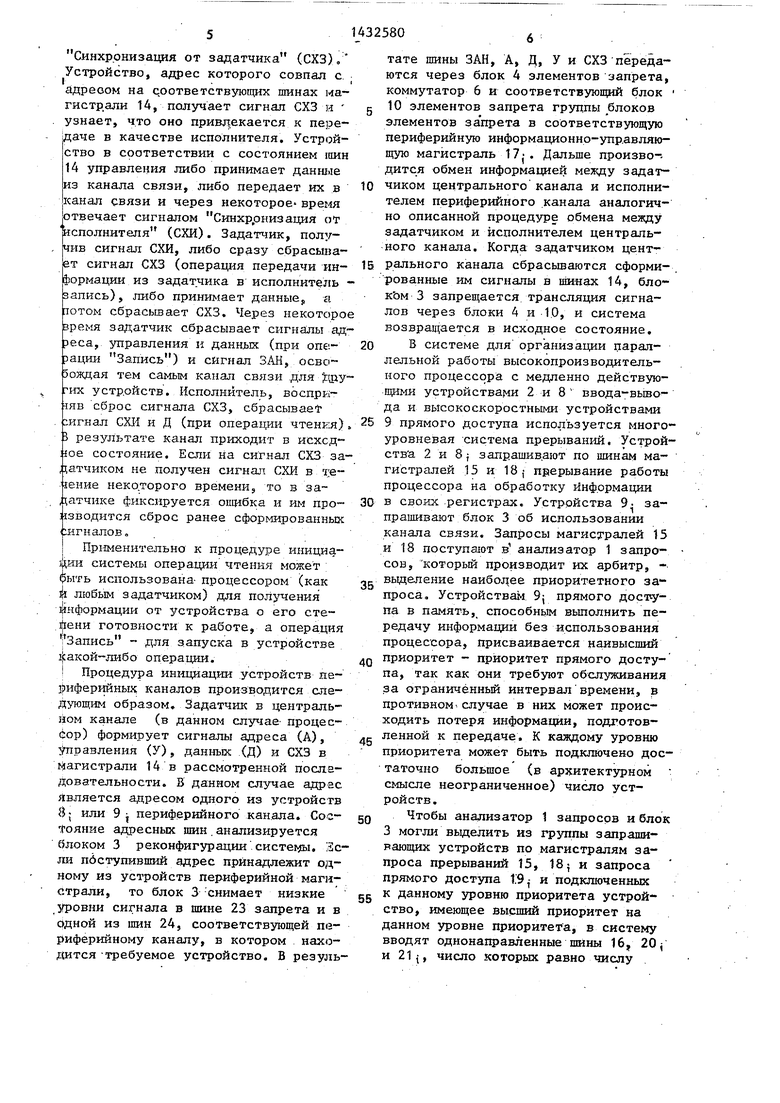

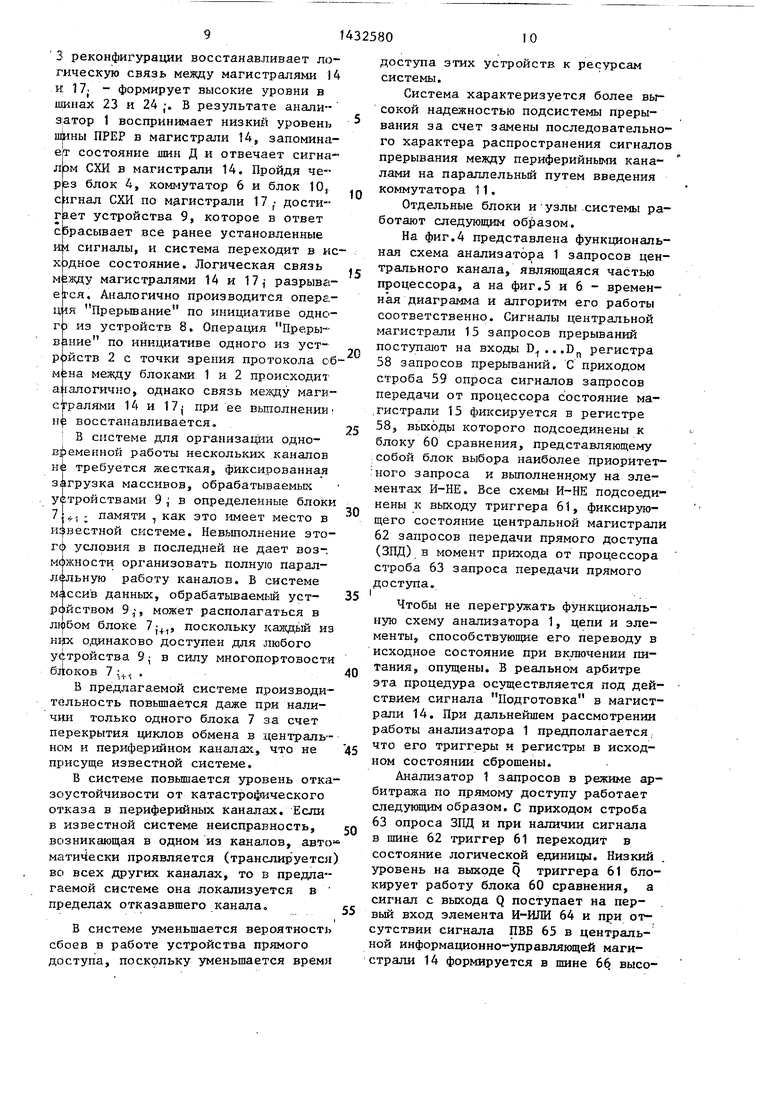

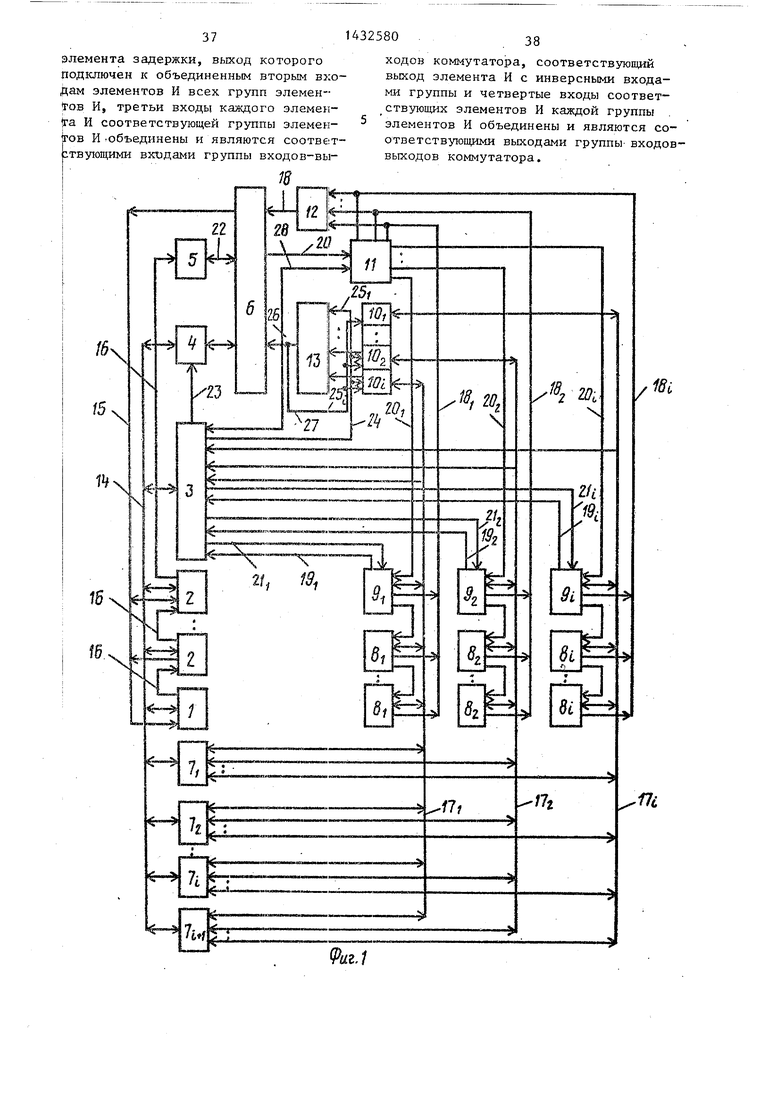

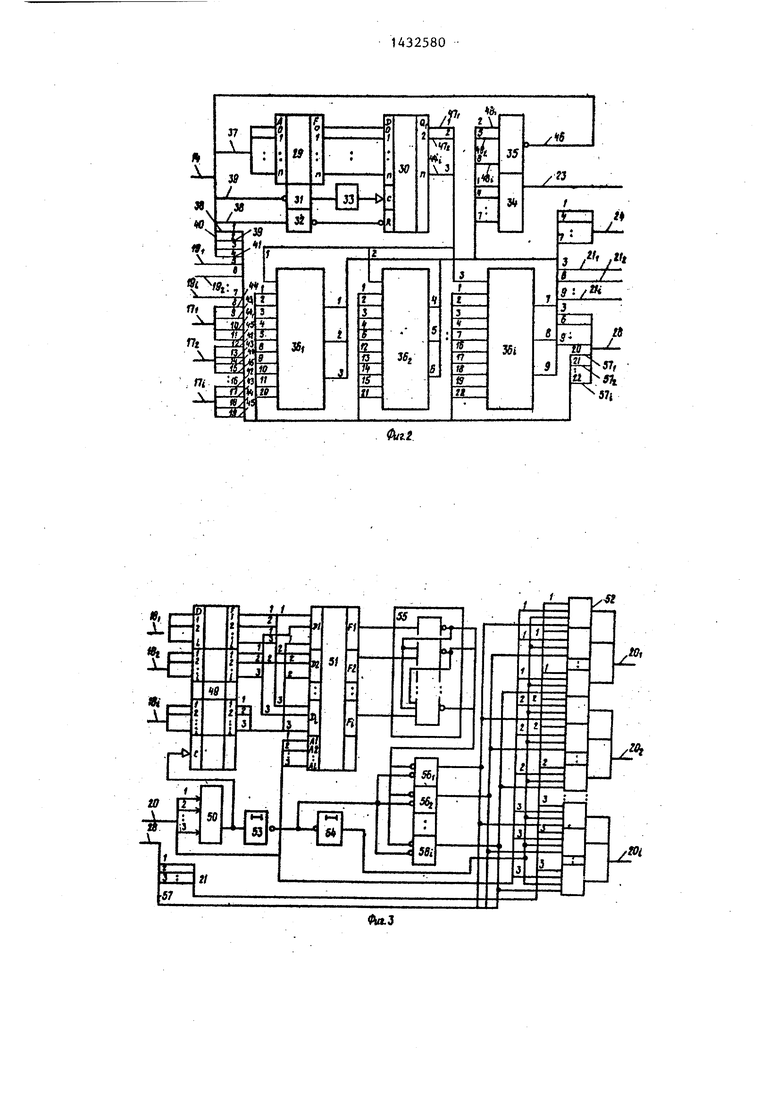

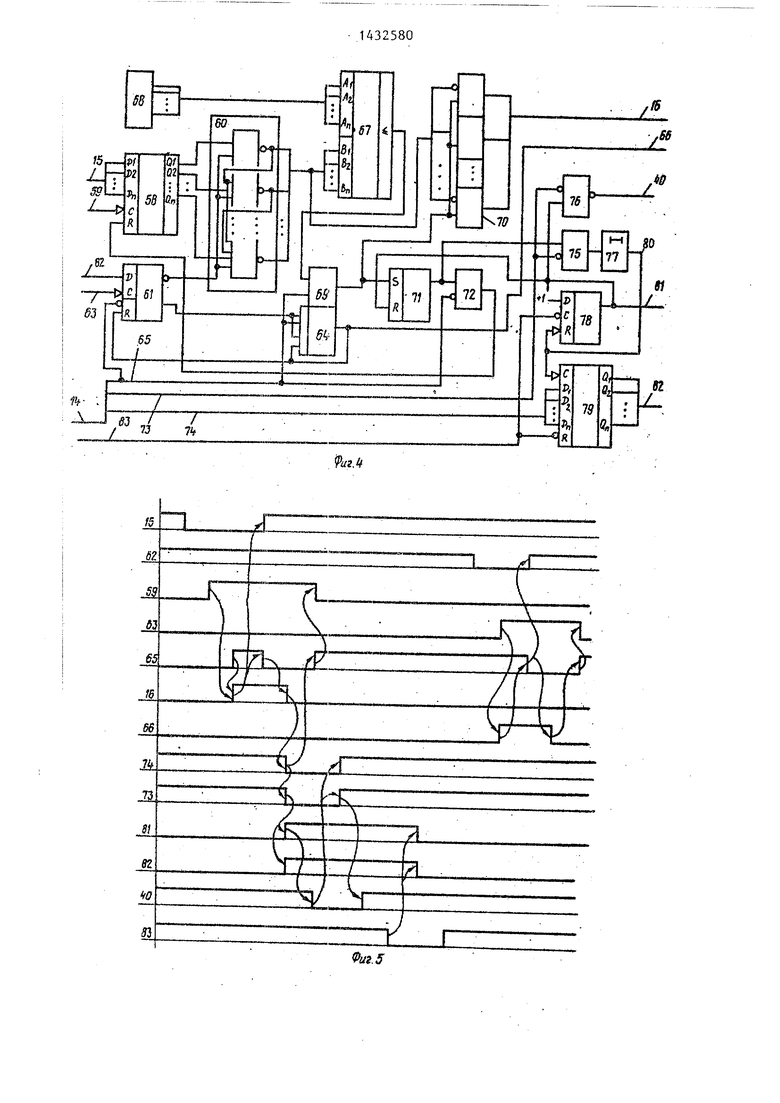

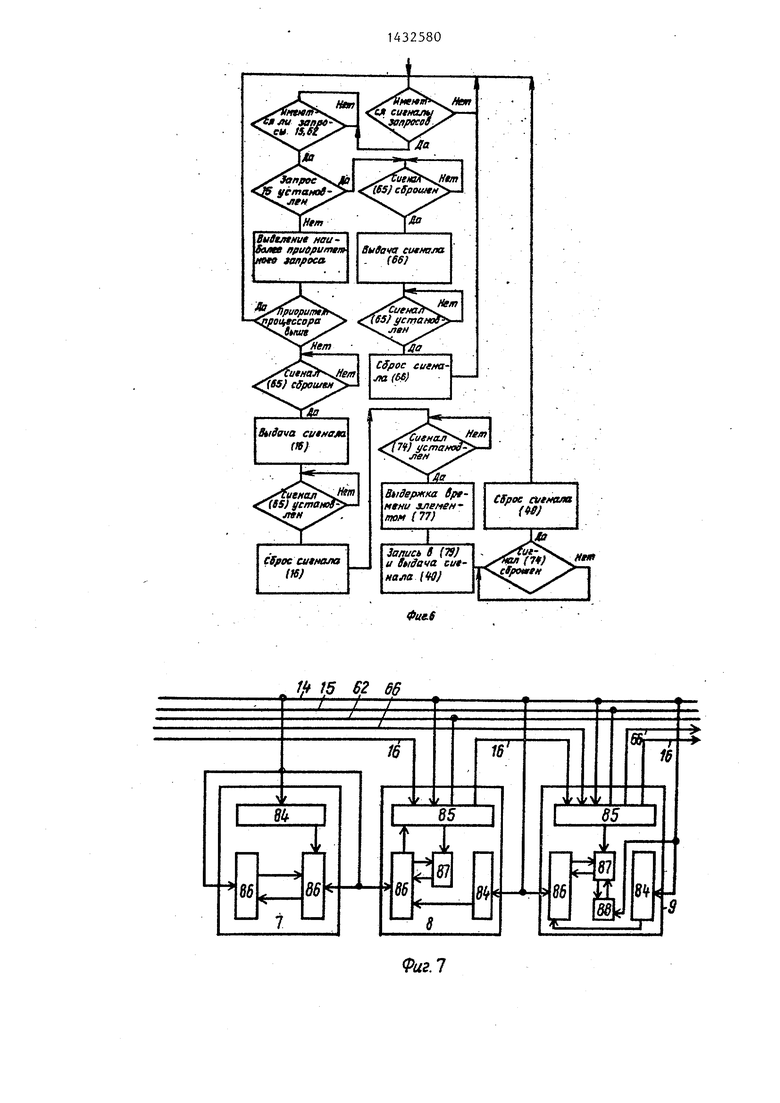

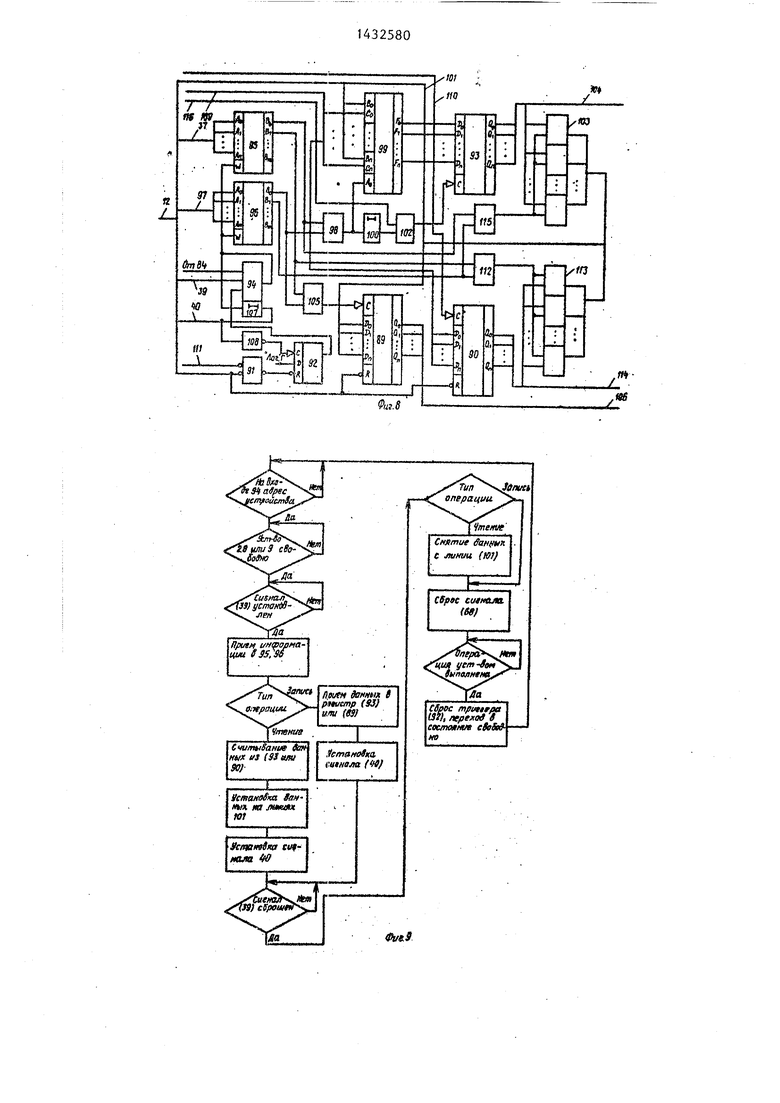

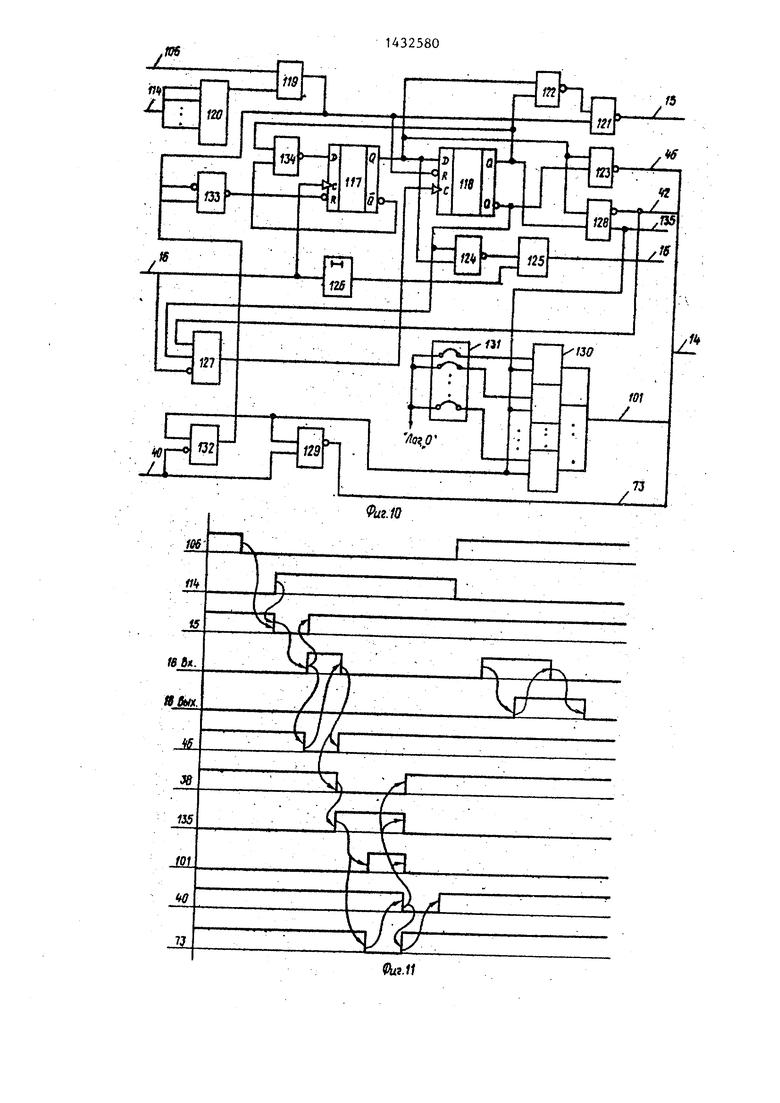

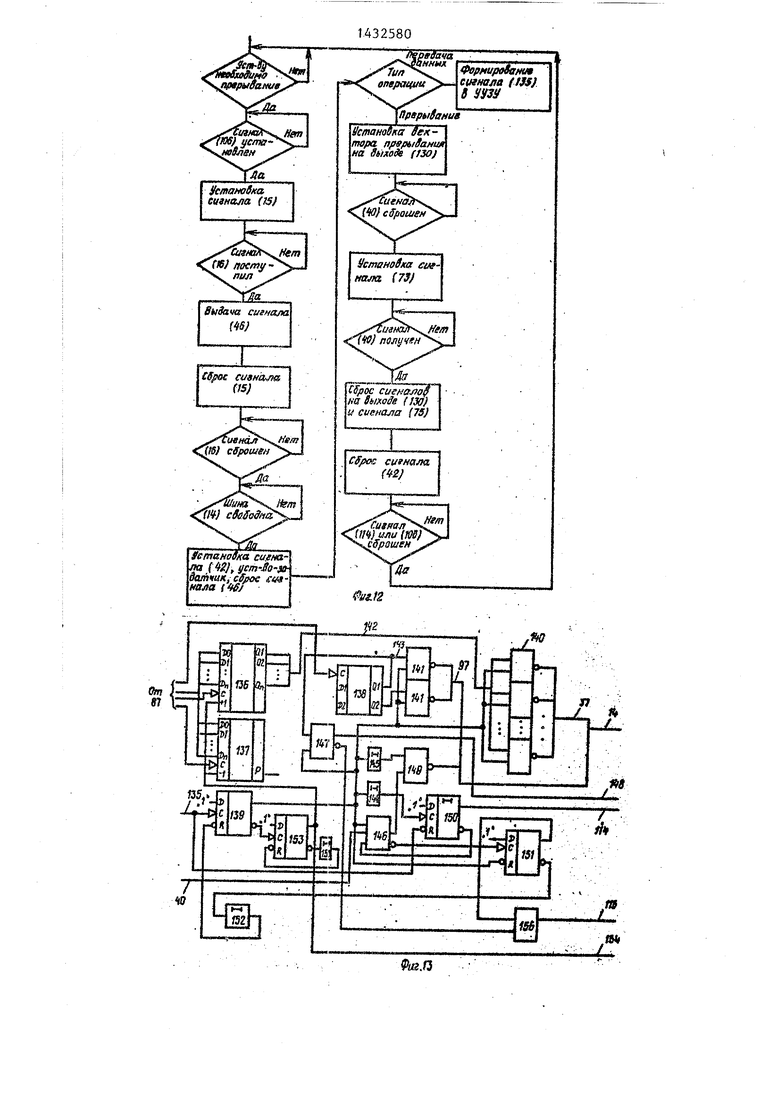

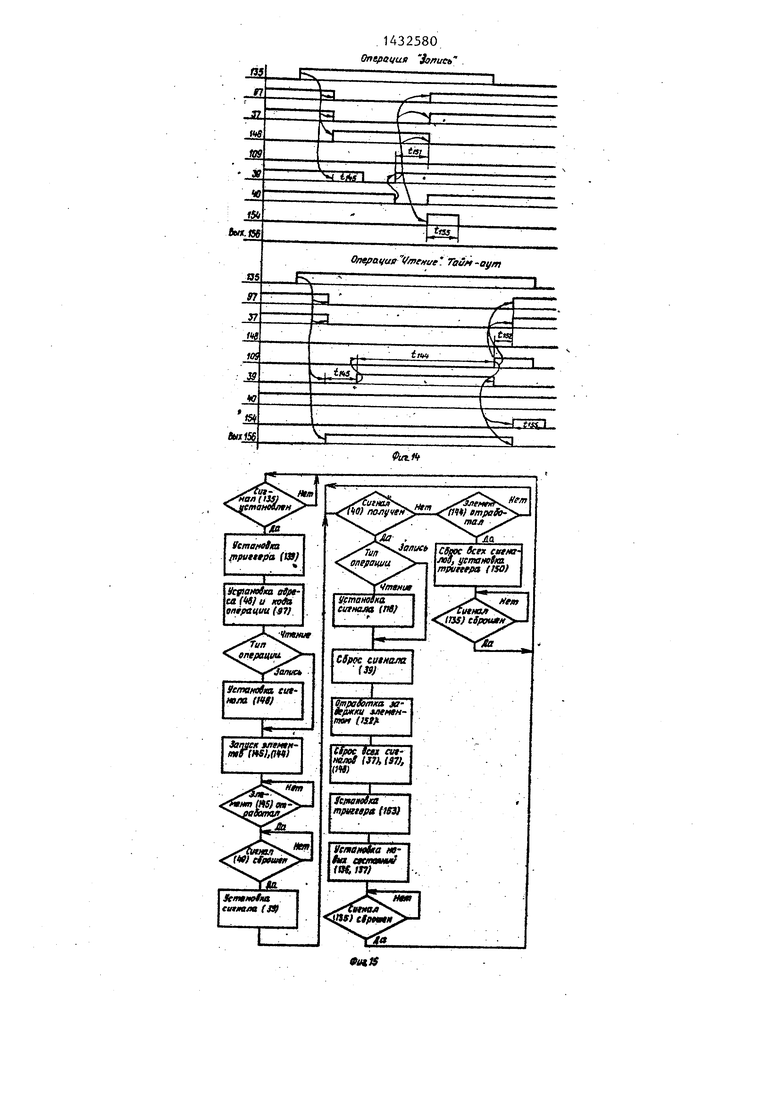

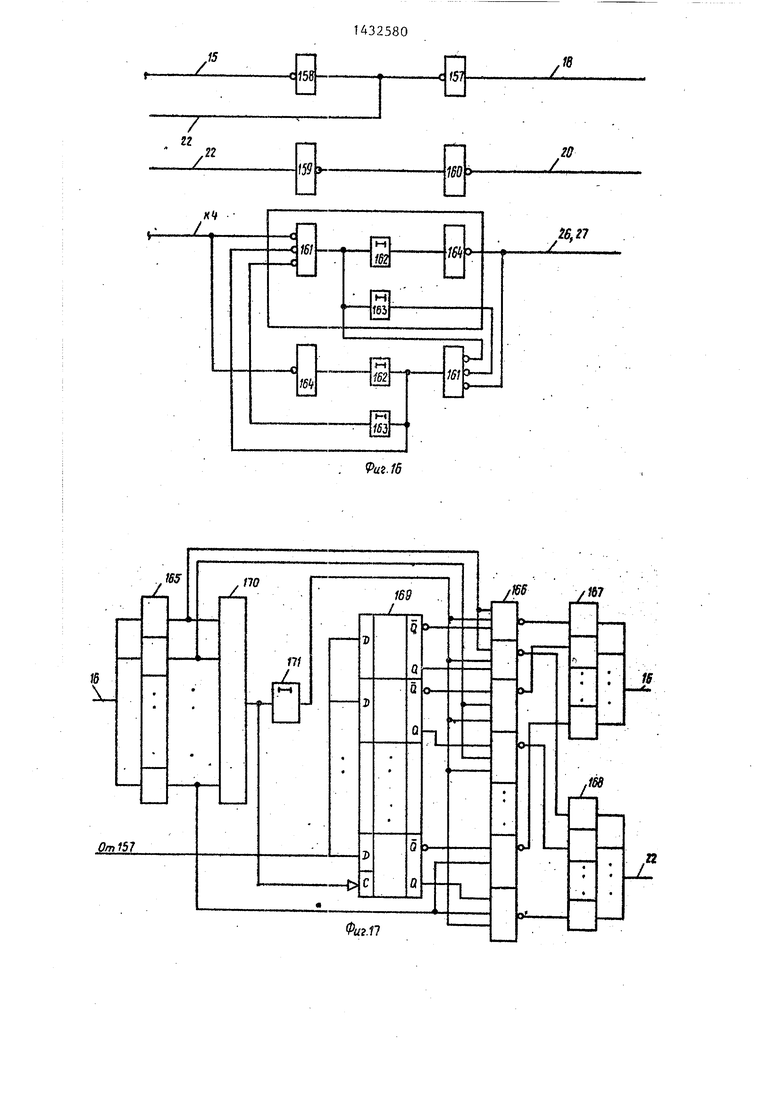

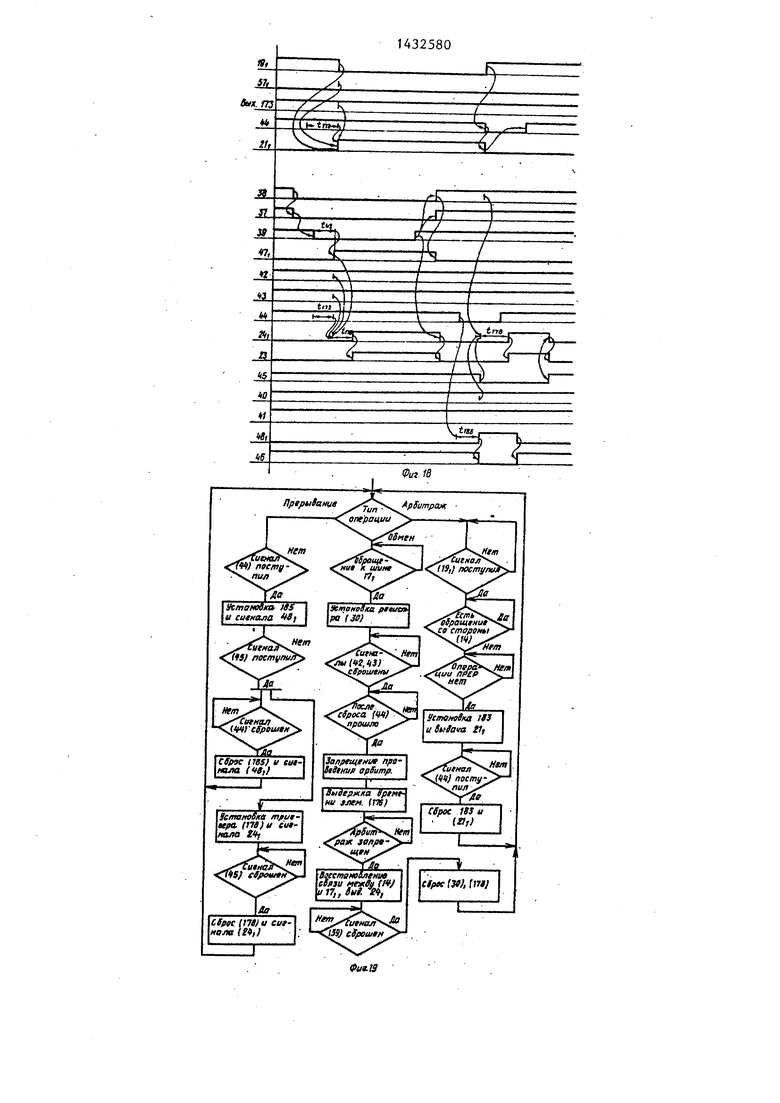

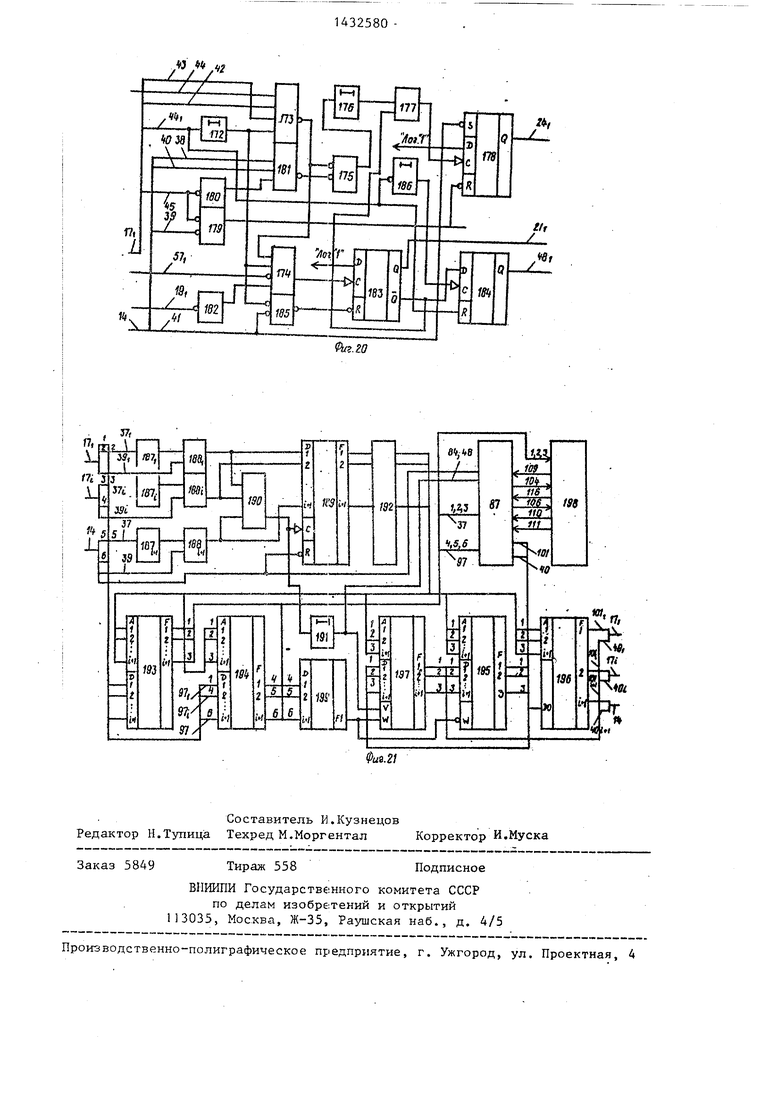

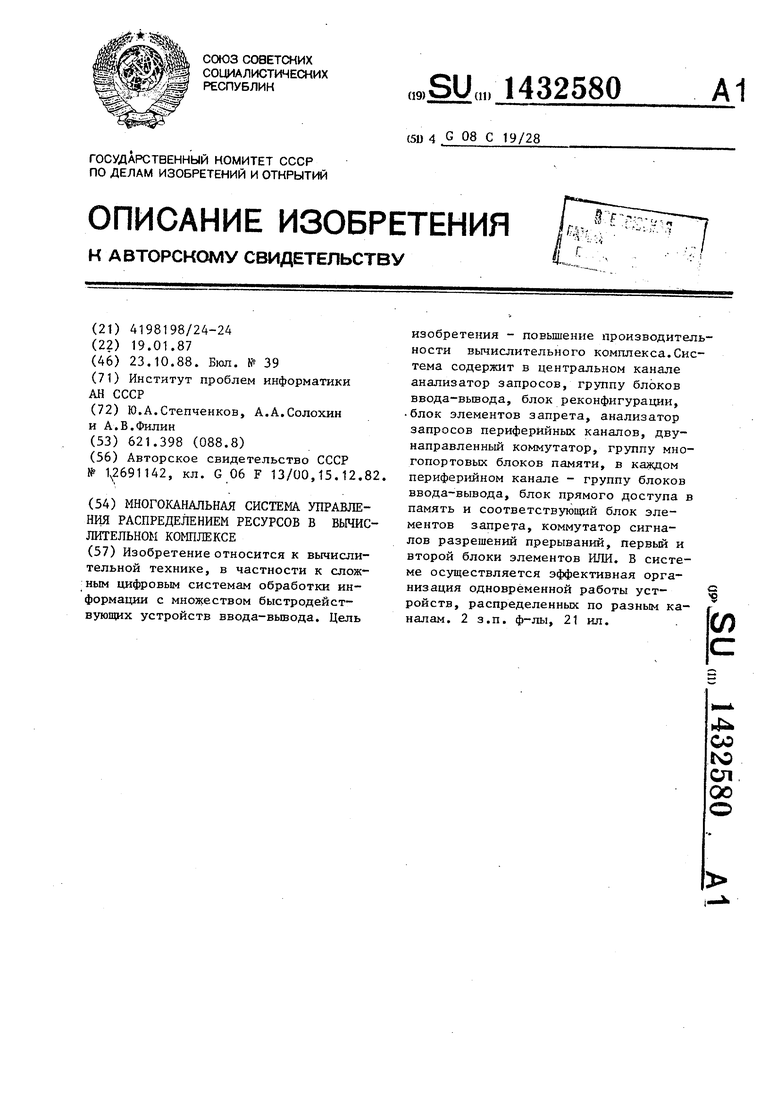

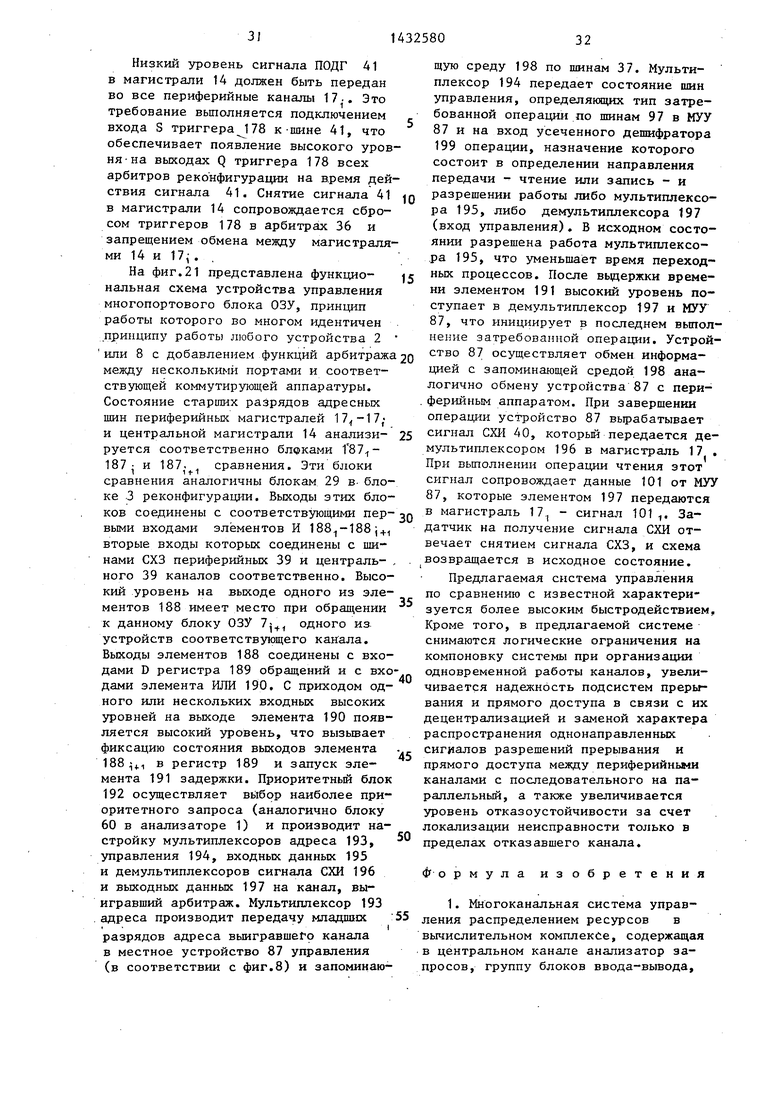

На фиг.1 приведена структура системы; на фиг.2 - функциональная схема блока реконфигурации; на фиг. 3 - функциональная схема коммутатора сиг йалов разрешений прерьшаний; на ,фиг.4-6 - функциональная схема, временная диаграмма и блок-схема алгоритма работы анализатора запросов центрального канала, соответственно, на фиг.7 - совмещенные блок-схемы од нопортового блока памяти, устройства ввода-вывода и устройства пряного доступа; на фиг. 8 и 9 - функцион аль- ная схема и блок-схема алгоритма работы местного устройства управления, соответственно) на фиг.10-12 - функциональная схема, временная диаграмма и алгоритм работы устройства управления прерьшанием, соответственно на фиг.13-15 - функциональная схема, временная диаграмма и алгоритм работы устройства управления задающим устройством, соответственно; на фиг. 16 - функциональная схема двунаправленного коммутатора; на фиг,17 функциональная схема анализатора запросов периферийных каналов; на фиг.18 и 19 - временная диаграмма и алгоритм работы блока реконфигурации, соответственно; на фиг.20 --функциональная схема арбитра реконфигу- рации на фиг.21 - функциональная схема устройства управления многопортового блока памяти.

Многоканальная система управления распределением ресурсов в вычислительном комплексе содержит в ценгКоммутатор 11 сигналов разрешений

ральном канале анализатор 1 запросов, 45 прерывания (фиг. 3) содержит группу

группу блоков 2 ввода-вывода, блок 3 реконфигурации, блок 4 элементов запрета, анализатор 5 запросов-периферийных каналов, двунаправленный коммутатор 6, группу многопортовых блоков ,-, памяти, в каждом периферийном канале - группу блоков 8 ввода-:вьшода, устройство 9 прямого доступа и соответствующий блок эле-, ментов запрета группы блоков 10 - 10. элементов запрета, коммутатор 11 сигналов разрешений прерьшания, первый 12 и второй 13 блоки элементов ИЛИ. Обмен информацией между всеми

50

55

регистров 49, элемент ИЛИ 50, мультиплексор 51, группу блоков элементов И 52,-52,, первый 53 и второй 54 элементы задержки, группу 55 элементов И с инверсными входами 56.,-56j, шину 57 запрета.

Система работает следующим образом.

После включения питания машины в центральной информационно-управляющ магистрали 14 процессором формирует ся сигнал Подготовка, Эта шина ан лизируется устройствами 2, 3 и. 7 ,4i.

устройствами и блоками осуществляется с помощью центральной информационно-управляющей магистрали 14, центральной магистрали 15 запросов прерывания, центральной магистрали 16 разрешения прерывания, периферийных информационно-управляющих магистралей 17. (i 1, 2,..., п), периферийных

магистралей , запросов прерывания, ашн 19-f запросов прямого доступа, периферийньпс магистралей 20 разрешения прерьшания и шин 21,-21- разрешейия прямого доступа, двунаправленных шин 22 запросов-разрешений, шин 23 запрета, шин 24 разрешений периферийного канала, однонаправленных периферийных информационно-управляющих шин , входных 26 и выходных 27 периферийных информационно-управляющих шин и шин 28 взаимоблокировки.

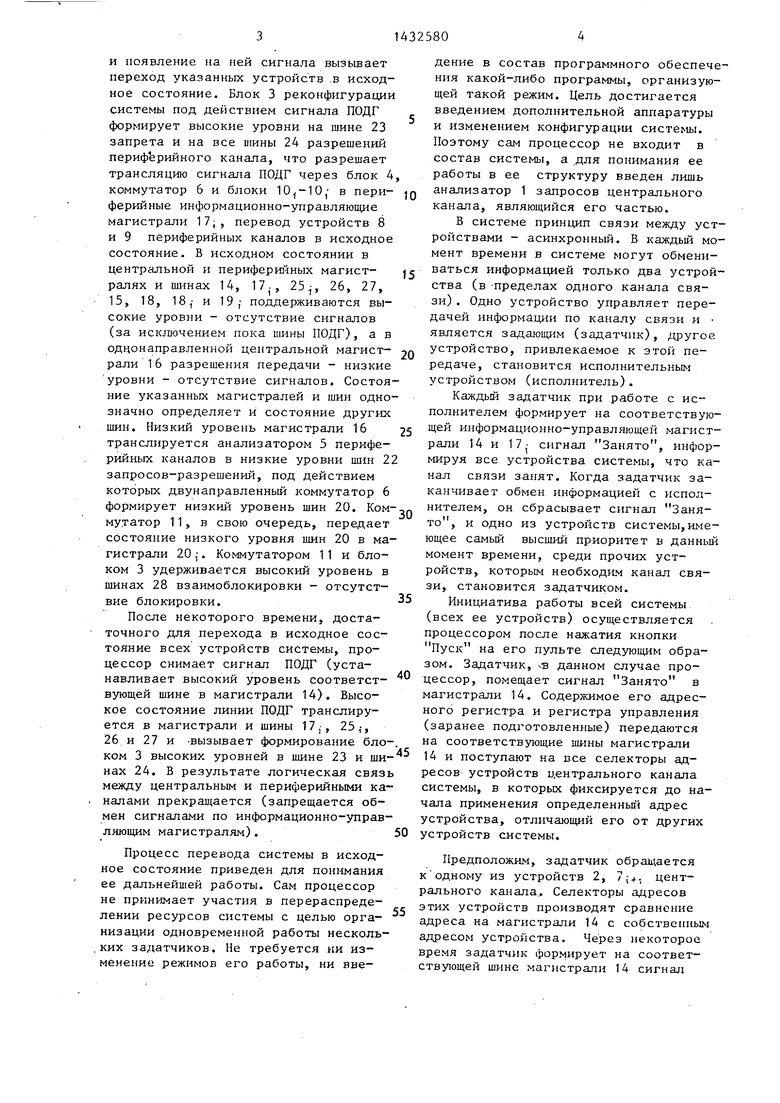

Блок 3 реконфигурации системы (фиг, 2) содержит блок 29 сравнения регистр 30, первый 31 и второй 32 элементы НЕ, элемент 33 задержки, первый 34 и второй 35 элементы ИЛИ, i арбитров 36 реконфигурации. Кз центральной информационно-управляющей магистрали 14 в блок 3 реконфигурации системы поступают следующие сигналы: сигналы 37 адреса, сигнал Занято (ЗАН) 38, сигнал Синхронизация от задатчика (СХЗ) 39, сигнал Синхронизация от исполнителя (СХИ) 40 и сигнал Подготовка (ПОДГ) 41, а из периферийных информационно-управляющих магистралей 17- - сигналы ЗАН 42, сигналы СХЙ 43, сигналы 44 подтверждения выборки (ПВБ), сигналы Прерьдаание (ПРЕР) 45, в магистраль 14 от блока 3 поступает сигнал ПВБ 46, входы 47 выборки и выходы ПВБ 48 арбитров 36 реконфигурации.

Коммутатор 11 сигналов разрешений

прерывания (фиг. 3) содержит группу

0

5

регистров 49, элемент ИЛИ 50, мультиплексор 51, группу блоков элементов И 52,-52,, первый 53 и второй 54 элементы задержки, группу 55 элементов И с инверсными входами 56.,-56j, шину 57 запрета.

Система работает следующим образом.

После включения питания машины в центральной информационно-управляющей магистрали 14 процессором формируется сигнал Подготовка, Эта шина анализируется устройствами 2, 3 и. 7 ,4i.

и появление на ней сигнала вызьшает переход указанных устройств ,в исходное состояние. Блок 3 реконфигурахдии системы под действием сигнала ПОДГ формирует высокие уровни на шине 23 запрета и на все нгины 24 разрешений периферийного канала, что разрешает трансляцию сигнала ПОДГ через блок 4, коммутатор 6 и блоки , в пери- д ферийные информационно-управляющие магистрали 17;, перевод устройств 8 и 9 периферийных каналов в исходное состояние, В исходном состоянии в центральной и перифериз ных магист- 5 ралях и шинах 14, 17., 25 j, 26, 27, 15, 18, 18, и 19; поддерживаются высокие уровни - отсутствие сигналов (за иск;почением пока шины ПОДГ), а в однонаправленной центральной магист- 20 рали 16 разрешения передачи - низкие уровни - отсутствие сигналов. Состояние указанных магистралей и шин однозначно определяет и состояние других шин. Низкий уровень магистрали 16 25 транслируется анализатором 5 периферийных каналов в низкие уровни шин 22 запросов-разрешений, под действием которых двунаправленный коммутатор 6 формирует низкий уровень шин 20, мутатор 11, в свою очередь, передает состояние низкого уровня шин 20 в магистрали 20 ,, Коммутатором 11 и блоком 3 удерживается высокий уровень в шинах 28 взаимоблокировки - отсутствие блокировки,- -

После некоторого времени, достаточного для перехода в исходное состояние всех устройств системы, процессор снимает сигнал ПОДГ (устанавливает высокий уровень соответствующей шине в магистрали 14), Высокое состояние линии ПОДГ транслируется в магистрали и шины 17,-, 25,-, 26 и 27 и -вызывает формирование бло-. ком 3 высоких уровней в шине 23 и шинах 24, В результате логическая связь между центральным и периферийными каналами прекращается (запрещается обмен сигналами по информационно-управляющим магистралям),50

Процесс перевода системы в исходое состояние приведен для понимания е дальнейшей работы. Сам процессор е принимает участия в перераспредеении ресурсов системы с целью оргаизации одновременной работы несколь- их задатчиков. Не требуется ни изенение режимов его работы, ни введение в состав программного обеспечения какой-либо программы, организующей такой режим. Цель достигается введением дополнительной аппаратуры и изменением конфигурации системы. Поэтому сам процессор не входит в состав системы, а для понимания ее работы в ее структуру введен лишь анализатор 1 запросов центрального канала, являющийся его частью,

В системе принцип связи между устройствами - асинхронный, В каждый момент времени в системе могут обмениваться информацией только два устройства (в -пределах одного канала связи) , Одно устройство управляет передачей информации по каналу связи и является задающим (задатчик), другое устройство, привлекаемое к этой передаче, становится исполнительным устройством (исполнитель),

Каждьй задатчик при работе с исполнителем формирует на соответствующей информационно-управляющей магистрали 14 и 17j сигнал Занято, информируя все устройства системы, что канал связи занят. Когда задатчик заканчивает обмен информацией с исполнителем, он сбрасывает сигнал Занято, и одно из устройств системы,имеющее самьй высший приоритет в данный момент времени, среди прочих устройств, которым необходим канал связи, становится задатчиком.

Инициатива работы всей системы (всех ее устройств) осуществляется процессором после нажатия кнопки Пуск на его пульте следующим образом, Задатчик, -.в данном случае процессор, помещает сигнал Занято в магистрали 14, Содержимое его адресного регистра и регистра управления (заранее подготовленные) передаются на соответствующие шины магистрали 14 и поступают на все селекторы адресов устройств центрального канала системы, в которых фиксируется до начала применения определенньш адрес устройства, отличающий его от других устройств системы.

Предположим, задатчик обра цается к одному из устройств 2, 7;4-, центрального канала.. Селекторы адресов этих устройств производят сравнение адреса на магистрали 14 с собственным адресом устройства. Через некоторое время задатчик формирует на соответствующей шине магистрали 14 сигнал

Синхронизация от задатчика (СХЗ), Устройство, адрес которого совпал с

адресом на с оответствздащих шинах магистрали 14, получает сигнал СХЗ и узнает, что оно привл:екается к пере- |даче в качестве исполнителя. Устройство в срответствии с состоянием IDHH 14 управления либо принимает даншае из канала связи, либо передает их в канал связи и через некоторое время отвечает сигналом Синхррнизация от исполнителя (СХИ). Задатчик, получив сигнал СХИ, либо сразу сбрасывает сигнал СХЗ (операция передачи ин- формации из задатчика в исполнитель запись), либо принимает данные, а :ioTOM сбрасьшает СХЗ. Через некоторо время задатчик сбрасывает сигналы а,ц реса,, управления и данньпс (при onei- рации Запись) и сигнал ЗАН, осво эождая тем самым канал связи .для 7iix устройств. Исполнитель, воспри- шв сброс сигнала СХЗ, сбрасывает г,игнал СХИ и Д (при операции чтения) i результате канал приходит в исход- :ше состояние. Если На сигнал СХЗ за датчиком не получен сигнал СХИ в те- 1ение некоторого времени, то в за- датчике фиксируется ошибка и им про™ изводится сброс ранее сформированных сигналов.

I Пр1менительно к процедуре инициа- JJJSHH системы операции чтения может ; фыть использована- процессором (как любым задатчиком) для пол чения ф-нформации от устройства о его сте фени готовности к работе, а операция Запись - для запуска в устройстве 1|:акой либо операции.

I Процедура инициации устройств пе- 1|)иферийных каналов производится следующим образом, Задатчик в центральном канале (в данном слуг1ае- процессор) формирует сигналы адреса (А), irnpaBЛенин (У), данных (Д) и СХЗ в магистрали 14 в рассмотренной последовательности. В данном случае адрес Является адресом одного из устройств {5; или 9 j периферийного кан.ала. Соо- тояние адресных шин.анализируется блоком 3 реконфигурации .системы, Зс ли П(5ступивпп1й адрес принадлежит одному из устройств периферийной магистрали, то блок 3 снимает низкие уровни сигнала в шине 23 запрета и в одной из шин 24, соответствующей периферийному каналу, в котором нахо- датся -требуемое устройство. В результате шины ЗАН, А, Д, У и СХЗ передаются через блок 4 элементов запрета, коммутатор 6 и соответствующий блок 10 элементов запрета группы блоков элементов за прета в соответствующую периферийную информационно-управляющую магистраль 17;. Дальше произво-- дится обмен информацией между задатчиком центрального канала и исполнителем периферийного канала аналогично описанной процедуре обмена между задатчиком и исполнителем центрального канала. Когда задатчиком центрального канала сбрасываются сформи- рованные им сигналы в вшнах 14, бло- к ом 3 запрещается трансляция сигналов через блоки 4 и 1.0, и система возвращается в исходное состояние.

В системе для организации параллельной работы высокопроизводительного процессора с медленно действующими устройствами 2 и 8 ввода-вьшо- да и высокоскоростньми устройствами 9 прямого доступа испол ьзуется многоуровневая система прерываний. Устройства 2 и 8 i запрашивают по шинам ма- гистралей 15 и 16,- прерывание работы процессора на обработку информации в своих регистрах. Устройства 9- запрашивают блок 3 об использовании канала связи. Запросы магистралей 15 и 18 поступают в анализатор 1 запросов, которьй производит их арбитр, - выделение наиболее приоритетного запроса. Устройствам 9j прямого доступа в память, способным вьшолнить передачу информации без использования процессора, присваивается наивысший приоритет - приоритет прямого доступа, так как они требуют обслуживания за ограниченный интервал времени, в ПРОТИВНОМ случае в них может происходить потеря информации, подготовленной к передаче, К каждому приоритета может быть подключено достаточно большое (в архитектзфном смысле неограниченное) число устройств.

Чтобы анализатор 1 запросов и бло 3 могли вьщелить из группы запралм- вающик устройств по магистралям запроса прерываний 15, 18; и запроса прямого доступа 1.9,- и Подключенных к данному уровню приоритета устройство, имеющее высший приоритет на данном уровне приоритета, в систему вводят одионадравленные шины 16, 20 и 21, число которых равно числу

уровней приоритета. Эти шины последовательно проходят через все устройства, подключенные к данному уровню приоритета, причем чём ближе в электрической цепи и источнику сигнала располагается устройство, тем более высокий приоритет на данном уровне оно имеет. Источником шин разрешения прерывания является анализа- тор 1 запросов центрального канала, а шин 21- разрешения прямого доступа - блок реконфигурации системы.

После того, как процессором осуществлена процедура инициации уст- ройств, в системе возможна одновременная работа нескольких каналов (по числу инициированных каналов). Рас смотрим автономную работу .одного из периферийных каналов; Устройство 9 прямого доступа, инициированное процессором, осуществляет процедуру захвата соответствующего периферийного

канала, формируя низкий уровень сигнала. Запрос прямого доступа (ЗПД) - 19. Низкий уровень поступает в блок 3, которьй производит анализ поступившего запроса. При вьшолнении опре дeJ eнныx условий (см. описание работ блока 3) блоком вьщается разрешение прямого доступа - высокий уровень сигнала 21 .

Получив сигнал 21 -, устройство 9 при определенных условиях (см. описание работы устройства управления прерьшанием) формирует низкий уро- вень на шине ЗАН в магистрали 17 j - становится задатчиком - сбрасывает сигнал 19 и отвечает блоку 3 низким уровнем сигнала Подтверждение выборки (ПВБ) в магистрали 17 . Блок 3 на сигнал ПВБ отвечает сбросом высокого уровня шины 21J, а устройство 9,- в свою очередь сбросом сигнала ПББ. На этом процедура захвата периферийного канала заканчивается и устройство 9. может осуществлять обмен информации с исполнителем, например 7(, аналогично рассмотренному обмену между задатчиком и исполнителем центрального канала.

Обмен в рассматриваемом периферийном канале не оказывает влияния на Ьбмены, осуществляемые в других каналах. Именно поэтому возможна организация параллельной работы нескольких каналов. Устройство 9ч занимает периферийньш канал на определенное время - время обмена массивом инфор5

л

,,

5 0 5

мации с исполнителем 7,- . Велргчина массива задается процессором. После окончания передачи массива устройство 9,- освобождает канал и уведомляет об этом процессор операцией Прерывание следующим образом.

Устройство 9. формирует низкий уровень на соответствующей шине магистрали 18; запроса прерывания.Пройдя через блок ИЛИ 12 и коммутатор 6, низкий уровень появляется на соответствующей шине магистрали 15 запросов прерьшания центрального канала, который поступает в анализатор 1. Анализатор 1 производит арбитраж - выделение наиболее приоритетного запроса - и при определенных условиях (см. описание работы анализатора 1) отвечает высоким уровнем соответствующей шины в магистрали 16. Высокий уровень этой шины в магистрали 16 последовательно распространяется через блоки 2,. которые имеют более высокий приоритет на данном приоритетном уровне, и достигает входа ана.ш1- затора 5 запросов периферийных каналов в случае отсутствия запросов со стороны блоков 2. Анализатор 5 передает высокий уровень в шины 22, а коммутатор 6 - в шины 20 разреше- ,ния прерывания. Коммутатор 11 сигналов разрешений производит передачу высокого уровня шин 20 в одну из магистралей 20 , в соответствии с ранее . поступившими в него запросами на пре- рьшание 18 и их приоритетом. Высокий уровень, распространяясь по соответствующей шине магистрали 20 ,, достигает устройс ва 9 j - источника запроса в магистрали 18., который отвечает низким уровнем сигнала ПББ в магистрали 17, которьш, пройдя через блок 3, появляется в магистрали 14. Анализатор 1 в ответ на низкий уровень сигнала ПВБ в магистрали 14 сбрасывает высокий уровень в соответствующей шине магистрали 16, которьй, пройдя последовательно через анализатор 5, коммутаторы 6.и 11, появляется в соответствующей магистрали шине 20,-. Устройство 9,- отвеча- е-т сбросом сигнала в соответствующей шине магистрали 18 и при определенных условиях формирует сигналы ЗАН в магистрали - становится задатчиком, свой вектор прерьшания на шинах Д и сопровождает их сигналом Прерывание. Под действием последнего блок

3 реконфигурации восстанавливает логическую связь между магистралями 14 и 17. - формирует высокие уровни в щкиах 23 и 24 ,-. В результате анализатор 1 воспринимает низкий уровень ПРЕР в магистрали 14, запомина- efT состояние шин Д и отвечает сигна- лЬм СХИ в магистрали 14. Пройдя че- блок 4, коммутатор 6 и блок 10, сигнал СХИ по магистрали 17 ,, дости- устройства 9, которое в ответ с|брасывает все ранее установленные им сигналы, и система переходит в ис х|эдное состояние. Логическая связь мгзвду магистралями 14 и 17 разрывается, Анап.огично производится оперг:- цця Прерьгоание по инициативе одно- г|з из устройств 8. Операция Прерывание по инитдиативе одного из уст- р эйств 2 с точки зрения протокола об между блоками 1 и 2 происходит а|1алогично, однако связь маги- с гралями 14 и 17j при ее выполнении: н восстанавливается

; В системе для организации одновременной работы нескольких каналов не требуется жесткая, фиксированная загрузка массивов, обрабатываемых устройствами 9i в определенные блоки ..| ; памяти , как это 1-1меет место в и: вестной системе. Невыполнение зто- гф условия в последней не дает воз-, нежности организовать полную парал- жшьную работу каналов, В системе массив данных, обрабатьшаемьй устройством , может располагаться в Л19бом блоке 7j,, поскольку каждый из Hipc о,щнаково доступен для любого устройства 9 в силу многопортовостн блоков 7 ,, .

В предлагаемой системе производи- тальность повышается даже при наличии только одного блока 7 за счет перекрытия циклов обмена в центральном и периферийном каналах, что не присуще известной системе,

В системе повьшается уровень отказоустойчивости от катастрофического отказа в периферийных каналах. Если в известной системе неисправность, возникающая в одном из канапов, авто MaTHtiecKH проявляется (транслируется во всех других каналах, то в предлагаемой системе она локализуется в пределах отказавшего канала«

В системе уменьшается вероятность сбоев в работе устройства прямого доступа, поскольку уменьшается время

0

5

0

5

0

5

0

5

0

5

доступа этих устройств к ресурсам системы.

Система характеризуется более высокой надежностью подсистемы прерывания за счет замены последовательного характера распространения сигналов прерывания между периферийными каналами на параллельньй путем введения коммутатора 11.

Отдельные блоки и узлы системь работают следующим образом.

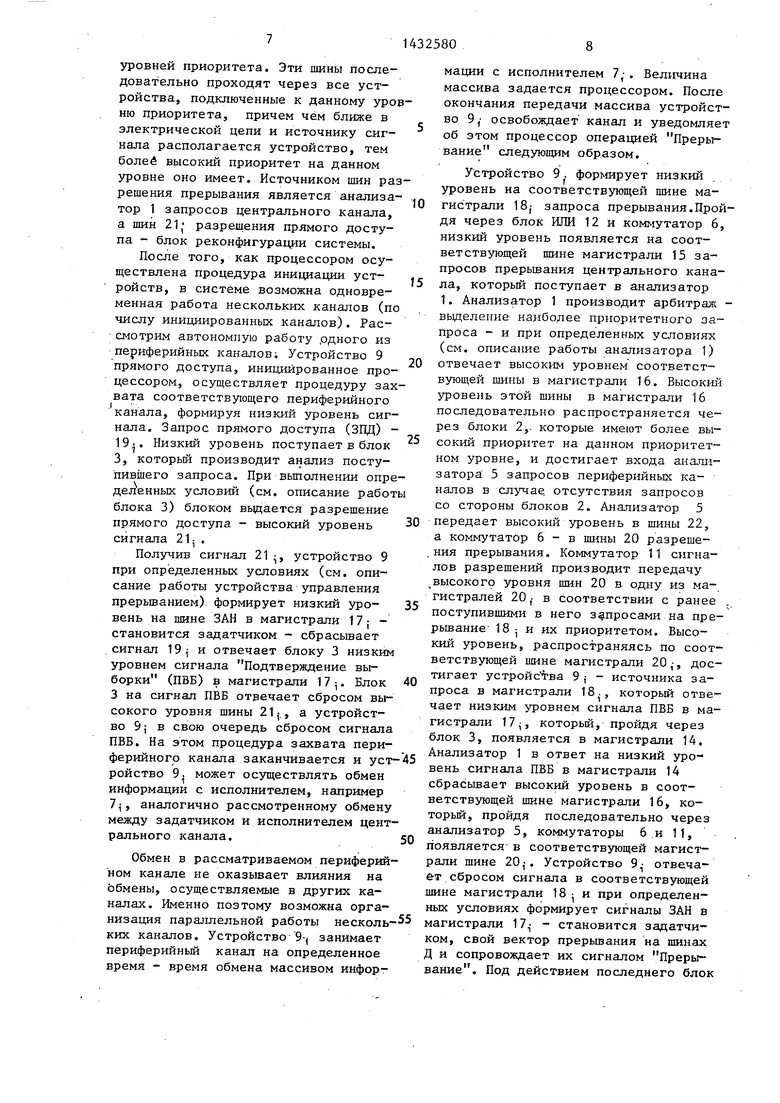

На фиг.4 представлена функциональная схема анализатора 1 запросов центрального канала, являющаяся частью процессора, а на фиг.5 и 6 - временная диаграмма и алгоритм его работы соответственно. Сигналы центральной магистрали 15 запросов прерываний поступают на входы D « «D регистра 58 запросов прерываний, С приходом строба 59 опроса сигналов запросов передачи от процессора Состояние магистрали 15 фиксируется в регистре 58, выходы которого подсоединены к блоку 60 сравнения, представляющему собой блок выбора наиболее приоритет- :ного запроса и вьшолненн.ому на элементах И-НЕ. Все схемы И-НЕ подсоединены к выходу триггера 61, фиксирующего состояние центральной магистрали

62запросов передачи прямого доступа (ЗПД) в момент прихода от процессора строба 63 запроса передачи прямого

доступа,

I

Чтобы не перегружать функциональную схему анализатора 1, цепи и элементы, способствующие его переводу в исходное состояние при включении питания, опущены. В реальном арбитре эта процедура осуществляется под действием сигнала Подготовка в магистрали 14. При дальнейшем рассмотрении работы анализатора 1 предполагается, что его триггеры и регистры в исходном состоянии сброшены.

Анализатор 1 запросов в режиме арбитража по прямому доступу работает следующим образом, С приходом строба

63опроса ЗПД и при наличии сигнала в шине 62 триггер 61 переходит в состояние логической единицы. Низкий уровень на выходе Q триггера 61 блокирует работу блока 60 сравнения, а сигнал с выхода Q поступает на пер- . вый вход элемента И-ИЛИ 64 и при отсутствии сигнала ПВБ 65 в центральной информационно-управляющей магистрали 14 формируется в шине 66 высоn14

кий уровень. В ответ на этот сигнал устройство (источник сигнала ЗПД) снимает сигнал на шине 62 и подтверждает принятие сигнала с шины 66 формированием низкого уровня сигнала 65. Ана- лизатор 1 запросов в ответ снимает высокий уровень в центральной магистрали 66 разрешения.прямого доступа, и в результате, блок возвращается в исходное состояние.

Рассмотрим процедуру арбитража для сигналов центральной магистрали 15 запросов прерываний. С приходом от процессора строба 59 опроса ЗП в ре

запроса становится задатчиком в системе, оно формирует в центральной информационно-управляющей магистрали 14 сигнал Прерывание (ПРЕР) 73 и информацию на шинах 74 данных. Сигнал 73 поступает на первые входы схем И 75, 76 н через время, отрабатьшае- мое элементом 77 задержки, сигнал 80 высокого уровня поступает на управляющие входы триггера 78 и регистра 79. Триггер 78 фиксирует факт прихода ПРЕР 73, а регистр 79 запоминает содержимое шин 74 данных в центральной информационно-управляющей магистгистр 58 записывается состояние маги-15 рали 14. Усп-ройство-задатчик по шинам страли 15. Если блок 60 сравнения не блокирован триггером 61, то на одном из его выходов, соответствующих наиболее приоритетному запросу на маги- стгГали 15 в данньш момент времени, 20 формируется низкий уровень (логическая единица). Выходы блока 60 сравнения соединены с второй группой входов компаратора 67, первая группа

- 25

74 передает информацию, однозначно определяющую -устройство-источник прерывания. Вьздержка времени элементом 77 необходима для заверше.ния переходных процессов в канале и з аписи в регистр 79 достоверной информации. Высокий уровень выхода триггера 78 вызывает сброс триггера 71 и фор шрова- ние в магистрали 14 сигнала Синхронизация от исполнителя сигнала CX1I 40. После прихода в анализатор 1 запросов сброса сигнала 73 сигнал 40 тарсже сбрасьшается. На этом процедура арбитража и операдая Прерывавходов которого соединена с выхода

74 передает информацию, однозначно определяющую -устройство-источник пре рывания. Вьздержка времени элементом 77 необходима для заверше.ния переход ных процессов в канале и з аписи в ре гистр 79 достоверной информации. Высокий уровень выхода триггера 78 вызывает сброс триггера 71 и фор шрова ние в магистрали 14 сигнала Синхронизация от исполнителя сигнала CX1I 40. После прихода в анализатор 1 запросов сброса сигнала 73 сигнал 40 тарсже сбрасьшается. На этом процедура арбитража и операдая Прерывами разрядов регистра 68 команд и состояний процессора, в которых фиксиру- приоритет программы, выполняемой процессором в текущий момент времени. Компаратор 67 сравнивает прио- 30 ние в канале связи заканчивается, ритет процессора с наиболее приори- Информация о факте прерывания 81 и тетным запросом в магистрали 15. Если приоритет процессора ниже приоритета запрашивающего устройства, на

об источнике прерьшания 82 поступает в процессор, который после ее обработки сбрасывает триггер 78 и выходе компаратора 67 формируется регистр 79 сигналом 83, и схема сокий уровень, который поступает на возвращается в исходное состояние, первый вход схемы И 69. При отсутствии сигнала ПББ 65 на выходе схемы

69появляется высокий уровень, которьй поступает на вторые входы схем дО нительные структурные схемы, которые

70и на вход S триггера 71. В резуль- позволяют более наглядно перейти от тате триггер 71 переходит в состояние

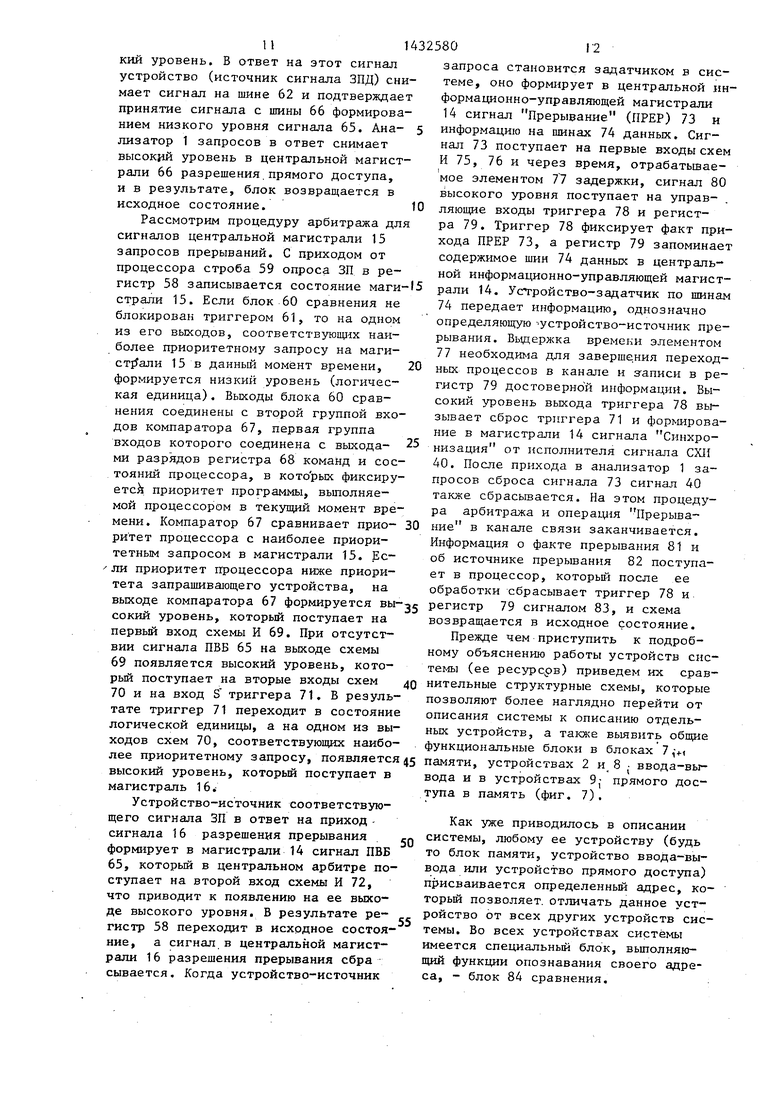

логической единицы, а на одном из выходов схем 70, соответствующих наибоПрежде чем приступить к подробному объяснению работы устройств системы (ее ресурсов) приведем их сравописания системы к описанию отдельных устройств, а также выявить общие функциональные блоки в блоках 7 ,t

лее приоритетному запросу, появляется 45 памяти, устройствах 2 и, 8 ; ввода-вы высокий уровень, который поступает в вода и в устройствах 9{ прямого дос- магистраль 16.тупа в память (фиг. 7).

Устройство-источник соответствующего сигнала ЗП в ответ на приход 50

сигнала 16 разрешения прерывания формирует в магистрали 14 сигнал ПВБ 65, который в центральном арбитре поступает на второй вход схемы И 72, что приводит к появлению на ее выходе высокого уровня. В результате ре- . гистр 58 переходит в исходное состояние, а сигнал в центральной магистрали 16 разрешения прерывания сбра сывается. Когда устройство-источник

Как уже приводилось в описании системы, любому ее устройству (будь то блок памяти, устройство ввоДа-вы- вода или устройство прямого доступа) присваивается определенньй адрес, ко торьй позволяет, отличать данное устройство от всех других устройств сис темы. Во всех устройствах системы имеется специальный блок, выполняющий функции опознавания своего адреса, - блок 84 сравнения.

Г2

запроса становится задатчиком в системе, оно формирует в центральной информационно-управляющей магистрали 14 сигнал Прерывание (ПРЕР) 73 и информацию на шинах 74 данных. Сигнал 73 поступает на первые входы схем И 75, 76 н через время, отрабатьшае- мое элементом 77 задержки, сигнал 80 высокого уровня поступает на управляющие входы триггера 78 и регистра 79. Триггер 78 фиксирует факт прихода ПРЕР 73, а регистр 79 запоминает содержимое шин 74 данных в центральной информационно-управляющей магистрали 14. Усп-ройство-задатчик по шинам

15 рали 14. Усп-ройство-задатчик по шинам 20

25

74 передает информацию, однозначно определяющую -устройство-источник прерывания. Вьздержка времени элементом 77 необходима для заверше.ния переходных процессов в канале и з аписи в регистр 79 достоверной информации. Высокий уровень выхода триггера 78 вызывает сброс триггера 71 и фор шрова- ние в магистрали 14 сигнала Синхронизация от исполнителя сигнала CX1I 40. После прихода в анализатор 1 запросов сброса сигнала 73 сигнал 40 тарсже сбрасьшается. На этом процедура арбитража и операдая Прерыва30 ние в канале связи заканчивается, Информация о факте прерывания 81 и

об источнике прерьшания 82 поступает в процессор, который после ее обработки сбрасывает триггер 78 и регистр 79 сигналом 83, и схема возвращается в исходное состояние,

Прежде чем приступить к подробному объяснению работы устройств системы (ее ресурсов) приведем их сравпозволяют более наглядно перейти от

описания системы к описанию отдельных устройств, а также выявить общие функциональные блоки в блоках 7 ,t

Как уже приводилось в описании системы, любому ее устройству (будь то блок памяти, устройство ввоДа-вы- вода или устройство прямого доступа) присваивается определенньй адрес, ко- торьй позволяет, отличать данное устройство от всех других устройств системы. Во всех устройствах системы имеется специальный блок, выполняющий функции опознавания своего адреса, - блок 84 сравнения.

131432580

В системе с одной магистралью в любой операции обмена информацией всегда участвуют дда устройства,связанные между собой как задатчик (управляющее устройство) и исполнителъ управляемое устройство). Bqe другие устройства, которым требуется маги- траль для обмена, информируют об фтом анализатор 1 запросов централь14

нальньЕС частей, содержат запоминаю щую среду, состоящую из взаимосвязанных запоминакшщх элементов.

Уровень детализации функциональ ных частей блоков 7j, , за исключе нием блока 84 сравнения, соответст вует уровню стандартных функционал ных элементов и не требует дальней конкретизации. Местное устройство

,- - -. - jT --jt-, - «.M.uA « «А J - Л JJЛ л.

ото канала по шинам магистрали запро- управления здесь вьфождается в дефа прерьшаний. Часть устройства, от етственная за формирование сигналов Запросов прерываний и обмена сигна с анализатора 1 вплоть до того фомента, когда устройство становится $адатчиком, называется устройством {15 управления прерыванием. Устройст но ввода-вывода запрашивает канал с|вязи только для уведомления процес- (fopa о завершении устройством опера- 20

шифратор кодрв операции, из которых основными являются операции чтения записи. Функции запоминающих устройств ограничены исключительно хра нением информации в запоминающей ср де.

Блок 84 сравнения является распространенным функциональным элемен том, который представляет собой адресный дешифратор с усеченным число выходов, в данном случае одним. Бло сравнения может быть выполнен разли ными способами. В частности, блок сравнения устройств 2 и 8- ввода-вы вода, устройств прямого доступа мож быть выполнен на основе одноразрядн го постоянного запоминающего устрой ства, адресные входы которого соеди няются с адресными шинами информаци онно-управляющей магистрали. До начала применения логическая единица заносится аппаратно (путем прожига плавк их перемычек в постоянном запоминающем устройстве) только в те ячейки, которые соответствуют адресу, вьзделенному для данного устройства. При этом логическая единица н выходе блока 84 сравнения имеет мес то только при совпадении адреса, за 40 фиксированного аппаратным путем, с адресом, пришедшим по информационно управляющей магистрали 14.

.ijpiH, инициированной ранее процессо- IJIOM, или об обнаружении ошибки в про 1|;ессе операции.

Принцип связи между устройствами фистемы - асинхронный, что позволяет Участйовать в обмене устройствами 1{ азличного быстродействия. Однако, не занимать единственную маги- фтраль надолго, Кс1ждое устройство iJLMeeT не менее одного буферного ре- ij HCTpa 86 данных для быстрого приема и выдачи данных,

В ЭВМ с магистральной структурой правление устройствами выполняется ф помощью адресуемых регистров уст- $| ойства, отдельные разряды которых йсуществляют требуемые оцерации управления. Эти регистры входят в сос- 1 ав местного устройства 87 управле- фия, которое осуществляет выбор одного из регистров устройства, производит запись или считьшанйе информации в буферные регистры 86, а также инициирует ту или иную операцию в исполнительном механизме (периферий- ный аппарат).

Устройства прямого доступа в память, кроме указанных операций, могут запрашивать магистраль для обмена информацией с оперативной памятью 1гши любым другим устройством без помощи-- процессора. Эти устройства способны функционировать в режиме за- датчика, т.е. имеют возможность уп-, равлять этим обменом самостоятельно Эти функции осуществляются устройст вом 88 управления задатчика.

Блоки оперативных запоминаюпщх устройств, кроме указанных функцио

14

нальньЕС частей, содержат запоминающую среду, состоящую из взаимосвязанных запоминакшщх элементов.

Уровень детализации функциональных частей блоков 7j, , за исключением блока 84 сравнения, соответствует уровню стандартных функциональных элементов и не требует дальнейшей конкретизации. Местное устройство 87

-jt-, - «.M.uA « «А J - Л JJЛ л.

управления здесь вьфождается в де0

5

0

5

5

шифратор кодрв операции, из которых основными являются операции чтения и записи. Функции запоминающих устройств ограничены исключительно хранением информации в запоминающей среде.

Блок 84 сравнения является распространенным функциональным элементом, который представляет собой адресный дешифратор с усеченным числом выходов, в данном случае одним. Блок сравнения может быть выполнен различными способами. В частности, блок сравнения устройств 2 и 8- ввода-вывода, устройств прямого доступа может быть выполнен на основе одноразрядного постоянного запоминающего устройства, адресные входы которого соединяются с адресными шинами информационно-управляющей магистрали. До начала применения логическая единица заносится аппаратно (путем прожига плавк их перемычек в постоянном запоминающем устройстве) только в те ячейки, которые соответствуют адресу, вьзделенному для данного устройства. При этом логическая единица на выходе блока 84 сравнения имеет место только при совпадении адреса, за- 0 фиксированного аппаратным путем, с адресом, пришедшим по информационно- управляющей магистрали 14.

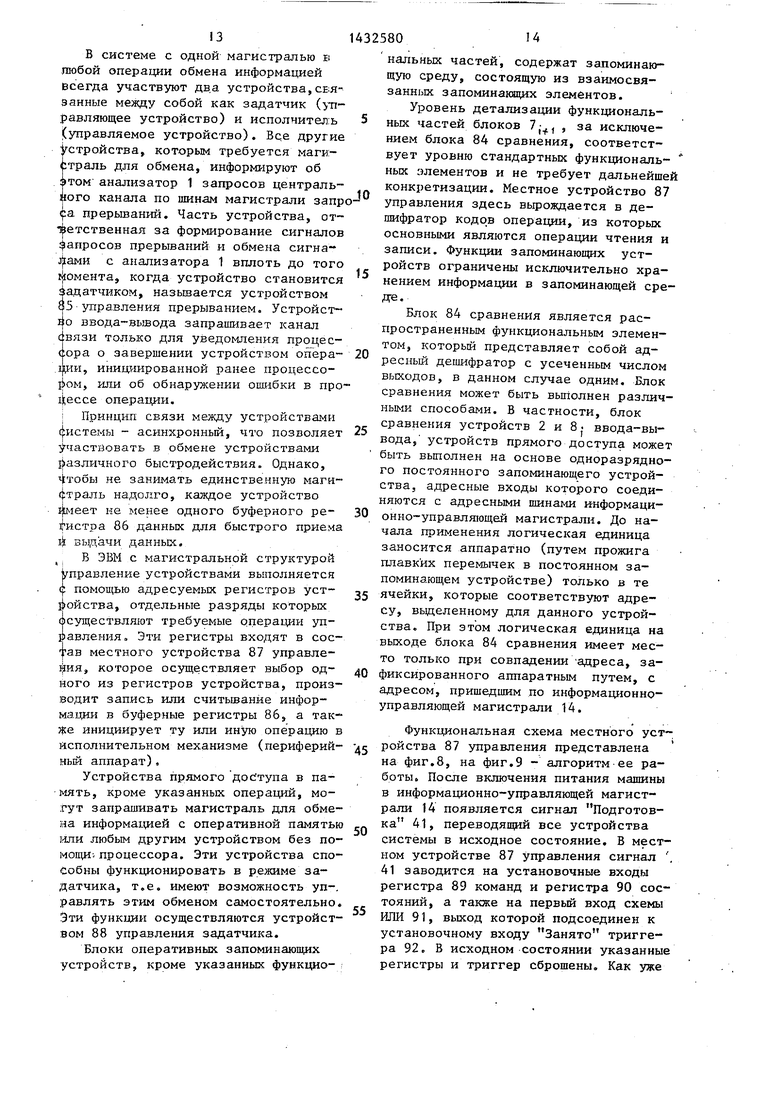

Функциональная схема местного устройства 87 управления представлена на фиг.8, на фиг.9 - алгоритм ее работы. После включения питания машины в информационно-управляющей магистрали 14 появляется сигнал Подготовка 41, переводящий все устройства системы в исходное состояние. В местном устройстве 87 управления сигнал , 41 заводится на установочные входы регистра 89 команд и регистра 90 состояний, а также на первый вход схемы ИЛИ 91, выход которой подсоединен к установочному входу Занято триггера 92. В исходном состоянии указанные регистры и триггер сброшены. Как уже

отмечалось, в системе управление работой устройств ввода-вьгоода осуществляется с помощью адресуемых регистров, в данном случае регистра 89. Установка в логическую единицу отдель ных битов этого регистра возбуждает ту ил и иную операцию в устройстве. Такими операциями могут быть: перемока ленты, установка головки в исходное состояние, возврат каретки и другие, специфические для каждого устройства операции. Ряд битов имеет универсальное значение для всех устройств системы, например бит разрешения прерывания, бит запуска операции чтения (выводы информации из данного устройства), бит запуска операции записи и дро

.Рассмотрим операцию записи информации в устройство ввода-вывода, которая представляет собой запись требуемой информации в буферньш регистр 93 и установку бита запуска операции Запись в регистре 89. Доступ к указанным регистрам может быть разрешен при совпадении логических единиц на входах элемента И 94. Пер- вьш вход схемы И 94 соединен с выходом блока 84 сравнения, второй вход с .сигналом синхронизации задатчика 48 в магистрали 14, а третий - с выходом Q триггера 92. Если устройство свободно, адрес на магистрали 14 совпал с адресом устройства (старшие значения разряда адресных шин) и пришел управляющий сигнал от задатчика, на выходе схемы И 94 появляется высокий уровень. Последний поступает на управляющие входы дешифратора 95 регистра и дешифратора 96 кода операции. Первьй производит декодирование младших значащих разрядов адресных ишн 37 и выбор одного из регистров устройства, а второй - декодирование операции, затребован- ной задатчиком и определяемой шиной 97 управления в магистрали 14. В рассматриваемом случае выход В дешифратора 95 соответствует регистру 93, а выход В - регистру 89. Анало- гично выход БД дешифратора 96 соответствует операции Запись, а выход В - операции Чтение. При организации записи в регистр 93 на выходах BQ дешифраторов 95 и 96 появляются высокие уровнр и, как следствие, - на выходе элемента И 98. С выхода элемента И 98 высокий уровень поступает на адресный вход АО мультиплек

o

5

0

5

50 5 Q

0

сора 99 и на вход элемента 100 задержки. Мультиплексор 99 настраивается на прием с магистрали 14 и передает состояние шин 101 данных на вход буферного регистра 93. Через некоторое время, отрабатываемое элементом 100 и достаточное для установки достоверной информации на информационных входах регистра 93, высокий уровень передается через элемент ИЛИ 102 и производит запись информации в регистр 93 по динамическому управляющему входу. Сигналы с выходов регистра

93поступаю на соответствующие первые входы элементов И 103, а также

в периферийный аппарат 104. Аналогично производится запись в регистр 89 при формировании высокого уровня на выходе элемента И -105.

Сигналы с выходов Q , регистра 89 поступают в периферийный аппарат 106 и возбуждают специфичную для каж,цого устройства операцию, затребованную задатчиком. Сигнал с выхода элемента

94возбуждает элемент 107 задержки, время срабатывания которого выбирается с учетом максимального времени выполнения операции чтения 1ши записи, после истечения которого низкий уровень поступает на шину СХИ 43 магистрали 14 и через элемент НЕ 108 на управляющий вход триггера 92,. что вызывает переход устройства в состояние Занято (установка 92). В ответ на сигнал 40 задатчик сбрасьшает сигнал СХЗ 39, которьй вызывает сброс сигнала СХИ 40. Сбросом сигнала 40 заканчивается обмен информацией между задатчиком и ис полнителем по магистрали 14. Установка триггера 92 вызывает блокировку устройства, т.е. запрещаются повторные обращения к устройству вплоть до тех пор, пока устройство не выполнит операцию, затребованную задатчиком. Результат вьшол- нения операции 109 заносится периферийным аппаратом в регистр 90 по сигналу 110 и устройство переходит в состояние Свободно - сброс триггера 92 по сигналу 111.

Возможны следующие результаты вы- прлнения операции - устройство успешно завершило операцию, устройство не может вьшолнить операцию (не подключен носитель информации, на периферийном аппарате нет питания и т.д.) или в процессе выполнения операции была обнаружена ошибка. О результате вьтолнения операции задатчик мо171432580

узнать двояким образом. Можно произвести операцию чтения состояния регистра 90 посредством элементов И 112 и 113, после того как устройство перейдет в состояние Свободно. 5 |Второй способ заключается в исполь- |3овании механизма прерывания, Состо- яния бита разрешения прерывания операции 109 и битов завершения опера- ии 114 анализируются устройством 85 10 управления прерьюанием. Считьшание «{СОСТОЯНИЯ буферного регистра 90 про- Изводится посредством элементов 115 103, запись в него информации 109

18

системы, подключейные к данному уровню приоритета.

Этот сигнал, поступая на вход первого устройства 2 или 9, подвергается анализу и в случае требования устройством обслуживания ему дается право пользоваться ресурсами системы (рассматриваемьй случай), в противном случае сигнал разрешения пре- рьшания поступает на продолжение центральной магистрали разрешения прерывания (выход элемента 125).

Анализатор 1 запросов в ответ на сигнал ПВБ 46 сбрасьшает сигнал на

ри инициативе периферийного аппара- 15 магистрали 16. Элемент И 127 отслежи25

30

35

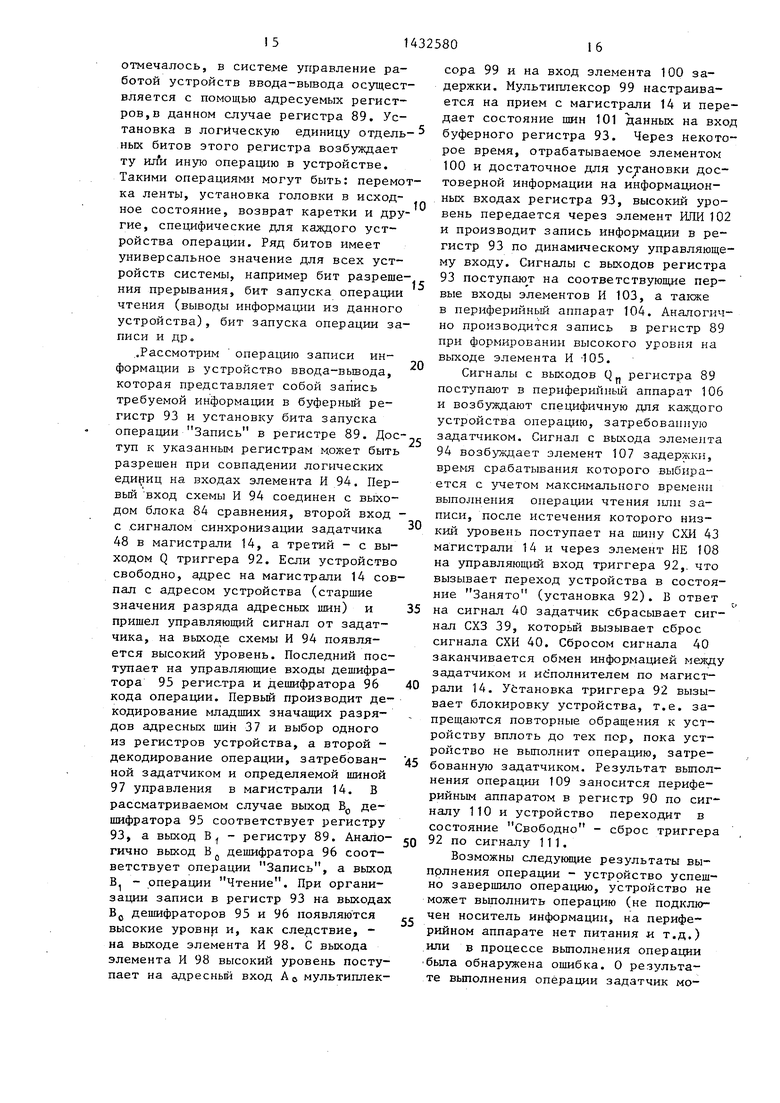

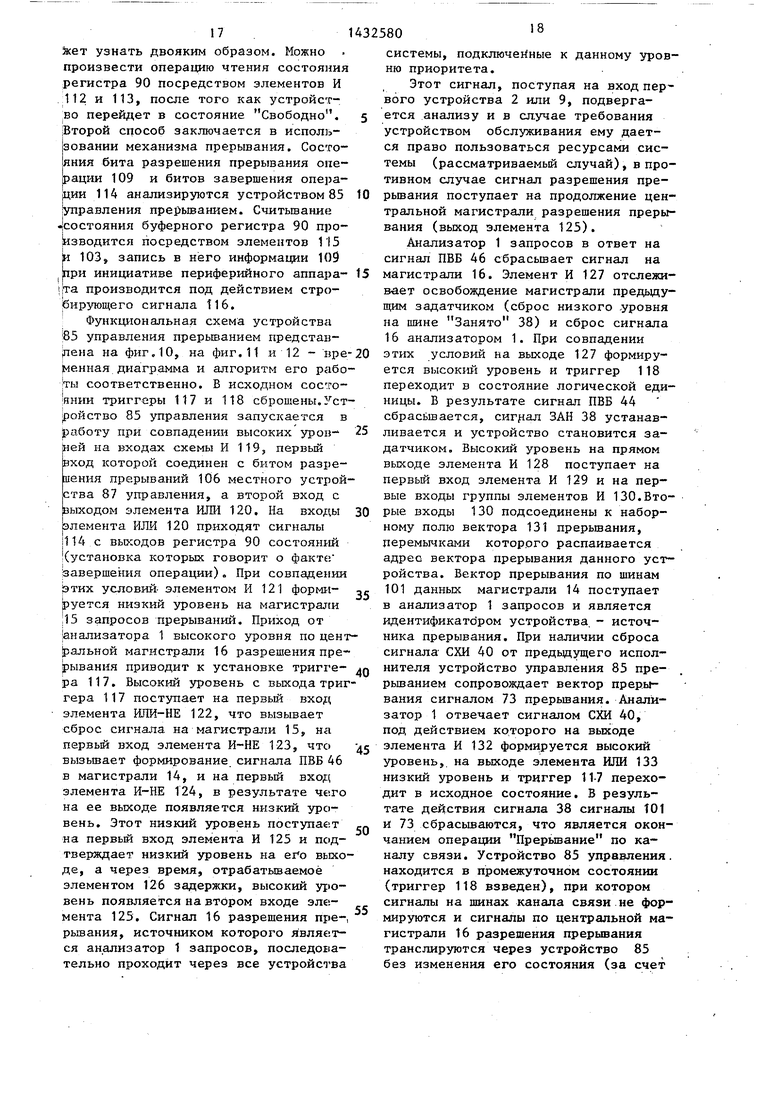

ihfa производится под действием стро- бирующего сигнала Т16. ; Функциональная схема устройства в5 управления прерьгоанием предстан- |пена на фиг, 10, на фиг. 11 и 12 - вре-20 (менная диаграмма и алгоритм его рабо- |ты соответственно. В исходном состоянии триггеры 117 и 118 сброшены. З ст- ройство 85 управления запускается в работу при совпадении высоких урон- ней на входах схемы И 119, первый вход которой соединен с битом разрешения прерываний 106 местного устрой ства 87 управления, а второй вход с выходом элемента ИЛИ 120. На входы Элемента ИЛИ 120 приходят сигналы 1114 с вькодов регистра 90 состояний Кустановка которых говорит о фактег Завершения операции). При совпадении ртих условий- элементом И 121 форми- руется низкий уровень на магистралей ;15 запросов прерываний. Приход от анализатора 1 высокого уровня по цент- ральной магистрали 16 разрешения пре- рывания приводит к установке тригге- Q pa 117. Высокий уровень с выхода триггера 117 поступает на первьй вход элемента ИЛй-НЕ 122, что вызывает сброс сигна,па на магистрали 15, на первьй вход элемента И-НЕ 123, что вызьшает формирование сигнала ПВБ 46 в магистрали 14, и на первый вход элемента И-НЕ 124, в результате че.го на ее выходе появляется низкий уровень. Этот низкий уровень поступает на первый вход элемента И 125 и пс1Д- тверждает низкий уровень на еГо выходе, а через время, отрабатываемое элементом 126 задержки, высокий угю- вень появляется на втором входе эле;- мента 125. Сигнал 16 разрешения пре-, рьшания, источником которого является анализатор 1 запросов, последовательно проходит через все устройства

45

50

55

освобождение магистрали предьзду- щим задатчиком (сброс низкого уровня на шине Занято 38) и сброс сигнала 16 анализатором 1. При совпадении этих условий на выходе 127 формируется высокий уровень и триггер 118 переходит в состояние логической единицы. В результате сигнал ПВБ 44 сбрасьшается, ЗАН 38 устанавливается и устройство становится задатчиком. Высокий уровень на прямом выходе элемента И 128 поступает на первый вход элемента И 129 и на первые входы группы элементов И 130.Вторые входы 130 подсоединены к наборному полю вектора 131 прерьшания, перемычками которого распаивается адрес вектора прерывания данного устройства. Вектор прерывания по шинам 101 данных магистрали 14 поступает в анализатор 1 запросов и является идентификатором устройства, - источника прерывания. При наличии сброса сигнала СХИ 40 от предьщущего исполнителя устройство управления 85 пре- рьшанием сопровождает вектор прерывания сигналом 73 прерьшания. Анализатор 1 отвечает сигналом СХИ 40, под действием которого на выходе элемента И 132 формируется высокий уровень,, на выходе элемента ИЛИ 133 низкий уровень и триггер 11-7 переходит в исходное состояние. В результате действия сигнала 38 сигналы tOt и 73 сбрасываются, что является окончанием операции Прерьтанке по каналу связи. Устройство 85 управления. находится в промежуточном состоянии (триггер 118 взведен), при котором сигналы на шинах канала связи не формируются и сигналы по центральной магистрали 16 разрешения прерьшания транслируются через устройство 85 без изменения его состояния (за счет

18

системы, подключейные к данному уровню приоритета.

Этот сигнал, поступая на вход первого устройства 2 или 9, подвергается анализу и в случае требования устройством обслуживания ему дается право пользоваться ресурсами системы (рассматриваемьй случай), в противном случае сигнал разрешения пре- рьшания поступает на продолжение центральной магистрали разрешения прерывания (выход элемента 125).

Анализатор 1 запросов в ответ на сигнал ПВБ 46 сбрасьшает сигнал на

5

0

5

0 Q 5

0

5

освобождение магистрали предьзду- щим задатчиком (сброс низкого уровня на шине Занято 38) и сброс сигнала 16 анализатором 1. При совпадении этих условий на выходе 127 формируется высокий уровень и триггер 118 переходит в состояние логической единицы. В результате сигнал ПВБ 44 сбрасьшается, ЗАН 38 устанавливается и устройство становится задатчиком. Высокий уровень на прямом выходе элемента И 128 поступает на первый вход элемента И 129 и на первые входы группы элементов И 130.Вторые входы 130 подсоединены к наборному полю вектора 131 прерьшания, перемычками которого распаивается адрес вектора прерывания данного устройства. Вектор прерывания по шинам 101 данных магистрали 14 поступает в анализатор 1 запросов и является идентификатором устройства, - источника прерывания. При наличии сброса сигнала СХИ 40 от предьщущего исполнителя устройство управления 85 пре- рьшанием сопровождает вектор прерывания сигналом 73 прерьшания. Анализатор 1 отвечает сигналом СХИ 40, под действием которого на выходе элемента И 132 формируется высокий уровень,, на выходе элемента ИЛИ 133 низкий уровень и триггер 11-7 переходит в исходное состояние. В результате действия сигнала 38 сигналы tOt и 73 сбрасываются, что является окончанием операции Прерьтанке по каналу связи. Устройство 85 управления. находится в промежуточном состоянии (триггер 118 взведен), при котором сигналы на шинах канала связи не формируются и сигналы по центральной магистрали 16 разрешения прерьшания транслируются через устройство 85 без изменения его состояния (за счет

элемента И 134). Перевод устройства 85 в исходное состояние может быть произведен только после сброса либо одного из сигналов 106, либо 114, т.е. или запрета разрешения прерывания, или после устранения причины прерьгвания.

Устройство 85 управления прерьша- нием (УУП) функционально можно раз- бить на две части. Первая часть отрабатывает процедуру получения права использовать ресурсы системы (т.е., процедуру становления устройством задатчиком на магистрали), а вторая часть отрабатывает собственно процедуру операции Прерывание. Устройство 85 управления прерьшанием устройств 9 прямого доступа в память полностью включают УУП 85 устройств ввода-вывода 2 или 8 плюс дополнительно его первую часть, которая подключается не на уровень запроса прерывания (магистрали 15 и 16), а на

уровень прямого доступа (шины 62 и

66). Запуск этой части схемы производится при установке в логическую единицу двух дополнительных битов - битй разрешения передачи по прямому доступу в регистре 89 и бита готовности передачи по прямому доступу в регистре 90 местного устройства 87 управления. Прямой выход 135 элемента 128 в данном случае используется не для инициации операции прерьша- ния, а поступает в устройство 88 уп- равления задающим устройством (УУЗУ) и запускает его в работу.

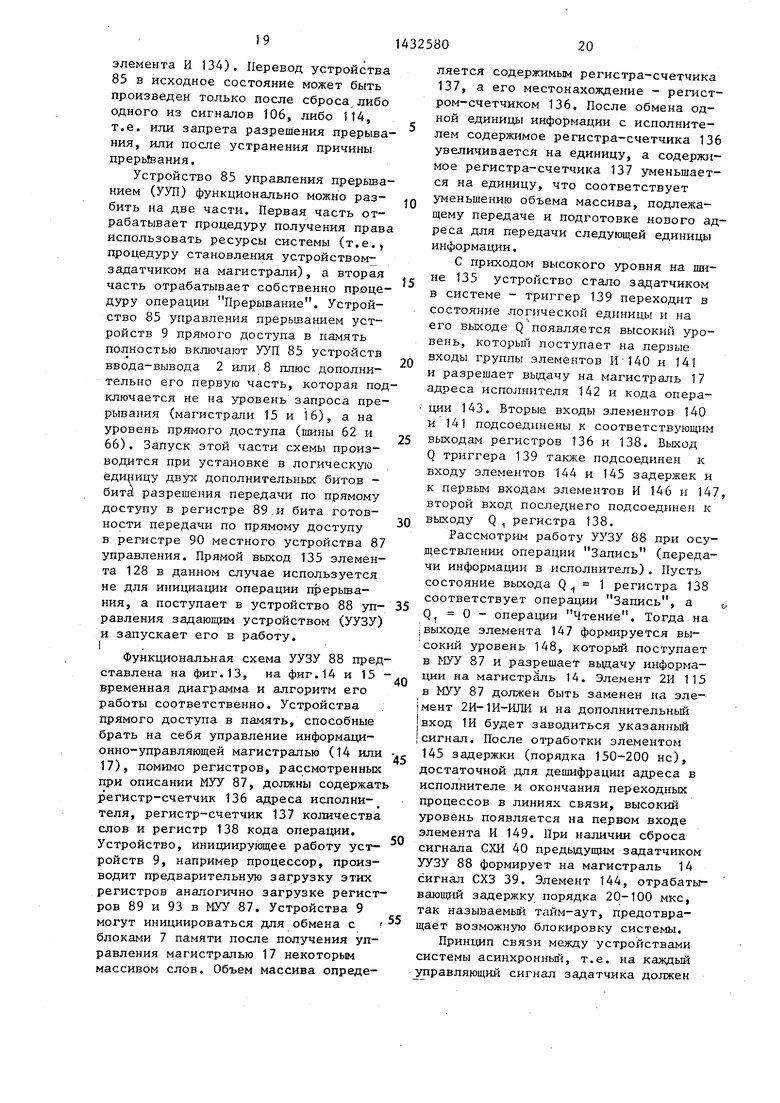

Функциональная схема УУЗУ 88 представлена на фиг.13, на фиг.14 и 15 временная диаграмма и алгоритм его работы соответственно. Устройства прямого доступа в память, способные брать на себя управление информационно-управляющей магистралью (14 или 17), помимо регистров, рассмотренных при описании МУУ 87, должны содержать регистр-счетчик 136 адреса исполни- теля, регистр-счетчик 137 количества слов и регистр 138 кода операции. Устройство, инициирующее работу устройств 9, например процессор, производит предварительную загрузку этих регистров аналогично загрузке регистров 89 и 93 в МУУ 87. Устройства 9 могут инициироваться для обмена с блоками 7 памяти после получения управления магистралью 17 некоторым массивом слов. Объем массива опреде

5

0

5

5

0

ляется содержимым регистра-счетчика 137, а его местонахождение - регистром-счетчиком 136. После обмена одной единицы информации с исполнителем содержимое регистра-счетчика 136 увеличивается на единицу, а содержимое регистра-счетчика 137 уменьшается на единицу, что соответствует уменьшению объема массива, подлежащему передаче и подготовке нового адреса для передачи следующей единицы информации.

С приходом высокого уровня на mi- He 135 устройство стало задатчиком в системе - триггер 139 переходит в состояние логической единицы и на его выходе Q появляется высокий уровень, которьш поступает на первые входы группы элементов И 140 и 141 и разрешает выдачу на магистраль 17 адреса исполнителя 142 и кода опера- ции 143. Вторые входы элементов 140 и 141 подсоединены к соответствующим выходам регистров 136 и 138. Выход Q триггера 139 также подсоединен к входу элементов 144 и 145 задержек и к первым входам элементов И 146 и 147, второй вход последнего подсоединен к выходу Q регистра 138.

Рассмотрим работу УУЗУ 88 при осуществлении операции Запись (передачи информации в исполнитель). Пусть состояние выхода Q. 1 регистра 138 соответствует операции Запись, а с. Q, О - операции Чтение. Тогда на jвыходе элемента 147 формируется вы- сокий уровень 148, которьй поступает в МУУ 87 и разрешает вьщачу информации на магистраль 14. Элемент 2И 115 в МУУ 87 должен быть заменен на эле- мент 2И-1И-ИЛИ и на дополнительный вход Ш будет заводиться указанньй сигнал. После отработки элементом 145 задержки (порядка 150-200 не), достаточной для дешифрации адреса в исполнителе и окончания переходных процессов в линиях связи, высокий уровень появляется на первом входе элемента И 149. При наличии сброса сигнала СХИ 40 предыдущим задатчиком УУЗУ 88 формирует на магистраль 14 сигнал СХЗ 39. Элемент 144, отрабатывающий задержку порядка 20-100 мкс, так называемьй тайм-аут, предотвращает возможную блокировку системы.

Принцип связи между устройствами системы асинхронный, т.е. на каждый управляющий сигнал задатчика должен

21

прийти ответный управляюицад сигнал от исполнителя (в данном случае сигналы 39 и 40 соответственно). При неисправиости в исполнителе или шинах связи ответньш сигнал вообще не прдцет. Если в задатчике не будет предусмотрена подобная ситуация, то система блокируется и для возобновления ее ра:боты потребуется вмешательство оператора. Подобную блокировку устраняет элемент I44 и триггер 150, Если ответный сигнал 40 не пройдет в УУЗУ 88 до истечения тайм- аута, триггер 150 переходит в состояние логической единицы, дальнейшая работа блокируется (низкий уровень па третьем входе элемента 146), о чем уведомляется УУП 85. Еспи бит разрешения прерывания в регистре 90 установлен, устройство, используя механизм прерывания, уведомит процессор о возникшей ошибке и после запрещения последним прямого доступа (низкий уровень сигнала 135) схема переходит в исходное состояние. При правильной работе исполнителя приход сигнала СХИ 40 вызывает сброс сигнала СХЗ 39, установку триггера 151 и через задержку, отрабатываемую элемент.ом 152, сброс триггера 139, что вызывает сброс всех сигналов на магистрат 14. Сброс триггера 139вы зьшает установку триггера 153., вихбц Q которого заходит на вход прямого счета счетчика 136, на вход обратно

го счета счетчика 137 и з качестве сигнала 154 заходит в периферийньш аппарат для сигнализации последнем о вьшолненной операции. Через время отрабатьшаемое элементом 155, триг- гер 153 сбрасьшается и схема готова к передаче следующего элемента инфомации. Если переданный, элемент был последним на выходе антипереполнени Р (т.е., обнуления), формируется ло гическая единица, которая также приводит в действие механизм прерьшани

Работа схемы при выполнении за- датчиком операции чтения аналогична Однако вместо сигнала 148 вьщача да ных формируется сигнал Прием данны 156,-которьй поступает в МУУ 87 на дополнительньй вход элемента 98 (см приведенную замену .элемента 115FCx

ме 87) и приводит к записи информации вход элемента 161 противоположного

в регистр 93.

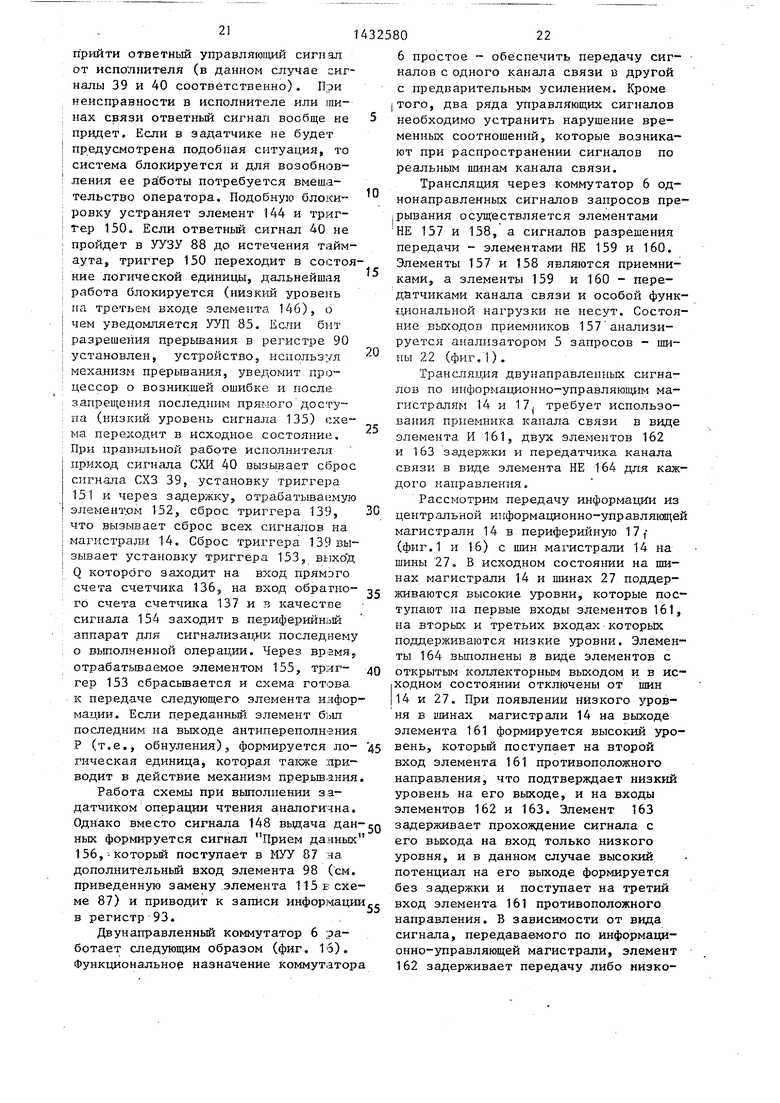

Двунаправленный коммутатор 6 работает следующим образом (фиг. 16), Функциональное назначение коммутатора

направления. В зависимости от вида сигнала, передаваемого по информаци онно-управляющей магистрали, элемен 162 задерживает передачу либо низко

80

22

6 простое обеспечить передачу сигналов с одного канала связи в другой с предварительным усилением. Кроме того, два ряда управляющих сигналов необходимо устранить нарушение временных соотношений, которые возникают при распространении сигналов по реальным цгинам канала связи.

Трансляция через коммутатор 6 однонаправленных сигналов запросов прерывания осуществляется элементами НЕ 157 и 158, а сигналов разрешения передачи - элементами НЕ 159 и 160. Элементы 157 и 158 являются приемниками, а элементы 159 и 160 - передатчиками канала связи и особой функциональной нагрузки не несут. Состояние вьЕХодов приемников 157 анализируется анализатором 5 запросов - шины 22 (фиг,1).

Трансляидя двунаправленных сигналов по информационно-управляющим магистралям 14 и 17. требует использо5

5

G

О 45

сп

приемни.ка канала связи в виде элемента И 161, двух элементов 162 и 163 задержки и передатчика канала связи в виде элемента НЕ 164 для каждого направления.

Рассмотрим передачу информации из центральной информационно-управлящей магистрали 14 в периферийную 17,- (фиг.1 и 16) с шин магистрали 14 на шины 27. В исходном состоянии на шинах магистрали 14 и шинах 27 поддерживаются высокие уровни, которые поступают на первые входы элементов 161, на вторых и третьих входах которь1х поддерживаются низкие уровни. Элементы 164 выполнены в виде элементов с открытым коллекторным выходом и в ис- гходном состоянии отключены от шин

|14 и 27. При появлении низкого уровня в шинах магистрали 14 на выходе элемента 161 формируется высокий уровень, который поступает на второй вход элемента 161 противоположного направления, что подтверждает низкий уровень на его выходе, и на входы элементов 162 и 163. Элемент 163 задерживает прохождение сигнала с его выхода на вход только низкого уровня, и в данном случае высокий потенциал на его выходе формируется без задержки и поступает на третий

вход элемента 161 противоположного

направления. В зависимости от вида сигнала, передаваемого по информационно-управляющей магистрали, элемент 162 задерживает передачу либо низко

го уровня, либо высокого. Например, трансляция сигналов СХЗ и СХИ требует задержки высокого уровня, а трансляция адреса, данных и линий управления - низкого. Пройдя через эле мент 162, высокий уровень поступает на вмод элемента 164, на выходе которого формируется низкий уровень. Так происходит передача низкого уровня с шин магистрали 14 на шины 27.

При передаче шин магистрали 14 в состояние высокого потенциала на втором входе элемента 161 противоположного направления без задержки формируется низкий уровень, на шинах 27 высокий уровень появляется с задержкой, отрабатываемой элементом 162 и вносимой элементом 164. На выходе элемента 163 низкий уровень должен появиться только после гарантированного появления высокого уровня на шинах 27. Из этих условий выбирается величина задержки, отрабатываемая элементом 163. При отсутствии эле- ментов 163 и связи выхода элемента 161 одного направления с входом элемента 161 другого направления комму- татбр 6 перейдет в режим блокировки при передаче низкого уровня. В этом случае элементы 164 обоих направле- НИИ будут поддерживать низкие уровни и нормальная работа системы будет нарушена. При наличии обратной связи между приемниками 161 двух направлений, но при отсутствии элементов 163 возникает генерация в коммутаторе 6 и, следовательно, в шинах 14 и 27 при снятии низкого уровня в шинах магистрали 14. Таким образом, схема коммутатора (фиг. 16) содержит мини- мальное количество функциональных элементов и функциональных связей между ними, необходимых для его правильной работы.

Блоки 4 и 10 элементов запрета центрального и периферийных каналов, представляют собой совокупность отдельных элементов запрета, являгацих- ся стандартными функциональными элементами. Количество элементов запре- та в каждом блоке 4 и 10 равно числу шин в информационно-управляннцих магистралях 14 или 17. Информационные ; входы элементов запрета подсоединены к шинам информационно-управляющих ма

гистралей, выходы - к узлам трансляции отдельных сигналов в коммутаторе 6 и к входам блока 13, а управляющие входы подсоединены к шинам 23 и

10

15

20

35 40

45 0

5

24. соответственно. При наличии низкого уровня на этих входах через блоки 4 и 10 запрещена передача сигналов, а следовательно, и логическая связь между информационно-управляющими магистралями 14 и 17.

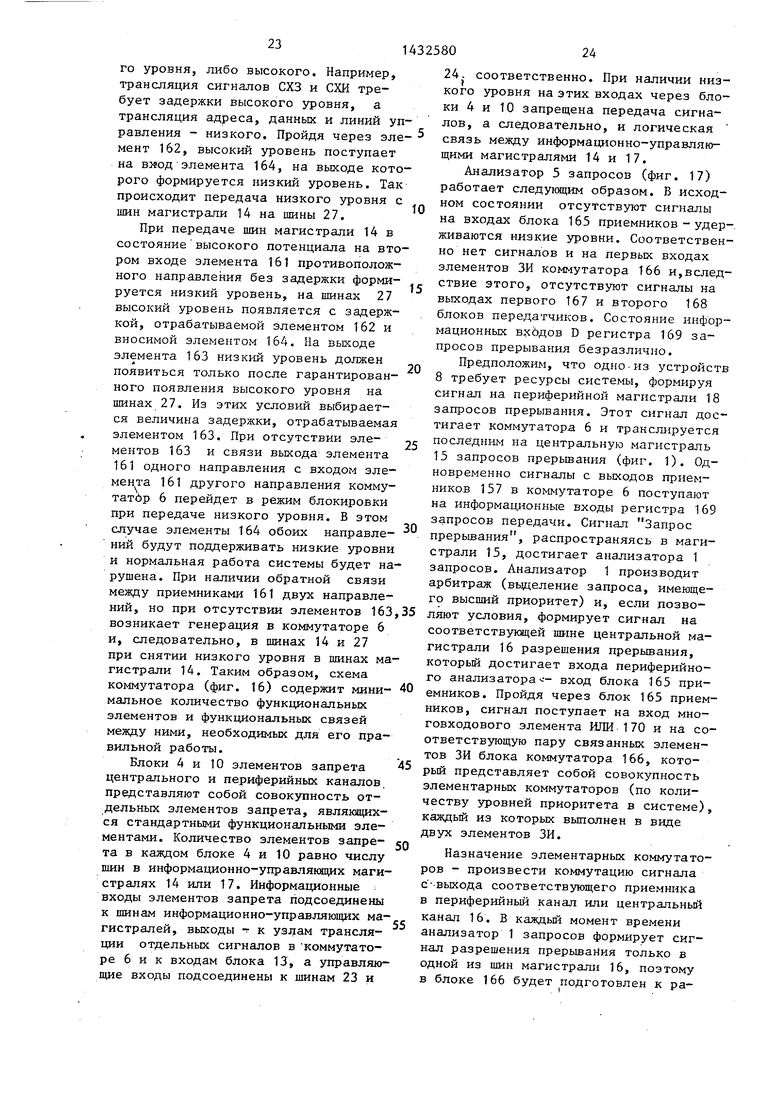

Анализатор 5 запросов (фиг. 17) работает следукщим образом. Б исходном состоянии отсутствуют сигналы на входах блока 165 приемников - удерживаются низкие уровни. Соответственно нет сигналов и на первых входах элементов ЗИ коммутатора 166 и,вследствие этого, отсутствуют сигналы на выходах первого 167 и второго 168 блоков передатчиков. Состояние информационных вхбдов D регистра 169 запросов прерывания безразлично.

Предположим, что одно-из устройств 8 требует ресурсы системы, формируя сигнал на периферийной магистрали 18 запросов прерывания. Этот сигнал достигает коммутатора 6 и транслируется последним на центральную магистраль 15 запросов прерьшания (фиг. 1). Одновременно сигналы с выходов приемников 157 в кoм yтaтope 6 поступают на информационные входы регистра 169 запросов передачи. Сигнал Запрос прерьшания, распространяясь в магистрали 15, достигает анализатора 1 запросов. Анализатор 1 производит арбитраж (вьщеление запроса, имеющего высший приоритет) и, если позволяют условия, формирует сигнал на соответствующей шине центральной магистрали 16 разрешения прерьшания, которьй достигает входа периферийного анализатора -- вход блока 165 приемников. Пройдя через блок 165 приемников, сигнал поступает на вход мно- говходового элемента ИЛИ 170 и на соответствующую пару связанных элементов ЗИ блока коммутатора 166, который представляет собой совокупность элементарных коммутаторов (по количеству уровней приоритета в системе), каждьй из которых вьтолнен в виде двух элементов ЗИ.

Назначение элементарных коммутаторов - произвести коммутацию сигнала с --выхода соответствующего приемника в периферийньш канал или центральньй канал 16. В каждый момент времени анализатор 1 запросов формирует сигнал разрешения прерывания только в одной из шин магистрали 16, поэтому в блоке 166 будет подготовлен к ра(5оте только один из элементарных коммутаторов. Высокий уровень с выхода элемента Ш1И 170 поступает на вхоц Элемента 171 задержки и производит апись информации в регистр 1С9, Через некоторое время, отрабатываемое элементом 171, на общем входе элемен ( арных коммутаторов блока 166 появ- л 1Явтся высокий уровень, разрешающий фнализ выходов Q и Q того триггера, оторьй связан с входами ранее подготовленного элементарного коммута- фора. Если этот триггер установлен состояние логической единицы, то игнал Разрешение прерьшания про- юдит через второй блок передатчиков 68 и затем транслируется через ком- .ryтaтopы 6 и 11 на периферийную ма- Истраль 20 разрешения прерьшания. I Таким образом, анализатор 5 за- ijipocoB запретил дальнейшее распро- (транение сигнала в центральной ма- истрали 16 разрешения прерывания и произвел его трансля1цно в периферий- йую магистраль 20 . разрешения преры ания.

I Допустим, что источникам сигнала тЗапрос прерывания, поступившего в Диализатор t запросов, является од- , из устройств ввода-вьшода, под- атченных после анализатора 5 в центральном канале. В этом случае к мо-; liieHTy записи в регистр 169 запросов йередачи на его соответствующем информационном входе сохранится уро- ень логического нуля (отсутствие Сигнала Запрос передачи). Поэтому :оответствунщий триггер установится в состояние логического нуля и в случае сигнал Разрешение пре- рьшания пройдет иа соответствующую йину выходной магистрали первого блока 167 передатчиков. В результате анализатор 5 осуществил трансляцию сигнала разрешения прерьшания к еле- дующему устройству ввода-вывода в Последовательной цепи. Число линий в соответствукяцих шинах анализатора. 5, разрядность регистра 169 1запросов Прерывания, число приемников, пере- датч1иков и элементарных коммутаторов в блоках 165, 167 или t68 и 166 соответственно равно числу уровней приоритетов в системе.

На фиг. 3 приведена функхщональна схема коммутатора 11 сигналов разрешений прерьюания, который в функцко- иальном плане идентичен анализатор У 5 запросов прерываний периферийные:

0

5

0

5

0 5 0 5 0

каналов. Действительно, назначение анализатора 5 состоит в трансляции входного сигнала с центральной магистрали 16 либо на пр одолжение этой же магистрали, либо в периферийную магистраль 20 в соответствии с состоянием магистрали 18 запросов прерываний периферийных каналов. Назначение коммутатора 11 состоит в трансляции входного сигнала с магистрали 20 разрешений.прерывания периферийных каналов в один из периферийных каналов 20,- в соответствии с состоянием шин магистрали 18(.

Коммутатор -11 работает следующим образом. В исходном состоянии коммутатором 6 поддерживаются низкие уровни в шинах 20, что определяет низкие, уровни сигналов в шинах магистрали 20,- и на выходе элементов И 55 - отсутствие блокировки блока 3. Состояние регистров 49 безразлично. С приходом высокого уровня по одной из шин 20 анализатором 5, а следовательно, и коммутатором 6 гарантируется появление высокого уровня только на одной шине 20 - на выходе элемента 50 также появляется высокий уровень. Последний вызьшает фиксацию состояний шин магистралей 18,- в группе регистров 49 и запускает элемент 53 задержки, время отработки которого больше или равно формированию достоверной информации на выходе блока 55 выбора приоритетного запроса. Состояние шин 20 определяет настройку мультиплексора 51 на анализ тех выходов регистров 49, которые соответствуют уровню поступившего с шины 20 разрешения прерьшания, и определяет выбор блока элементов И в группе 52, соответствующего данному приоритетному уровню. Состояние регистров 49 через мультиплексор 51 передается на вход блока 55. В результате на одном из выходов 44 блока формируется низкий уровень, соответствующий наиболее приоритетному запросу в шинах магистрали 18 к моменту прихода высокого уровня в шинах 20. Низкий уровень на одном из выходов блоке 55 обязательно будет иметь место, поскольку приход высокого уровня в шинах 20 есть результат наличия соот- ветствунщего запроса хотя бы в одном из периферийных каналов 18-. При отработке элемента 53 на соответствующем выходе группы элементов И t ин

вареными входами 56 появляется высокий уровень.57, который по шинам 28 взаимоблокировки поступает в блок 3. Одновременно -запускается элемент 54 задержки на время окончания переходных процессов в блоке 3. После истечения этого времени разрешается анализ только одному подготовленному элементу И в группе 52. Когда посту- пает сигнал 21- разрешения (высокий уровень), высокий уровень формируется на выходе этого элемента. При снятии высокого, уровня в шинах 20 коммутатор 11 возвращается в исходное состояние.

Рассмотрим работу блока 3 реконфигурации системы, функциональная схема которого приведена на фиг.2, а временная диaгpa шa и алгоритм работы соответственно на фиг. 18 и ,19. Целесообразно рассмотреть его работу одновременно с работой арбитра 36 реконфигураций, функциональна я схема которого приведена на фиг. 20. Исходное состояние схемы с точки зрения выходных сигналов обеспечиваетс соо7 ветству ощим состоянием входных шин (см. описание системы по фиг.1) и фактом прихода сигнала ПОДГ 41. .. Назначение блока 3 состоит в своевременном восстановлении и запрете логических связей (трансляция сигналов) между центральным и периферийными каналами и проведение арбит- ража по запросам прямого доступа. В исходном состоянии трансляция сигналов между каналами запрещена. Блок реконфигурации, анализируя сигналы в шинах магистралей 14 и 17 , должен определить ситуацию необходимости обмена между каналами, отработать процедуру восстановления связи между ними и после окончания обмена - процедуру запрещения связи.

Блок 29 сравнения предназначен для определения факта обращения одного из устройств центрального канала в зону адреса одного из периферийных каналов. Блок 29 сравнения выполнен на основе п-разрядного постоянного запоминающего устро.йства, адресные входы которого соединены с адресными шинами 37 информационно- управляющей магистрали 14. Система имеет сквозную адресацию всех регистров устройств и ячеек оперативной памяти. Блок имеет 2 (п равно числу адресных шин в системе) ячеек.

, ю j

0 5 0 Q 5

0

5

каждая из которых имеет п разрядов, определяемое числом периферийных каналов, используемых в системе. Каж- дьй разряд всех 2 ячеек памяти служит для хранения информации о составе устройств периферийного канала. Логическая единица в разряд заносится аппаратно (путем прожигания плавких перемычек только в те ячейки, которым соответствуют устройства в периферийном канале).

Рассмотрим процесс обращения одного из устройств центрального канала к одному из устройств периферийного канала, например первого. Этому процессу предшествует процесс выбора (арбитража) задатчика из ряда устройств, которым требуется канал связи и который завершается установкой низкого уровня сигнала Занято 38 устройством-победителем. В результате на выходе элемента 32 появляется высокий уровень и регистру 30 разрешается прием информации. Задат- чик устанавливает в шинах магистрали 14 адрес 37 исполнителя. По данному адресу в блоке 29 была занесена логическая единица, поэтому на ее выходе появляется высокий уровень, которьш поступает на вход DO регистра 30.. Через некоторое время задатчик сопровождает адрес устройства низким уровнем управляющего сигнала 39 - синхронизации задатчика СХЗ. На выходе первого элемента НЕ 31 появляется высо- кий уровень, которьй запускает элемент 33 задержки. Через время, отра- батьшаемое элементом 33 и достаточное для подготовки достоверной информации, на входе регистра 30 производит- .ся запись в него - высокий уровень на его динамическом входе С. В рассматриваемом случае логическая единица будет записана в первьй разряд - высокий уровень Q1.

Выход Q1 регистра 30 соединен с выходом 47 выборки арбитра 36., реконфигурации. Если задатчик в периферийной магистрали 17, освобод11п ее, сбросив сигнал Занято 42, исполнитель освободил ее информационную часть - сбросил сигнал СХИ 43, не подготовлен новьй задатчик - высокий уровень сигнала ПВБ 44 и npQi.iino некоторое время, отрабатываемое элементом 172 задержки отсутствия сигнала ПВБ 44, то па выходе первого элемента И 173 формируется низкий

Зфовень,, Этот низкий уровень поступает на первьй вход второго элем(2н- та И 174, что запрещает выбор следующего задатчика на магистрали 17, и через первый элемент ИЛИ 175 - на выход элемента 176 задержки. После отработки элементом 176 времени, необходимого для завершения возможных переходных процессов,на первом входе элемента И 177 появляется высокий уровень, которьй разрешает анализ его второго входа. Если выбор задатчика на м агистрали удалось запретить, то на втором входе элемента 177 удерживается .высокий уровень.,что вызывает перевод триггера 178 в (;ос- тояние логической единицы. В резуль- : тате в соответствующей шине 24 разрешений периферийных каналов появляется высокий уровень, который,прой- ,ця через элемент ЖШ 34, появляется и в шине. 23 запрета. Высокие уровни i;inn 23 и 24 разрешают трансляций) сигналов блоки 4 и 10, и ло- ; гическая связь между центральной 14 : н периферийной 17 магистралями востаиавливается. После сброса задс1т- ; чика сигнала СХЗ 39 логическая связь между магистралями разрьшается под действием низкого уровня на выход:;е элемента РИШ 179 и после сброса сигнала 3AIi 38 схема возвращается и исходное состояние.

Восстановление логической связ-и меясду рассматриваемыми магистраля:ми возможно при вьшолнении операции I Прерьшание одним из устройств пе ;риферийной магистрали 17, Приход низкого уровня сигнала ПРЕР 45 вь.- зывает снятие низкого уровня на входе R триггера 178 и установку высокого уровня на выходе элемента НЕ 180. Элемент И 181 отслеживает освобождение магис1Т5али 14 задатчиком сброс сигнала ЗАН 38, исполнителем - сброс сигнала СХИ 40. При освобождении магистрали 14 на выходе элемента 181 формируется низкий уровень, который вызывает установку триггера 178 и восстановление логической связи между магистралями 14 и 17, (по анал:о- гии с процедурой, описанной выше). После сброса задатчиком сигнала 45 схема возвращается в исходное состояние.

Рассмотрена только одна из функций арбитра 36,.реконфигурации - установление и.запрет логической связи

5

0

5

0

5

0

5

0

5

между магистралями 14 и 17 , Его дру- .гая функция заключается в инициации арбитраяса среди устройств прямого доступа магистрали 17 , т.е. вьтол- нение части функций анализатора запросов центрального канала. Предположим, чтр устройство 9, запрашивает доступ к магистрали 17 - низкий уровень шин 19-,,.под действием которых элемент НЕ 182 формирует высокий уровень на первом входе элемента И 174. При отсутствии обращения со стороны центрального канала - высокий уровень на выходе элемента 173, отсутствие сигналов разрешения прерыва- н ия для рассматриваемого периферийного канала - низкий уровень шины 57 в шинах 28 взаимоблокировки, при.наличии высокого уровня на выходе 172 элементом 174 формируется высокий уро вень на входе С триггера 183. На входе D триггера 183 постоянно поддерживается высокий уровень, поэтому он переходит в состояние логической единицы, что и определяет вьвдачу сигнала разрешения в шину 21 . Низкий уровень выхода Q блокирует возможные обращения со стороны магистрали 14, а высокий уровень Q 21, поступает в шины 28, что запрещает возможную трансляцию сигнала разрешения прерывания коммутатором 11 в шину 20.

Устройство 9 на высокий уровень в шине 21 т отвечает низким уровнем сигнала ПВБ 44 в магистрали 17. В результате элементом ИЛИ 185 формируется низкий уровень на входе Rтриггера 183 и схема переходит в исходное состояние. Триггер 184, анали руя выход Q триггера 183, определяет необходимость передачи сигнала 44. из магистрали. 17, в магистраль 14. Если текущий задатчик в магистрали 17, выполняет передачу на уровне прямого доступа (состояние логической единицы триггера 183), то триггер 184 не изменяет своего состояния. Если же имеет место операция Прерывание, то триггер 184 взводится (высокий уровень на выходе элемента 186 задержки) и через элемент 35 передает высокий уровень выхода вьщачи ПВБ 48 в магистраль 14. Сброс сигнала 44, переводит схемы в исходное состояние .

Кроме того, еще одну особенность имеет арбитр 36 реконфигурации.

Низкий уровень сигнала ПОДГ 41 в магистрали 14 должен быть передан во все периферийные каналы 17.. Это требование вьшолняется подключением входа S триггера 178 к-шине 41, что обеспечивает появление высокого уровня -на выходах Q триггера 178 всех арбитров реконфигурации на время действия сигнала 41. Снятие сигнала 41 в магистрали 14 сопровождается сбросом триггеров 178 в арбитрах 36 и запрещением обмена между магистралями 1 4 и 1 7 ,.,

На фиг.21 представлена функциональная схема устройства управления многопортового блока ОЗУ, npHHuiin работы которого во многом идентичен . принципу работы любого устройства 2

или 8 с добавлением функций арбитража между несколькими портами и соответствующей коммутирующей аппаратуры. Состояние старших разрядов адресных шин периферийных магистралей ,- и центральной магистрали 14 анализируется соответственно блоками 187- и 187. сравнения. Эти блоки сравнения аналогичны блокам 29 в- блоке .3 реконфигурации. Выходы этих блоков соединены с соответствующими первыми входами элементов И 188 -188;., вторые входы которых соединены с шинами СХЗ периферийных 39 и централь- , ного 39 каналов соответственно. Высокий уровень на выходе одного из элементов 188 имеет место при обращении к данному блоку ОЗУ 7j одного из устройств соответствующего канала. Выходы элементов 188 соединены с вхоами D регистра 189 обращений и с вхоами элемента ИЛИ 190. С приходом одного или нескольких входных высоких уровней на выходе элемента 190 появяется высокий уровень, что вызьшает иксацию состояния выходов элемента 188.1 в регистр 189 и запуск элеента 191 задержки. Приоритетный блок 192 осуществляет вйбрр наиболее приоритетного запроса (аналогично блоку 60 в анализаторе 1) и производит настройку мультиплексоров адреса 193, управления 194, входных данных 195 демультиплексоров сигнала СХИ 196 выходных данных 197 на канал, выгравший арбитраж. Мультиплексор 193

адреса производит передачу младших : разрядов адреса выигравшего канала в местное устройство 87 управления (в соответствии с фиг.8) и запоминаю0

5

0

5

0

5

0

5

0

5

щую среду 198 по шинам 37. Мультиплексор 194 передает состояние шин управления, определяюцих тип затребованной операции по шинам 97 в МУУ 87 и на вход усеченного дешифратора 199 операции, назначение которого состоит в определении направления передачи - чтение или запись - и разрешении работы либо мультиплексора 195, либо демультиплексора 197 (вход управления). В исходном состоянии разрешена работа мультиплексора 195, что уменьшает время переходных процессов. После вьщержки времени элементом 191 высокий уровень поступает в демультиплексор 197 и МУУ 87, что инициирует в последнем выполнение затребованной операции. Устройство 87 осуществляет обмен информацией с запоминающей средой 198 аналогично обмену устройства 87 с пери- . ферийным аппаратом. При завершении операции устройство 87 вырабатывает сигнал СХИ 40, которьй передается де- мультиплексором 196 в магистраль 17 . При выполнении операции чтения этот сигнал сопровождает данные 101 от МУУ 87, которые элементом 197 передаются в магистраль 17 - сигнал 101 . За- датчик на получение сигнала СХИ отвечает снятием сигнала СХЗ, и схема возвращается в исходное состояние. Предлагаемая система управления по сравнению с известной характери зуется более высоким быстродействием, Кроме того, в предлагаемой системе снимаются логические ограничения на компоновку системы при организации одновременной работы каналов, увеличивается надежность подсистем прерывания и прямого доступа в связи с их децентрализацией и заменой характера распространения однонаправленных сиг 1алов разрешений прерывания и прямого доступа между периферийными каналами с последовательного на па- раплельный, а также увеличивается уровень отказоустойчивости за счет локализации неисправности только в пределах отказавшего канала.

Формула изобретения

1. Многоканальная система управления распределением ресурсов в вычислительном комплексе, содержащая в центральном канале анализатор запросов, группу блоков ввода-вывода.

33

блок элементов запрета, анализатор запросов периферийных каналов и дву- иаправленньй коммутатор, а в каждом периферш1ном канале - группу блоков ввода-вьюода, блок прямого доступа к памяти и соответствующий блок элементов запрета группы блоков элемен- го в запрета, в центральном канале входы-вьэсоды группы входов-выходов I анализатора запросовj входы-выходы I группы входов-выходов каяодого блока I ввода-вывода группы и входы-выхо;,ы первой группы входов-выходов блока элементов запрета объединены и псд клгочены к соответствующим шинам дент ральной информационно-управляющей ма |гистрали, выходы первой группы вь:хо- дов двунаправленного коммутатора, выходы первой группь выходов ка:ждого 1 блока ввода-вьшода группы объединены I и через соответствуюя1ие ШП1Ы цент- Гральной магистрали запросов прерыва- пия подключены к входам группы вхо- дов анализатора запросов, вькоды :1 ру.гшы выходов которого подключены к ;входам группы входов первого блока I ввода-вывода группы, выходы второй I группы выходов кансдого-предыдущего : блока ввода-вывода подключены к вхо- |дам группы входов каждого последую- ;щего блока ввода-вывода группы, вы- ходь второй группы выходов последнего блока ввода-вывода группы через соответствующие шины центральной ма- :гистрали разрешений прерываний под- включены к входам анализатора запро- |сов периферийных каналов, входы-:зы- |ходы которого и входы-выходы первой I группы входов-выходов двунаправлен- :ного коммутатора объединены соответ- :ственно„ входы-выходы вторых групл входов-выходов блока элементов запрета и двунаправленного коммутатора ; объединены соответственно,, в каждом периферийном канале входы группы входов блока прямого доступа к памяти являются входами, соответствующ;ях: тин соответствующей периферийной магистрали разрешения прерьшания, входы-выходы групп входов-выходов блока прямого доступа к памяти, каждого блока ввода-вывода группы и соответствующего блока элементов запрета группы объединены через соответст- . вующие пины соответствующей периферийной информадионно-управлякяцей гистрали, выходы первых групп выходов блока прямого доступа к памяти и каждого блока ввода-вьшода группы

10

ts

20

25

43258034

объединены через соответствующие шины соответствующей периферийной магистрали запросов прерьгеания, выходы второй группы выходов блока прямого доступа к памяти подключены к входам группы входов первого блока ввода-вьшода группы, выходы второй группы выходов каждого предьщущего блока ввода-вьшода группы подключены к входам группы входов каждого последующего блока ввода-вывода группы, отличающаяся тем, что, с целью повьшения производительности системы, в нее введены в дент- ральньй канал группа многопортовых блоков памяти и блок реконфигурации, первьй и второй блоки элементов ИЛИ, коммутатор сигналов разрешений прерывания, входы-вькоды первой группы входов-выходов блока реконфигурации подключены к соответствующим иинам центральной информационно-управляющей магистрали, входы-выходы второй группы входов-выходов блока реконфигурации подключены к входам-выходам группы входов-выходов коммутатора сигналов разрешения прерьшания, входы всех групп входов, кроме последней, блока реконфигураи;ии подключены к соответствующим шинам соответствующих периферийных информационно-управляющих магистралей,каж- дьй выход первой группы выходов блока реконфигурацш подключен к первым входам элементов запрета соответствующих блоков элементов запрета группы блоков элементов .запрета периферийных каналов, каждьй выход второй группы выходов блока реконфигурации подключен к вход соответствующего блока прямого доступа к памяти через соответствующую шину разрешения прямого доступа к памяти, выход каждого блока прямого доступа к памяти подключен к соответствующему входу последней группы входов блока реконфигурации через соответствующую шину запросов прямого доступа к памяти, выход блока реконфигурации подключен к входу блока элементов запрета центрального канала, входы-выходы первых групп каждого многопортового . блока памяти группы объединены и подключены к соответствуюпщм шинам центральной информационно-управляющей магистрали, входы-выходы остальных групп каждого многопортового блока памяти группы подключены к соответствующим шинам соответствующих пери30

35

40

45

50

55

35

ферийных информационно-управляющих магистралей, выходы второй группы выходов двунаправленного коммутатора подключены к входам первой группы входов коммутатора сигналов разрешений прерьшаний, входы каждой группы входов первого блока элементов ИЛИ и входы остальных групп коммутатора сигналов разрешений прерьшаний объединены соответственно и подключены к соответствующим шинам соответствующих периферийных магистралей запросо прерываний, выходы первого блока элементов ИЛИ подключены к входам группы входов двунаправленного коммутато ра, выходы каждой группы выходов коммутатора сигналов разрешений прерываний подключены к соответствующим шинам соответствующих периферийных магистралей разрешений прерываний, выходы группы выходов каждого блока элементов запрета группы подключены к входам соответствующих групп входов второго блока элементов ИЛИ, выходы которого подключены к входа:- - выходам третьей группы.входов-выходов двунаправленного коммутатора, каждый вход-выход которой подключен к вторым входам элементов запрета соответствующего блока элементов за пр ета группы блоков элементов запрет периферийных каналов.

2. Система управления по п. 1, отличающаяся тем, что, блок реконфигурации содержит блок сравнения, регистр, первый и второй элементы НЕ, элемент задержки, пер- вьй и второй элементы ИЛИ и арбитры реконфигурации, входы блока сравнения, входы первого и второго элементов НЕ, первые, вторые, третьи и четвертые входы арбитров реконфигурации являются соответствующими входами первой группы входов-выходов блока реконфигурации, выходы блока срав- нения подключены к входам группы входов регистра, каждый выход которого подключен к входу выборки каждого арбитра реконфигурации, выход первого элемента НЕ через элемент задержки подключен к первому входу регистра, выход второго элемента НЕ подключен к второму входу регистра, выхода запрета арбитров реконфигурации подключены к входам первого элемента ИЛИ и являются соответствующими выходами первой группы выходов блока реконфигурации, выходы выборки арбитров реконфигурации подключены к входам

10

15

20

25

в30

45143258036