Изобретение относится к радиоизмерительной технике, в частности к устройствам демодуляции фазомоду- / лированных сигналов, девиация фазы которых не превыгаает 21Г, а спектр закона фазовой модуляции узкополосный.

Цель изобретения - повьшение точности детектирования и увеличение соотношения сигнал-шум на выходе детектора.

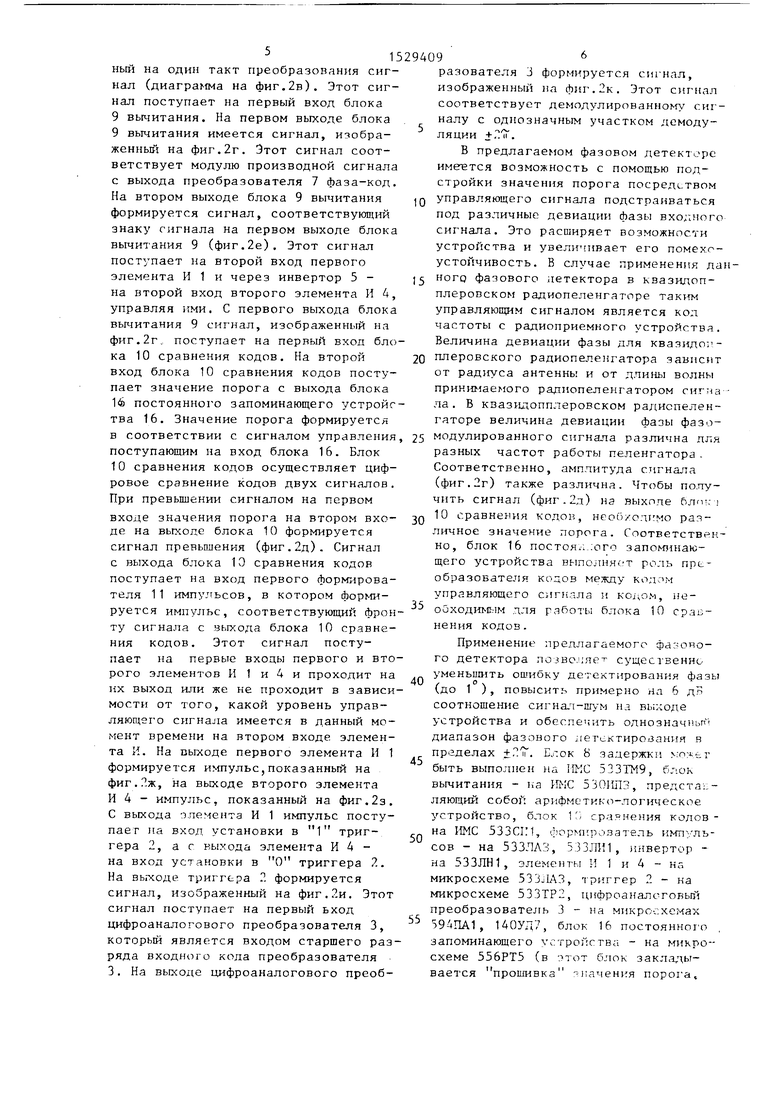

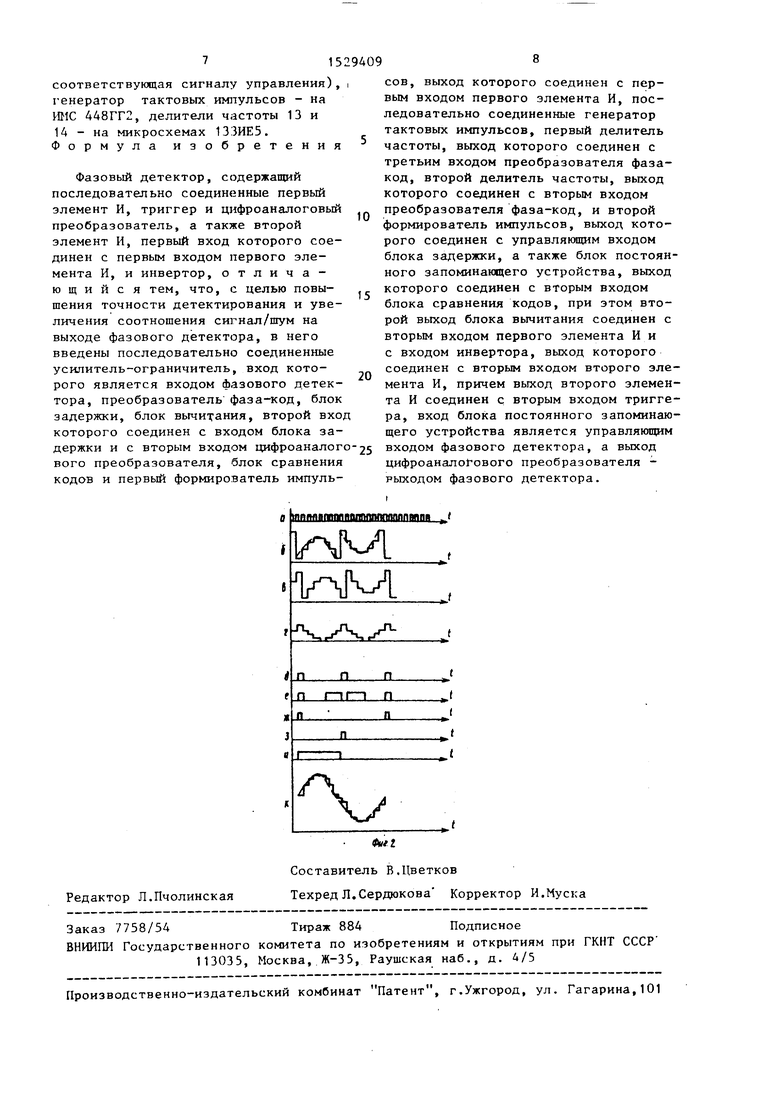

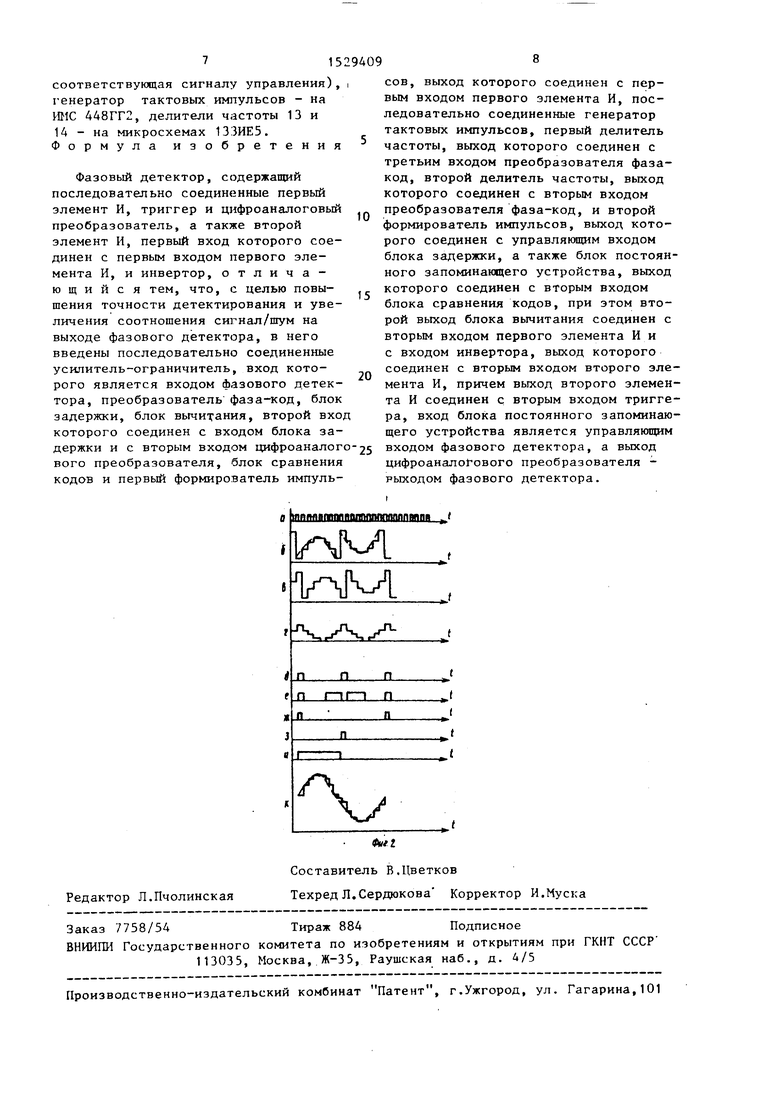

На фиг.1 приведена функциональная электрическая схема предлагаемого фазового детектора; на фиг.2 - временные диаграммы, поясняющие работу фазового детектора.

Фазовый детектор содержит первый элемент И 1, триггер 2, цифроанало- говьй преобразователь 3, второй элемент И 4, инвертор 5, усилитель-ограничитель 6, преобразователь 7 фаза- код, блок 8 задержки, блок 9 вычитания, блок 10 сравнения кодов, первый формирователь 11 импульсов, генератор 12 тактовых импульсов, первый 13 и второй 14 делители частоты, второй формирователь 15 импульсов и блок 16 постоянного запоминающего устройства.

Фазовый детектор работает следующим образом.

Фазомодулированный сигнал с частотой fg, имеющий фазовую модуляцию с синусоидальной огибающей, поступает на вход усилителя-ограничителя 6. Усилитель-ограничитель 6 преобразует входной синусоидальньй сигнал частоты fp в сигнал прямоугольной формы той же частоты, имеющий ту же фазовую модуляцию. Поскольку во входном сигнале вместе с входным синусоидальным сигна лом присутствует флуктуируклцая помеха и шум, нельзя применять высокбчувст- вительный входной формирователь, например компаратор напряжения, который искажает фронты и спады прямоугольного сигнала, внося большую ошибку в значение измеряемой фазы или же вообще может сделать устройство неработоспособным.

Прямоугольный сигнал с выхода усилителя-ограничителя 6 поступает на первый вход двухполупериодного -преобразователя 7 фаза-код. На второй вход преобразователя 7 фаза-код поступает опорное напряжение с выхода второго делителя 14 частоты (фиг.2а). Относительно этого сигнала осуществляется фазовая демодуляция. На третий

5

0

5

0

5

0

5

0

5

вход преобразователя 7 фаза-код поступают счетные импульсы с выхода первого делителя 13 частоты. Преобразователь 7 фаза-код преобразует фазовые сдвиги ФМ-сигнала в цифровой код. На выходе преобразователя 7 фаза-код получают значение фазового сдвига в цифровом коде. Усилитель-ограничитель 6 вносит в преобразуемый фазовый сдвиг ошибку, которая к тому же имеет температурную нестабильность. Если при формировании выходного сигнала по фронту ошибка преобразования имеет знак +, то при формировании по спаду она имеет знак -. Осуществляя формирование выходного сигнала одновременно по фронту и по спаду, а затем складывая полученные значения и деля их на 2, можно уменьшить ошибку, вносимую усилителем-ограничителем 6, в чем и заключается работа двухпо- лупериодного преобразователя 7 фаза- код. Частота счетных импульсов, поступающих с выхода первого делителя 13 частоты, определяет дискретность измерения фазы сигнала. Двухполупе- риодный преобразователь 7 фаза-код обеспечивает линейное преобразование ФМ-сигнала в цифровой код, пропорциональный фазе сигнала в динамическом диапазоне от О до 21 относительно опорного напряжения, поступающего с выхода второго делителя 14 частоты. В качестве такого преобразователя может быть использовано известное устройство. Диаграмма на фиг.26 соответствует продетектиро- ванному закону фазовой модуляции входного сигнала с синусоидальной огибающей в диапаз оне ±2 If. Выпуклая часть диаграммы соответствует про- детектированным положительным сдвигам фазы, вогнутая часть - продетек- тированным отрицательным сдвигам фазы.

Цифровой сигнал с выхода преобразователя 7 фаза-код поступает на первый вход блока 8 задержки на один интервал преобразования, на второй вход блока 9 вычитания и на второй вход цифроаналогового преобразователя 3. Блок 8 задержки выполняется в цифровом виде, например в виде регистра сдвига на один такт. Управление задержкой производится импульсами, поступающими с выхода второго формирователя 15 импульсов. На выходе блока задержки присутствует задержанный на один такт преобразования сигнал (диаграмма на фиг.2в). Этот сигнал поступает на первый вход блока 9 вычитания. На первом выходе блока

9вьиитания имеется сигнал, изображенный на фиг.2г. Этот сигнал соответствует модулю производной сигнала с выхода преобразователя 7 фаза-код. На втором выходе блока 9 вычитания формируется сигнал, соответствующий знаку сигнала на первом выходе блока вычитания 9 (фиг.2е). Этот сигнал поступает на второй вход первого элемента И 1 и через инвертор 5 на второй вход второго элемента И 4, управляя ими. С первого выхода блока вычитания 9 сигнал, изображенный на фиг.2г,, поступает на первый вход блока 10 сравнения кодов. На второй вход блока 10 сравнения кодов поступает значение порога с выхода блока 16 постоянного запоминающего устройства 16. Значение порога формируется в соответствии с сигналом управления поступающим на вход блока 16. Блок

10сравнения кодов осуществляет цифровое сравнение кодов двух сигналов. При превышении сигналом на первом

входе значения порога на втором входе на выходе блока 10 формируется сигнал превьпления (фиг.2д). Сигнал с выхода блока 10 сравнения кодов поступает на вход первого формирователя 11 импульсов, в котором формируется импульс, соответствующий фронту сигнала с выхода блока 10 сравнения кодов. Этот сигнал поступает на первые входы первого и второго элементов И 1 и 4 и проходит на их выход или же не проходит в зависимости от того, какой уровень управляющего сигнала имеется в данный момент времени на втором входе элемента И. На выходе первого элемента И 1 формируется импульс,показанный на фиг..ж, на выходе второго элемента И 4 - импульс, показанный на фиг.2з. С выхода элемента И 1 импульс поступает па вход установки в 1 триггера 2, ас выхода элемента И 4 - на вход установки в О триггера .. На выходе триггера 2 формируется сигнал, изображенный на фиг.2и. Этот сигнал поступает на первый вход цифроаналогового преобразователя 3, которьй является входом старшего разряда входного кода преобразователя 3. На выходе цифроаналогового преоб

0

5

0

5

0

5

0

5

разователя 3 формируется сигнал, изображенный на фиг.2к. Этот сигнал соответствует демодулированноьгу сигналу с однозначным участком демодуляции + .1 и .

В предлагаемом фазовом детекторе имеется возможность с помощью подстройки значения порога посредством управляющего сигнала подстраиваться под различные девиации фазы входного сигнала. Это расширяет возможности устройства и увеличивает его помехоустойчивость. В случае применения данного фазового детектора в квазидоп- плеровском радиопеленгаторе таким управляющим сигналом является кол частоты с радиоприемного устройства. Величина девиации фазы для квазидо;т- плеровского радиопеленгатора зависит от рад1гуса антенны и от длины волны принт1аемого радиопеленгатором сигнала. В квазидопплеровском радиопеленгаторе величина девиации фазы фазо- модулированного сигнала различна для разных частот работы пеленгатора . Соответственно, амплитуда сигнала (фиг.Зг) также различна. Чтобы получить сигнал (фиг.2д) на выходе блп;,-; 10 сравне 1ия кодов, необ/олг мо различное значение порога. Соответственно, блок 16 постоя. запож1наю- щего устройства выполнж-т роль преобразователя кодов между колсп-i управляющего сигнала н ко;;,ом, ие- оаход1-1М1;1М для работы блока 10 сравнения кодов.

Применение предлагаемого фазояо- го детектора позволяет- существенно уменьшить ошибку детектирования фазы (до 1 ), повысить примерно на 6 до соотнощение сигнал-шум нл выходе устройства и обеспечить однознач ньп т диапазон фазового легектирования в пределах +.. Блок 8 задержки .г быть выполнен на iffiC 533ТМ9, блок вычитания - на ИМС 5301ШЗ, представляющий собой арифметико-логическое устройство, блок 1 Г; сраянения кодов- на IWC 533Ci:i, формирователь импульсов - на 533ЛЛЗ, 533ЛИ1, инвертор - на 533ЛН1, элементы И 1 и 4 - на микросхеме 533J1A3, триггер 2 - на микросхеме 533ТР2, цифроаналсговьй преобразователь 3 - на микросхемах 594ПА1 , 140УД7, блок 16 постоянног о , запоминающего устройства - на микро-схеме 556РТ5 (в этот блок закла; ьг- вается прошивка г :11ачения порога.

715

соответствующая сигналу управления), генератор тактовых импульсов - на Ш1С А48ГГ2, делители частоты 13 и 14 - на микросхемах 13 ЗИЕ5. Формула изобретения

Фазовый детектор, содержащий последовательно соединенные первый элемент И, триггер и цифроаналоговый преобразователь, а также второй элемент И, первый вход которого соединен с первым входом первого элемента И, и инвертор, отличающийся тем, что, с целью повышения точности детектирования и увеличения соотношения сигнал/шум на выходе фазового детектора, в него введены последовательно соединенные усилитель-ограничитель, вход которого является входом фазового детектора, преобразователь фаза-код, блок задержки, блок вычитания, второй вхо которого соединен с входом блока задержки и с вторым входом цифроаналог вого преобразователя, блок сравнения кодов и первый формирователь импуль

5

0

5

сов, выход которого соединен с первым входом первого элемента И, последовательно соединенные генератор тактовых импульсов, первый делитель частоты, выход которого соединен с третьим входом преобразователя фаза- код, второй делитель частоты, выход которого соединен с вторым входом преобразователя фаза-код, и второй формирователь импульсов, выход которого соединен с управлянлцим входом блока задержки, а также блок постоянного запоминающего устройства, выход которого соединен с вторым входом блока сравнения кодов, при этом второй выход блока вычитания соединен с вторым входом первого элемента И и с входом инвертора, выход которого соединен с вторым входом второго элемента И, причем выход второго элемента И соединен с вторым входом триггера, вход блока постоянного запоминающего устройства является управляющим входом фазового детектора, а выход цифроаналоГового преобразователя - рыходом фазового детектора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Фазовый детектор | 1986 |

|

SU1415415A1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| УСТРОЙСТВО ДЛЯ НЕПРЕРЫВНОГО СЛЕЖЕНИЯ ЗА ДЕЯТЕЛЬНОСТЬЮ СЕРДЦА И ЛЕГКИХ | 2002 |

|

RU2236169C2 |

| АНАЛИЗАТОР ПАРАМЕТРОВ СЛОЖНЫХ СИГНАЛОВ | 1977 |

|

SU1840900A1 |

| СИСТЕМА ОБНАРУЖЕНИЯ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 2003 |

|

RU2256937C1 |

| Устройство для измерения флуктуационной составляющей частоты сигналов с линейно-частотной модуляцией | 1988 |

|

SU1631456A1 |

| АДАПТИВНЫЙ ЛАЗЕРНЫЙ ДОПЛЕРОВСКИЙ ЛОКАТОР | 1990 |

|

RU2012013C1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| Устройство для измерения девиации частоты линейно-частотно-модулированного колебания | 1989 |

|

SU1709266A2 |

Изобретение относится к радиоизмерительной технике, в частности к устройствам демодуляции фазомодулированных сигналов, девиация фазы которых не превышает ±2φ, а спектр закона фазовой модуляции узкополосный. Цель изобретения - повышение точности детектирования и увеличения соотношения сигнал/шум (С/Ш) на выходе фазового детектора. Для достижения цели в детектор введены усилитель-ограничитель 6, преобразователь 7 фаза - код, блок 8 задержки, блок 9 вычитания, блок 10 сравнения кодов, два формирователя 11,15 импульсов, генератор 12 тактовых импульсов, два делителя 13,14 частоты и блок 16 постоянного запоминающего устройства. В предлагаемом детекторе имеется возможность с помощью подстройки значения порога посредством управляющего сигнала подстраиваться под различные девиации фазы входного сигнала. Это увеличивает возможности устройства и его помехоустойчивость. Применение предлагаемого детектора позволяет существенно уменьшить ошибку детектирования (до 1°), повысить примерно на 6 дБ соотношение С/Ш на выходе устройства и обеспечить однозначный диапазон фазового детектирования в пределах ±2φ. 2 ил.

0 твнявтяпвппппппптппяппи t

.

.

п

п

п ml-I п

/

| Фазовый дискриминатор | 1978 |

|

SU809482A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-12-15—Публикация

1987-11-27—Подача