ствующими связями обеспечивают исправ- по модулю два появляется уровень лол|ение одиночных ошибок при считыва-гической 1, что вызывает коррекцию

нии информации. При отсутствии всоответствующего разряда. 1 ил.,

работе преобразователя одиночных оши- табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ УГОЛ-КОД | 2013 |

|

RU2530336C1 |

| Преобразователь угол-код | 1987 |

|

SU1474843A1 |

| Преобразователь угол-код | 1987 |

|

SU1619398A1 |

| ПСЕВДОСЛУЧАЙНАЯ КОДОВАЯ ШКАЛА | 2012 |

|

RU2510572C1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| КОДОВАЯ ШКАЛА | 2014 |

|

RU2560782C1 |

| КОДОВАЯ ШКАЛА | 2012 |

|

RU2497275C1 |

| Устройство для контроля многовыходных цифровых узлов | 1988 |

|

SU1566353A1 |

| Псевдослучайная кодовая шкала | 2017 |

|

RU2660609C1 |

| Устройство декодирования модифицированного кода БЧХ | 1990 |

|

SU1791961A1 |

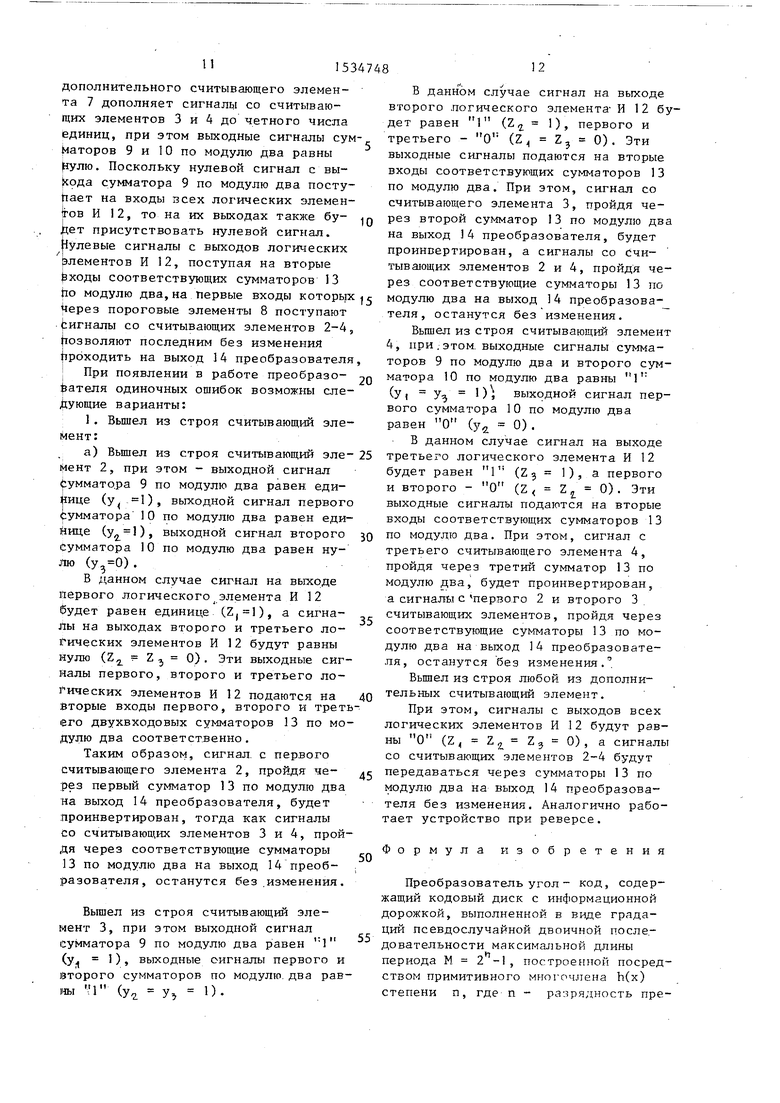

Изобретение относится к области аналого-цифрового преобразования, а именно к преобразователям угла поворота вала в код. Целью изобретения является повышение надежности преобразователя за счет исправления одиночных ошибок. Цель достигается тем, что в преобразователь угол - код, содержащий кодовый диск 1 с информационной дорожкой, выполненной в виде градаций псевдослучайной двоичной последовательности максимальной длины с периодом M = 2N-1, N считывающих элементов 2, 3 и 4, дополнительный считывающий элемент 5, сумматор 9 по модулю два, введены N-1 дополнительных считывающих элементов 6 и 7, N-1 сумматоров 10 по модулю два на три входа, N-1 элементов НЕ 11, N элементов И 12, N сумматоров 13 по модулю два на два входа, выходы которых являются выходом 14 преобразователя. Введенные элементы с соответствующими связями обеспечивают исправление одиночных ошибок при считывании информации. При отсутствии в работе преобразователя одиночных ошибок, сигналы с выходов дополнительных считывающих элементов 5, 6 и 7 дополняют сигналы с соответствующих считывающих элементов 2, 3 и 4 до четности, при этом выходные сигналы сумматоров 9 и 10 по модулю два равны нулю. В случае появления одиночной ошибки на некоторых выходах сумматоров 9 и 10 по модулю два появляется уровень логической "1", что вызывает коррекцию соответствующего разряда. 1 ил., 1 табл.

Изобретение относится к области цналого-цифрового преобразования, ii именно к преобразователям угла поборота вала в код.

Целью изобретения является повышение надежности преобразователя За счет исправления одиночных ошибок .

На чертеже показана линейная развертка кодового диска, а также Ьтруктурная схема трехразрядного преобразователя угол - код ().

Информационная дорожка кодового диска выполнена в виде псевдослучайной последовательности (двоичной) максимальной длины (ПСД ПМД) с периодом М 2п-1 .

Известно построение псевдослучайных двоичных последовательностей максимальной длины с периодом М 2 -1, а также, например, построение ПСДПМД при помощи сдвигающего регистра с сумматорами по модулю два в цепи обратной связи. В известном источнике дана таблица для , пригодная для генерирования ПСДПМД с периодом М до L

Поясняют один из вариантов реалзации информационной дорожки кодового диска на основе ПСДПМД и размещение вдоль информационной дорожки считывающих элементов и дополнительных считывающих элементов, ограничившись для простоты тремя разрядами преобразования, т.е.. Для получения ПСДПМД с периодом М 2 -1 7 необходим примитивный многочлен h(x) степени 3. Выбирают, например, многочлен h(x)x +хч-1 из таблицы 2Д возможно также использование сопряженного многочлена той же степени,

0

5

0

5

0

5

0

5

т.е. п(х)хэ+хг+1. При получении соответствующей ПСДПМД необходимо использовать трехразрядный сдвигаю- ЕЩЙ регистр с сумматором по модулю два в цепи обратной связи, где характер обратных связей определяется многочленом h(x) . В данном примере трехразрядный сдвигающий регистр будет генерировать ПСДПМД с периодом ,„. . ,0011301 . При построении информационной дорожки кодового диска ПСДПМД с периодом наносится на кодовый диск в виде активных (единицы ПСДПМД) и пассивных (нули ПСДПМД) участков информационной дорожки, например, по ходу часовой стрелки, причем на информационную дорожку кодового диска наносится только один период ПСДПМД. ПСДПМД с периодом определяет число квантов информационной дорожки кодового диска, которое в данном примере равно . Отсюда величина кванта X 360°/М 360°/7« 51,4°. Считывающие элементы должны быть размещены на информационной дорожке кодового диска с постоянным шагом, кратным величине кванта информационной дорожки.

Примем в данном примере равномерное размещение трех считывающих элементов на информационной дорожке кодового диска с шагом в два кванта, например, по ходу часовой стрелки.

При таком размещении считывающих элементов места размещения трех дополнительных считывающих элементов на информационной дорожке кодового диска определяются в соответствии со ел е дуюш ей т а бл ице и:

1 В таблице символами С1 , С2, СЗ обозначены считывающие элементы, размещенные на информационной дорожке кодового диска с шагом в два кванта п ходу часовой стрелки, а символами , СД1, СД2, СДЗ - соответственно первый, второй и третий дополнительные считывающие элементы, также размещенные на информационной дорожке. Столб- цами в таблице являются 1ТСДПМД, считываемые при полном обороте кодового диска против хода часовой стрелки с соответствующих считывающих и дополнительных считывающих элементов. ПСДПМД, считываемые с дополнительных считывающих элементов, при полном обороте кодового диска подчиняются следующим зависимостям:

С1 С1 - С2

© С2 © С2,

СЗ,

СЗ,

где

V±) - означает суммирование по

модулю два.

Для выполнения соотношения (1) первый дополнительный считывающий элемент должен быть смещен вдоль информационной дорожки кодового диск в сторону возрастания номера равномерно размещенных трех считывающих элементов С1, С2 и СЗ относительно С1 на один квант (столбцы С1 и СД1 таблицы), второй дополнительный считывающий элемент должен быть смещен вдоль информационной дорожки кодового диска в сторону возрастания номера равномерно размещенных трех считывающих элементов С1, С2, СЗ от- носительно С1 на три кванта (столбцы С1 и СД2 таблицы), третий дополнительный считывающий элемент должен быть смещен вдоль-информационной дорожки кодового диска в сторону воз растания номера равномерно размещенных трех считывающих элементов С1, С2 и СЗ относительно С2 на три кванта (столбцы С2 и СДЗ).

15347486

В n-разрядном преобразователе зависимости (1)выглядят следующим образом

СД1 С1 © С2 @ СЗ © ....

i@C(n-l) © Сп;

(2)

СД2 СДЗ

С1 © С2; С2 ©СЗ;

СД .п-О С(п-2) ©С(п-1); . СДп C(h-l) ©Cn,

)

, С2,...,С(п-1), С, СД1,СД2, .. . ,СД (п-1), СДп - ПСДПМД, считываемые с соответствующих считывающих элементов и дополнительных считывающих элементов.

Пример размещения трех считывающих в трех дополнительных считывающих элементов вдоль информационной дорожки кодового диска с использованием математических формул. Здесь h(x) « х3+х+1, , , , ,2, г(х)« 1+хг+х, (4(x) l+xk

30

х+х2+х +х о. л.

Х+Х +х

35

х+хг+х

х+хг+х

х +х

хэ+х4+х6

1 3 об х (n-l)-k+(M-l)

х 2-2 + (7-3) х-8 х

8(mod 7) 1 S 6

S х k+(M-S) х 2 +(7-6) х 3

В предложенном техническом решении обеспечивается исправление оди-. ночных ошибок. При доказательстве для простоты рассуждения ограничиваются, например, тремя разрядами преобразования, а затем обобщают полученные результаты на случай п- разрядного преобразователя.

Обозначают сигналы, снимаемые с первого, второго и третьего считывающих элементов, а также первого , второго и третьего дополнительных считывающих элементов через х, , хг xj и х1, ,х, х соответственно

1 В соответствии с (1) и принятыми обозначениями можно записать:

х, х,

хг х„

x3Qt

X

X

г;,

у (3)

хг© х,

х

При технической реализации соотношения (J3) необходимо использовать ОЈ;ин четырехвходовый сумматор по моду- лю два и два трехвходовых сумматора ncj модулю два, входными сигналами которых являются х,, х, х3, х , х2,

Х4, а ВЫХОДНЫМИ - У , Уг, У,,.

При отсутствии в работе преобра- зфвателя одиночных ошибок сигналы сiдополнительных считывающих элемен- трв дополняют сигналы с соответствующих считывающих элементов до четного числа единиц, при этом выходные сиг- налы у,, уг, уэ сумматоров по модулю два равны нулю.

В n-разрядном преобразователе зависимости (3) с соответствующими обозначениями будут выглядеть следую щим. образом:

х,

Xj. ©

h-i ®Х

, ;

У2 х{ ® хг© xj, ;

:г©х,

3 7

(4)

Уп УП

., хп.г ©х„., ©x h., ) х„, © хп © х п .

При технической реализации соотношения (.4) необходимо использавать Один (п+1) входовой сумматор по модулю два и (п-1) трехвходовых сумма- Гора по модулю два, входными сигналами которых являются сигналы с п считывающих элементов и п дополни- Кых считывающих элементов х, х, К,..,, хк, , хп, х, , х2, х,...,

Х ц-1 ХП а ВЫХОДНЫМИ - У, , У2 ,

Уп -,

При отсутствии одиночных ошибок в

работе преобразователя сигналы с

5

0

5

0

5

;

40

45

дополнительных считывающих элементов дополняют сигналы с соответствующих элементов до четного числа единиц, при этом, выходные сигналы у, у, ..., у всех сумматоров по модулю два равны нулю.

При появлении одиночных ошибок в работе преобразователя, например, при выходе из строя какого-либо считывающего элемента, нарушается суммарная четность единиц, снимаемых со считывающих элементов, и выходные сигналы у,,, У.-.-.у некоторых сумматоров по модулю два будут равны единице.

В этом случае возможны следующие варианты, рассмотренные на примере (соотношение (3)).

Вышел из строя любой считывающий элемент:

вышел из строя первый считывающий элемент, при этом

у 1-, У2 1-, Уэ 0;

вышел из строя второй считывающий элемент, при этом

V 1 V и 1 V

м J уч. ъ

вышел из строя третий считывающий элемент, при этом

у 1; Уй 0; У3 К

Учитывая изложенное, можно записать следующую систему уравнений

Z, , ,

2г У, УгУ3, .(5)

2э У,УгУз

При технической реализации соотношения (5) необходимо использовать три трехвходовых логических элемента И и два инвертора для получения инверсных сигналов Уй и у,. Входными сигналами логических элементов И являются у„ , у, уэ 7 yV, УЗ а выхо дами - Z, .

При выходе из строя одного из считывающих элементов выходной сигнал соответствующего логического элемента И будет равен единице, при этом выходные сигналы остальных логических элементов И равны нулю (5).

Далее, обозначая выходные сигналы преобразователя через , , о62 , oi 3 можно записать:

, 7

(6)

x

При выходе из строя, например, первого считывающего элемента выходной сигнал Z первого логического элемента И будет равен 1 (при этом Z4 Z3 0) и сигнал с первого считывающего элемента будет проинвер- тирован (6).

При отсутствии в работе преобразователя одиночных ошибок (четность

10

П-1 OU

СЛ 2 Oi-i Э

I

г П-1

(8)

Zn J

При технической реализации соот ношения (7) необходимо использовать

получаемых сигналов не нарушена), т.е п n-входовых логических элементов

Z3 О сигналы с первого, второго и третьего считывающих элементов без изменения проходят на выход преобразователя (6)

И и (п-1) инверторов для получения инверсных сигналов УД

При технической реализации соотношения (8) необходимо использовать п

7П

При технической реализации соотно- двухвходовых сумматоров по модулю два.

шения (6) необходимо использовать три двухвходовых сумматора по модулю два, входными сигналами для которых являются (х4, Z4), (х2, Zj), (х3, Z,),

ВЫХОДНЫМИ - Ј, , Otfc , Ofj.

Вышел из строя первый дополнительный считывающий элемент, при этом

У, 1-, у 0-, у3 О. В соответствии с (5 Z 4 Z4 в Z 0 и сигналы с первого, второго и третьего считывающих элементов беэ изменения проходят на выход преобразователя (6) .

Вышел из строя любой из дополнительных считывающих элементов, начи- ная с второго, при этом

У

0.

Z, Z,

О и

а следовательно, сигналы с первого, второго и третьего считывающих элементов без изменения проходят на выход преобразователя (5) и (6).

В n-разрядном преобразователе зависимости (5) и (6) с соответствующими обозначениями будут выглядеть следующим образом:

-У УгУъ Уп У(УаУ5У4---- УП

У У1УэУ4У5Уп j

У,УаУ3У4У5Уб-(7)

Уп5

У У2У}У4У5У6У7 ;

Zn-i

z „

П-1 OU

СЛ 2 Oi-i Э

I

г П-1

z,)

Уп-2 УП- УП / У n-i Уп ,

(8)

Zn J

При технической реализации соотношения (7) необходимо использовать

И и (п-1) инверторов для получения инверсных сигналов УД

При технической реализации соотношения (8) необходимо использовать п

),

25

30

35

40

45

50

55

Преобразователь содержит кодовый диск 1 с информационной дорожкой, на которой нанесен код псевдослучайной двоичной последовательности максимальной длины с периодом М 2 -1 7 (0011101), считывающие элементы 2-4, расположенные вдоль информационной дорожки с постоянным шагом,равным двум квантам X, дополнительные считывающие элементы 5-7, шесть пороговых элементов 8, четырехвходовый сумматор 9 по модулю два, два трехвходовых сумматора 10 по модулю два, два элемента НЕ 11, три трехвходовых логических элемента И 12, три двухвходовых сумматора 13 по модулю два, выходы 14 преобразователя.

Преобразователь работает следующим образом.

При перемещении кодового диска 1 против хода часовой стрелки на один квант со считывающих элементов 2-4 и дополнительных считывающих элементов 5-7 последовательно в параллельном коде через пороговые элементы 8 будут сниматься сигналы, соответствующие следующим кодовым комбинациям: 010111, 111100, 100110, 110001, 001101, 101011, 011010.

с

При отсутствии в работе преобразователя одиночных ошибок сигнал с дополнительного считывающего элемента 5 дополняет сигналы со считывающих элементов 2-4 до четного числа единиц, сигнал с дополнительного считывающего элемента 6 дополняет сиг-- налы со считывающих элементов 2 и 3 до четного числа единиц, сигнал с

дополнительного считывающего элемента 7 дополняет сигналы со считывающих элементов 3 и 4 до четного числа единиц, при этом выходные сигналы сумматоров 9 и 10 по модулю два равны |нулю. Поскольку нулевой сигнал с вывода сумматора 9 по модулю два поступает на входы всех логических элементов И 12, то на их выходах также будет присутствовать нулевой сигнал. Нулевые сигналы с выходов логических (элементов И 12, поступая на вторые Јходы соответствующих сумматоров 13

по модулю два,на первые входы которых 15 модулю два на выход 14 преобразова-

30

через пороговые элементы 8 поступают Сигналы со считывающих элементов 2-4, Дозволяют последним без изменения роходить на выход 14 преобразователя,

При появлении в работе преобразо- 20 бателя одиночных ошибок возможны следующие варианты:

а) Вышел из строя считывающий эле- 25 мент 2, при этом - выходной сигнал Сумматора 9 по модулю два равен еди- йице (у 1), выходной сигнал первого Сумматора 10 по модулю два равен единице (), выходной сигнал второго Сумматора 10 по модулю два равен нулю ().

В данном случае сигнал на выходе первого логическогоtэлемента И 12 будет равен единице (Z,l), а сигналы на выходах второго и третьего логических элементов И 12 будут равны нулю (Z Z.j 0). Эти выходные сигналы первого, второго и третьего логических элементов И 12 подаются на 40 Вторые входы первого, второго и третьего двухвходовых сумматоров 13 по модулю два соответственно.

Таким образом, сигнал с первого считывающего элемента 2, пройдя через первый сумматор 13 по модулю два на выход 14 преобразователя, будет Проинвертирован, тогда как сигналы со считывающих элементов 3 и 4, пройдя через соответствующие сумматоры 13 по модулю два на выход 14 преобразователя, останутся без изменения.

45

50

теля, останутся без изменения.

Вышел из строя считывающий элемент 4, при.этом выходные сигналы сумматоров 9 по модулю два и второго сумматора 10 по модулю два равны 1К (У УЗ ) выходной сигнал первого сумматора 10 по модулю два равен О (уг 0).

В данном случае сигнал на выходе третьего логического элемента И 12 будет равен 1 (Z $ 1), а первого и второго - О (Z Zj 0). Эти выходные сигналы подаются на вторые входы соответствующих сумматоров 13 по модулю два. При этом, сигнал с третьего считывающего элемента 4, пройдя через третий сумматор 13 по модулю два, будет проинвертирован, а сигналы с первого 2 и второго 3 считывающих элементов, пройдя через соответствующие сумматоры 13 по модулю два на выход 14 преобразователя, останутся без изменения.

Вышел из строя любой из дополнительных считывающий элемент.

При этом, сигналы с выходов всех логических элементов И 12 будут равны О 1 (Z 0), а сигналы со считывающих элементов 2-4 будут передаваться через сумматоры 13 по модулю два на выход 14 преобразователя без изменения. Аналогично работает устройство при реверсе.

Формула изобретения

Преобразователь угол - код, содержащий кодовый диск с информационной дорожкой, выполненной в виде градаций псевдослучайной двоичной последовательности максимальной длины периода М 2 -1, построенной посредством примитивного MHOIочлена h(x) степени п, где п - разрядность преВышел из строя считывающий элемент 3, при этом выходной сигнал сумматора 9 по модулю два равен 1 (у, 1), выходные сигналы первого и Второго сумматоров по модулю два равмы

у - у, - П.

В данном случае сигнал на выходе второго погического элемента- И 12 будет равен 1 (Zг - 1), первого и третьего - О (Z Z 0). Эти выходные сигналы подаются на вторые входы соответствующих сумматоров 13 по модулю два. При этом, сигнал со считывающего элемента 3, пройдя через второй сумматор 13 по модулю два на выход 4 преобразователя, будет проинвертирован, а сигналы со считывающих элементов 2 и 4, пройдя через соответствующие сумматоры 13 по

0

5

0

5

теля, останутся без изменения.

Вышел из строя считывающий элемент 4, при.этом выходные сигналы сумматоров 9 по модулю два и второго сумматора 10 по модулю два равны 1К (У УЗ ) выходной сигнал первого сумматора 10 по модулю два равен О (уг 0).

В данном случае сигнал на выходе третьего логического элемента И 12 будет равен 1 (Z $ 1), а первого и второго - О (Z Zj 0). Эти выходные сигналы подаются на вторые входы соответствующих сумматоров 13 по модулю два. При этом, сигнал с третьего считывающего элемента 4, пройдя через третий сумматор 13 по модулю два, будет проинвертирован, а сигналы с первого 2 и второго 3 считывающих элементов, пройдя через соответствующие сумматоры 13 по модулю два на выход 14 преобразователя, останутся без изменения.

Вышел из строя любой из дополнительных считывающий элемент.

При этом, сигналы с выходов всех логических элементов И 12 будут равны О 1 (Z 0), а сигналы со считывающих элементов 2-4 будут передаваться через сумматоры 13 по модулю два на выход 14 преобразователя без изменения. Аналогично работает устройство при реверсе.

Формула изобретения

Преобразователь угол - код, содержащий кодовый диск с информационной дорожкой, выполненной в виде градаций псевдослучайной двоичной последовательности максимальной длины периода М 2 -1, построенной посредством примитивного MHOIочлена h(x) степени п, где п - разрядность преобразователя, iv считывающих элементов размещенных вдоль информационной дорожки с постоянным угловым шагом

1360°

кх, где х ---- - величина кванта

и

преобразователя, k 1,2,..., причем kn-i М, первый дополнительный считывающий элемент, смещенный вдоль информационной дорожки относительно первого считывающего элемента на величину угла оЈ, х Ј(n-l )k+(M-iy, гдеМ - степень одночлена, являющегося остатком от деления по модулю два

со стороны младших степеней многочле- 15 первыми входами п элементов И, выход

на г(х)

на многочлен h(x),

(n-l)k+

25

& Jlc

Ј

причем 1, а также величина

+(M-1) берутся по модулю М, первый сумматор по модулю два, выходы ечи- 20 тывающих элементов и выход первого дополнительного считывающего элемента соединены с входами первого сумматора по модулю два, отличающий- с я тем, что, с целью повышения надежности преобразователя за счет исправления одиночных ошибок, в него введены (п-1) дополнительных считывающих элементов, (п-) сумматоров по модулю два на три входа, (п-1) элементов НЕ, п элементов И, п сумматоров по модулю два на два входа, (1+1)-й дополнительный считываюгоий элемент смещен вдоль информационной дорожки относительно 1-го считывающего элемента на величину угла о/ хрс(М-зУ где S - степень одночлена, являющегося остатком от деления по модулю два со стороны младших

30

35

первого сумматора по модулю два на три входа соединен с вторым входом первого элемента И, к остальным входам которого через элементы НЕ подключены выходы, остальных сумматоров по модулю два на три входа, выходы 1-го и (i+J)-ro сумматоров по модулю два на три входа соединены соответственно с вторым и третьим входом (i-H)-ro элемента И, к остальным входам которого через элементы НЕ подключены выходы остальных сумматоров по модулю два н-а три входа , выход (п-1)-сумматора по модулю два на три входа соединен с вторым входом n-го элемента И, к остальным входам которого через элементы НЕ подключены выходы остальных сумматоров по модулю два на три входа, выход 1-го элемента И соединен с вторым входом соответствующего 1-го сумматора по модулю два на два входа, выходы которых являются выходами преобразователя.

степеней двучлена q (х) 1+х|с на мир- гочлен h(x), причем степень S одночлена и величина }с+(M-S ) берутся по модулю М, i 1 ,2,. .. (п-1), выходы п считывающих элементов соединены соответственно с первыми входами п сумматоров по модулю два на два входа, выходы 1-го и (i+l)-ro считывающих элементов и ()-ro дополнительного считывающего элемента соединены с входами 1-го сумматора по модулю два на три входа, выход первого сумматора по модулю два соединен с

5

0

0

5

первого сумматора по модулю два на три входа соединен с вторым входом первого элемента И, к остальным входам которого через элементы НЕ подключены выходы, остальных сумматоров по модулю два на три входа, выходы 1-го и (i+J)-ro сумматоров по модулю два на три входа соединены соответственно с вторым и третьим входом (i-H)-ro элемента И, к остальным входам которого через элементы НЕ подключены выходы остальных сумматоров по модулю два н-а три входа , выход (п-1)-сумматора по модулю два на три входа соединен с вторым входом n-го элемента И, к остальным входам которого через элементы НЕ подключены выходы остальных сумматоров по модулю два на три входа, выход 1-го элемента И соединен с вторым входом соответствующего 1-го сумматора по модулю два на два входа, выходы которых являются выходами преобразователя.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Фотоэлектрические преобразователи информации./Под.ред.Л.Н.Прес- нухина.-М.: Машиностроение, 1974, с.294-304 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-01-07—Публикация

1987-07-28—Подача