Изобретение относится к вычислительной технике и предназначено для поиска неисправностей в аппаратных средствах цифровой вычислительной техники, в том числе для контроля много- выходных цифровых узлов ЭВМ.

Цель изобретения - увеличение быстродействия и повышение достоверности контроля.

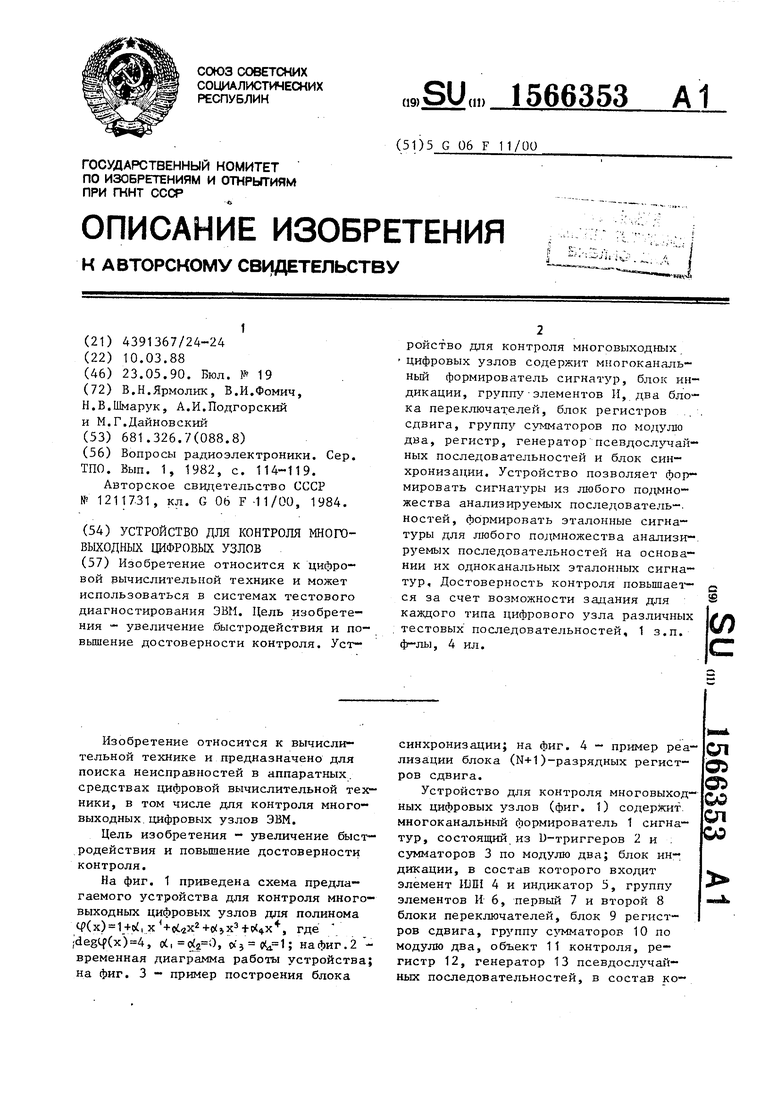

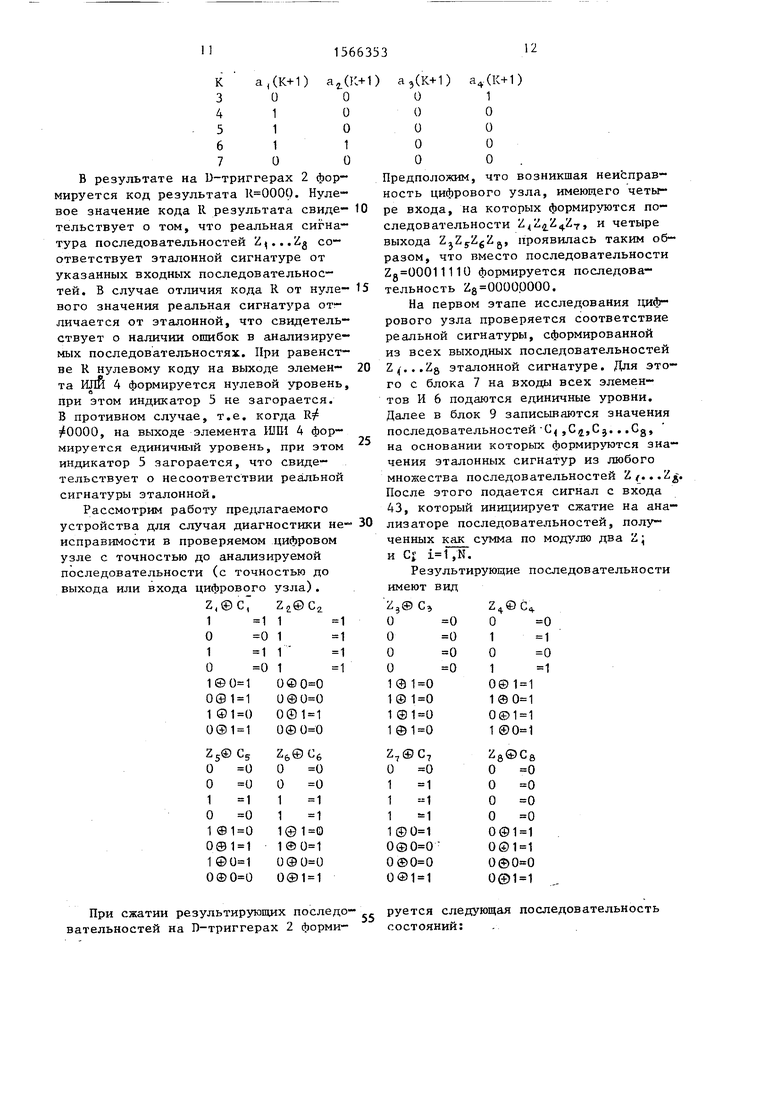

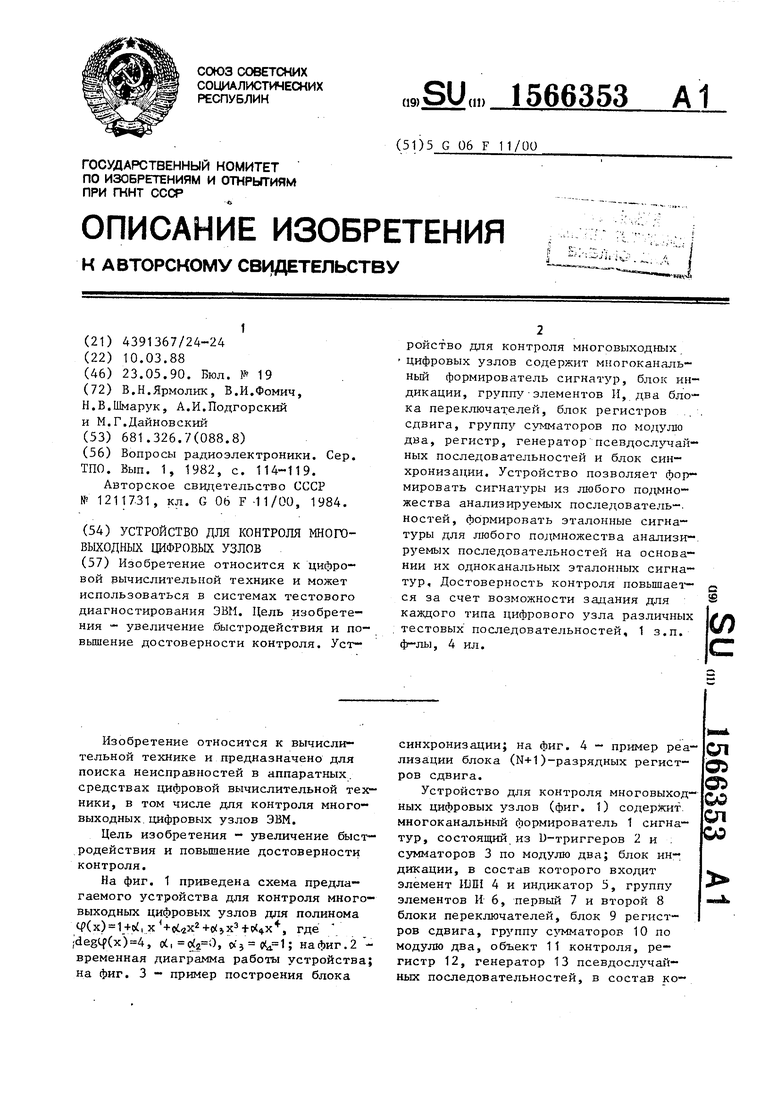

На фиг. 1 приведена схема предлагаемого устройства для контроля много- выходных цифровых узлов для полинома

ЧЧх)(, X + ci,2x2+C iX3t(X4X гДе

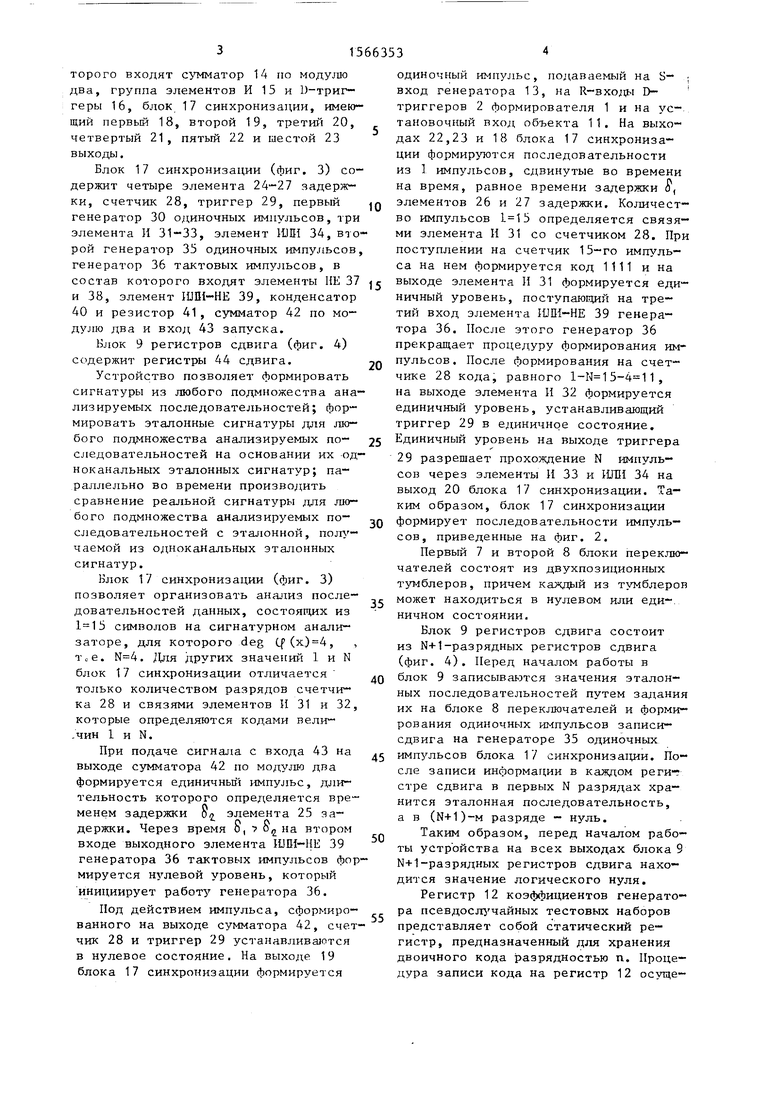

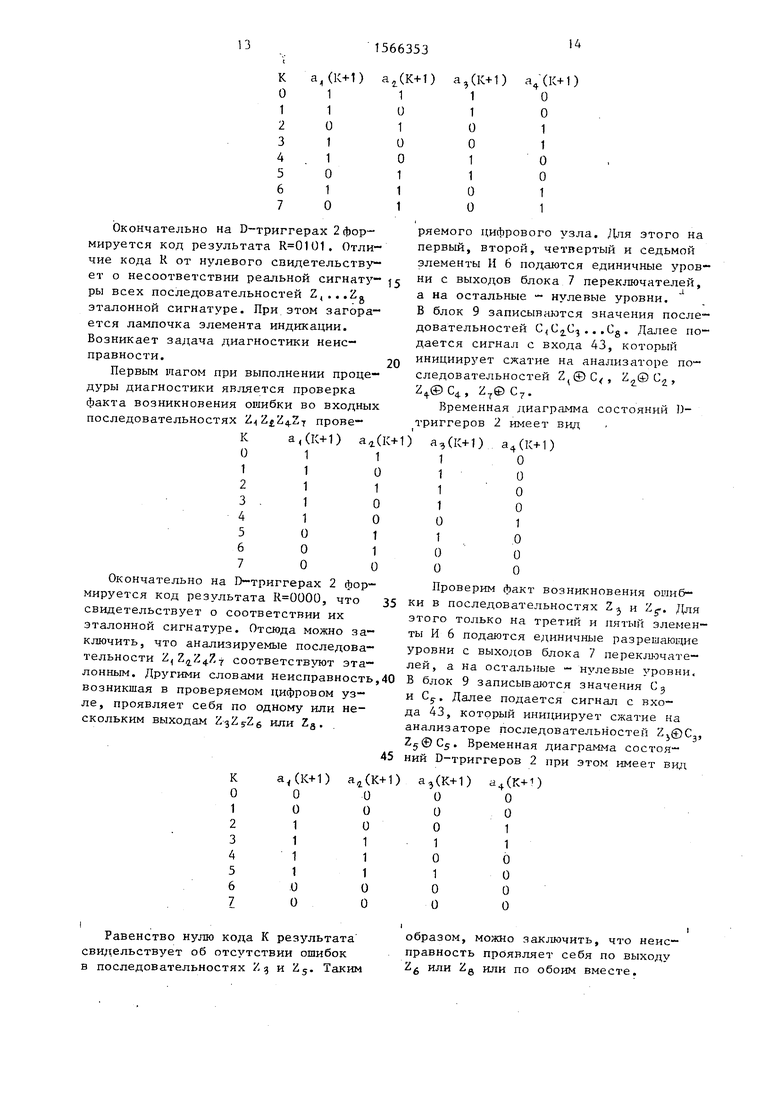

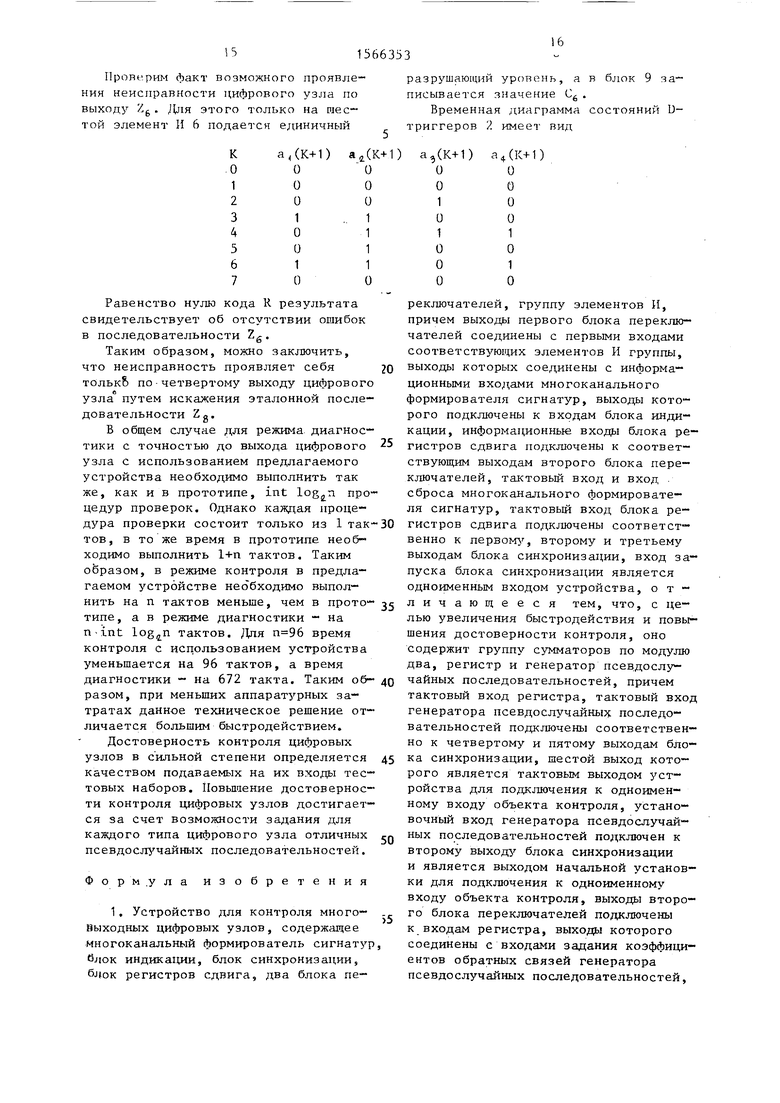

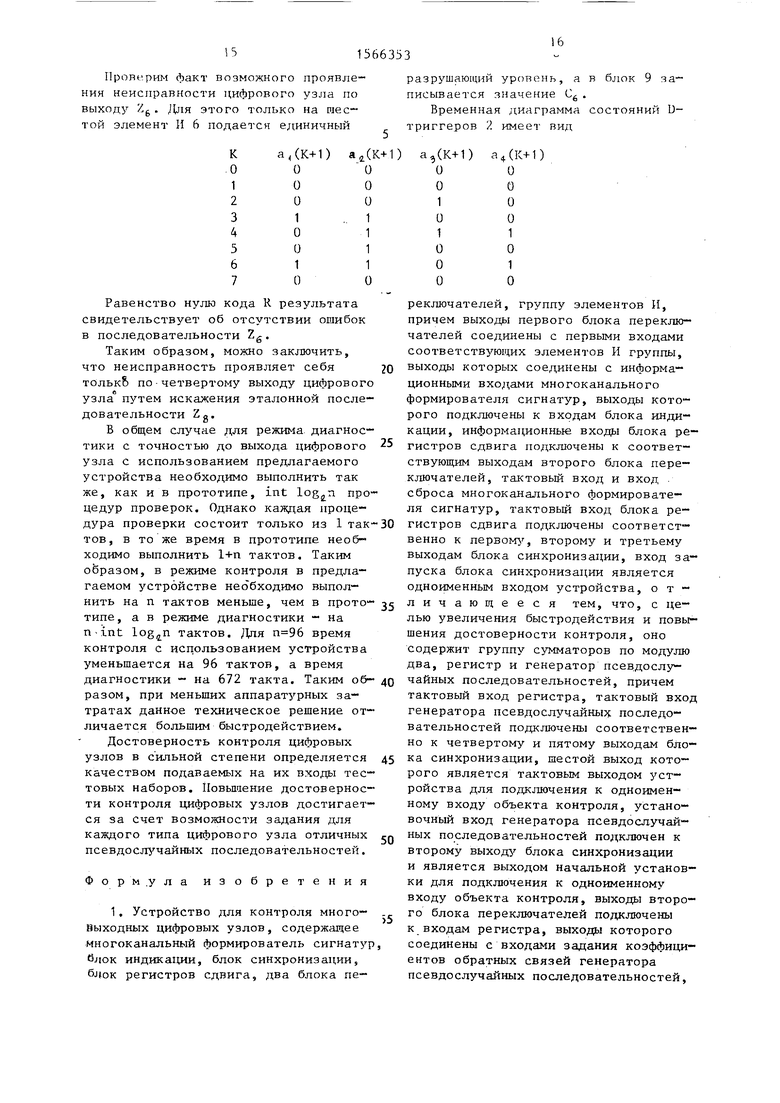

;degtf(x)4, oi,oi2, на фиг. 2 - временная диаграмма работы устройства; на фиг. 3 - пример построения блока

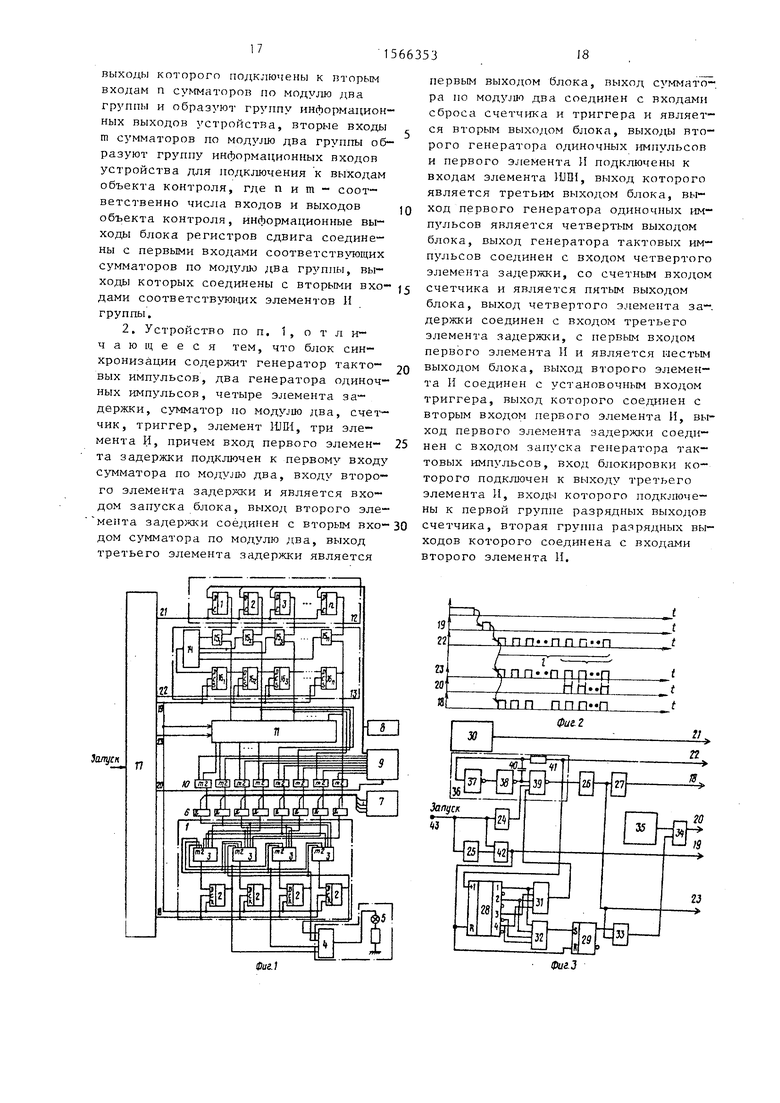

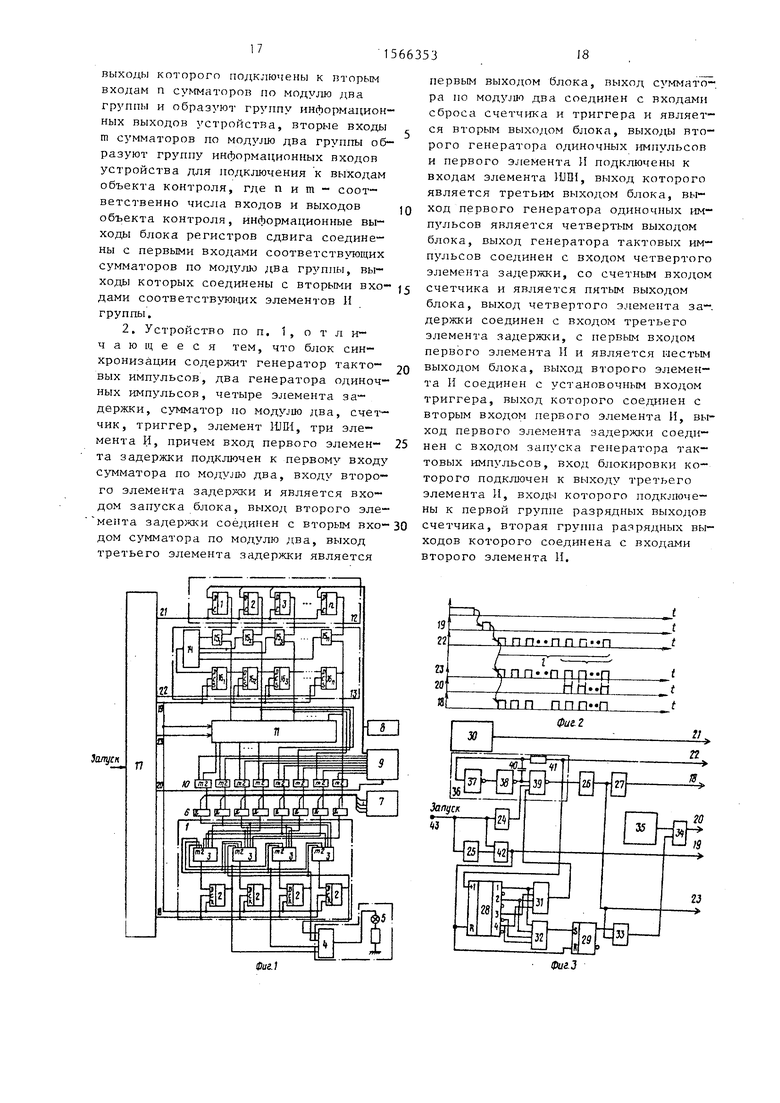

синхронизации; на фиг. 4 - пример реализации блока (N+1)-разрядных регистров сдвига.

Устройство для контроля многовыходных цифровых узлов (фиг. 1) содержит многоканальный формирователь 1 сигнатур, состоящий из D-триггеров 2 и сумматоров 3 по модулю два; блок индикации, в состав которого входит элемент ИЛИ 4 и индикатор 5, группу элементов И 6, первый 7 и второй 8 блоки переключателей, блок 9 регистров сдвига, группу сумматоров 10 по модулю два, объект 11 контроля, регистр 12, генератор 13 псевдослучайных последовательностей, в состав ко-

сд

ОЭ

ся со

ел Юо

торого входят сумматор 14 по модулю два, группа элементов И 15 и 1)-триг- геры 16, блок 17 синхронизации, имеющий первый 18, второй 19, третий 20, четвертый 21, пятый 22 и шестой 23 выходы.

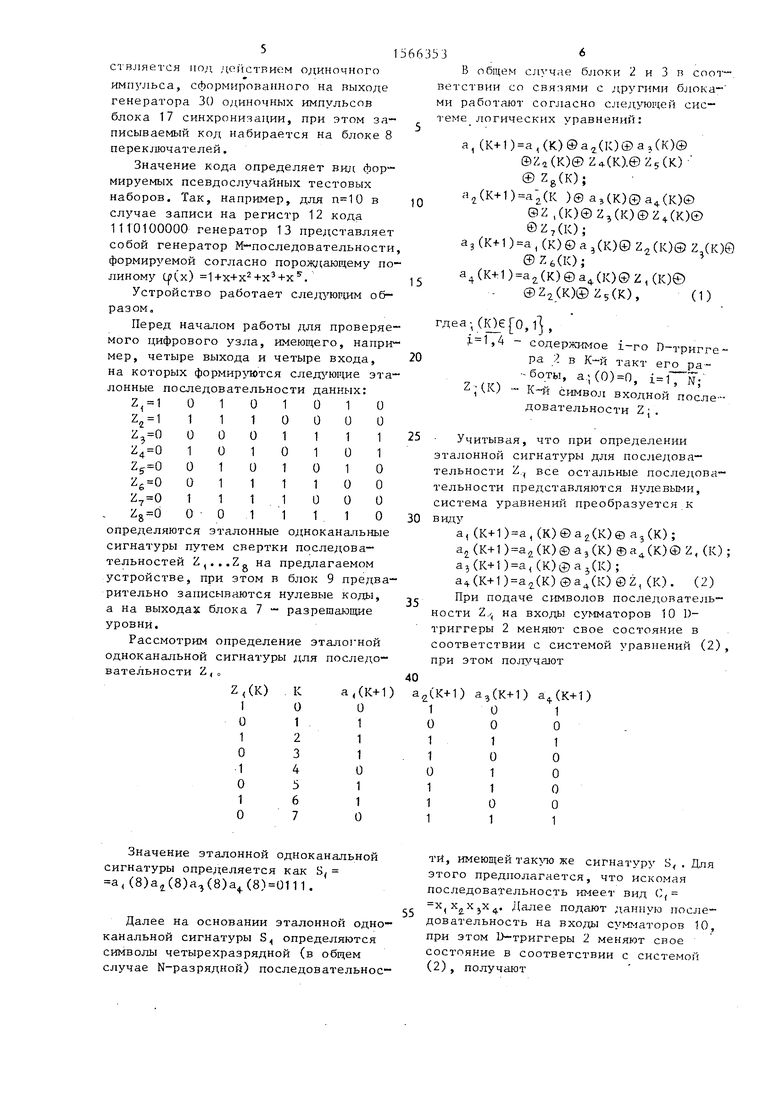

Блок 17 синхронизации (фиг. 3) содержит четыре элемента 24-27 задержки

, счетчик 28, триггер 29, первый JQ генератор 30 одиночных импульсов, три элемента И 31-33, элемент ИЛИ 34, второй генератор 35 одиночных импульсов, генератор 36 тактовых импульсов, в состав которого входят элементы НЕ 37 выходе элемента И 31 формируется еди и 38, элемент 11)111-НЕ 39, конденсатор ничный уровень, поступающий на тре- 40 и резистор 41 , сумматор 42 по мо- тий вход элемента IIJD1-HE 39 генера- дулю два и вход 43 запуска.тора 36. После этого генератор 36

одиночный импульс, подаваемый на Ь- вход генератора 13, на R-входы D- триггеров 2 Формирователя 1 и на установочный вход объекта 11. На выходах 22,23 и 18 блока 17 синхронизации формируются последовательности из 1 импульсов, сдвинутые во времени на время, равное времени задержки о, элементов 26 и 27 задержки. Количест во импульсов определяется связями элемента И 31 со счетчиком 28. Пр поступлении на счетчик 15-го импульса на нем формируется код 1111 и на

выходе элемента И 31 формируется еди ничный уровень, поступающий на тре- тий вход элемента IIJD1-HE 39 генера- тора 36. После этого генератор 36

одиночный импульс, подаваемый на Ь- вход генератора 13, на R-входы D- триггеров 2 Формирователя 1 и на установочный вход объекта 11. На выходах 22,23 и 18 блока 17 синхронизации формируются последовательности из 1 импульсов, сдвинутые во времени на время, равное времени задержки о, элементов 26 и 27 задержки. Количество импульсов определяется связями элемента И 31 со счетчиком 28. При поступлении на счетчик 15-го импульса на нем формируется код 1111 и на

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1985 |

|

SU1283772A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1211731A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство для контроля генератора М-последовательностей | 1985 |

|

SU1278850A1 |

| Устройство для стохастического контроля микропроцессорных цифровых блоков | 1990 |

|

SU1725222A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Сигнатурный анализатор | 1983 |

|

SU1223230A1 |

| Устройство для контроля многовыходных цифровых узлов | 1982 |

|

SU1019454A1 |

Изобретение относится к цифровой вычислительной технике и может использоваться в системах тестового диагностирования ЭВМ. Цель изобретения - увеличение быстродействия и повышение достоверности контроля. Устройство для контроля многовыходных цифровых узлов содержит многоканальный формирователь сигнатур, блок индикации, группу элементов И, два блока переключателей, блок регистров сдвига, группу сумматоров по модулю два, регистр, генератор псевдослучайных последовательностей и блок синхронизации. Устройство позволяет формировать сигнатуры из любого подмножества анализируемых последовательностей, формировать эталонные сигнатуры для любого подмножества анализируемых последовательностей на основании их одноканальных эталонных сигнатур. Достоверность контроля повышается за счет возможности задания для каждого типа цифрового узла различных тестовых последовательностей. 1 з.п.ф-лы, 4 ил.

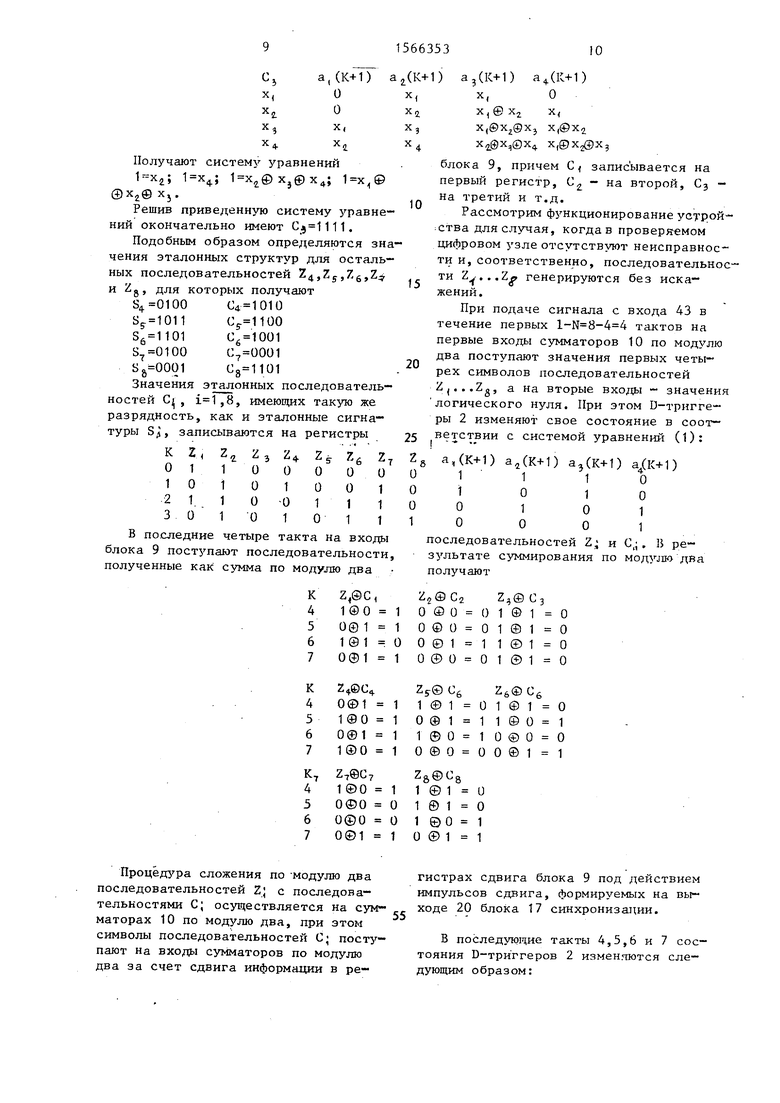

Блок 9 регистров сдвига (фиг. 4) содержит регистры 44 сдвига.

Устройство позволяет формировать сигнатуры из любого подмножества анализируемых последовательностей; формировать эталонные сигнатуры для любого подмножества анализируемых по- следовательностей на основании их од- ноканальных эталонных сигнатур; параллельно во времени производить сравнение реальной сигнатуры для любого подмножества анализируемых последовательностей с эталонной, получаемой из одноканальных эталонных сигнатур.

Блок 17 синхронизации (фиг. 3) позволяет организовать анализ последовательностей данных, состоящих из символов на сигнатурном анализаторе, для которого deg tf(x)4, , т.е. . Для других значений 1 и N блок 17 синхронизации отличается только количеством разрядов счетчика 28 и связями элементов И 31 и 32, которые определяются кодами величин 1 и N.

При подаче сигнала с входа 43 на выходе сумматора 42 по модулю дна формируется единичный импульс, длительность которого определяется временем задержки 0 элемента 25 задержки. Через время О, ое на втором входе выходного элемента ШП1-НЕ 39 генератора 36 тактовых импульсов формируется нулевой уровень, который инициирует работу генератора 36.

Под действием импульса, сформированного на выходе сумматора 42, счетчик 28 и триггер 29 устанавливается в нулевое состояние. На выходе 19 блока 17 синхронизации формируется

0

0

5

5

прекращает процедуру формирования импульсов. После формирования на счетчике 28 кода, равного , на выходе элемента И 32 формируется единичный уровень, устанавливающий триггер 29 в единичное состояние. Единичный уровень на выходе триггера 29 разрешает прохождение N импульсов через элементы И 33 и ИЛИ 34 на выход 20 блока 17 синхронизации. Таким образом, блок 17 синхронизации формирует последовательности импульсов, приведенные на фиг. 2.

Первый 7 и второй 8 блоки переключателей состоят из двухпозиционных тумблеров, причем каждый из тумблеров может находиться в нулевом или единичном состоянии.

Блок 9 регистров сдвига состоит из N+1-разрядных регистров сдвига (фиг. 4). Перед началом работы в блок 9 записываются значения эталонных последовательностей путем задания их на блоке 8 переключателей и формирования одиночных импульсов записи- сдвига на генераторе 35 одиночных 5 импульсов блока 17 синхронизации. После записи информации в каждом регистре сдвига в первых N разрядах хранится эталонная последовательность, а в (N+1)-M разряде - нуль.

Таким образом, перед началом работы устройства на всех выходах блока 9 N+1-разрядных регистров сдвига находится значение логического нуля.

Регистр 12 коэффициентов генератора псевдослучайных тестовых наборов представляет собой статический регистр, предназначенный для хранения двоичного кода разрядностью п. Процедура записи кода на регистр 12 осуще-

0

0

5

ОТ ИЛИСТ СИ ПОД ДСИГТВИеМ ОДИНОЧНОГО

импульса, сформированного на выходе генератора 30 одиночных импульсов блока 17 синхронизации, при этом записываемый код набирается на блоке 8 переключателей.

Значение кода определяет вид формируемых псевдослучайных тестовых наборов. Так, например, для ) в случае записи на регистр 12 кода 1110100000 генератор 13 представляет собой генератор М-последовательности формируемой согласно порождающему полиному ср(х) 1 +х+х2+хэ+х f.

Устройство работает следующим образом.

Перед началом работы для проверяемого цифрового узла, имеющего, например, четыре выхода и четыре входа, на которых формируются следующие эталонные последовательности данных:

0101010 1 1 10000 0001111 1010101 0101010

0111100

1111000

0011110 определяются эталонные одноканальные сигнатуры путем свертки последовательностей Z...Z.a на предлагаемом устройстве, при этом в блок 9 предварительно записываются нулевые коды, а на выходах блока 7 - разрешающие уровни.

Рассмотрим определение эталогной одноканальной сигнатуры для последовательности Z , о

Z,(K) Ка,(К+1

IОО

011

121

031

14О

051

161 070

z, 1 Z2 1

Z4 0

Значение эталонной одноканальной сигнатуры определяется как S( а((8)а1(8)а,(8)аф(8)0111.

Далее на основании эталонной одно- канальной сигнатуры S,, определяются символы четырехразрядной (в общем случае N-разрядной) последовательносВ общем случае блоки 2 и 3 г соответствии со связями с другими блоками работают согласно следующей системе логических уравнершй:

я, (K+1) a,(K)@a2(,(K)@

Ф/.а(К)(± Z(K).@Z5(K)

© Zg(K);

а2(К+1)а2(К )©а3(К)©а4(К)0 ©Z ,(K)©Z,(K)©Zf(K)© ©Z7(K); а, (К+1 )а , (К) & а ,(К)© Z2(K)© Z,(K)0

©Z6(K); a4(K+1)az(K)©a4(K)©Z,(K)e

©Z2(K)(±) Z5(K),(1)

гдеa; ,l,

- 1,4 содержимое i-го D-тригге- 0pa . в К-й такт его paz-(K) к0-™ а;(0)°

,) к-и символ входной последовательности Z;.

5 Учитывая, что при определении эталонной сигнатуры для последовательности Z, все остальные последовательности представляются нулевыми, система уравнений преобразуется к

0 виду

а, (К+1)а,(К)® а 2(К)© а , (К) ; а(Кн-1)а2(К)©а3(К) ffia4(K)0Z, (К); а,(К+1)а (К)©а}(К); а4(К+1)а2(К)®а4(К) ©Z, (К). (2) ,- При подаче символов последовательности Z., на входы сумматоров 10 1)- триггеры 2 меняют свое состояние в соответствии с системой уравнений (2), при этом получают 0

а2(К+1) а,(К+1) a(K-t-l) 1 0 1 000 1 1 1 1 О О

01 О

11 О 1 О О 1 1 1

ти, имеющей такую же сигнатуру S . Для этого предполагается, что искомая последовательность имеет вид С( х Х2Х 5х ч- Ш1ее подают данную последовательность на входы сумматоров 10, при этом D-триггеры 2 меняют свое состояние в соответствии с системой (2), получают

С, а(К+1) а4(К+1)

О х i х« х

Л I С/ О я

4 X2©x5 x4©xt

Учитывая, что последовательность С,) имеет ту же сигнатуру S( , получают систему линейных уравненийю

0 х2©хг; (® х 1 , откуда получают, что .

Для определения эталонной сигнатуры последовательности подставляют в систему уравнений (1) нулевые зна- 15 чения последовательностей Z,,/. ZЈ,Z6,Z7,Zfc, при этом получают

Значение эталонной сигнатуры определяется как Д8)аг(8)а ,(8)а4(8) 0001.30

Для определения последовательности ,х, имеющей сигнатуру SЈ,

х4 х, 0х4 х2

Получают систему уравнений JQ , ,©хЛ, получают, что сигнатура последовательности равняется Я„ 0001.

Для определения эталонной гигнату- 45 ры последовательности Z на основании (1) путем подстановки в последнюю

а4(К+1)

Х2 X,

х4

а , (К+1) а , (К) © а2 (К) © а , (К) © Z 2(К);

аг(К+1)а4(К)© а,(К)©а4(К);

а}(К+1)а((К)© аг(К)0 Z2(K);

aA(K+1)al(K)®a4(K)©Z2(K). (3)

При подаче символов последовательности Z на входы сумматоров 10 D- триггеры 2 меняют свое состояние в соответствии с системой (3), при этом получают

подают последовательность С2 на входы сумматоров 10 и, пользуясь системой (3), получают значение Ьг в зависимости от символов последовательности С2. При этом имеют , ,

а,(К+1) а4(К+1)

х,

х( © хг

х( ©хг©х5 с4xa©x ®xf

нулевых значений Z , ,Z,Z4,i ,,Z6,Z7 ,Zg получают систему уравнений

а, (К+1 )а , (К)© а2(К)©а 3(К) ;

a2(K+1)a4(K)©a3(K)©a).(K)®Z,(K) a,(K+1)a,(K)0a,(K)©Z3(K);

а4(К+1)аг(К)©а4(К). (4)

D-триггеры 2 изменяют свое состояние в соответствии с диаграммой

а,(К+1) аг(К+1) а,(К-И) а(К-Н)

х( О

О О х.

Получают систему уравнений

1 хг©х}©х4; ©хг© х5.

Решив приведенную систему уравнений окончательно имеют tJ.j 1111.

Подобным образом определяются значения эталонных структур для остальных последовательностей Z4,ZS,Z6,Z и Z8, для которых получают С4 Ю10

о

Значения эталонных последовательностей Cj, ,8, имеющих такую же разрядность, как и эталонные сигнатуры 5д, записываются на регистры

В последние четыре такта на входы блока 9 поступают последовательности, полученные как сумма по модулю два

К7Z7@C7Za©C8

41 ©0 11 © 1 О

5ОФО 01 © 1 О

60©0 01 © 0 1

7001 10 © 1 1

Процедура сложения по модулю два последовательностей Zj с последовательностями С; осуществляется на сумматорах 10 по модулю два, при этом символы последовательностей С; поступают на входы сумматоров по модулю два за счет сдвига информации в ре-

(К+1) а,(К-И) а(К-Н)

а

10

х( О

X j сУ 2

х,©х2©х3 х,©хг

Хг@Х,©Х4 Х(©Х,,©Х,

блока 9, причем С, записывается на первый регистр, С2 - на второй, С3 - на третий и т.д.

Рассмотрим функционирование устройства для случая, когда в проверяемом цифровом узле отсутствуют неисправности и, соответственно, последовательное- ти 1ц,.. Lg генерируются без искажений.

При подаче сигнала с входа 43 в течение первых тактов на первые входы сумматоров 10 по модулю два поступают значения первых четырех символов последовательностей Z(...Zg, а на вторые входы - значения логического нуля. При этом U-тригге- ры 2 изменяют свое состояние в соот- 25 ветствии с системой уравнений (1):

20

последовательностей зультате суммирован получают

Z2ffiC2Z.,©C3

О © 0 0 1 © 1 0 0©0 01©1 0

0© 1 1 1 © 1 О 0©0

Z5® С6 Z6©C6

1© 1 0 1 © 1 О О © 1 1 1 © 0 1 0 1

гистрах сдвига блока 9 под действием импульсов сдвига, формируемых на выходе 20 блока 17 синхронизации.

В последующие такты 4,5,6 и 1 состояния D-триггеров 2 изменчются следующим образом:

В результате на D-трнггерах 2 формируется код результата . Нулевое значение кода II результата свиде- тельствует о том, что реальная сигнатура последовательностей Z.-.Zg соответствует эталонной сигнатуре от указанных входных последовательностей. В случае отличия кода К от нуле- вого значения реальная сигнатура отличается от эталонной, что свидетельствует о наличии ошибок в анализируемых последовательностях. При равенстве К нулевому коду на выходе элемента ИЛИ 4 формируется нулевой уровень, при этом индикатор 5 не загорается. В противном случае, т.е. когда R 0000, на выходе элемента ШП1 4 формируется единичный уровень, при этом индикатор 5 загорается, что свидетельствует о несоответствии реальной сигнатуры эталонной.

Рассмотрим работу предлагаемого устройства для случая диагностики не- исправимости в проверяемом цифровом

При сжатии результирующих последовательностей на D-триггерах 2 форми5

0

0

5

а4(К+1) 1

О О О

о

Предположим, что возникшая неисправность цифрового узла, имеющего четыре входа, на которых формируются последовательности Z4Z4Z4ZT, и четыре выхода ZjZyZgZg, проявилась таким образом, что вместо последовательности Z8 00011110 формируется последовательность Z8 00000000.

На первом этапе исследования цифрового узла проверяется соответствие реальной сигнатуры, сформированной из всех выходных последовательностей Z. ..Z8 эталонной сигнатуре. Для этого с блока 7 на входы всех элементов И 6 подаются единичные уровни. Далее в блок 9 записываются значения последовательностейC,C,Cj...Gg, на основании которых формируются значения эталонных сигнатур из любого множества последовательностей Z...ZA. После этого подается сигнал с входа 43, который инициирует сжатие на анализаторе последовательностей, полученных как сумма по модулю два Z:

55

руется следующая последовательность состояний:

а(К+1) аа(К+1) а,(К+1) а4(К+1)

1 1

О 1 1

О 1 О

1

о 1 о о 1 1 1

1

1 о о 1 1 о о

о о 1 1

о о 1 1

Окончательно на D-триггерах 2 формируется код результата . Отличие кода К от нулевого свидетельствует о несоответствии реальной сигнату- ры всех последовательностей Z,.,.Zg эталонной сигнатуре. При этом загорается лампочка элемента индикации. Возникает задача диагностики неисправности.

Первым шагом при выполнении процедуры диагностики является проверка факта возникновения ошибки во входных последовательностях прове-

К

О

1

2

3

4

5

6

7

Окончательно на D-триггерах 2 формируется код результата , что свидетельствует о соответствии их эталонной сигнатуре. Отсюда можно заключить, что анализируемые последовательности Z,Z4Z4Z7 соответствуют эталонным. Другими словами неисправность возникшая в проверяемом цифровом узле, проявляет себя по одному или нескольким выходам , или 2д.

К О 1 2 3 4 5 6 7

аДК+1) О О 1 1 1 1

О О

Равенство нулю кода К результата свидельствует об отсутствии ошибок в последовательностях / .$ и Zs. Таким

1

1 о о 1 1 о о

о о 1 1

о о 1 1

ряемого цифрового узла. Для этого на первый, второй, четвертый и седьмой элементы И b подаются единичные уровни с выходов блока 7 переключателей, а на остальные - нулевые уровни. В блок 9 записываются значения последовательностей С,СгС}...Св. Далее подается сигнал с входа 43, который инициирует сжатие на анализаторе последовательностей Z{©C, C2 , Z4©C4, Z7© С7.

Временная диаграмма состояний D- триггеров 2 имеет вид

О а4(К+1)

О

О

О

О

1

О

О

О

Проверим факт возникновения ошиб-

40

35 ки в последовательностях Z

Для

этого только на третий и пятый элементы И 6 подаются единичные разрешающее уровни с выходов блока 7 переключателей, а на остальные - нулевые уровни. В блок 9 записываются значения Сэ и Су. Далее подается сигнал с входа 43, который инициирует сжатие на анализаторе последовательностей Z;@C3, Z5©C5. Временная диаграмма состояний D-триггеров 2 при этом имеет вид

аа(К+1) а,(К+1) a4(K+i)

и о о 1

о 1

о о

о о 1 1

о о о о

образом, можно заключить, что неисправность проявляет себя по выходу 26 или Ze или по обоим вместе.

Проверим факт возможного проявления неисправности цифрового узла по

выходу

Для этого только на шестой элемент И 6 подается единичный

а,(К+1) а(К+1) а,(К+1) а4(К+1)

О О О 1

О О

1

о

о о и 1 1 1 1 о

U О 1 О

1

О О

о

о о о о 1

о 1 о

Равенство нулю кода К результата свидетельствует об отсутствии ошибок в последовательности Z6.

Таким образом, можно заключить, что неисправность проявляет себя только по четвертому выходу цифрового узла путем искажения эталонной последовательности Zg.

В общем случае для режима диагностики с точностью до выхода цифрового узла с использованием предлагаемого устройства необходимо выполнить так же, как и в прототипе, int процедур проверок. Однако каждая процедура проверки состоит только из 1 тактов, в то же время в прототипе необходимо выполнить 1+п тактов. Таким образом, в режиме контроля в предлагаемом устройстве необходимо выполнить на п тактов меньше, чем в прото- типе, а в режиме диагностики - на n int logen тактов. Для время контроля с использованием устройства уменьшается на 96 тактов, а время диагностики - на 672 такта. Таким об- разом, при меньших аппаратурных затратах данное техническое решение отличается большим быстродействием.

Достоверность контроля цифровых узлов в сильной степени определяется качеством подаваемых на их входы тестовых наборов. Повышение достоверности контроля цифровых узлов достигается за счет возможности задания для каждого типа цифрового узла отличных псевдослучайных последовательностей.

Формула изобретения

Временная диаграмма состояний D- триггеров 2 имеет вид

U О 1 О

1

О О

о

о о о о 1

о 1 о

0

5

0 о

5 д

5

реключателей, группу элементов И, причем выходы первого блока переключателей соединены с первыми входами соответствующих элементов И группы, выходы которых соединены с информационными входами многоканального формирователя сигнатур, выходы которого подключены к входам блока индикации, информационные входы блока регистров сдвига подключены к соответствующим выходам второго блока переключателей, тактовый вход и вход сброса многоканального формирователя сигнатур, тактовый вход блока регистров сдвига подключены соответственно к первому, второму и третьему выходам блока синхронизации, вход запуска блока синхронизации является одноименным входом устройства, отличающееся тем, что, с целью увеличения быстродействия и повышения достоверности контроля, оно содержит группу сумматоров по модулю два, регистр и генератор псевдослучайных последовательностей, причем тактовый вход регистра, тактовый вход генератора псевдослучайных последовательностей подключены соответственно к четвертому и пятому выходам блока синхронизации, шестой выход которого является тактовым выходом устройства для подключения к одноименному входу объекта контроля, установочный вход генератора псевдослучайных последовательностей подключен к второму выходу блока синхронизации и является выходом начальной установки для подключения к одноименному входу объекта контроля, выходы второго блока переключателей подключены к входам регистра, выходы которого соединены с входами задания коэффициентов обратных связей генератора псевдослучайных последовательностей,

выходы которого подключены к шорым входам п сумматоров по модулю два группы и образуют rpyimv ннЛормацион- ных выходов устройства, вторые входы m сумматоров по модулю два группы образуют группу информационных входов устройства для подключения к выходам объекта контроля, где пит- соответственно числа входов и выходов объекта контроля, информационные выходы блока регистров сдвига соединены с первыми входами соответствующих сумматоров по модулю два группы, выходы которых соединены с вторыми вхо- дами соответствующих элементов 11 группы.

Запуск

Фиг I

0

с

0

0

5

первым выходом блока, выход сумматора по модулю два соединен с входами сброса счетчика и триггера и является вторым выходом блока, выходы второго генератора одиночных импульсов и первого элемента И подключены к входам элемента ШШ, выход которого является третьим выходом блока, выход первого генератора одиночных импульсов является четвертым выходом блока, выход генератора тактовых импульсов соединен с входом четвертого элемента задержки, со счетным входом счетчика и является пятым выходом блока, выход четвертого элемента задержки соединен с входом третьего элемента задержки, с первым входом первого элемента И и является местым выходом блока, выход второго элемента И соединен с установочным входом триггера, выход которого соединен с вторым входом первого элемента И, выход первого элемента задержки соединен с входом запуска генератора тактовых импульсов, вход блокировки которого подключен к выходу третьего элемента И, входы которого подключены к первой группе разрядных выходов счетчика, вторая группа разрядных выходов которого соединена с входами второго элемента И.

П П««П П

Г г - тппги П

Т1ПП

я.

ФигЭ

От блока 8

К блоку Ю Фиг

| Вопросы радиоэлектроники | |||

| Сер | |||

| ТПО | |||

| Вып | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Способ получения борнеола из пихтового или т.п. масел | 1921 |

|

SU114A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1211731A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-05-23—Публикация

1988-03-10—Подача