Изобретение относится к вычислительной технике и может быть использовано в информационных системах управления высокой степени надежности для обработки информации, передаваемой последовательным кодом.

Цель изобретения - повышение достоверности приема информации и функциональной надежности.

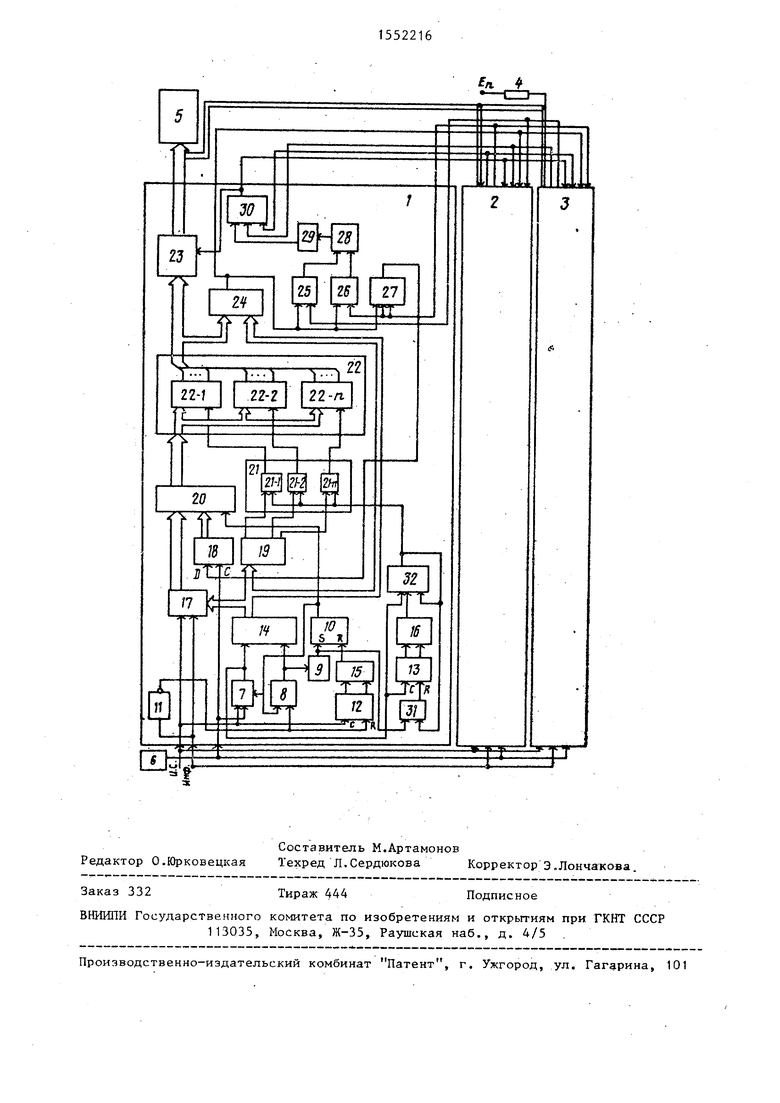

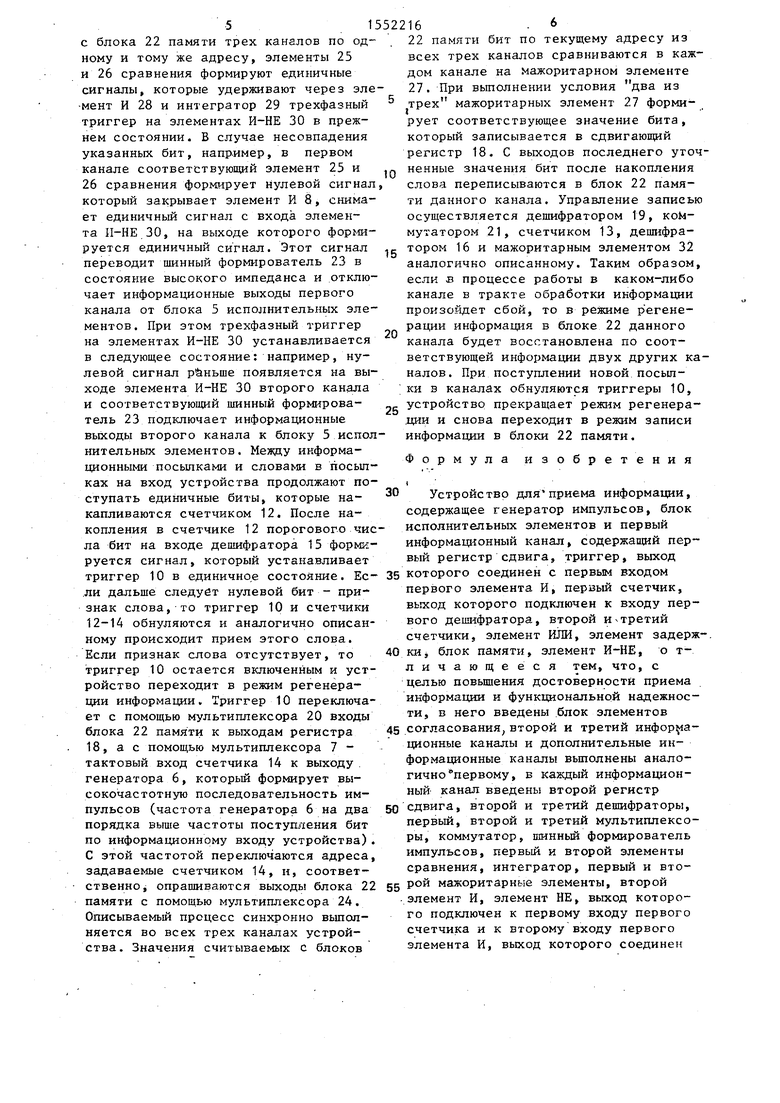

На чертеже представлена функциональная схема устройства.

Устройство содержит каналы 1-3 приема информации, блок 4 согласования, блок 5 исполнительных элементов, генератор 6 импульсов, каждый канал содержит мультиплексор 7, элемент И 8, элемент 9 задержки, триггер 10, элемент НЕ 11, счетчики 12-14, дешифраторы 15 и 16, регистры 17 и 18 сдвига, дешифратор 19, мультиплексор 20, коммутатор 21, блок 22 памяти,

шинный формирователь 23 импульсов, мультиплексор 24, элементы 25 и 26 сравнения, мажоритарный элемент 27, - элемент И 28, интегратор 29 элемент И-НЕ 30, элемент ИЛИ 31 и мажоритарный элемент 32.

Устройство работает следующим образом.

В исходном состоянии в каждом канале триггер 10, счетчики 12-14, регистры 17 и 18 и регистры блока 22 памяти обнулены (цепи начальной установки не показаны). При этом на входах элементов 25 и 26 сравнения нулевые сигналы совпадают, на их выходах формируются единичные сигналы, которые открывают элемент И 28, и на первый вход элемента И-НЕ 30 через интегратор 29 в каждом канале подается единичный сигнал. Соединение входов и выходов элементов И-НЕ 30 в

01

ел to го

0

315

трех каналах образует трехфазный триггер, который в исходном положении устанавливается произвольно в одном из своих трех состояний. Например, первым срабатывает элемент И-НЕ 30 пер- вого канала, и нулевой сигнал с его выхода отключает элементы И-НЕ 30 второго и третьего каналов. Единичные сигналы с выходов элементов И-НЕ 30 второго и третьего каналов удерживают трехфазный триггер в указанном устойчивом состоянии и с помощью соответствующих шинных формирователей 23 отключают информационные выходы второго и третьего каналов от блока 5 исполнительных элементов. При этом к входам блока 5 остаются подключенными только информационные выходы первого канала. На информационный вход устройства информационные посыл- ки слов длины К числом п поступают в последовательном коде в виде сочетаний бит логических О и 1. Каждый бит сопровождается тактовым импульсом. При отсутствии информационного слова на вход устройства подаются единичные биты, а признаком начала слова является нулевой первый бит, следующий за некоторым пороговым числом Р единичных бит. Счетчик

12с дешифратором 15 определяет по количеству тактовых импульсов пороговое число Р единичных бит, счетчик

13с дешифратором 16 - конец слова длины К бит. При отсутствии информа- ционного слова и между словами счетчик 12 заполняется до порогового числа и на выходе дешифратора 15 формируется сигнал, который устанавливает триггер 10 в единичное состояние. По следний определяет режим работы устройства : в нулевом состоянии - режим приема и записи слов в блок 22 памяти, в единичном состоянии - режим регенерации памяти. Триггер 10 во включенном состоянии подг отавливаа-т

к открыванию элемент И 8. При поступлении на второй (информационный) вход устройства первого нулевого бита (признака слова) на выходе элемен та НЕ 11 формируется сигнал, который обнуляет счетчик 12 через элемент И 8 счетчик 14, через элемент 9 задержки триггер 10 и через элемент ИЛИ 31 счетчик 13. Триггер 10 нулевы сигналом с прямого выхода подключает тактовый вход счетчика 14 через мультиплексор 7 к первому (тактовому) входу устройства и второй (информа0

5

5

22

- 30

35 40 45

50 ее

16 4

ционный) вход блока 22 памяти через мультиплексор 20 к выходу регистра 17. Счетчик 14 считает тактовые импульсы сопровождения от начала слова и формирует адреса бит слова, которые управляют регистром 17, дешифратором 19 и мультиплексором 24. Регистр 17 сдвига преобразует последовательный код слова в параллельный, управляется старшими разрядами адреса счетчика 14, т.е. выдает слово на выход после его накопления в регистре, и через мультиплексор 20 подает код слова на информационные входы регистров блока 22 памяти. Число регистров 22-1-22-п блока 22 памяти равно числу п слов в посыпке. В каждый из регистров блока 22 записывается одно слово информации длины К. Выбор регистра осуществляется с помощью дешифратора 19 число слов, на вход которого подаются старшие разряды счетчика 14 адресов бит. Дешифратор 19 управляет соответствующими элементами И коммутатора 21, а сигнал на разрешение записи слова в соответствующий регистр блока 22 формируется счетчиком 13, который считает импульсы с выхода мультиплексора 7, дешифратором 16 и мажоритарным элементом 32. После накопления К бит слова импульс через элемент ИЛИ 31 обнуляет счетчик 13 и процесс накопления бит следующего слова повторяется. С выходов блока 22 памяти коды записанных слов поступают через шинный формирователь 23 импульсов на блок 5 исполнительных элементов. Исполнительные элементы являются инерционными устройствами, например реле, электромагниты и др., и срабатывают с относительно большой задержкой, что позволяет произвести сравнение накопленной информации во всех каналах. С целью контроля выходы блока 22 памяти последовательно опрашиваются с помощью мультиплексора 24 и адресного счетчика 14. Считываемые значения бит с блока 22 памяти подаются через мультиплексор 24 на входы элементов 25 и 26 сравнения и мажоритарного элемента, 27. Описанный процесс приема информации синхронно происходит во втором и третьем каналах. Сигналы с выходов мультиплексоров 24 трех каналов поступают на входы элементов 25 и 26 сравнения и мажоритарного элемента 27 соответствующих каналов. При совпадении значений бит, считанных

с блока 22 памяти трех каналов по одному и тому же адресу, элементы 25 и 26 сравнения формируют единичные сигналы, которые удерживают через элемент И 28 и интегратор 29 трехфазный триггер на элементах И-НЕ 30 в прежнем состоянии. В случае несовпадения указанных бит, например, в первом канале соответствующий элемент 25 и 26 сравнения формирует нулевой сигнал который закрывает элемент И 8, снимает единичный сигнал с входа элемента 1I-HE 30, на выходе которого формируется единичный сигнал. Этот сигнал переводит шинный формирователь 23 в состояние высокого импеданса и отключает информационные выходы первого канала от блока 5 исполнительных элементов. При этом трехфазный триггер на элементах И-НЕ 30 устанавливается в следующее состояние: например, нулевой сигнал рйньше появляется на выходе элемента И-НЕ 30 второго канала и соответствующий шинный формирователь 23 подключает информационные выходы второго канала к блоку 5 исполнительных элементов. Между информационными посылками и словами в посылках на вход устройства продолжают поступать единичные биты, которые накапливаются счетчиком 12. После накопления в счетчике 12 порогового числа бит на входе дешифратора 15 форм;:30 Устройство для приема информации содержащее генератор импульсов, бло исполнительных элементов и первый информационный канал, содержащий пе вый регистр сдвига, триггер, выход

руется сигнал, который устанавливает триггер 10 в единичное состояние. Ее- 35 которого соединен с первым входом ли дальше следует нулевой бит - при-первого элемента И, периый счетчик,

знак слова, то триггер 10 и счетчики 12-14 обнуляются и аналогично описанному происходит прием этого слова. Если признак слова отсутствует, то триггер 10 остается включенным и устройство переходит в режим регенерации информации. Триггер 10 переключает с помощью мультиплексора 20 входы блока 22 памяти к выходам регистра 18, ас помощью мультиплексора 7 - тактовый вход счетчика 14 к выходу генератора 6, который формирует высокочастотную последовательность имвыход которого подключен к входу пе вого дешифратора, второй и третий счетчики, элемент ИЛИ, элемент заде

40 ки, блок памяти, элемент И-НЕ, о т личающееся тем, что, с целью повышения достоверности прием информации и функциональной надежно ти, в него введены блок элементов

45 согласования, второй и третий информ ционные каналы и дополнительные информационные каналы выполнены анало гично первому , в каждый информацион ный канал введены второй регистр

50 сдвига, второй и третий дешифраторы первый, второй и третий мультиплекс ры, коммутатор, шинный формировател импульсов, первый и второй элементы сравнения, интегратор, первый и вто

50 сдвига, второй и третий дешифраторы, первый, второй и третий мультиплексо ры, коммутатор, шинный формирователь импульсов, первый и второй элементы сравнения, интегратор, первый и втопульсов (частота генератора 6 на два порядка выше частоты поступления бит по информационному входу устройства). С этой частотой переключаются адреса, задаваемые счетчиком 14, и, соответственно, опрашиваются выходы блока 22 55 рой мажоритарные элементы, второй памяти с помощью мультиплексора 24.элемент И, элемент НЕ, выход котороОписываемый процесс синхронно выпол-го подключен к первому входу первого

няется во всех трех каналах устрой-счетчика и к второму входу первого

ства. Значения считываемых с блоковэлемента И, выход которого соединен

22 памяти бит по текущему адресу из всех трех каналов сравниваются в каждом канале на мажоритарном элементе 27. При выполнении условия два из трех мажоритарных элемент 27 формирует соответствующее значение бита, который записывается в сдвигающий регистр 18. С выходов последнего уточненные значения бит после накопления слова переписываются в блок 22 памяти данного канала. Управление записью осуществляется дешифратором 19, коммутатором 21, счетчиком 13, дешифра5 тором 16 и мажоритарным элементом 32 аналогично описанному. Таким образом, если в процессе работы в каком-либо канале в тракте обработки информации произойдет сбой, то в режиме регенерации информация в блоке 22 данного канала будет восстановлена по соответствующей информации двух других каналов. При поступлении новой посылки в каналах обнуляются триггеры 10,

,- устройство прекращает режим регенерации и снова переходит в режим записи информации в блоки 22 памяти.

0

Формула изобретения

Устройство для приема информации, содержащее генератор импульсов, блок исполнительных элементов и первый информационный канал, содержащий первый регистр сдвига, триггер, выход

которого соединен с первым входом первого элемента И, периый счетчик,

выход которого подключен к входу первого дешифратора, второй и третий счетчики, элемент ИЛИ, элемент задержки, блок памяти, элемент И-НЕ, о т- личающееся тем, что, с целью повышения достоверности приема информации и функциональной надежности, в него введены блок элементов

согласования, второй и третий информационные каналы и дополнительные информационные каналы выполнены аналогично первому , в каждый информационный канал введены второй регистр

сдвига, второй и третий дешифраторы, первый, второй и третий мультиплексоры, коммутатор, шинный формирователь импульсов, первый и второй элементы сравнения, интегратор, первый и второй мажоритарные элементы, второй элемент И, элемент НЕ, выход которос первым входом второго счетчика и через элемент задержки с первыми входами триггера и элемента ИЛИ, выход которого подключен к первому входу третьего счетчика, выход которого соединен с входом второго дешифратора, выход которого подключен к первому входу первого мажоритарного элемента, выход которого соединен с его вторым входом, вторым входом элемента ИЛИ и с первым входом коммутатора, выходы которого подключены к первым входам блока памяти, выходы которого соединены с соответствующими первыми входами шинного формирователя импуль-. сов и первого мультиплексора, выходы , которого подключены к первым входам первого и второго блоков сравнения и второго мажоритарного элемента, выход которого соединен с первым входом первого регистра сдвига, выход которого подключен к первому входу второго мультиплексора, выход которого соединен с вторым входом блока памяти, выход третьего мультиплексора подключен к второму входу третьего счетчика, третьему входу первого мажоритарного элемента и к второму входу второго счетчика, выход которого соединен с вторым входом первого мультиплексора, входом третье го дешифратора и с первым входом второго регистра сдвига, выход которого подключен к второму входу второго мультиплексора, выходы третьего дешиф ратора соединены с вторыми входами коммутатора, выход первого дешифратора подключен к второму входу триггера, выход которого соединен с третьим входом второго мультиплексора и с пер вым входом третьего мультиплексора, выходы первого и второго блоков срав-, нения подключены к соответствующим входам второго элемента И, выход которого через интегратор соединен с первым входом элемента И-НЕ, выход которого подключен к второму входу шинного формирователя импульсов, выход которого является первым выходом каждого информационного канала, выходы элемента И-НЕ и первого мульти

0

5

20

25

30

35

40

45

50

плексора являются соответственно вторым и третьим выходами каждого информационного канала, второй и третий входы элемента И-НЕ являются соответственно первым и вторым входами каждого информационного канала, вторые входы второго блока сравнения и второго мажоритарного элемента объединены и являются третьим входом каждого информационного канала, второй вход первого блока сравнения и третий вход второго мажоритарного элемента объединены и являются четвертым входом каждого информационного канала, первый вход второго регистра сдвига, вторые входы первого счетчика и третьего мультиплексора являются первым входом всех информационных каналов, вход элемента НЕ, вторые входы второго регистра сдвига являются вторым входом каждого информационного канала, выход генератора соединен с третьим входом третьего мультиплексора и с вторым входом первого регистра сдвига всех информационных каналов, первые выходы всех i информационных каналов объединены и подключены.к входам блока элементов согласования и блока исполнительных элементов, второй выход первого инфорс мационного канала соединен с первыми входами второго и третьего информационных каналов, третий выход первого информационного канала подключен к третьим входам второго и третьего информационных каналов, второй выход второго информационного канала соеди- ,нен с первым и вторым входами соответственно первого и третьего информационных каналов, третий выход второго информационного канала подключен к третьему и четвертому входам соответственно первого и третьего информационных каналов, второй выход третьего информационного канала соединен с вторыми входами первого и второго информационных каналов, третий выход третьего информационного канала подключен к четвертым входам первого и второго информационных каналов ,

f/i

| название | год | авторы | номер документа |

|---|---|---|---|

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Многоканальное устройство для сбора и обработки информации | 1988 |

|

SU1524078A1 |

| Устройство для приема и обработки информации | 1989 |

|

SU1603418A1 |

| Резервированное устройство | 1989 |

|

SU1635185A1 |

| Многоканальное устройство для сбора, обработки и выдачи информации | 1990 |

|

SU1753482A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для обмена данными | 1985 |

|

SU1297067A1 |

| Устройство для вывода информации | 1991 |

|

SU1833857A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для контроля срабатывания клавиш наборного поля | 1986 |

|

SU1432524A1 |

Изобретение относится к вычислительной технике и может быть использовано в информационных системах для приема двоичной информации, представленной последовательными кодами. Цель изобретения - повышение достоверности приема информации и функциональной надежности. Устройство обеспечивает тройное резервирование канала приема последовательного кода и его преобразование в параллельный код, непрерывный побитный контроль принятого сообщения, сравнение значений одноименных бит всех каналов и регенерацию их значений в памяти каждого канала по принципу большинства, что повышает функциональную надежность. При этом неисправный канал отключается и не искажает принятой информации. 1 ил.

Составитель М.Артамонов Редактор О.Юрковецкая Техред Л.Сердюкова Корректор Э.Лончакова.

Заказ 332

Тираж 444

В ШИШИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Подписное

| Устройство для приема информации | 1979 |

|

SU830488A2 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Устройство для приема информации | 1983 |

|

SU1104572A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1990-03-23—Публикация

1988-07-06—Подача