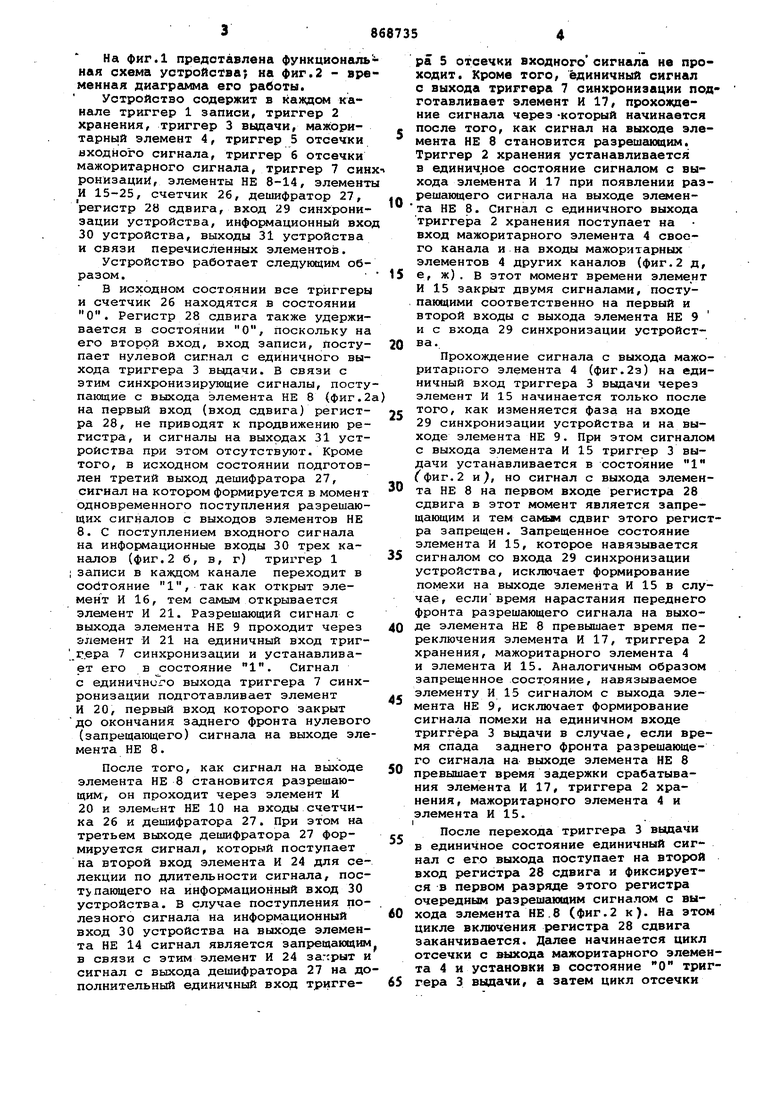

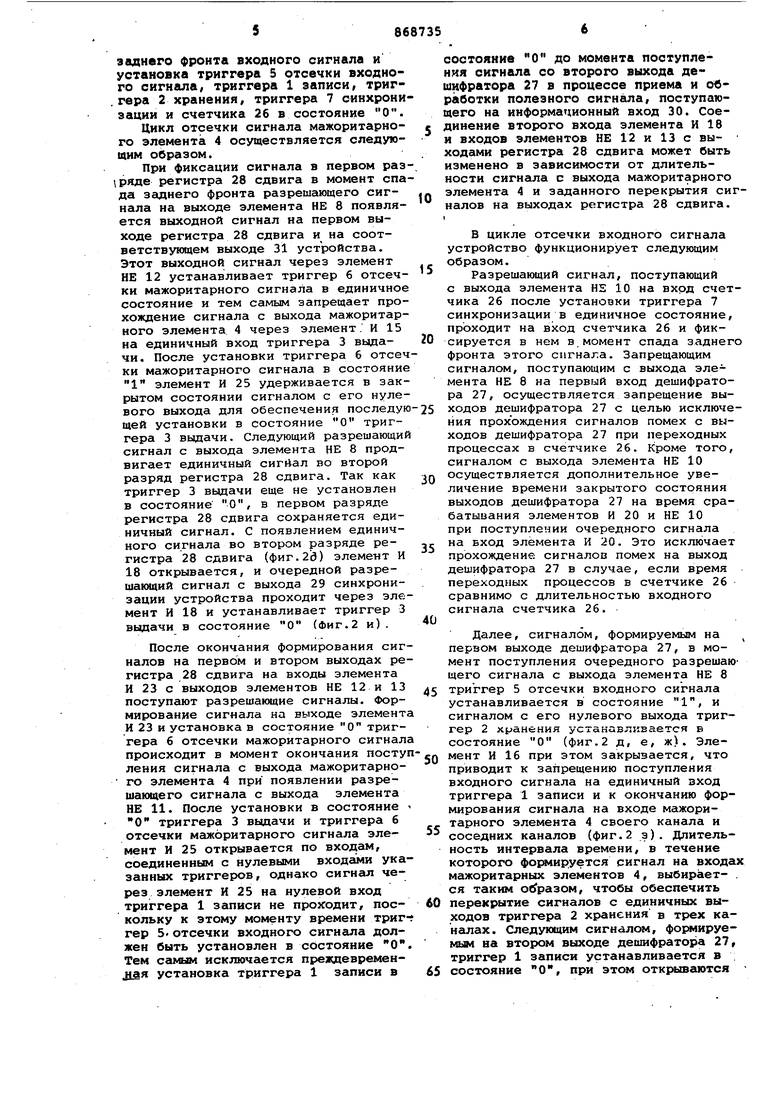

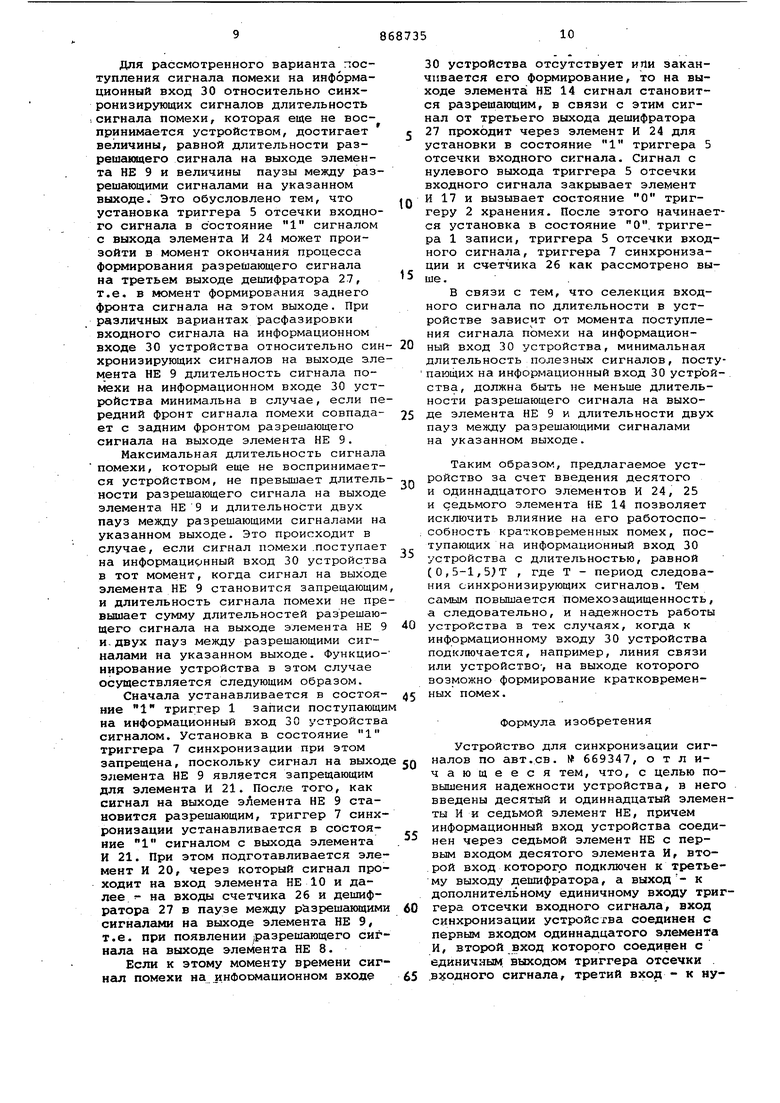

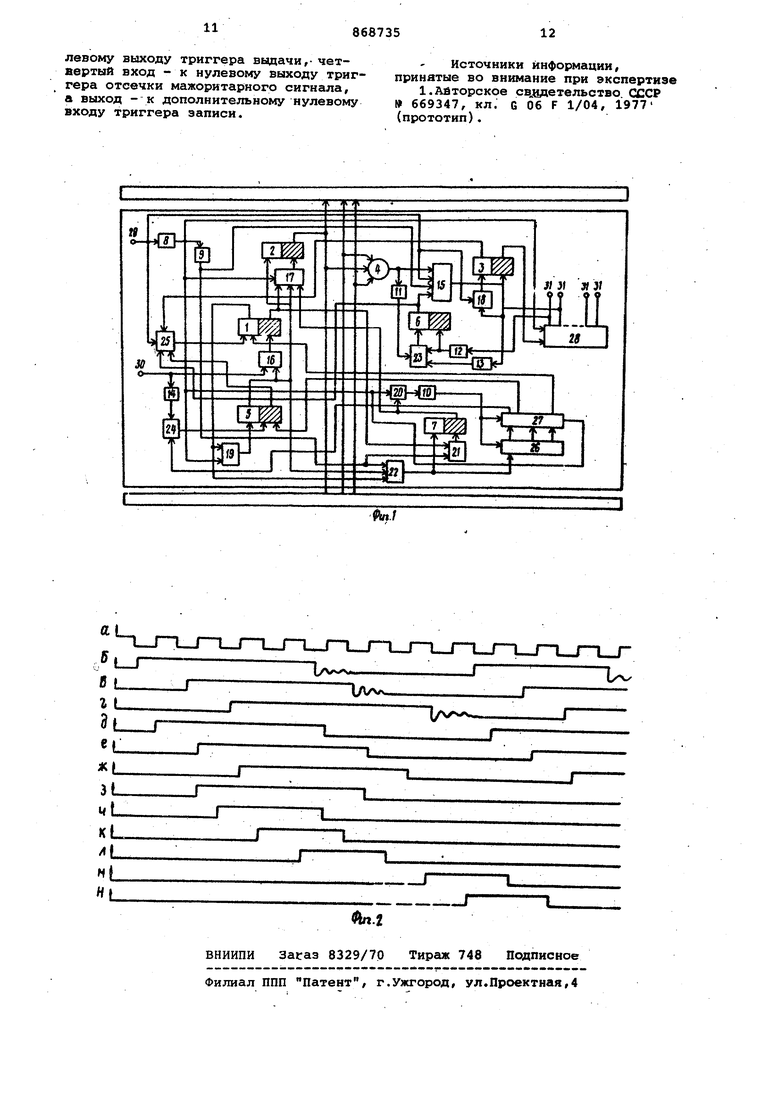

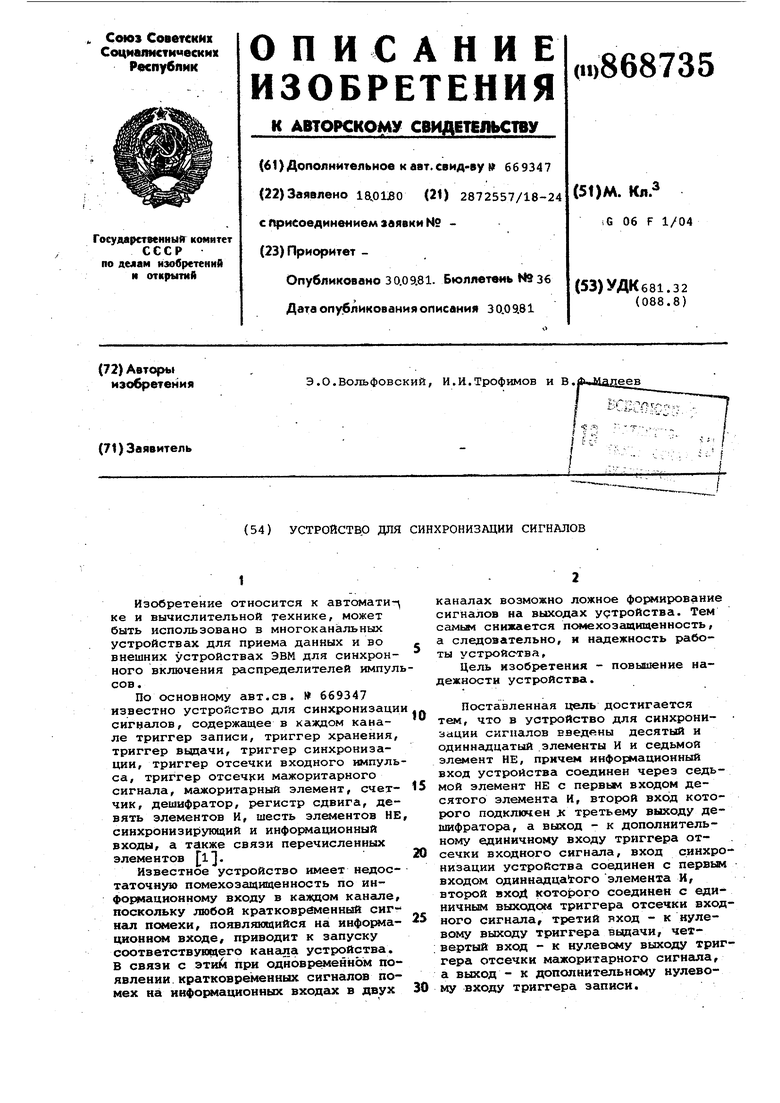

Изобретение относится к автоматике и вычислительной технике, может быть использовано в многоканальных устройствах для приема данных и во внешних устройствах ЭВМ для синхронного включения распределителей импул сов. По основному авт.св. 669347 известно устро 1ство для синхронизаци сигналов, содержащее в каждом канале триггер записи, триггер хранения, триггер выдачи, триггер синхронизации, триггер отсечки входного импуль са, триггер отсечки мажоритарного сигнала, мгикоритарный элемент, счетчик, дешифратор, регистр сдвига, девять элементов И, шесть элементов НЕ синхронизирующий и инфо1 1ационный входы, а также связи перечисленных элементов 1. Известное устройство имеет недостаточную помехозащищенность по информационному входу в каждом канале, поскольку любой кратковременный сигнаш помехи, появляющийся на информационнс входе, приводит к запуску соответствующего канала устройства. В связи с этиА при одновременном появлении, кратковременных сигналов помех на инфо1 «ационных входах в двух каналах возможно ложное фо «ирование сигналов на выходах устройства. Тем самым снижается помехозащищенность, а следовательно, и надежность работы устройства. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в устройство для синхронизации сигналов введены десятый и одиннадцатый элементы И и седьмой элемент НЕ, причем информационный вход устройства соединен через седьмой элемент НЕ с первым входом десятого элемента И, второй вход которого подключен j третьему выходу дешифратора, а выход - к дополнительному единичному входу триггера отсечки входного сигнала, вход синхронизации устройства соединен с первым входом одиннадцатого элемента И, второй вход которого соединен с единичным вахокси. триггера отсечки входного сигнала, третий РХОД - к нулевому выходу триггера вьвдачи, четвертый вход - к нулевому выходу триггера отсечки мажоритарного сигнала, а выход - к дополнительному нулевому входу триггера записи. На фиг.1 представлена функциональ ная схема устройства; на фиг.2 - вре менная диаграмма его работы. Устройство содержит в каждом канале триггер 1 записи, триггер 2 хранения, триггер 3 вьвдачи, мажоритарный элемент 4, триггер 5 отсечки входного сигнала, триггер б отсечки мажоритарного сигнала, триггер 7 син ронизации, элементы НЕ 8-14, элемент И 15-25, счетчик 26, дешифратор 27, регистр 28 сдвига, вход 29 синхронизации устройства, информационный вхо 30 устройства, выходы 31 устройства и связи перечисленных элементов. Устройство работает следующим образом. В исходном состоянии все триггеры и счетчик 26 находятся в состоянии О. Регистр 28 сдвига также удерживается в состоянии О, поскольку на его второй вход, вход записи, поступает нулевой сигнал с единичного выхода триггера 3 вьщачи. В связи с этим синхронизирующие сигналы, посту пающие с выхода элемента НЕ 8 (фиг.2 на первый вход (вход сдвига) регистра 28, не приводят к продвижению регистра, и сигналы на выходах 31 устройства при этом отсутствуют. Кроме того, в исходном состоянии подготовлен третий выход дешифратора 27, сигнал на котором формируется в момент одновременного поступления разрешающих сигналов с выходов элементов НЕ 8. С поступлением входного сигнала на информационные входы 30 трех каналов (фиг.2 б, в, г) триггер 1 i записи в каждом канале переходит в состояние 1, так как открыт элемент И 16, тем самым открывается элемент И 21. Разрешающий сигнал с выхода элемента НЕ 9 проходит через элемент И 21 на единичный вход триг г.ера 7 синхронизации и устанавливаСигналет его в состояние с единичного выхода триггера 7 синхронизации подготавливает элемент И 20, первый вход которого закрыт до окончания заднего фронта нулевого (запрещающего) сигнала на выходе эле мента НЕ 8. После того, как сигнал на выходе элемента НЕ 8 становится разрешающим, он проходит через элемент И 20 и элемент НЕ 10 на входы счетчика 26 и дешифратора 27. При этом на третьем выходе дешифратора 27 формируется сигнал, который поступает на второй вход элемента И 24 для селекции по длительности сигнала, поступающего на информационный вход 30 устройства. В случае поступления полезного сигнала на информационный вход 30 устройства на выходе элемента НЕ 14 сигнал является запрещающим в связи с этим элемент И 24 за::рыт и сигнал с выхода дешифратора 27 на до полнительный единичный вход триггера 5 отсечки входного сигнала не проходит. Кроме того, единичный сигнал с выхода триггера 7 синхронизации подготавливает элемент И 17, прохоящение сигнала через -который начинается после того, как сигнал на выходе элемента НЕ 8 становится разрешающим. Триггер 2 хранения устанавливается в единичное состояние сигналом с выхода элемента И 17 при появлении разрешаняцего сигнала на выходе элилента НЕ 8. Сигнал с единичного выхода триггера 2 хранения поступает на вход мажоритарного элемента 4 своего канала и на входы мажоритарных элементов 4 других каналов (фиг.2 д, е, ж). в этот момент времени элемент И 15 закрыт двумя сигналами, поступающими соответственно на первый и второй входы с выхода элемента НЕ 9 и с входа 29 синхронизации устройства. Прохождение сигнала с выхода мажоритарного элемента 4 (фиг.2з) на единичный вход триггера 3 выдачи через элемент И 15 начинается только после того, как изменяется фаза на входе 29 синхронизации устройства и на выходе элемента НЕ 9. При этом сигналом с выхода элемента И 15 триггер 3 выдачи устанавливается в состояние 1 (фиг.2 тл), но сигнал с выхода элемента НЕ 8 на первом входе регистра 28 сдвига в этот момент является запрещающим и тем самьм сдвиг этого регистра запрещен. Запрещенное состояние элемента И 15, которое навязывается сигналом со входа 29 синхронизации устройства, исключает формирование помехи на выходе элемента И 15 в случае, есливремя нарастания переднего фронта разрешающего сигнала на выходе элемента НЕ 8 превышает время переключения элемента И 17, триггера 2 хранения, мажоритарного элемента 4 и элемента И 15. Аналогичным образом запрещенное состояние, навязываемое элементу И 15 сигналом с выхода элемента НЕ 9, исключает формирование сигнала помехи на единичном входе триггера 3 выдачи в случае, если время спада заднего фронта разрешающего сигнала на выходе элемента НЕ 8 превышает время задержки срабатывания элемента И 17, триггера 2 хранения, мажоритарного элемента 4 и элемента И 15. После перехода триггера 3 выдачи в единичное состояние единичный сигнал с его выхода поступает на второй вход регистра 28 сдвига и фиксируется в первом разряде этого регистра очередным разрешающим сигналом с выхода элемента НЕ.8 (фиг.2 к). На этом цикле включения регистра 28 сдвига заканчивается. Далее начинается цикл отсечки с выхода мажоритарного элемента 4 и установки в состояние О триггера 3 выдачи, а затем цикл отсечки заднего фронта входного сигнала и установка триггера 5 отсечки входного сигнала, триггера 1 записи, триг. гера 2 хранения, триггера 7 синхрони зации и счетчика 26 в состояние О. Цикл отсечки сигнала мажоритарного элемента 4 осуществляется следующим образом. При фиксации сигнала в первом раз ряде регистра 28 сдвига в момент спа да заднего фронта разрешающего сигнала на выходе элемента НЕ 8 появляется выходной сигнал на первом выходе регистра 28 сдвига и на соответствующем выходе 31 устройства. Этот выходной сигнал через элемент НЕ 12 устанавливает триггер 6 отсечки мажоритарного сигнала в единичное состояние и тем самым запрещает прохождение сигнала с выхода мажоритарного элемента 4 через элемент. И 15 на единичный вход триггера 3 выдачи. После установки триггера 6 отсеч ки мажоритарного сигнала в состояние 1 элемент И 25 удерживается в зак рытом состоянии сигналом с его нуле вого выхода для обеспечения последую щей установки в состояние О триггера 3 выдачи. Следующий разрешающи сигнал с выхода элемента НЕ 8 продвигает единичный сигнал во второй разряд регистра 28 сдвига. Так как триггер 3 выдачи еще не установлен в состояние О, в первом разряде регистра 28 сдвига сохраняется единичный сигнал. С появлением единичного сигнала во втором разряде регистра 28 сдвига (фиг.23) элемент И 18 открывается, и очередной разрешающий сигнал с выхода 29 синхронизации устройства проходит через эле мент И 18 и устанавливает триггер 3 выдачи в состояние О (Фиг.2 и). После окончания формирования сиг налов на первом и втором выходах ре гистра 28 сдвига на входы элемента И 23 с выходов элементов НЕ 12 и 13 поступают разрешающие сигналы. Формирование сигнала на выходе элемент И 23 и установка в состояние О триггера 6 отсечки мажоритарного сигнал происходит в момент окончания посту ления сигнала с выхода мажоритарного элемента 4 при появлении разрешающего сигнала с выхода элемента НЕ 11. После установки в состояние О триггера 3 выдачи и триггера 6 отсечки мажоритарного сигнала элемент И 25 открывается по входам, соединенным с нулевыми входгичи указанных триггеров, однако сигнал через элемент И 25 на нулевой вход триггера 1 записи не проходит, поскольку к этому моменту времени триггер 5-отсечки входного сигиала должен быть установлен в состояние О Тем сгшым исключается преждевременЛая установка триггера 1 записи в состояние О до момента поступления сигнала со второго выхода дешифратора 27 в процессе приема и обработки полезного сигнала, поступающего на информат;ионный вход 30. Соединение второго входа элемента И 18 и входов элементов НЕ 12 и 13 с выходами регистра 28 сдвига может быть изменено в зависимости от длительности сигнала с выхода мажоритарного элемента 4 и заданного перекрытия сигналов на выходах регистра 28 сдвига. В цикле отсечки входного сигнала устройство функционирует следующим образом. Разрешающий сигнал, поступающий с выхода элемента НЕ 10 на вход счетчика 26 после установки триггера 7 синхронизации в единичное состояние, проходит на вход счетчика 26 и фиксируется в нем в момент спгща заднего фронта этого сигнала. Запрещающим сигналом, поступающим с выхода элемента НЕ 8 на первый вход дешифратора 27, осуществляется запрещение выходов дешифратора 27 с целью исключения прохождения сигналов помех с виходов дешифратора 27 при переходных процессах в счетчике 26. Кроме того, сигналом с выхода элемента НЕ 10 осуществляется дополнительное увеличение времени закрытого состояния выходов дешифратора 27 на время срабатывания элементов И 20 и НЕ 10 при поступлении очередного сигнала на вход элемента И 20. Это исключает прохождение сигналов помех на выход дешифратора 27 в случае, если время переходных процессов в счетчике 26 сравнимо с длительностью входного сигнала счетчика 26. Далее, сигналом, формируемым на первом выходе дешифратора 27, в момент поступления очередного разрешающего сигнала с выхода элемента НЕ 8 триггер 5 отсечки входного сигнала устанавливается в состояние 1, и сигналом с его нулевого выхода триггер 2 хранения устанавливается в состояние О (фиг.2 д, е, ж). Элемент И 16 при этом закрывается, что приводит к запрещению поступления входного сигнала на единичный вход триггера 1 записи и к окончанию формирования сигнала на входе мажоритарного элемента 4 своего канала и соседних каналов (фиг.2 э). Длительность интервала времени, в течение которого фоЕжируется сигнал на входах мажоритарных элементов 4, выбирает- . ся таким образом, чтобы обеспечить перекрытие сигналов с единичных выходов триггера 2 хранения в трех каналах. Следующим сигналом, формируемьм на втором выходе дешифратора 27, триггер 1 записи устанавливается в ; состояние О, при этом откЕлавгиотся элементы И 19 и 22, управляемые нулевым выходом триггера 1 записи. Установка триггера 5 отсечки вход ного сигнала осуществляется сигналом с выхода элемента И 19, который сфор мировывается при поступлении очередногд разрешающего сигнала с элемента НЕ 8. При этом установка триггера 5 отсечки входного сигнала может быть произведена тем же самым сигналом на выходе элемента НЕ 8, который через элемен,ты И 20 и НЕ 10 поступает на вход дешифратора 27 и далее на его второй выход. Это происходит в случае, если в паузе между двумя разрешающими сигналами на выходе эле мента НЕ 8 в счетчике 26 окончены пе реходвые процессы, и сформировался код на его выходе, а при поступлении очередного разрешакядего сигнала с вы хода элемента НЕ 8 время срабатывания элементов И 20, НЕ 10, дешифрато ра 27 и триггера 1 записи меньше дли тельности разрешающего сигнала на вы ходе элемента НЕ 8. Если же время задержки сигнала в элементах И 20, НЕ 10, дешифратора 27 и триггера 1 записи превьшает длительность разрешающего сигнала на выходе элемента НЕ 8, то установка триггера 5 отсечки входного сигнала в сойтояние О осуществляется следующим разрешающим сигналом на выходе элемента НЕ 8 Так как триггер 1 записи и триггер 5 отсечки входного сигнала установлены в состояние О, то подготовлены соответственно второй и третий входы элемента И 22. В связи с этим очеред ной разрешакадий сигнал с выхода элемента НЕ 9 проходит через элеяент И 22 и устанавливает триггер 7 синхр низации и счетчик 26 в состояние О На этом цикл приема входного сигнала заканчивается. . J гитeльнocть интервала времени, определяемого моментом фор 1ирования сигнала на втором входе дешифратора 27, выбирается таким образом, чтобы разрешить сброс триггера 1 записи в состояние О и последующих узлов схемы только после окончания переход ных процессов, которые могут иметь место после спада заднего фронта входного сигнала, поступающего на информационный вход 30 устройства. В свя,и с тем, что входные элементы устройства в каждом канале .работают автономно,длительность отоеч , ки входного сигналав каждом канале не зависит от момента поступления входных сигналов в других каналах. Кроке того, после установки в состояние О триггера 5 отсечки входных сигналов возможно поступление очеред ного сигнала на информационный вход 30 устройства в тот момент, когда ещ не закончено формирование сигналов на остальных выходах 31 регистра 28 сдвига (фиг 2 м, н). При этом уст ройство не теряет работоспособности и при рассинхронизации сигналов, поступающих на информационный вход 30 устройства в разных каналах, если величина сдвига между входными сигналами не превышает длительности временного интервала, формируемого на первом выходе дешифратора 27. в случае поступления на информационный, вход 30 устройства сигнала Iпомехи, например, с длительностью) ;не превьяоаСощей длительности разрешающего сигнала на выходе элемента НЖ.9г запуска триггера 3 вьадачи, следовательно, и формирования сигналов на выходах 31 устройства не происходит. Осуществляется это следующим образом. Если сигнал помехи на информационном входе 30 устройства поступает сразу же после появления разрешающего сигнала на выходе элемента НЕ 9, триггер 1 записи устанавливается в состояние 1 сигналом с выхода элемента И 16. Так как оба входа элемента И 21 оказываются подготовленншш, триггер 7 синхронизации устанавливается в состояние 1 и подготавливает элемент И 17 к срабатыванию. После установки триггера 7 синхронизации в состояние 1 первый же разрешающий сигнал, формнруемаЛ на выходе элемента НЕ 8, приводшт к появлению сигнала на третьем входе дешифратора 27, поскольку этот выход подготовлен в исходном состоянии счетчика 26. Так как сигнал на выходе элемента НЕ 14 становится к этому моменту времени разрешакпцш, то сигнал с третьего выхода дешифратора 27 устанавливает в состояние 1 триггер 5 отсечки входного сигнала, сигналом с нулевого выхода которого триггер 2 хранения устанавливается S состояние О. Вследствие этого разрешающий сигнал с единичного выхода триггера 2 хранения, который кратковременно появляется при срабатывании элемента И 17, на единичный вход триггера 3 выдачи через элемент И 15 не проходит, поскольку элемент И 15 и этот момент закрыт запрещающими сигналами со входа 29 синхронизации устройства и с выхода элемента НЕ 9. Так как триггер 3 выдачи и триггер 6 отсечки мажоритарного сигнала находятся в состоянии О, то очередной разрешающий сигнал со входа 29 синхронизации устройства проходит на дополнительный нулевой вход триггера 1 записи и устанавливает его в состояние О. После установки в состояние О триггера 1 записи подготавливаются к срабатыванию элементы И 19 и 22, начинается цикл установки в состояние О триггера 5 отсечки входного сигнала, триггера 7 синхронизации и четчика 26 как рассмотрено ранее. Для рассмотренного варианта поступления сигнала помехи на информационный вход 30 относительно синхронизирующих сигналов длительность .сигнала помехи, которая еще не воспринимается устройством, достигает величины, равной длительности разрешаиицего сигнала на выходе элемента НЕ 9 и величины паузы между разрешающими сигналами на указанном выходе. Это обусловлено тем, что установка триггера 5 отсечки входного сигнала в состояние 1 сигналом с выхода элемента И 24 может произойти в момент окончаний процесса формирования разрешающего сигнала на третьем выходе дешифратора 27, т.е. в момент формирования заднего фронта сигнала на этом выходе. При различных вариантах расфазировки входного сигнала на информационном входе 30 устройства относительно син хронизирующих сигналов на выходе эле мента НЕ 9 длительность сигнала помехи на информационном входе 30 устройства минимальна в случае, если пе редний фронт сигнала помехи совпадает с задним фронтом разрешающего сигнала на выходе элемента НЕ 9, Максимальная длительность сигнала помехи, который еще не воспринимается устройством, не превышает длитель ности разрешающего сигнала на выходе элемента НЕ 9 и длительности двух пауз между разрешающими сигналами на указанном выходе. Это происходит в случае, если сигнал помехи .поступает на информаци рнный вход 30 устройства в тот момент, когда сигнал на выходе элемента НЕ 9 становится запрещающим и длительность сигнала помехи не пре вышает сумму длительностей разрешающего сигнала на выходе элемента НЕ И.двух пауз между разрешающими сигналами на указанном выходе. Функцио нирование устройства в этом случае осуществляется следующим образом. Сначала устанавливается в состояние 1 триггер 1 записи поступающи на информационный вход 30 устройства сигналом. Установка в состояние 1 триггера 7 синхронизации при этом запрещена, поскольку сигнал на выход элемента НЕ 9 является запрещающим для элемента И 21. После того, как сигнал на выходе элемента НЕ 9 становится разрешающим, триггер 7 синх ронизации устанавливается в состояние 1 сигналом с выхода элемента И 21. При этом подготавливается эле мент И 20, через который сигнал про ходит на вход элемента НЕ 10 и далее на входы счетчика 26 и дешифратора 27 в паузе между разрешающим сигналами на выходе элемента НЕ 9, т.е. при появлении (разрешающего сиг нала на выходе элемента НЕ 8. Если к этому моменту времени сиг нёш помехи на информационном входе 30 устройства отсутствует ипи заканчивается его формирование, то на выходе элемента НЕ 14 сигнал становится разрешающим, в связи с этим сигнал от третьего выхода дешифратора 27 проходит через элемент И 24 для установки в состояние 1 триггера 5 отсечки входного сигнала. Сигнал с нулевого выхода триггера 5 отсечки входного сигнала закрывает элемент И 17 и вызывает состояние О триггеру 2 хранения. После этого начинается установка в состояние О, триггера 1 записи, триггера 5 отсечки входного сигнала, триггера 7 синхронизации и счетчика 26 как рассмотрено выше. В связи с тем, что селекция входного сигнала по длительности в устройстве зависит от момента поступления сигнала помехи на информационный вход 30 устройства, минимальная длительность полезных сигналов, поступающих на информационный вход 30 устройства, должна быть не меньше длительности разрешающего сигнала на выходе элемента НЕ 9 и длительности двух пауз между разрешающими сигналами на указанном выходе. Таким образом, предлагаемое устройство за счет введения десятого и одиннадцатого элементов И 24, 25 и седьмого элемента НЕ 14 позволяет исключить влияние на его работоспособность кратковременных помех, поступающих на информационный вход 30 устройства с длительностью, равной С О,5-1,5)Т , где Т - период следования синхронизирующих сигналов. Тем самым повышается помехозащищенность, а следовательно, и надежность работы устройства в тех случаях, когда к информационному входу 30 устройства подключается, например, линия связи или устройство-, на выходе которого возможно формирование кратковременных помех. Формула изобретения Устройство для синхронизации сигналов по авт.св. № 669347, отличающееся тем, что, с целью повышения надежности устройства, в него введены десятый и одиннадцатый элементы И и седьмой элемент НЕ, причем информационный вход устройства соединен через седьмой элемент НЕ с первым входом десятого элемента И, второй вход которого подключен к третьему выходу дешифратора, а выход- к дополнительному единичному входу триггера отсечки входного сигнала, вход синхронизации устройства соединен с первым входом одиннадцатого элемента И, второй вход которого соедивен с единичным: выходом триггера отсечки .входного сигнала, третий вход - к нулевому выходу триггера вьвдачи,- четвертый вход - к нулевому выходу триггера отсечки мажоритарного сигнала, а выход - к дополнительному нулевому входу триггера записи.

Источники информации, принятые во внимание при экспертизе

1. Авторское свлщетельство СССР 669347, кл. G 06 F 1/04, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации сигналов | 1977 |

|

SU669347A1 |

| Устройство для мажоритарного выбора сигналов | 1989 |

|

SU1656539A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1711167A1 |

| Устройство для сдвига информации | 1989 |

|

SU1607017A2 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство для контроля и восстановления микропроцессорной системы | 1985 |

|

SU1317441A1 |

| Трехканальное устройство для управления синхронизацией микропроцессорной системы | 1985 |

|

SU1352475A1 |

| Устройство для мажоритарного выбора сигналов | 1988 |

|

SU1619278A1 |

| Устройство для приема последовательного кода | 1986 |

|

SU1390625A2 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1989 |

|

RU1819116C |

Авторы

Даты

1981-09-30—Публикация

1980-01-18—Подача