Изобретение относится к области вычислительной техники, может быть использовано в управляющих вычислительных системах и является усовер- шенствованием устройства по основному авт.св. N 1322246.

Цель изобретения - расширение функциональных возможностей за счет обеспечения формирования пакетов им- пульсов с переменным числом импульсов в пакете и переменным периодом следования пакетов.

На фиг.1 представлена блок-схема таймера; на фиг,2 - схема формирова- теля счетного импульса.

Таймер содержит первый счетчик 1, группу 2 информационных выходов, элемент И-НЕ 3, первый элемент НЕ 4, выход 5 сигнала ответа, вход 6 внеш- него тактового генератора, вход 7 разрешения записи команд, группу 8 входов задания длительности выходных импульсов, второй регистр 9, вход 10 разрешения записи данных, формирователь 11 сигнала перезаписи, выход 12 прерывания, первый регистр 13, первый коммутатор 14, формирователь 15 счетного импульса, мультиплексор 16, одновибратор 17, второй элемент НЕ 18, первый счетный триггер 19, элемент ИЛИ 20, вход 21 разрешения чтения, выход 22 импульсной последовательности, тактовый генератор 23, вход 24 разрешения записи в третий регистр, третий регистр 25, второй коммутатор 26, третий элемент НЕ 27, второй счетный триггер 28, второй формирователь 29 сигнала перезаписи, второй счетчик 30, эле- мент И 31, выход 32 пакетов импульсов ,

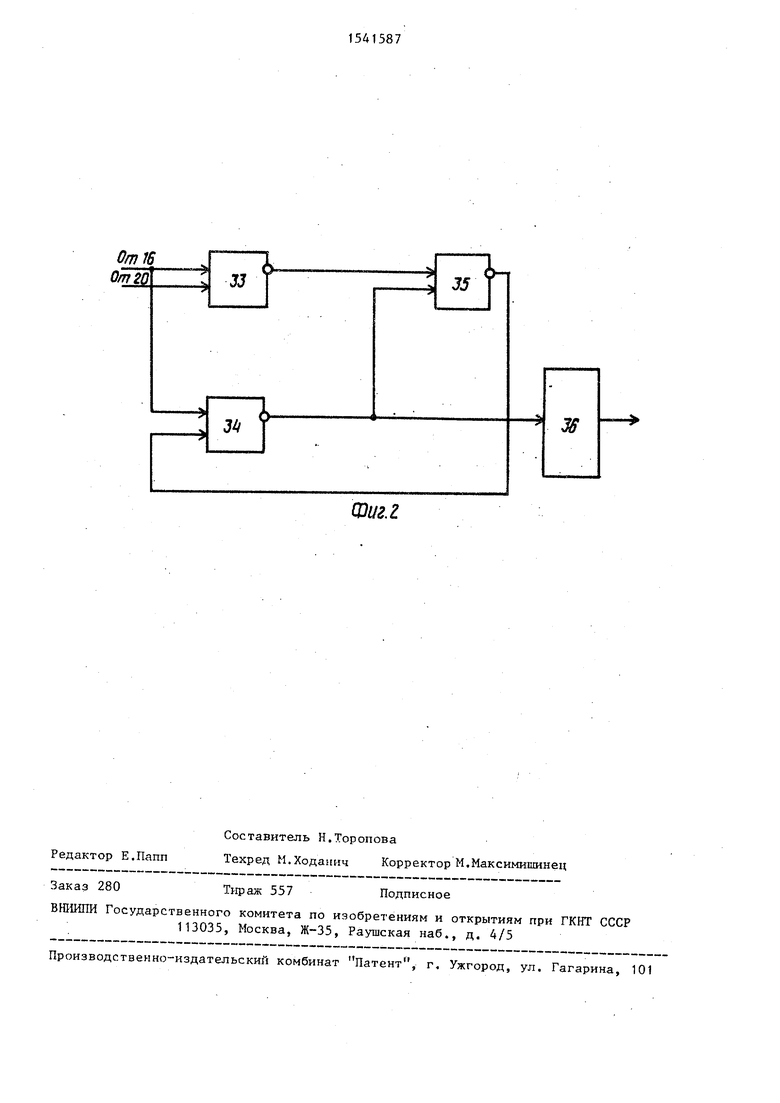

Формирователь 15 счетного импульса содержит элементы И-НЕ 33-35, одновибратор 36 .

Таймер работает следующим образом Режим I. Таймер работает в режиме отсчета временного интервала так же, как в основном изобретении.

Режим IT. Если необходимо получи непрерывную импульсную последователность с регулируемыми длительностью импульса и периодом следования, а такж пакеты импульсов из этой импульсной поледовательности с регулируемыми числом импульсов в пакете и периодом следования пакетов, в регистр 9 зансят цифровые значения длительности импульса и паузы, а в третий регист

5

0 5 Q Q

45

5

50

55

25 заносят цифровые значения количества импульсов в пакете и паузы меж;гу пакетами. В зависимости от состояния выходов счетных триггеров 19 и 28 в первый и второй счетчики 1 и 30 соответственно будет записано сначала либо значение длительности импульса, число импульсов в пакете, либо значение паузы. Если на прямом выходе счетных триггеров 19 и 28 устанавливается при включении высокий потенциал (уровень логической 1), то в первом счетчике 1 по входу 10-разрешения записи данных записывается цифровое значение времени импульса, а во второй счетчик 30 по входу 24 разрешения записи данных записывается цифровое значение числа импульсов в пакете.

Первый счетчик 1 работает в режиме вычитания. Счетные импульсы поступают на счетный вход первого счетчика 1, после отсчета длительнбсти импульса на выходе переполнения счетчика появляется импульс, который попадает на выход 12 прерывания и через первый элемент НЕ 18 на счетный вход первого триггера 19.

Состояние прямого выхода первого триггера 19 изменяется. На инверсном выходе первого триггера 19 устанавливается уровень логической 1 и цифровое значение паузы через первый коммутатор 14 поступает на информационные входы первого счетчика 1 из второго регистра 9. Эта информация переписывается в первый счетчик 1 и с выхода 12 прерывания и цикл повторяется. Сформированная таким образом импульсная последовательность поступает на выход 22, а также на счетный вход второго счетчика 30 и на один из входов элемента И 31. Второй счетчик 30 также работает в режиме вычитания. Во время отсчета числа импульсов в пакете на прямом выходе второго счетного триггера 28 и втором входе элемента И 31 устанавливается уровень логической 1, и на выход 32 пакетов импульсов поступает определенное число импульсов, определяемое цифровым кодом. После отсчета чи«ла импульсов в пакете на выходе переполнения второго счетчика 30 появляется импульс, который устанавливает через элемент НЕ 27 инверсный выход второго счетного триггера 28 в состояние логической 1 и цифро515

вое значение паузы между пакетами через второй коммутатор 26 поступает на информационные входы второго счетчика 30 из третьего регистра 25. На прямом выходе второго счетного триггера 28 устанавливается уровень логического О и тем самым прекращается поступление импульсов на выход 32 пакетов импульсов. Таким образом, формирование пакета импульсов закончено. После отсчета паузы между пакетами цикл повторяется.

При наличии импульса на входе 21 разрешения чтения или импульса, поступившего с выхода 12 прерывания, и импульса, поступившего через мультиплексор 16, формирователь 15 счетного импульса ждет окончания импульса на входе 21, после чего формирует счетный импульс, изменяющий- состояние первого счетчика 1.

При поступлении сигнала на входе 21 разрешения чтения во время импульса на выходе формирователя 15 счетного импульса элемент И-НЕ 3 блокирует сигнал на выходе 5 сигнала ответа до окончания счетного импульса. Сигнал на выходе 5 свидетельствует о наличии достоверной информации на выходах первого счетчика 1.

Формула изобретения

Таймер по авт.св. Р 1322246, отличающийся тем, что, с целью расширения функциональных возможностей, таймера за счет обеспечения формирования пакетов импульсов с переменным числом импульсов в пакете

0

5876

и с переменным периодом следования пакетов, в него дополнительно введены третий регистр, второй коммута- тор, третий элемент НЕ, второй счетный триггер, второй формирователь сигнала перезаписи, второй счетчик и элемент И, выход которого является выходом пакетов импульсов таймера,

Q первый вход элемента И соединен со счетным входом второго счетчика и с прямым выходом первого счетного триггера, второй вход элемента И соединен с первым управляющим входом второго

коммутатора и с прямым выходом второго счетного триггера, инверсный выход которого соединен с.вторым управляющим входом второго коммутатора, группа информационных выходов которого соединена с группой информационных входов второго счетчика, вход разрешения записи которого соединен с выходом второго формирователя сигнала перезаписи, выход переполнения второго счетчика соединен с входом второго элемента НЕ и с первым входом второго формирователя сигнала перезаписи, второй вход которого соединен с входом разрешения записи третьего регистра и с входом разрешения записи первого регистра, причем группа информационных входов третьего регистра соединена с группой информационных входов первого регистра, первая и вторая группы выходов третьего регистра соединены соответственно с первой и второй группами информационных входов второго коммутатора, выход третьего элемента НЕ соединен со счетным входом второго счетного триггера.

5

0

5

0

От 16

От го

| название | год | авторы | номер документа |

|---|---|---|---|

| Таймер | 1986 |

|

SU1322246A1 |

| Таймер | 1988 |

|

SU1531081A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 1998 |

|

RU2144267C1 |

| Таймер | 1990 |

|

SU1732338A2 |

| Таймер | 1983 |

|

SU1142822A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2000 |

|

RU2179787C1 |

| Таймер | 1989 |

|

SU1626250A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ ПО РАДИОКАНАЛУ | 2001 |

|

RU2211540C2 |

Изобретение относится к области вычислительной техники и может быть использовано в управляющих вычислительных системах. Отличительной особенностью таймера является то, что он работает как в режиме таймера, так и в режиме формирования непрерывной импульсной последовательности с одновременным формированием из этой последовательности пакетов импульсов. Длительность импульсов, период их следования, а также число импульсов в пакете и период следования пакетов регулируются цифровым кодом. Целью изобретения является расширение функциональных возможностей за счет обеспечения формирования пакетов импульсов с переменным числом импульсов в пакете и с переменным периодом следования пакетов. Поставленная цель достигается за счет введения третьего регистра 25, второго коммутатора 26, третьего элемента НЕ 27, второго счетного триггера 28, формирователя 29 сигнала перезаписи, второго счетчика 30, элемента И 31. 2 ил.

J4

Редактор Е.Папп

Составитель Н.Торопова

Техред М.Ходанич Корректор М.Максимишинец

Заказ 280

Тираж 557

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

3S

Сии г. г

Подписное

| Таймер | 1986 |

|

SU1322246A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-07—Публикация

1988-05-25—Подача