ё

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2024920C1 |

| УСТРОЙСТВО ДЛЯ ОТСЧЕТА ВРЕМЕНИ | 1990 |

|

RU2079165C1 |

| Устройство для отсчета времени | 1990 |

|

SU1817085A1 |

| Таймер | 1986 |

|

SU1310792A1 |

| Устройство для регистрации неисправностей | 1986 |

|

SU1377858A1 |

| Таймер | 1985 |

|

SU1357939A1 |

| Таймер | 1988 |

|

SU1531081A1 |

| Устройство для сопряжения интерфейсов ввода-вывода с регистратором | 1987 |

|

SU1413636A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Устройство для регистрации неисправностей | 1986 |

|

SU1429116A1 |

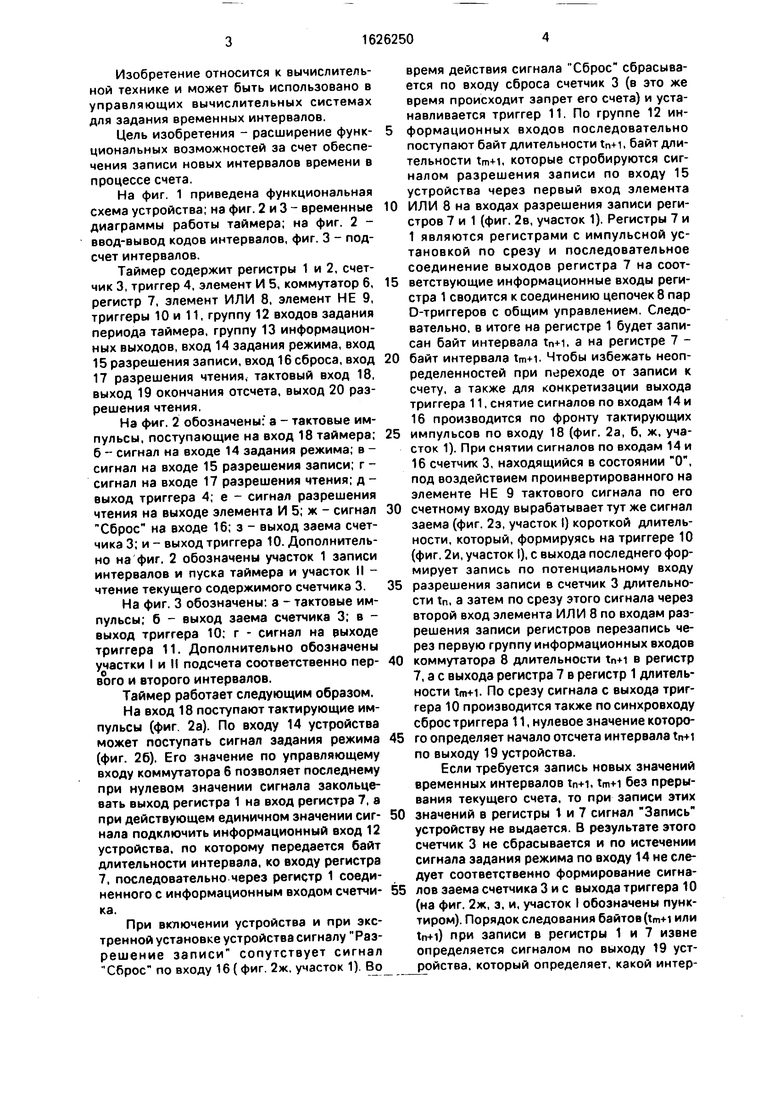

Изобретение относится к вычислительной технике и может быть использовано в управляющих вычислительных системах для задания временных интервалов. Отличительной особенностью таймера является то, что он автономно просчитывает два предварительно задаваемых интервала, выдает признак просчитываемого интервала и при необходимости производит экстренные установки интервалов. Целью изобретения является расширение функциональных возможностей за счет обеспечения записи новых интервалов времени в процессе счета. Цель достигается за счет введения коммутатора 6, регистра 7, элемента ИЛИ 8, элемента НЕ 9, триггера 10, счетного триггера 11. 3 ил.

О

ю ( ю ся о

Изобретение относится к вычислительной технике и может быть использовано в управляющих вычислительных системах для задания временных интервалов.

Цель изобретения - расширение функциональных возможностей за счет обеспечения записи новых интервалов времени в процессе счета,

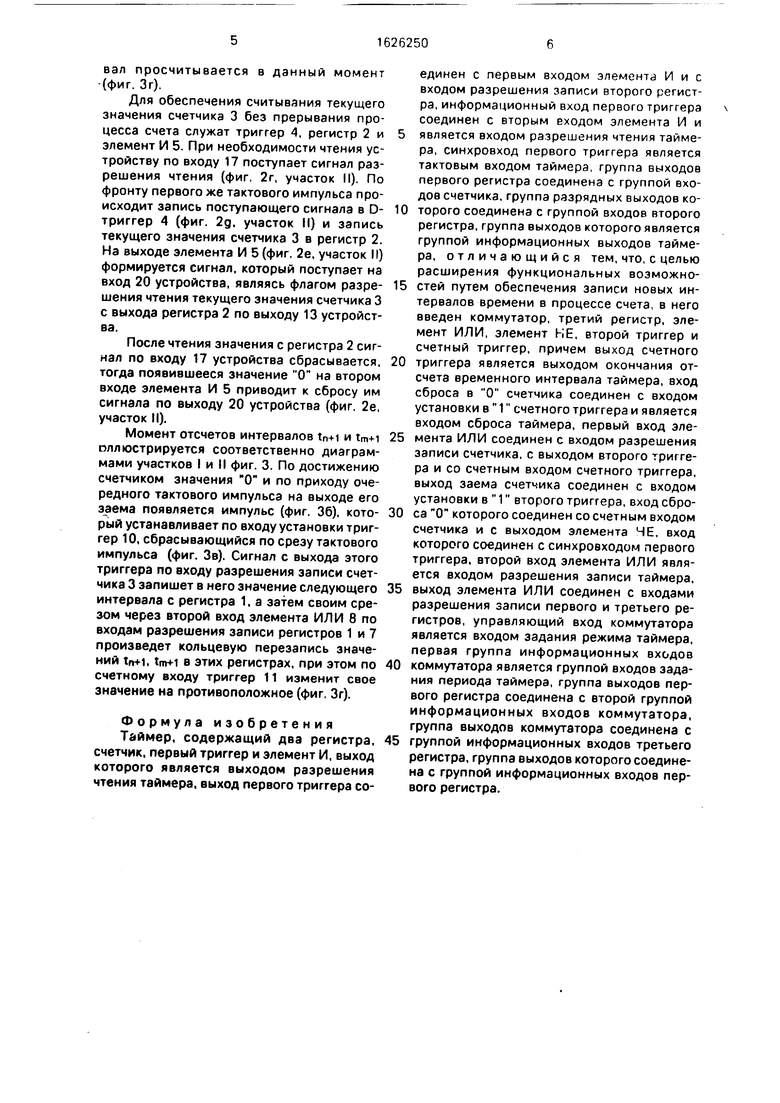

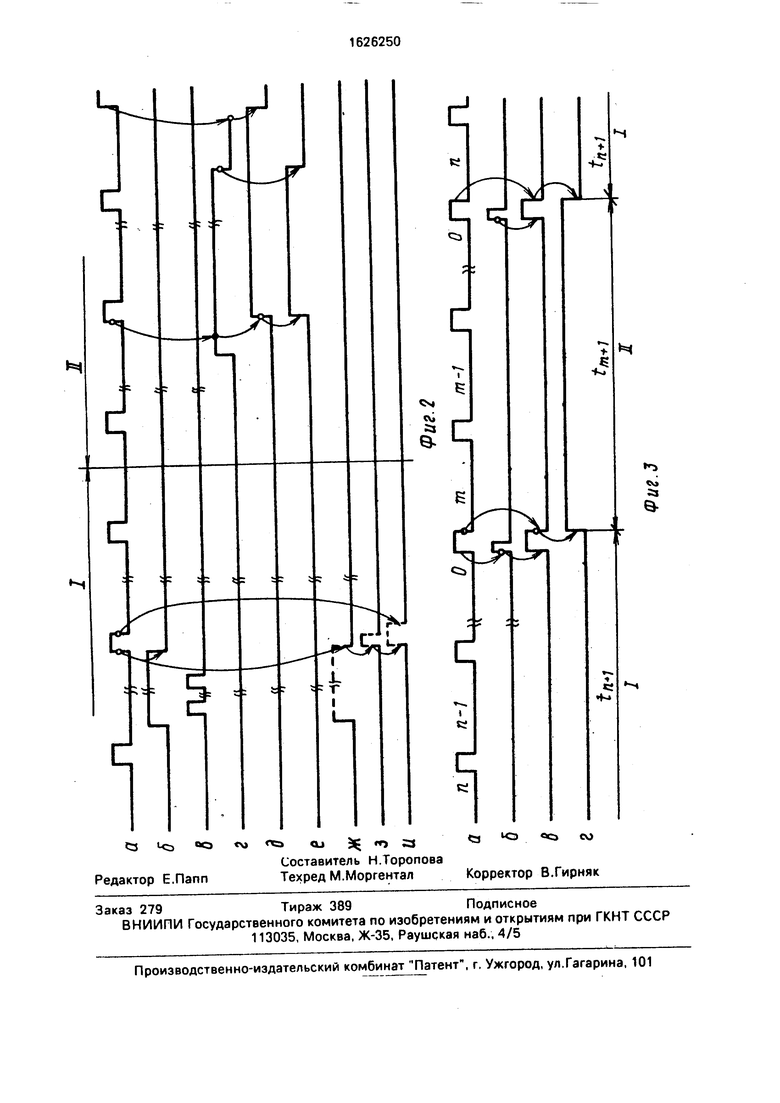

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 и 3 - временные диаграммы работы таймера; на фиг. 2 - ввод-вывод кодов интервалов, фиг. 3 - подсчет интервалов.

Таймер содержит регистры 1 и 2, счетчик 3, триггер 4, элемент И 5, коммутатор 6, регистр 7, элемент ИЛИ 8. элемент НЕ 9, триггеры 10 и 11, группу 12 входов задания периода таймера, группу 13 информационных выходов, вход 14 задания режима, вход 15 разрешения записи, вход 16 сброса, вход 17 разрешения чтения, тактовый вход 18, выход 19 окончания отсчета, выход 20 разрешения чтения.

На фиг. 2 обозначены: а - тактовые импульсы, поступающие на вход 18 таймера; б - сигнал на входе 14 задания режима; в - сигнал на входе 15 разрешения записи; г - сигнал на входе 17 разрешения чтения; д - выход триггера 4; е - сигнал разрешения чтения на выходе элемента И 5; ж - сигнал Сброс на входе 16; з - выход заема счетчика 3; и - выход триггера 10. Дополнительно на фиг. 2 обозначены участок 1 записи интервалов и пуска таймера и участок II - чтение текущего содержимого счетчика 3.

На фиг. 3 обозначены: а - тактовые импульсы; б - выход заема счетчика 3; в - выход триггера 10: г - сигнал на выходе триггера 11. Дополнительно обозначены участки I и II подсчета соответственно первого и второго интервалов.

Таймер работает следующим образом.

На вход 18 поступают тактирующие импульсы (фиг. 2а). По входу 14 устройства может поступать сигнал задания режима (фиг. 26). Его значение по управляющему входу коммутатора 6 позволяет последнему при нулевом значении сигнала закольцевать выход регистра 1 на вход регистра 7, а при действующем единичном значении сигнала подключить информационный вход 12 устройства, по которому передается байт длительности интервала, ко входу регистра 7, последовательно через регистр 1 соединенного с информационным входом счетчика.

При включении устройства и при экстренной установке устройства сигналу Раз- решение записи сопутствует сигнал Сброс по входу 16 (фиг. 2ж, участок 1). Во

время действия сигнала Сброс сбрасывается по входу сброса счетчик 3 (в это же время происходит запрет его счета) и устанавливается триггер 11, По группе 12 информационных входов последовательно поступают байт длительности tn-н, байт длительности tm-м, которые стробируются сигналом разрешения записи по входу 15 устройства через первый вход элемента

0 ИЛИ 8 на входах разрешения записи регистров 7 и 1 (фиг. 2в, участок 1). Регистры 7 и 1 являются регистрами с импульсной установкой по срезу и последовательное соединение выходов регистра 7 на соот5 ветствующие информационные входы регистра 1 сводится к соединению цепочек 8 пар D-триггеров с общим управлением. Следовательно, в итоге на регистре 1 будет записан байт интервала tn-и, а на регистре 7 0 байт интервала tm-н. Чтобы избежать неопределенностей при переходе от записи к счету, а также для конкретизации выхода триггера 11, снятие сигналов по входам 14 и 16 производится по фронту тактирующих

5 импульсов по входу 18 (фиг. 2а, б, ж, участок 1). При снятии сигналов по входам 14 и 16 счетчик 3, находящийся в состоянии О, под воздействием проинвертированного на элементе НЕ 9 тактового сигнала по его

0 счетному входу вырабатывает тут же сигнал заема (фиг. 2з, участок I) короткой длительности, который, формируясь на триггере 10 (фиг, 2и, участок I), с выхода последнего формирует запись по потенциальному входу

5 разрешения записи в счетчик 3 длительности tn, а затем по срезу этого сигнала через второй вход элемента ИЛИ 8 по входам разрешения записи регистров перезапись через первую группу информационных входов

0 коммутатора 8 длительности tn+t в регистр 7, а с выхода регистра 7 в регистр 1 длительности trtH-1. По срезу сигнала с выхода триггера 10 производится также по синхровходу сброс триггера 11, нулевое значение которо5 го определяет начало отсчета интервала tn+i по выходу 19 устройства.

Если требуется запись новых значений временных интервалов tn+1, W1 без прерывания текущего счета, то при записи этих

0 значений в регистры и 7 сигнал Запись устройству не выдается. В результате этого счетчик 3 не сбрасывается и по истечении сигнала задания режима по входу 14 не следует соответственно формирование сигна5 лов заема счетчика 3 и с выхода триггера 10 (на фиг. 2ж, э, и, участок I обозначены пунктиром). Порядок следования байтов (tm-м или tn+i) при записи в регистры 1 и 7 извне определяется сигналом по выходу 19 устройства, который определяет, какой интервал просчитывается в данный момент -(фиг. Зг).

Для обеспечения считывания текущего значения счетчика 3 без прерывания процесса счета служат триггер 4, регистр 2 и элемент И 5. При необходимости чтения устройству по входу 17 поступает сигнал разрешения чтения (фиг. 2г, участок II). По фронту первого же тактового импульса происходит запись поступающего сигнала в D- триггер 4 (фиг. 2д, участок II) и запись текущего значения счетчика 3 в регистр 2. На выходе элемента И 5 (фиг. 2е, участок II) формируется сигнал, который поступает на вход 20 устройства, являясь флагом разрешения чтения текущего значения счетчика 3 с выхода регистра 2 по выходу 13 устройства.

После чтения значения с регистра 2 сигнал по входу 17 устройства сбрасывается, тогда появившееся значение О на втором входе элемента И 5 приводит к сбросу им сигнала по выходу 20 устройства (фиг. 2е, участок II).

Момент отсчетов интервалов tn+i и wi оллюстрируется соответственно диаграммами участков I и II фиг. 3. По достижению счетчиком значения О и по приходу очередного тактового импульса на выходе его эаема появляется импульс (фиг. 36), который устанавливает по входу установки триггер 10, сбрасывающийся по срезу тактового импульса (фиг. Зв). Сигнал с выхода этого триггера по входу разрешения записи счетчика 3 запишет в него значение следующего интервала с регистра 1. а затем своим срезом через второй вход элемента ИЛИ 8 по входам разрешения записи регистров 1 и 7 произведет кольцевую перезапись значений tfH-1, tm-t-1 в этих регистрах, при этом по счетному входу триггер 11 изменит свое значение на противоположное (фиг, Зг).

Формула изобретения

Таймер, содержащий два регистра,

счетчик, первый триггер и элемент И, выход

которого является выходом разрешения

чтения таймера, выход первого триггера соединен с первым входом элемента И и с входом разрешения записи второго регистра, информационный вход первого триггера соединен с вторым входом элемента И и

является входом разрешения чтения таймера, синхровход первого триггера является тактовым входом таймера, группа выходов первого регистра соединена с группой входов счетчика, группа разрядных выходов которого соединена с группой входов второго регистра, группа выходов которого является группой информационных выходов таймера, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения записи новых интервалов времени в процессе счета, в него введен коммутатор, третий регистр, элемент ИЛИ, элемент КЕ, второй триггер и счетный триггер, причем выход счетного

триггера является выходом окончания отсчета временного интервала таймера, вход сброса в О счетчика соединен с входом установки в 1 счетного триггера и является входом сброса таймера, первый вход элемента ИЛИ соединен с входом разрешения записи счетчика, с выходом второго триггера и со счетным входом счетного триггера, выход заема счетчика соединен с входом установки в 1 второго триггера, вход сброса О которого соединен со счетным входом счетчика и с выходом элемента ЧЕ, вход которого соединен с синхровходом первого триггера, второй вход элемента ИЛИ является входом разрешения записи таймера,

выход элемента ИЛИ соединен с входами разрешения записи первого и третьего регистров, управляющий вход коммутатора является входом задания режима таймера, первая группа информационных входов

коммутатора является группой входов задания периода таймера, группа выходов первого регистра соединена с второй группой информационных входов коммутатора, группа выходов коммутатора соединена с

группой информационных входов третьего регистра, группа выходов которого соединена с группой информационных входов первого регистра.

«

з

В

| Таймер | 1983 |

|

SU1142822A1 |

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Счетчик времени | 1980 |

|

SU1357910A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-02-07—Публикация

1989-02-13—Подача