Изобретение относится к автоматике и измерительной технике и может быть использовано в качестве корректирующего звена импульсных и цифровых нелинейных систем управления, а также в составе цифровых измерительных средств для восстановления сигналов частотно-импульсных датчи- ков при выполнении динамических измерений.

Цель изобретения - упрощение устройства и повышение точности восстановления сигналов с измерительного преобразователя за счет компенсации его статических и динамических погрешностей.

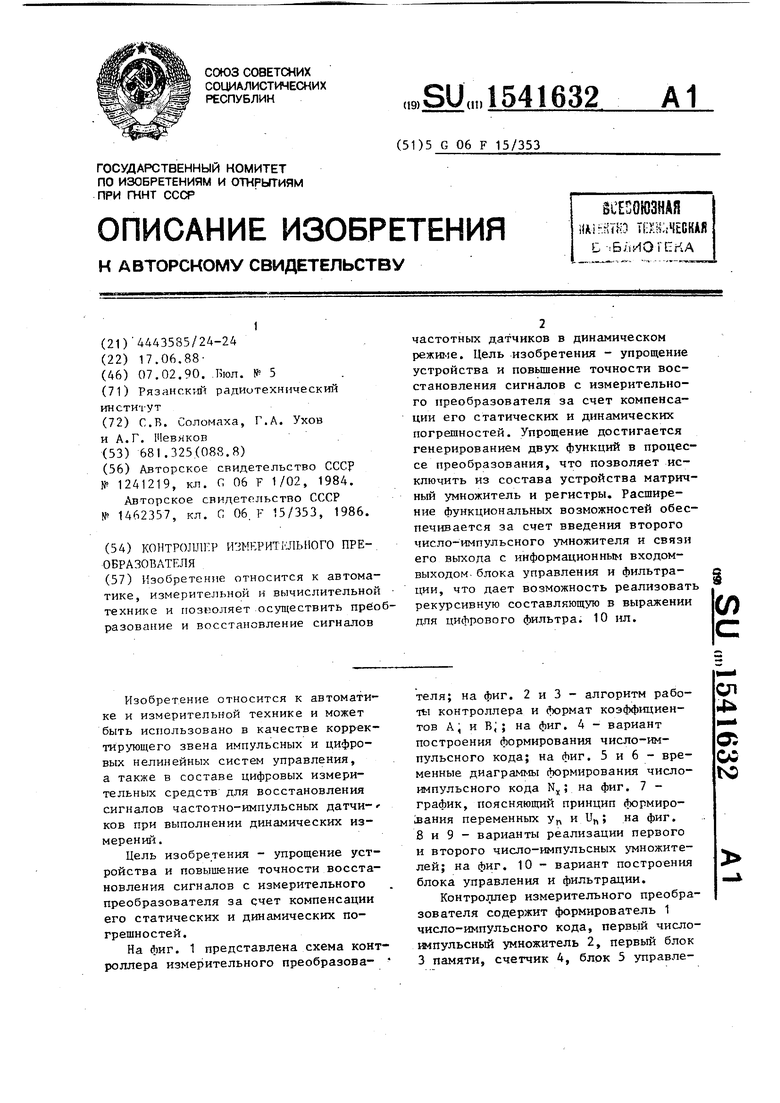

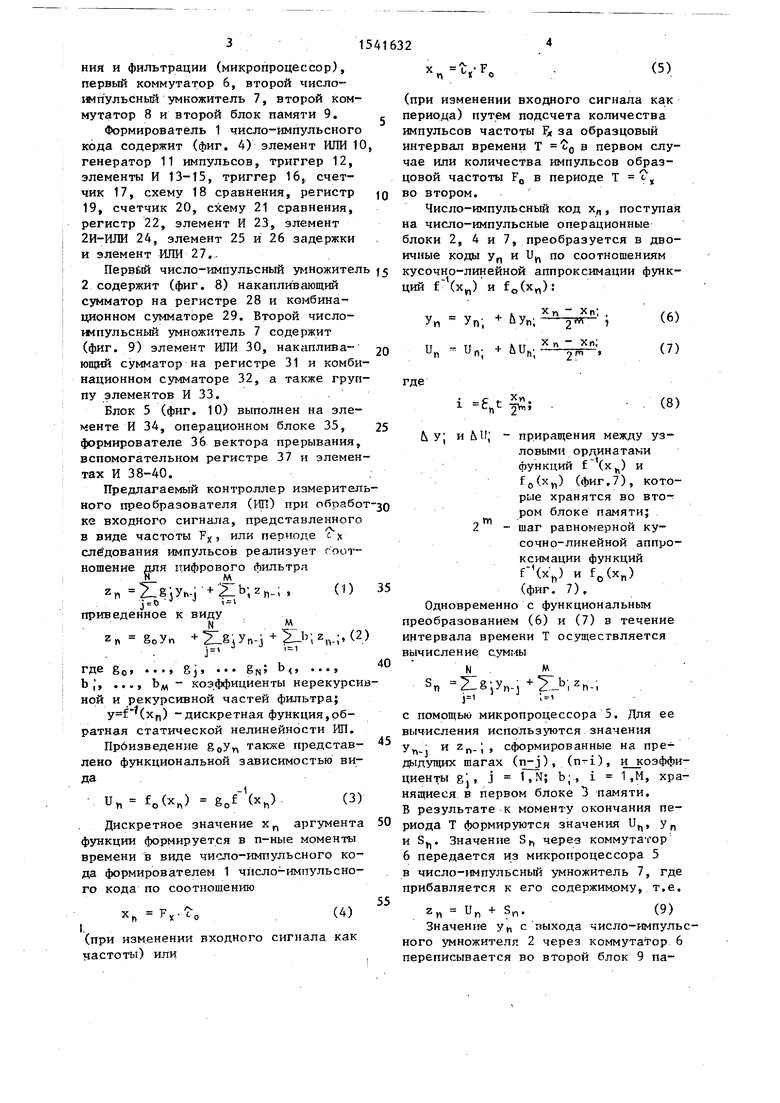

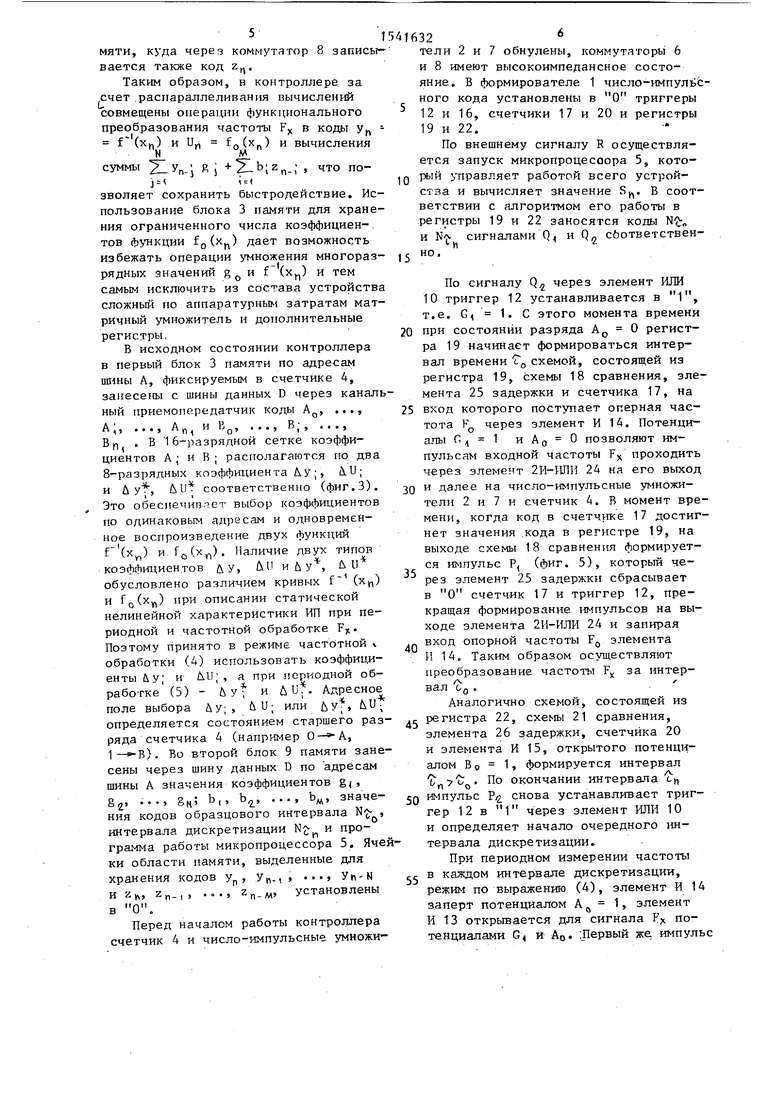

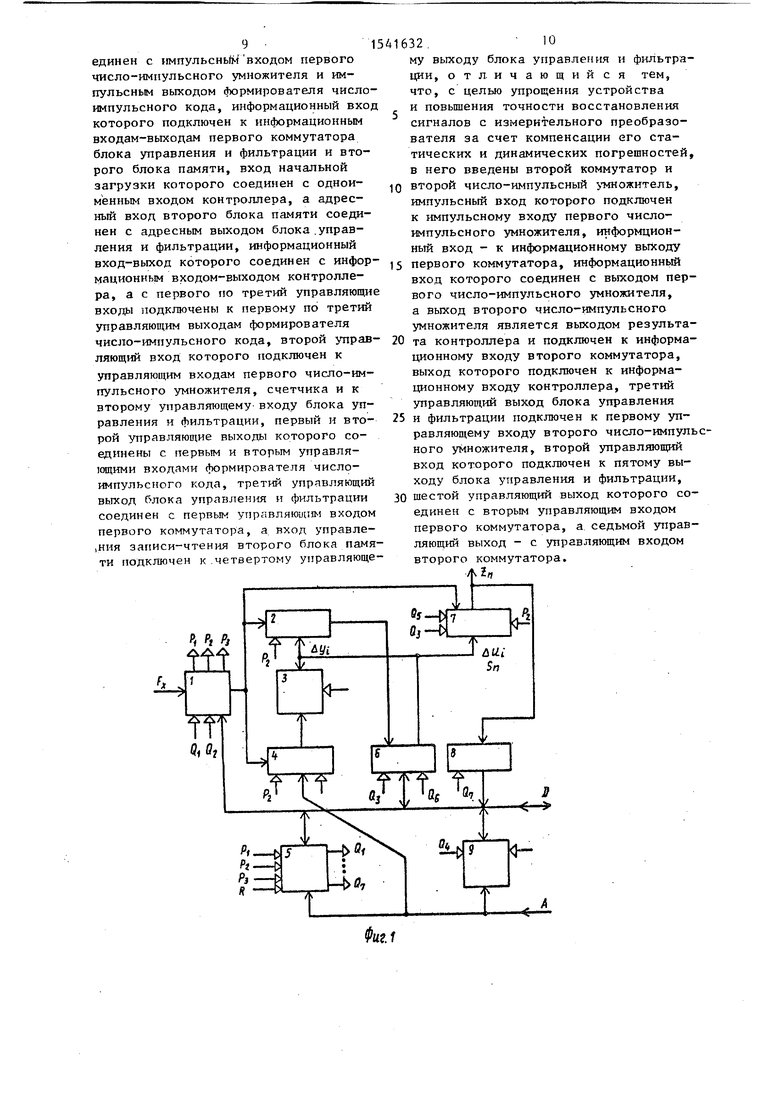

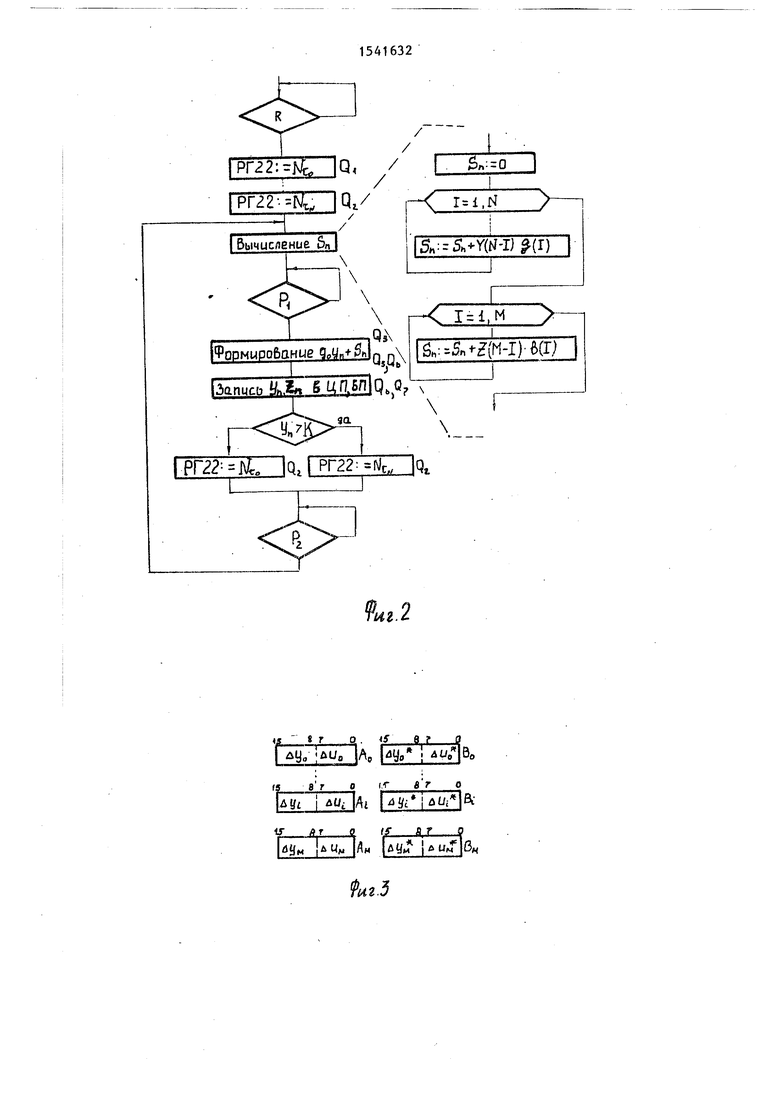

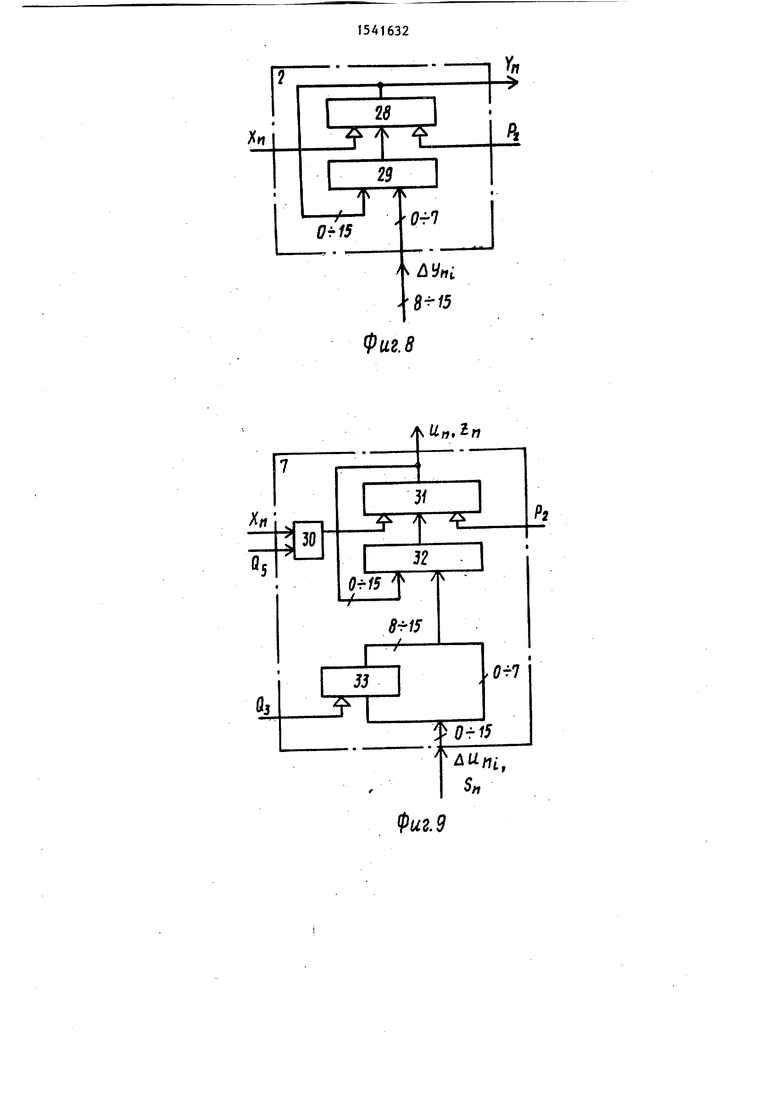

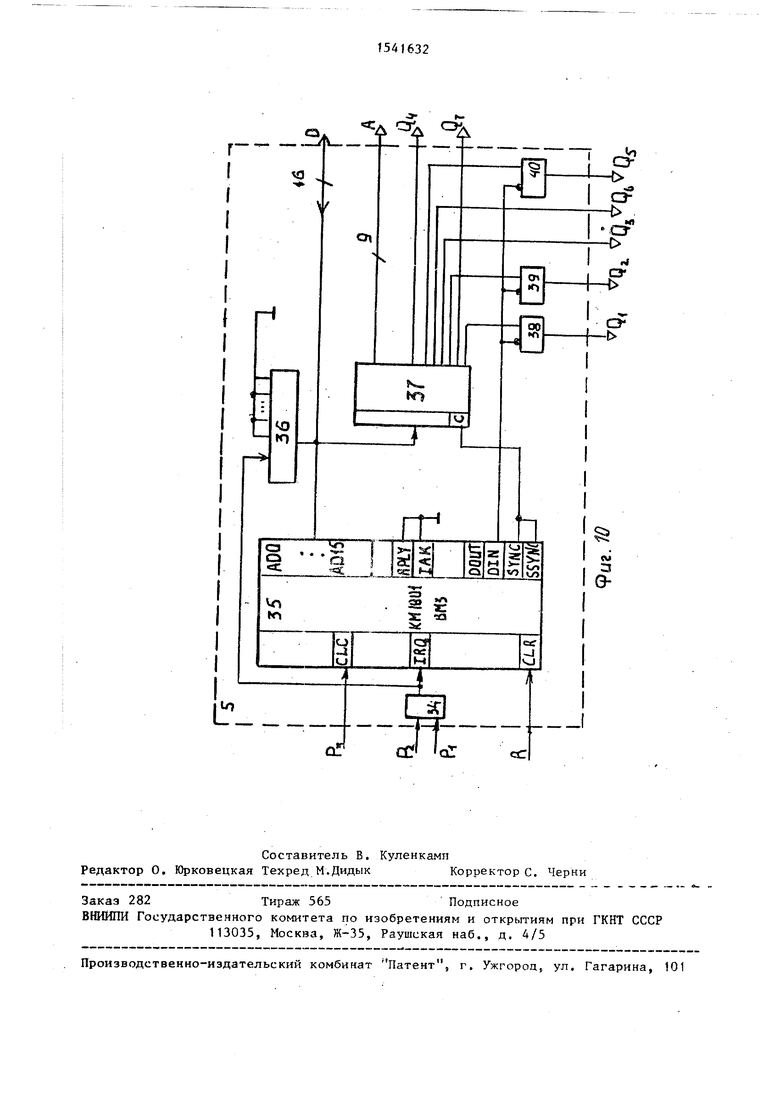

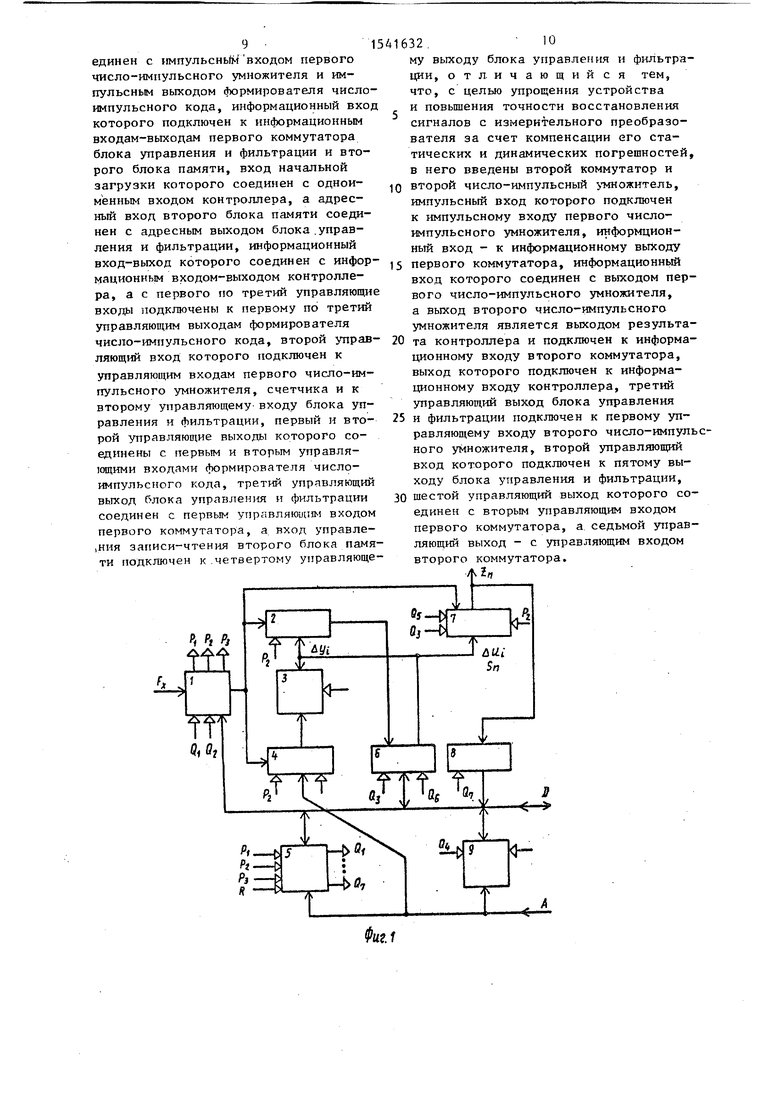

На фиг. 1 представлена схема контроллера измерительного преобразователя; на фиг. 2 и 3 - алгоритм работы контроллера и Аормат коэффициентов А; и Б;; на фиг. 4 - вариант построения формирования число-импульсного кода; на фиг. 5 и 6 - временные диаграммы формирования число- импульсного кода Nx; на фиг. 7 - график, поясняющий принцип формирования переменных уп и Un; на фиг. 8 и 9 - варианты реализации первого и второго число-импульсных умножителей; на фиг. 10 - вариант построения блока управления и фильтрации.

Контроллер измерительного преобразователя содержит формирователь 1 число-импульсного кода, первый число- импульсный умножитель 2, первый блок 3 памяти, счетчик 4, блок 5 управлеСЛ 4

5

со ю

ния и фильтрации (микропроцессор), первый коммутатор 6, второй число- импульсный умножитель 7, второй коммутатор 8 и второй блок памяти 9.

Формирователь 1 число-импульсного кода содержит (фиг. 4) элемент ИЛИ 10 генератор 11 импульсов, триггер 12, элементы И 13-15, триггер 16„ счетчик 17, схему 18 сравнения, регистр 19, счетчик 20, схему 21 сравнения, регистр 22, элемент И 23, элемент 2И-ИЛИ 24, элемент 25 и 26 задержки и элемент ИЛИ 27.

Первый число-импульсный умножител 2 содержит (фиг. 8) накапливающий сумматор на регистре 28 и комбинационном сумматоре 29. Второй число- шпульсный умножитель 7 содержит (фиг. 9) элемент ИЛИ 30, накаплива- ющий сумматор на регистре 31 и комбинационном сумматоре 32, а также группу элементов И 33.

Блок 5 (фиг. 10) выполнен на элементе И 34, операционном блоке 35, формирователе 36 вектора прерывания, вспомогательном регистре 37 и элементах И 38-40.

Предлагаемый контроллер измерителного преобразователя (ИП) при обоабо ке входного сигнала, представленного в виде частоты Fx, или периоде с х следования импульсов реализует соотношение для пифрового фильтра К м

(1)

zn Zl8;yh.i ,

J J ,l

приведенное к виду

N

2 п So

М

УП + 2L8jyn-j + X-b;zn-;(2

где g0gj, ... gN; Ь0 ...,

b |, ..., bw - коэффициенты нерекурсиной и рекурсивной частей фильтра;

(xn) -дискретная функция,обратная статической нелинейности ИП.

Прбизведение g0yn также представ- лено функциональной зависимостью вида

Urt- f0(xn) (xh) О)

Дискретное значение х п аргумента функции формируется в n-ные моменты времени в виде число-импульсного кода формирователем 1 число-импульсного кода по соотношению

(4)

I

х, ,.,

(при изменении входного сигнала как частоты) или

„-

f Fo

(5)

(при изменении входного сигнала как периода) путем подсчета количества импульсов частоты 7Л за образцовый интервал времени Т Ј0 в первом случае или количества импульсов образцовой частоты F0 в периоде Т Јх во втором.

Число-импульсный код х„, поступая на число-импульсные операционные блоки 2, 4 и 7, преобразуется в двоичные коды уп и Un по соотношениям кусочно-линейной аппроксимации функций (xw) и f0(xn):

. X у X п УП; + Ьуп; 1

- + ип;

х п - хп;

- fft;

(6)

(7) (8)

, w

fi у; и &U, - приращения между узловыми ординатами функций (xh) и f0(xn) (фиг.7), которые хранятся во втором блоке памяти; - шаг равномерной кусочно-линейной аппроксимации функций ) и f0(xn) (фиг. 7),

Одновременно с функциональным преобразованием (6) и (7) в течение интервала времени Т осуществляется вычисление суммы

N И

Sn Z jyn-j ,zh-,

с помощью микропроцессора 5. Для ее вычисления используются значения уп и , сформированные на предыдущих шагах (n-j), (n-i), и коэффциенты g

Г

1,N; b;

1,М, хранящиеся в первом блоке 3 памяти. В результате к моменту окончания периода Т формируются значения U, yn и S. Значение Sh через коммутатор 6 передается из микропроцессора 5 в число-импульсный умножитель 7, где прибавляется к его содержимому, т.е.

zn Un + Sn.(9)

Значение уп с выхода число-импульного умножителя 2 через коммутатор 6 переписывается во второй блок 9 па51

мяти, куда через коммутатор 8 записывается также код z.

Таким образом, в контроллере за счет распараллеливания вычислений совмещены операции функционального преобразования частоты Fx в коды yh - f(xn) и Un f0(xn) и вычисления

NАЛ

суммы gj +51Ь;2П ; , что поj -i

зволяет сохранить быстродействие. Использование блока 3 памяти для хранения ограниченного числа коэффициентов функции Ј0(х) дает возможность избежать операции умножения многоразрядных значений й0 и f (хп) и тем самым исключить из состава устройства сложный но аппаратурным затратам матричный умножитель и дополнительные регистры,

В исходном состоянии контроллера в первый блок 3 памяти по адресам шины А, фиксируемым в счетчике 4, занесены с шины данных D через канальный приемопередатчик коды AQ, ..., А, ..., A n и В Q, .., В j , Bfi .В 16-разрядной сетке коэффициентов А и В; располагаются по два 8-разрядных коэффициента &.У;, &U; и U у, UU соответственно (фиг.З). Это обеспечивает выбор коэффициентов по одинаковым адресам и одновременное воспроизведение двух функций (xn) и f0(xn). Наличие двух типов коэффициентов ду, &U и Л У, UU обусловлено различием кривых f (xn) и Г0(хЛ) при описании статической нелинейной характеристики ИП при пе- риодной и частотной обработке Рх. Поэтому принято в режиме частотной обработки (4) использовать коэффициенты Ау; и A.U; , а при иериодной обработке (5) - ЙУ и UU. Адресное поле выбора &У,, &U; или ЛУ &и, определяется состоянием старшего разряда счетчика 4 (например , ). Во второй блок 9 памяти занесены через шину данных D по адресам шины А значения коэффициентов g, ga, .., gH5 b,, Ъг, ..., Ьм, значения кодов образцового интервала , интервала дискретизации NЈ и программа работы микропроцессора 5. Ячейки области памяти, выделенные для хранения кодов ур , у„., , ..., У«-И и ah, zn.,, ..., zn.M, установлены в О.

Перед началом работы контроллера счетчик 4 и число-импульсные умножи

416326

тели 2 и 7 обнулены, коммутаторы 6 и 8 имеют высоконмпедансное состояние. В формирователе 1 число-импульсного кода установлены в О триггеры 12 и 16, счетчики 17 и 20 и регистры 19 и 22.

По внешнему сигналу R осуществляется запуск микропроцессора 5, кото- Q рыч управляет работой всего устройства и вычисляет значение Sh. В соответствии с алгоритмом его работы в регистры 19 и 22 заносятся коды NЈ0

и N сигналами Q, и (}„ сЬответствен- 1 и

15

но.

По сигналу Q2 через элемент ИЛИ 10 триггер 12 устанавливается в 1, т.е. G, 1. С этого момента времени

при состоянии разряда А0 0 регистра 19 начинает формироваться интервал времени Т0 схемой, состоящей из регистра 19, схемы 18 сравнения, элемента 25 задержки и счетчика 17, на

5 вход которого поступает оперная частота FQ через элемент И 14. Потенциалы О ,, 1 и А0 0 позволяют импульсам входной частоты Кх проходить через элемент 2И-1ШИ 24 на его выход

0 и далее на число-импульсные умножители 2 и 7 и счетчик 4. В момент времени, когда код в счетчике 17 достигнет значения кода в регистре 19, на выходе схемы 18 сравнения формируется импульс Р, (фиг. 5), который через элемент 25 задержки сбрасывает в О счетчик 17 и триггер 12, прекращая формирование импульсов на выходе элемента 2И-ИЛИ 24 и запирая

вход опорной частоты F0 элемента И 14. Таким образом осуществляют преобразование частоты Fx за интервал GO . Аналогично схемой, состоящей из

5 регистра 22, схемы 21 сравнения, элемента 26 задержки, счетчика 20 и элемента И 15, открытого потенциалом В0 1, формируется интервал уЈп-7Ј0. По окончании интервала ц.,

Q импульс РЈ снова устанавливает триггер 12 в 1 через элемент ИЛИ 10 и определяет начало очередного интервала дискретизации.

При периодном измерении частоты

5 в каждом интервале дискретизации, режим по выражению (4), элемент И 14 заперт потенциалом А 0 1, элемент И 13 открывается для сигнала F потенциалами G, и А0« Первый же импульс

частоты FK проходит на счетный вход триггера 16 и по заднему фронту устанавливает его потенциал G2 в 1, который позволяет импульсам опорной частоты F0 проходить через элемент 2И-ИЛИ 24 на его выход. Следующий импульс частоты Fx проходит через элементы И 23 и ИЛИ 27 в качестве управляющего сигнала P и по заднему фронту устанавливает в О триггера 16, запрещая прохождение опорной частоты F0 на выход элемента 2И-ИЛИ 24. Триггер 16 через элемент ИЛИ 10 сбрасывает триггер 12. Описанные процессы получения число-импульсного кода хп поясняются временными диаграммами (фиг, 5 и 6).

В процессе формирования число- Импульсный код хп поступает с выхода формирователя 1 число-импульсного кода на число-импульсные умножители 2 и 7 и счетчик 4. В число-импульсном умножителе 2, построенном на основе накапливающего сумматора (ре- гистр 28, комбинационный сумматор 29 фиг. 8), и в число-импульсном умножителе 7 (регистр 31 и комбинационны сумматор 32, дополнительные элементо ИЛИ 30 и группой элементов И 33, фиг 9) каждым импульсом кода хп прибавляются к предыдущему значению регистров 28 и 31 величины &v, и &U;/2lrY1 соответственно (делениг на 2т осуществлено путем подачи &у; и Ь U; на сумматоры 29 и 32 со сдвигом на m разрядов вправо). Величины &у;/2ти U;/2tn определяют единичные приращения Функций f (xn) и Ј0(х) на каждом i-м участке аппро- ксимации. Значение &у; путем подключения снимается со старших 8-15, a &Uj (за счет того, что Q-J 0) с младших 0-73 разрядов выхода блока 3 памяти. Переход от участка к участку и адресация значений &у; и & U; , которые выбираются из первого блока 3 памяти, осуществляются с помощью счетчика 4. Первые его m младших разрядов определяют длину участка аппроксимации и используются как делитель частоты на 2, реализующий соотношение (8), а следующие разряды являются адресом i и подаютс на адресный вход первого блока 3 па- мяти.

Таким образом, в регистрах 28 и 3 происходит развертывание функций (хм) и f0(xh) при измене -ия аргу™

. Q

0 5 0 0 5 Q

5

мента от 0 до х (фиг, 7) за интервал времени Ј„ . Одновременно в том же интервале времени Ј0 (после установки кодов NЈQ и NЈ-a в регистры 19 и 22) микропроцессором 5 выполняются арифметические операции для вычисления суммы Sn и перемещение в массиве Y(l) кодов yn., , yh г, .... , хранящихся в блоке 9 памяти, в соответствии с алгоритмом (фвиг. 2). Перемещение массива Y(I) необходимо для подготовки к расчету 3П4, в следующем (п+1)-м такте. Далее микропроцессор 5 переходит в режим ожидания сигнала Р . По окончании /cQ микропроцессор 5 продолжает свою работу и формирует сигналы О и , открывающие коммутатор 6 и группу элементов И 33 второго чиела-имиульеного умножителя 7 для подачи нэ накапливающий сумматор полного 16-разрядно го кода S, который прибавляется к содержимому регистра 31 сигналом Q, Затем осуществляется запись кода уа из регистра 28 первого число-импульсного умножителя 2 в ячейку уд второго бпока 9 памяти через коммутатор 6, Далее осуществляется запись в блок 9 памяти через коммутатор 8 значения кода zn. Направление передачи обеспечивается сигналом 0-j,

После записи кода . h в блок 9 памяти микропроцессор 5 снова переходит в режим ожидания второго импульса, по которому повторяется работа устройства, т.е. сбрасываются в О регистры 28 и 32 число-импульсных умножителей 2 и 7 и счетчик 4. Запуск программы микропроцессора 5 осуществляется через вектор прерывания, назначение которого продолжить программу (фиг, 2).

Формула изобретения

Контроллер измерительного преобразователя, содержащий первый число- импульсный умножитель, первый и второй блоки памяти, формирователь число- импульсного кода, счетчик, блок управления и фильтрации, первый коммутатор, информационный выход которого подключен к информационному входу первого число-импульсного умножителя и к информационному выходу первого блока памяти, адресный вход которого соединен с информационным выходом счетчика, счетный вход которого соединен с импульсным входом первого число-импульсного умножителя и им- пульсньм выходом формирователя число- импульсного кода, информационный вход которого подключен к информационным входам-выходам первого коммутатора блока управления и фильтрации и второго блока памяти, вход начальной загрузки которого соединен с одноименным входом контроллера, а адресный вход второго блока памяти соединен с адресным выходом блока управления и фильтрации, информационный вход-выход которого соединен с информационным входом-выходом контроллера, ас первого по третий управляющие входы подключены к первому по третий управляющим выходам формирователя число-импульсного кода, второй управляющий вход которого подключен к управляющим входам первого число-импульсного умножителя, счетчика и к второму управляющему входу блока управления и фильтрации, первый и второй управляющие выходы которого соединены с первым и вторым управляющими входами формирователя число- импульсного кода, третий управляющий выход блока управления и фильтрации соединен с первым управляющим входом первого коммутатора, а вход управле- ,ния записи-чтения второго блока памяти подключен к четвертому управляющему выходу блока управления и фильтрации, отличающийся тем, что, с целью упрощения устройства и повышения точности восстановления сигналов с измерительного преобразователя за счет компенсации его статических и динамических погрешностей, в него введены второй коммутатор и

второй число-импульсный умножитель, импульсный вход которого подключен к импульсному входу первого число- импульсного умножителя, информцион- ный вход - к информационному выходу

первого коммутатора, информационный вход которого соединен с выходом первого число-импульсного умножителя, а выход второго число-импульсного умножителя является выходом результа0 та контроллера и подключен к информационному входу второго коммутатора, выход которого подключен к информационному входу контроллера, третий управляющий выход блока управления

5 и фильтрации подключен к первому управляющему входу второго ч и ел о-импульсного умножителя, второй управляющий вход которого подключен к пятому выходу блока управления и фильтрации,

шестой управляющий выход которого соединен с вторым управляющим входом первого коммутатора, а седьмой управляющий выход - с управляющим входом второго коммутатора. bin

/

/

t

| название | год | авторы | номер документа |

|---|---|---|---|

| Контроллер измерительного преобразователя | 1987 |

|

SU1462357A1 |

| СПОСОБ РЕГУЛИРОВАНИЯ ЖИДКОСТНОГО РАКЕТНОГО ДВИГАТЕЛЯ И УСТРОЙСТВА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2085755C1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| СПЛАЙН-ИНТЕРПОЛЯТОР | 1997 |

|

RU2116668C1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Цифровой фильтр | 1985 |

|

SU1244786A1 |

| Устройство для определения технического состояния механизмов циклического действия | 1989 |

|

SU1686334A1 |

| Перестраиваемый цифровой фильтр с программируемой структурой | 2016 |

|

RU2631976C2 |

| Цифровой нерекурсивный фильтр | 1987 |

|

SU1429294A1 |

Изобретение относится к автоматике, измерительной и вычислительной технике и позволяет осуществить преобразование и восстановление сигналов частотных датчиков в динамическом режиме. Цель изобретения - упрощение устройства и повышение точности восстановления сигналов с измерительного преобразователя за счет компенсации его статических и динамических погрешностей. Упрощение достигается генерированием двух функций в процессе преобразования, что позволяет исключить из состава устройства матричный умножитель и регистры. Расширение функциональных возможностей обеспечивается за счет введения второго число-импульсного умножителя 7 и связи его выхода с информационным входом-выходом блока 5 управления и фильтрации, что дает возможность реализовать рекурсивную составляющую в выражении для цифрового фильтра. 10 ил.

РГ22:-М-Г|(3 /

,/

I Вычисление &nj

Q

s

Формыробание

Запись tt..i UJJjSQb Q

1РГ22;. IQ j РГ22 МС. Jq.

45 Г О У 8 Г

Ј„.о 1

,N

)Ј(Г)

rX . M --1

Q

s

&,, г(м-1)гсг;

г

.1

Utt.2

fk

OU1

PI

L™J

P. iiiiiiiiiiiiimmiiiiiiiiiniMiiiiiiiimii

IliUIIIIIIIMUntniHIl

4n

л

n

I

J

fu.5

0 Фиг 6

Ш | fr-fr i5 i

.

AUL I

1

I у II

I x« I I y .

л/,

A t --v- i+

пГП

ФигЛ

Л

п

Or 15

Xii

имв

«

30

/я

JF

15

0-1

/ ч

&Ущ 8+15

Фм.8

, 2W

ЗУ

g 7ч Я2

52 (г7ГТ

С

JJ

,0+1

, 5Л

/

«.

| Генератор функций | 1984 |

|

SU1241219A1 |

| Г, 06 F 1/02, 1984 | |||

| Контроллер измерительного преобразователя | 1987 |

|

SU1462357A1 |

| Г, 06 F 15/353, 1986. | |||

Авторы

Даты

1990-02-07—Публикация

1988-06-17—Подача