Изобретение относится к области цифрового управления объектами авиационной техники, техники обработки и передачи дискретной информации в таких системах и наиболее эффективно может быть использовано для создания цифровых фильтров различного типа и структуры, выполнения цифровой фильтрации, формирования потоков с определенными свойствами, а также при построении цифровых контуров управления непрерывными объектами.

Известно, что в аппаратуре дискретной автоматики, вычислительной техники и техники передачи информации широко используются авторегрессионные цифровые фильтры и фильтры с конечным импульсным откликом (КИО), которые реализованы на регистровых структурах и сумматорах сигналов с определенными весовыми коэффициентами, местоположение и включение которых определяют тип цифрового фильтра, со структурой, определяемой разностным уравнением или Z-передаточной функцией [1, стр. 45]. Однако при изменении в процессе работы частоты f0 периодического поступления обрабатываемой входной информации частотные свойства фильтра меняются, а при значительном изменении такая фильтрация может привести к неудовлетворительным результатам, если при этом не изменять - перестраивать параметры цифрового фильтра.

Авторегрессионные фильтры и фильтры с конечным импульсным откликом (КИО-фильтры), которые известны и реализованы как отдельные устройства, имеют жесткую структуру, определяемую типом фильтра и «фильтрующим» полиномом, которые для фильтров остаются неизменными. Применительно к фильтрам второго порядка в устройстве [3] приведена реализация программируемого цифрового фильтра, допускающая изменение свойств фильтра, в частности обеспечение устройством свойств фильтра низких частот, фильтра высоких частот и режекторного фильтра. Наиболее близким техническим решением является цифровой фильтр с программируемой структурой, содержащий, последовательно соединенные внешнее устройство настройки, блок хранения кода типа фильтра и блок фильтрации, выход внешнего устройство настройки соединен с входом блока хранения кода структуры фильтра, а через блок формирования тактовых импульсов - со вторым входом блока фильтрации [2] - ПРОТОТИП. Указанный прототип позволяет реализовать цифровые фильтры различного назначения и с различными свойствами, например авторегрессионные фильтры, фильтры с конечным импульсным откликом (КИО) и т.п

Однако при наличии в процессе работы нерасчетного изменения фактической частоты  относительно расчетной

относительно расчетной  частоты поступления входной информации, свойства фильтра, в частности частотные характеристики меняются, а при значительном изменении частоты фильтр может потерять требуемые функциональные свойства. В замкнутой цифровой системе управления непрерывным объектом это может привести к уменьшению запасов устойчивости и ухудшению качества процессов управления, а при определенном изменении

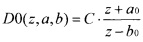

частоты поступления входной информации, свойства фильтра, в частности частотные характеристики меняются, а при значительном изменении частоты фильтр может потерять требуемые функциональные свойства. В замкнутой цифровой системе управления непрерывным объектом это может привести к уменьшению запасов устойчивости и ухудшению качества процессов управления, а при определенном изменении  возможна даже потеря устойчивости системы. Это можно показать на простейшем примере цифрового фильтра 1 порядка, описываемого z-передаточной функцией вида:

возможна даже потеря устойчивости системы. Это можно показать на простейшем примере цифрового фильтра 1 порядка, описываемого z-передаточной функцией вида:  ,

,

где а0, b0, С - числовые параметры звена.

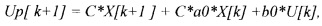

Данная Z - передаточная функция соответствует разностным уравнениям, связывающим вход X и выход U цифрового фильтра:

где а0, b0, С - параметры фильтра.

Пусть данный алгоритм цифрового управления (цифровой фильтр) реализуется с различными частотами:  - расчетная частота и

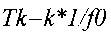

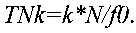

- расчетная частота и  - измененная частота, где параметр N определяет изменение частоты. При этом разностные уравнения и соответствующая программа реализации фильтра, будут одинаковыми, но моменты квантования разными - соответственно

- измененная частота, где параметр N определяет изменение частоты. При этом разностные уравнения и соответствующая программа реализации фильтра, будут одинаковыми, но моменты квантования разными - соответственно  и

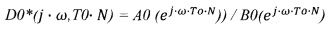

и  Частотная характеристики такого фильтра для частоты квантования

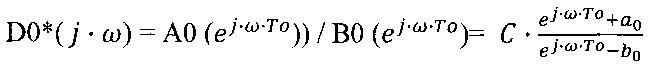

Частотная характеристики такого фильтра для частоты квантования  имеет вид:

имеет вид:

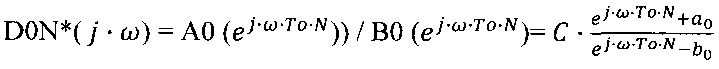

а для измененной частоты квантования  определится выражением:

определится выражением:

,

,

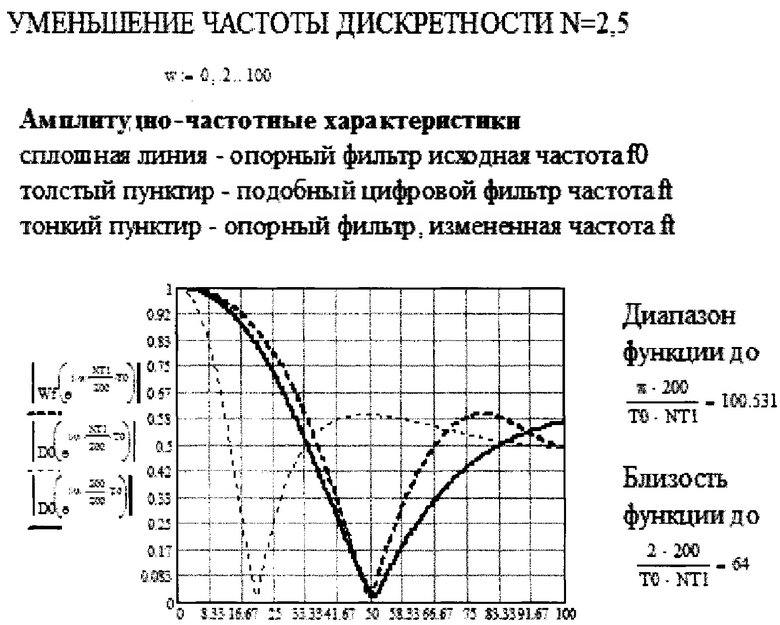

т.е. при изменении частоты квантования частотные свойства фильтра существенно меняются относительно расчетных свойств D0*(j⋅ω). Так, при a0=-0.97, b0=0.3 амплитудно-частотная характеристика может отличаться в два раза на определенных частотах.

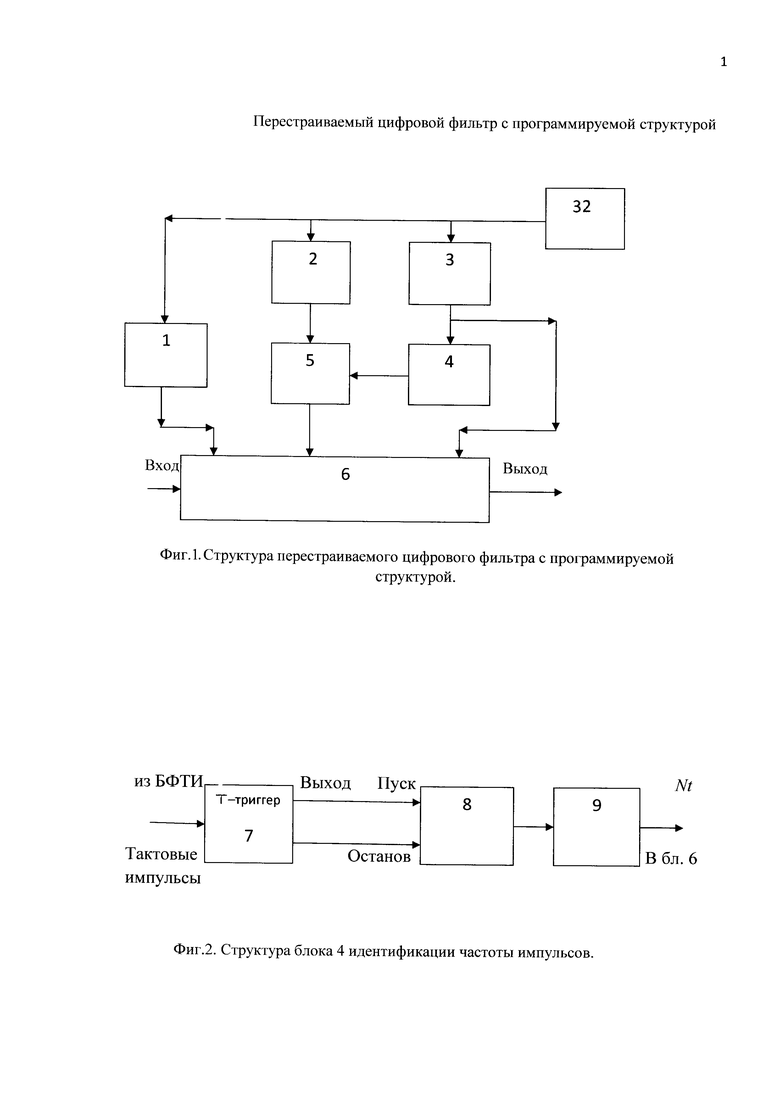

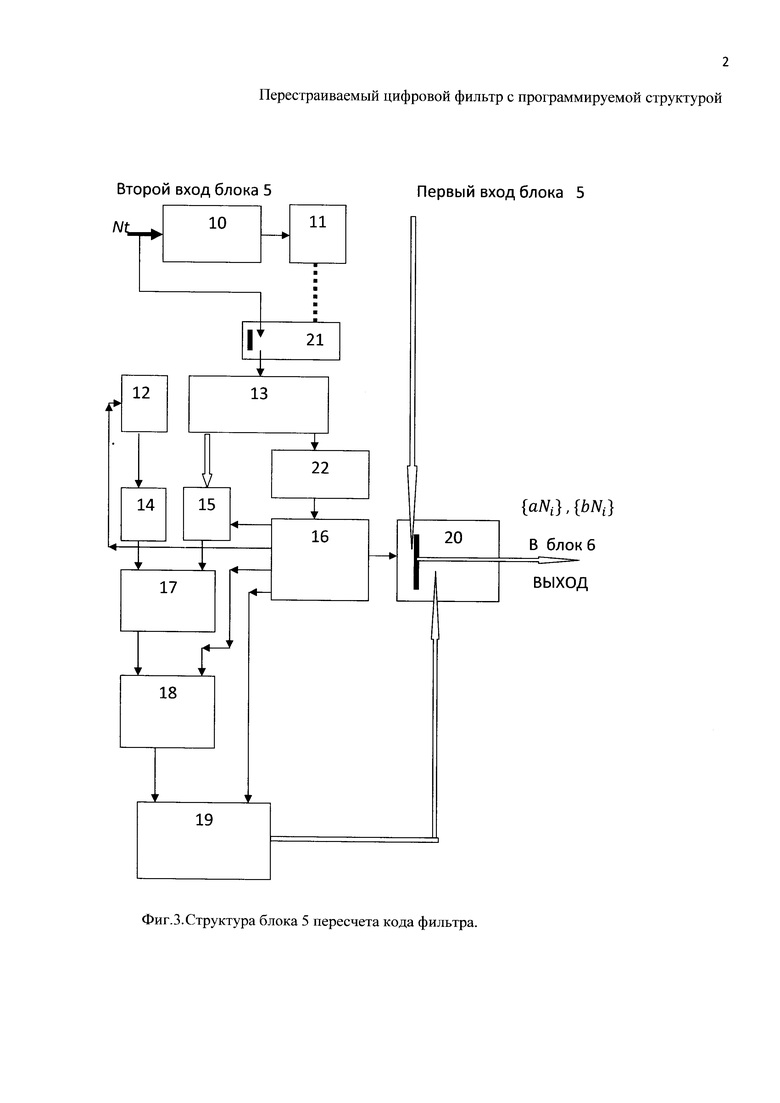

С целью исключения указанных недостатков известного фильтра предложенное техническое решение отличается тем, что перестраиваемый цифровой фильтр с программируемой структурой, дополнительно содержит блок идентификации частоты импульсов и блок пересчета кода фильтра, выход блока хранения кода структуры фильтра через блок пересчета кода фильтра соединен с третьим входом блока фильтрации, а выход блока формирования тактовых импульсов через блок идентификации частоты импульсов - со вторым входом блока пересчета кода фильтра, при этом блок идентификации частоты импульсов содержит Т-триггер, первый генератор импульсов и счетчик импульсов, причем вход блока идентификации частоты импульсов соединен через последовательно подключенные Т-триггер, первый генератор импульсов и счетчик импульсов с выходом блока идентификации частоты импульсов, а второй выход Т-триггера соединен со вторым входом первого генератора импульсов, кроме того, блок пересчета кода фильтра содержит сумматор, реле с первым переключателем, блок элементов памяти, вычислитель параметров пересчета, регистр множителя, мультиплексор, счетчик-коммутатор, умножитель, сумматор-накопитель, память вектора параметров, второй генератор импульсов, второй переключатель, второй вход блока пересчета кода фильтра соединен со входом реле через сумматор, а через последовательно подключенные первый переключатель, вычислитель параметров пересчета, мультиплексор, умножитель, сумматор-накопитель, память вектора параметров и второй переключатель с выходом блока пересчета кода фильтра, выход блока элементов памяти через регистр множителя соединен со вторым входом умножителя, второй выход вычислителя параметров пересчета соединен через второй генератор импульсов со входом счетчика-коммутатора, а первый, второй третий и четвертый выходы счетчика-коммутатора соединены соответственно со входом блока элементов памяти, вторыми входами мультиплексора, сумматора-накопителя и блока памяти вектора параметров, пятый выход счетчика-коммутатора соединен со вторым входом второго переключателя, третий вход которого подключен к первому входу блока пересчета кода фильтра.

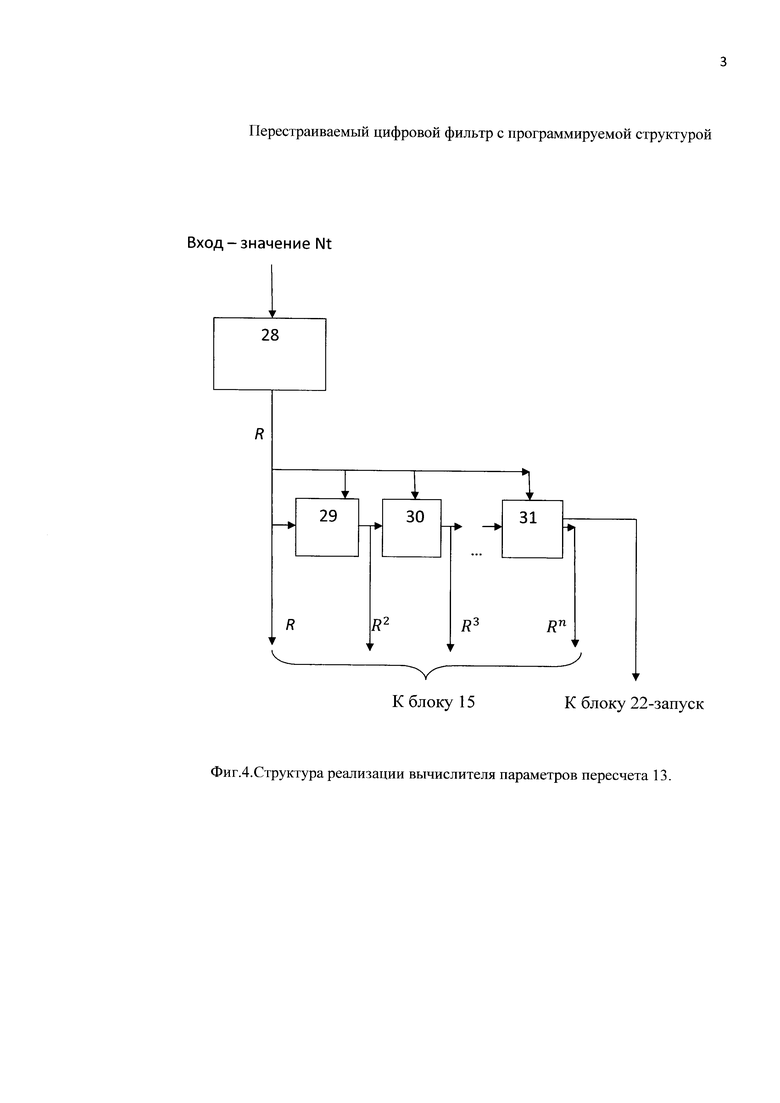

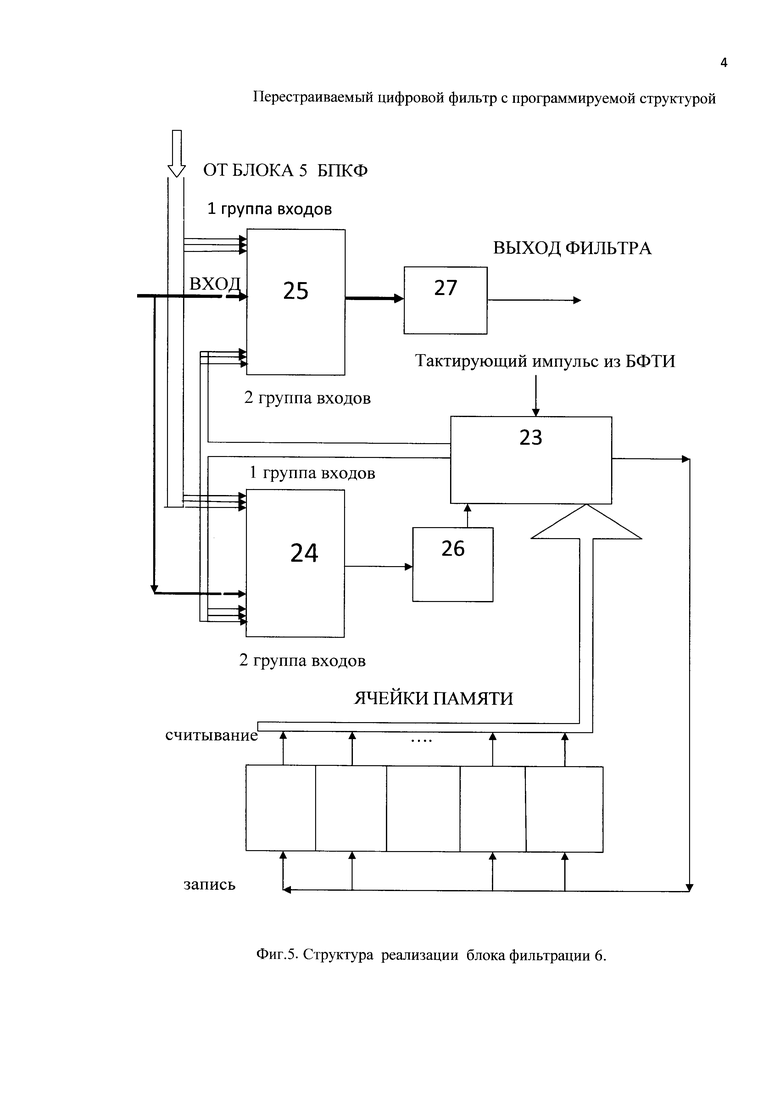

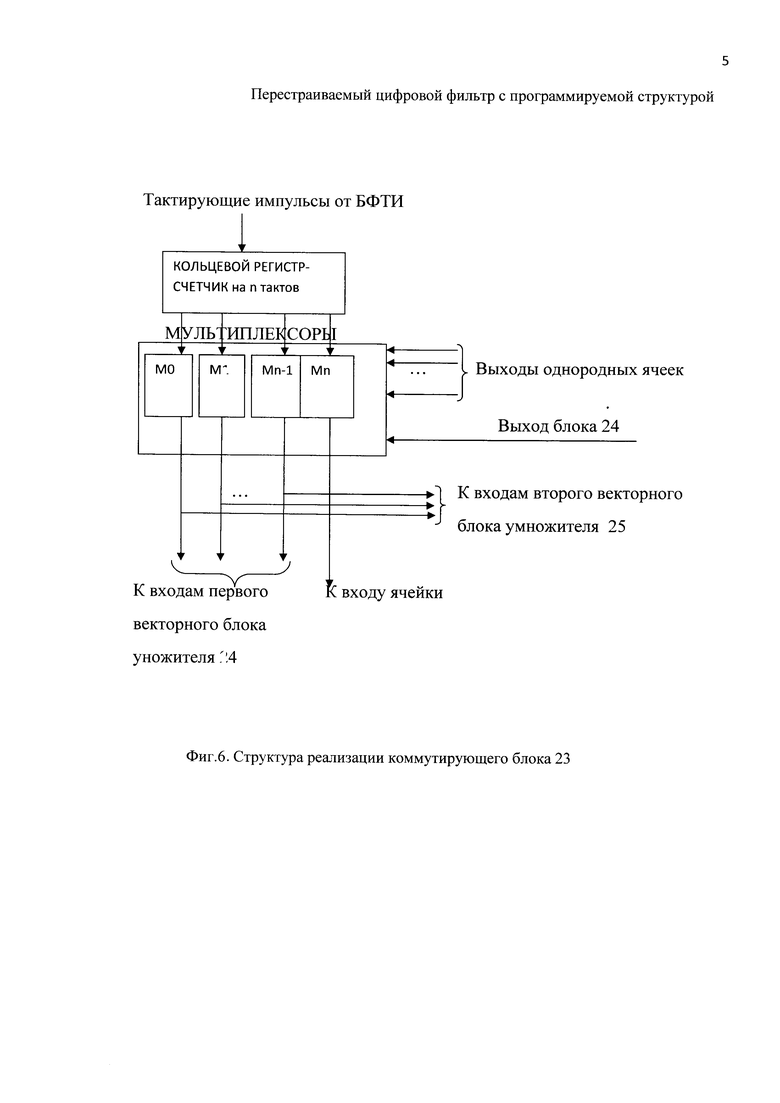

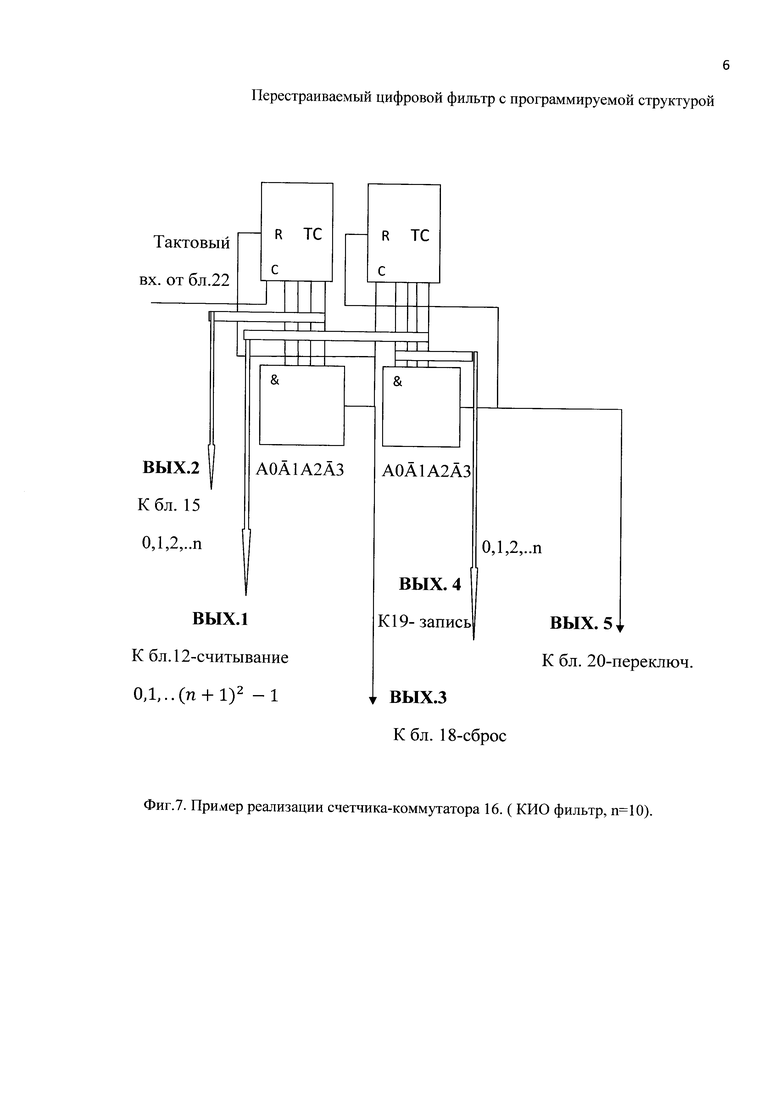

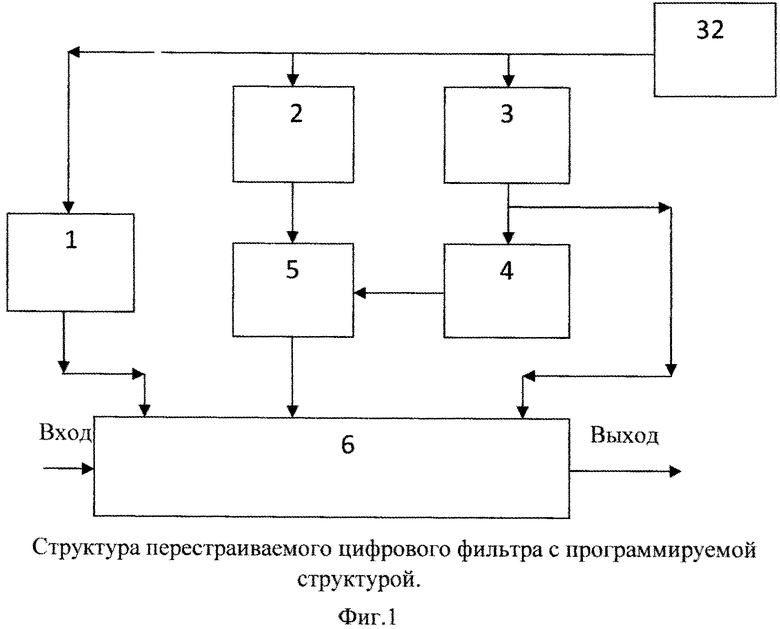

На фиг. 1 изображена структура перестраиваемого цифрового фильтра с программируемой структурой, на фиг. 2 - структура блока идентификации частоты импульсов, на фиг. 3 - структура блока пересчета кода фильтра, на фиг. 4 - структура реализации вычислителя параметров пересчета, фиг. 5 - структура реализации блока фильтрации, фиг. 6 - структура реализация блока коммутации, фиг. 7 - пример реализации счетчика-коммутатора, где приняты следующие обозначения:

1 - Блок хранения кода типа фильтра,

2 - Блок хранения кода структуры фильтра,

3 - Блок формирования тактовых импульсов,

4 - Блок идентификации частоты импульсов

5 - Блок пересчета кода фильтра,

6 - Блок фильтрации,

7 - Т-триггер,

8 - Первый генератор импульсов,

9 - Счетчик импульсов,

10 - Сумматор,

11 - Реле,

12 - Блоки элементов памяти,

13 - Вычислитель параметров пересчета,

14 - Регистр множителя,

15 - Мультиплексор,

16 - Счетчик- коммутатор,

17 - Умножитель,

18 - Сумматор-накопитель,

19 - Память вектора параметров,

20 - Второй переключатель,

21 - Первый переключатель,

22 - Второй генератор импульсов,

23 - Блок коммутации,

24 - Первый векторный умножитель,

25 - Второй векторный умножитель

26 - Первый регистр-накопитель,

27 - Второй регистр-накопитель,

28 - Память значений функции,

29 - Первый умножитель,

30 - Второй умножитель,

31 - N-й умножитель,

32 - Внешнее устройство настройки.

Осуществление перестраиваемого цифрового фильтра с программируемой структурой.

Сущность работы перестраиваемого цифрового фильтра заключается в следующем.

Пусть требуется обеспечить близость частотной характеристики цифрового фильтра при измененной частоте  и частотной характеристики (исходного) линейного цифрового фильтра, описываемого z-передаточной функцией вида

и частотной характеристики (исходного) линейного цифрового фильтра, описываемого z-передаточной функцией вида

где  - период дискретности, A0(z) и B0(z) - многочлены от z.

- период дискретности, A0(z) и B0(z) - многочлены от z.

Фильтр, описываемый передаточной функцией (1), назовем опорным цифровым фильтром (ОЦФ) - он соответствует желаемым функциональным свойствам. Частотная характеристика (ЧХ) такого фильтра определяется выражением [1]:

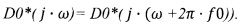

где символом * будем обозначать ЧХ дискретной системы. Такая характеристика является трансцендентной функцией ω и обладает периодическими свойствами [1, стр. 59]:

В случае, когда частота квантования изменилась  , использование старой передаточной функции опорного фильтра приведет к измененной ЧХ вида:

, использование старой передаточной функции опорного фильтра приведет к измененной ЧХ вида:

.

.

Заметим, что данная ЧХ обладает другими свойствами: она масштабно изменена по оси частот относительно опорной, а главное, имеет период повторения  который в N раз меньше, чем у исходной (N>1). В силу этого, подобрать «подобный фильтр», т.е. некоторый цифровой фильтр DN (z, T0⋅N) такого же порядка, как опорный, но который полностью повторял бы свойства опорного ЦФ, при измененной частоте

который в N раз меньше, чем у исходной (N>1). В силу этого, подобрать «подобный фильтр», т.е. некоторый цифровой фильтр DN (z, T0⋅N) такого же порядка, как опорный, но который полностью повторял бы свойства опорного ЦФ, при измененной частоте  невозможно.

невозможно.

Однако можно сформировать цифровой фильтр, обеспечивающий повторение ЧХ опорного фильтра в ограниченной полосе частот, в частности в основной полосе частот цифровой системы  . Для этого нужно выбирать параметры подобного ЦФ так, чтобы псевдочастотные характеристики ОЦФ при исходной частоте квантования

. Для этого нужно выбирать параметры подобного ЦФ так, чтобы псевдочастотные характеристики ОЦФ при исходной частоте квантования  и псевдочастотные характеристики подобного фильтра при частоте квантования

и псевдочастотные характеристики подобного фильтра при частоте квантования  были близки в указанном диапазоне. Такой критерий может дать очень близкое совпадение характеристик подобного и опорного фильтров в полосе реальных частот

были близки в указанном диапазоне. Такой критерий может дать очень близкое совпадение характеристик подобного и опорного фильтров в полосе реальных частот

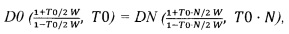

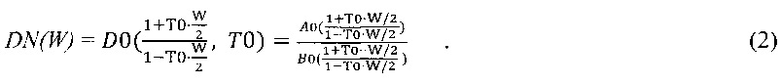

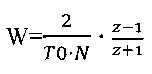

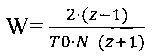

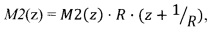

Это следует из того, что абсолютная псевдочастота ∧ [1, стр. 61] и реальная частота совпадают в указанном диапазоне достаточно близко. Используя переход в W-область, где W - параметр билинейного преобразования  [1, стр. 61], и приравнивая характеристики ОЦФ и ПФ в W-области, запишем:

[1, стр. 61], и приравнивая характеристики ОЦФ и ПФ в W-области, запишем:

откуда получим для подобного фильтра передаточную функцию в W области в форме:

Зная передаточную функцию DN(W) из (2) подобного фильтра в W области, перейдем к его z-передаточной функции с учетом измененной частоты  :

:

DN (z, T0⋅N)=DN(W, T0⋅N) при замене

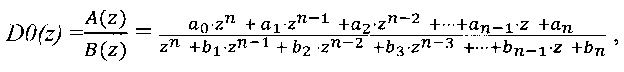

Пусть опорный цифровой фильтр описывается z-передаточной функцией вида:

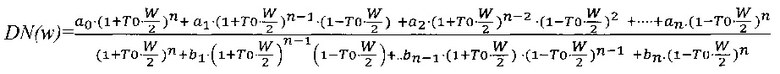

Используя выражение (2), после преобразований получим:

Подставляя в полученное выражение формулу обратного w-преобразования, где  , получим z-передаточную функцию фильтра в виде:

, получим z-передаточную функцию фильтра в виде:

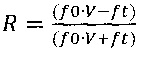

Для упрощения выражения введем коэффициент  , в дальнейшем называемый параметром пересчета, связанный с изменением частоты квантования (R=0 при неизменной частоте f0), и преобразуем DN(z) к следующему виду:

, в дальнейшем называемый параметром пересчета, связанный с изменением частоты квантования (R=0 при неизменной частоте f0), и преобразуем DN(z) к следующему виду:

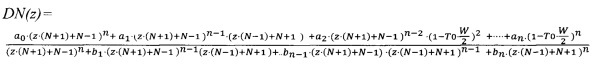

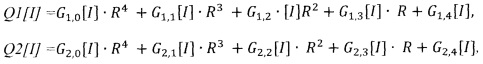

Из выражения (3) получим алгоритм вычисления коэффициентов числителя при степенях z, используя представления многочлена в форме схемы Горнера:

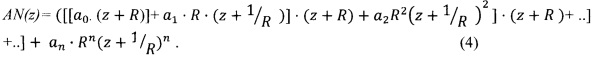

Обозначим многочлены в квадратных скобках как M1(z), а многочлены в круглых скобках как M2(z). При этом размерность многочленов меняется от 1 до n, элементы многочленов - коэффициенты при степенях z. Из схемы Горнера следует правило для вычисления последующих многочленов M1 и M2(z):

M1(z)=M1(z)⋅(z+R)+ai⋅M2(z).

Начальные многочлены:

M2(z)=(z⋅R+1),

M1(z)=(a0+a1⋅R)⋅z+(a1+a0⋅R),

Вычисление многочленов заканчивается на шаге i=n, причем коэффициенты результирующего многочлена M1 это и есть искомые коэффициенты числителя.

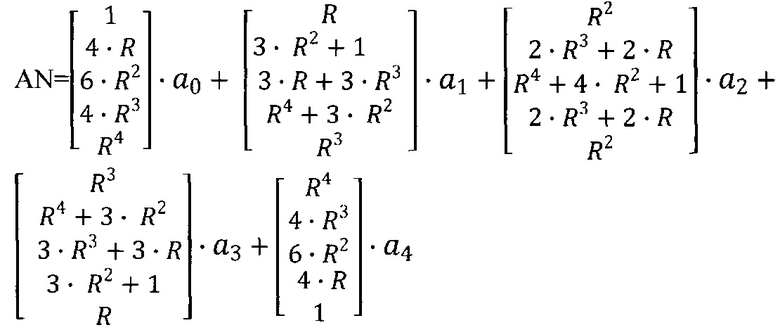

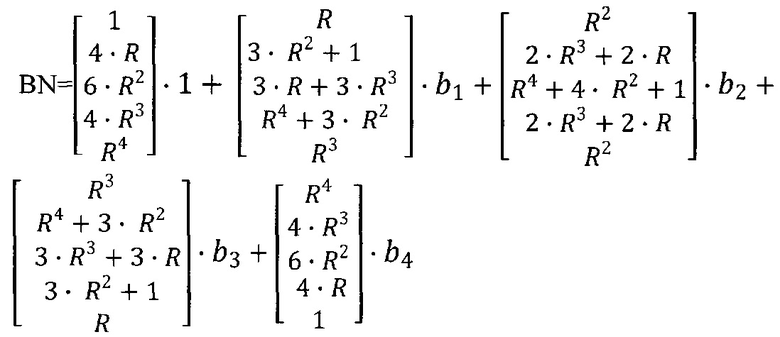

Аналогично, но для коэффициентов bi можно вычислить и знаменатель DN(z). В таблице, приведенной в ПРИЛОЖЕНИИ 1, записаны конкретные значения многочленов числителя и знаменателя в функции параметра пересчета R для подобных, т.е. пересчитанных, фильтров низкого порядка. Аналогичные соотношения можно получить для любого фиксированного порядка фильтра по (4). На приведенном в ПРИЛОЖЕНИИ 2 чертеже пунктирной линией показаны частотные характеристики подобного цифрового фильтра первого порядка, параметры которого вычислены по соотношениям (4). Как видно из чертежа, перестройка параметров цифрового фильтра позволяет добиться значительной близости ЧХ фильтра к характеристикам опорного цифрового фильтра при значительном изменении Т0.

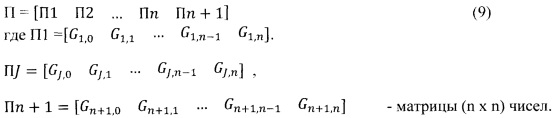

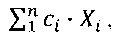

Удобно задавать формулы пересчета в форме матричных соотношений, позволяющих по известным параметрам опорного алгоритма {a0i,b0i} и значениям фактического периода квантования T0*N, или параметра R, пересчитать значения параметров подобного фильтра по следующему соотношению:

где A0, B0-n+1 - мерные векторы параметров опорного цифрового фильтра,

AN, BN-n+1 - мерные векторы параметров подобного цифрового фильтра,

Q(R)-(n+1)×(n+1) - матрица преобразований, или пересчета.

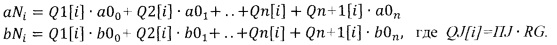

Представляя (5) по отдельным компонентам aNJ, bNJ, получим:

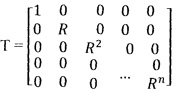

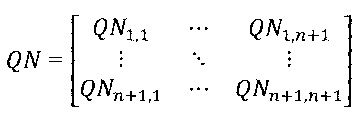

Представим матрицу пересчета Q в виде произведения Q=QN⋅T, где

- нормирующая матрица (n+1)⋅(n+1)

- нормирующая матрица (n+1)⋅(n+1)

- нормированная матрица пересчета.

- нормированная матрица пересчета.

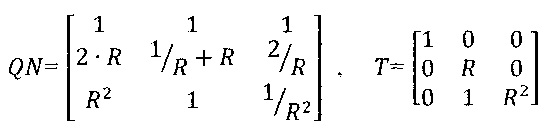

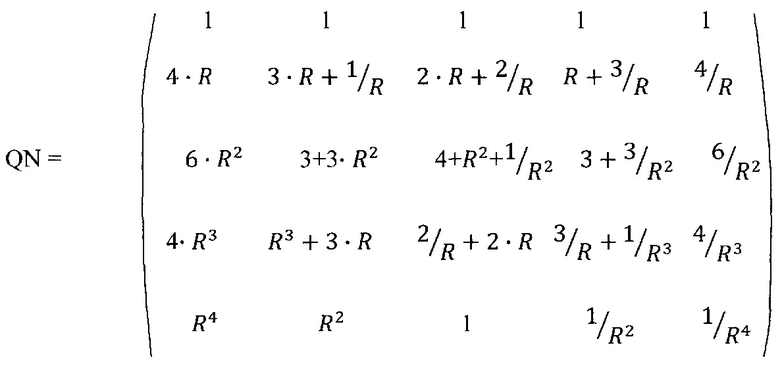

Так, для примера 2 порядка матрицы QN и Т примут вид:

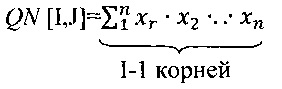

Рассмотрим структуру матрицы QN пересчета в ее нормированном виде. Нетрудно заметить, что J-й столбец матрицы представляет собой набор коэффициентов многочлена

причем (J-1) корней многочлена равно 1/R, а остальные (n-J+1) корни равны R. Тогда строка с номером I будет определять коэффициент при n-I+1 степени z многочлена (6): первая строка - степень n, вторая - n-1, …, последняя - степень 0. Таким образом, можно сформулировать простое правило вычисления коэффициентов нормированной матрицы QN пересчета для перестройки параметров фильтра при изменении частоты квантования.

Элемент матрицы пересчета QN [I,J] = сумме всевозможных сочетаний произведений (I-1) разных корней:  ,

,

причем значений различных корней всего два: -R и -1/R.

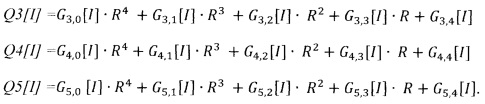

Выразить J-й столбец исходной Q[I,J] матрицы можно в виде ряда

Например, для n=4 матрица пересчета в функции R выразится так:

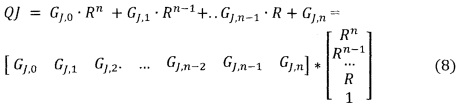

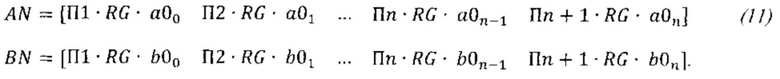

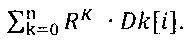

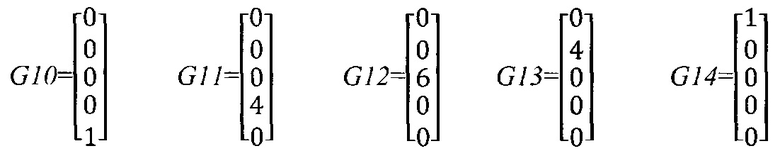

В связи с этим для хранения векторов GJ,K, определяющих матрицу пересчета, можно использовать память на (n+1)*(n+1)*(n+1) целых чисел. В этом случае общий алгоритм вычисления векторов QJ[1] для любых J примет вид:

Формула (8) позволяет вычислить векторы, составляющие матрицу пересчета по известным векторам GJ,K и текущим значениям Rn, Rn-1 … R,

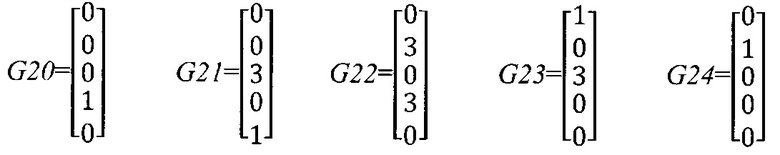

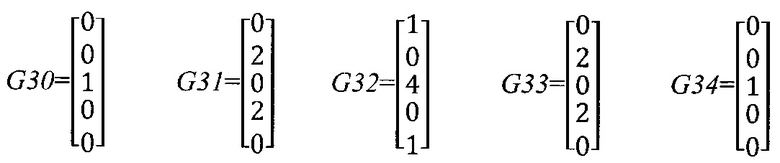

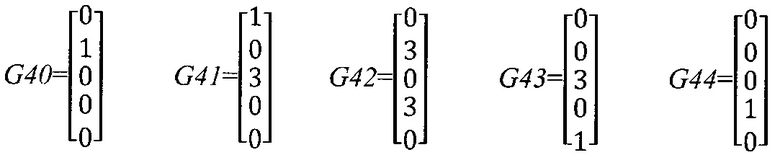

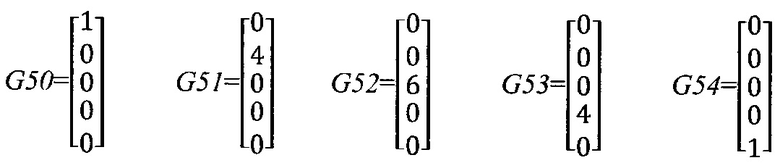

Таким образом для вычисления матрицы пересчета необходимо использовать блоки памяти Пk, содержащие векторы GJ,K в следующем виде:

Приведенная матрица П из (9) содержит (n+1)*(n+1)*(n+1) целых чисел, которые не зависят от параметров фильтра, а определяются только его порядком. Получение матрицы пересчета Q(R) для конкретного значения R можно осуществить умножением П на (n+1)2×(n+1) - матрицу Р вида:

где RG=[Rn Rn-1 … R 1]T, Т - знак транспонирования.

Характерно, при этом, что векторы GJ,K содержат большое число нулей и целые числа - биноминальные коэффициенты или их композиции, в связи с чем число умножений при вычислении матрицы Q по крайней мере в два-три раза меньше, чем номинальное число (n+1)3 умножений.

Учитывая, что собственно матрица пересчета нам не нужна, а нужны ее строки, умноженные на aNJ и bNJ, из (5*) получим:

Таким образом, получим для вычисления параметров aNi, bNi соотношение вида:

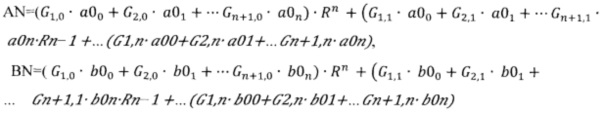

Раскрывая (11), получим:

В компактном виде полученное выражение запишем так:

Из выражения (12) видно, что пересчитанные коэффициенты цифрового фильтра aNi, bNi могут вычисляться по известным, рассчитанным заранее векторам Dk и Uk, зависящим от порядка системы, известным параметрам a0i, b0i опорного фильтра, а также по параметрам пересчета R, R2, …, Rn, зависящим от текущего изменения частоты  дискретности относительно опорной частоты

дискретности относительно опорной частоты  .

.

Следует отметить, что хорошая близость характеристик опорного фильтра на частоте  и подобного фильтра на частоте

и подобного фильтра на частоте  будет выполняться на низких частотах, а на частотах в окрестности

будет выполняться на низких частотах, а на частотах в окрестности  и выше реальная частота может отличаться от псевдочастоты, и характеристика фильтра будет смещена на 10-15% относительно опорной. Для уменьшения смещения по частоте в указанном диапазоне частот удобно ввести компенсирующий множитель V=0,9-1,3 и параметр пересчета R вычислять по формуле:

и выше реальная частота может отличаться от псевдочастоты, и характеристика фильтра будет смещена на 10-15% относительно опорной. Для уменьшения смещения по частоте в указанном диапазоне частот удобно ввести компенсирующий множитель V=0,9-1,3 и параметр пересчета R вычислять по формуле:  , где множитель V выбирается при проектировании цифрового фильтра так, что N>1 при

, где множитель V выбирается при проектировании цифрового фильтра так, что N>1 при  и V<1 при

и V<1 при  .

.

Следовательно, для обеспечения постоянства характеристик цифрового фильтра при изменении в процессе работы частоты  квантования необходимо:

квантования необходимо:

1. Предварительно, перед использованием цифрового фильтра, рассчитать постоянные векторы GJ,K, определяющие вычисление матрицы пересчета, для чего:

а) вычислить матрицу пересчета как функцию от параметра R,

б) получить нормированную матрицу пересчета,

в) составить постоянные векторы Dk, Uk по (12) для К=0, 1, …, n,

г) определить минимальное значение eps изменения частоты дискретности, при котором требуется перестройка параметров фильтра.

2. Предварительно разместить данные, определяющие векторы Dk, Uk в блоках памяти устройства фильтрации - 2⋅(n+1)2 чисел.

3. В процессе фильтрации эпизодически проводить измерения частоты  поступления информации.

поступления информации.

4. В случае значительного изменения частоты фильтрации  произвести оперативный пересчет параметров фильтра, для этого:

произвести оперативный пересчет параметров фильтра, для этого:

а) вычислить текущие параметры пересчета  , Ri,

, Ri,

б) используя формулу (12), рассчитать параметры aNi, bNi для конкретных значений параметра пересчета R,

в) использовать рассчитанные параметры aNi, bNi в текущей работе цифрового фильтра.

Именно такой способ обеспечения постоянства характеристик цифрового фильтра реализует описываемое далее устройство. Работа предлагаемого устройства заключается в следующем.

Предварительно, на этапе проектирования выбирается структура цифрового фильтра, работающего на определенной частоте квантования  Выбранный тип структуры определяется порядком фильтра n, типом фильтра (КИО или авторегрессионный), а также конкретными параметрами - например коэффициентами фильтрующего полинома, или z-передаточной функции. Выбирается значение частоты

Выбранный тип структуры определяется порядком фильтра n, типом фильтра (КИО или авторегрессионный), а также конкретными параметрами - например коэффициентами фильтрующего полинома, или z-передаточной функции. Выбирается значение частоты  первого генератора импульсов 8, соответствующей соотношению

первого генератора импульсов 8, соответствующей соотношению  - фиксированное число. По расчетам и результатам моделирования процессов фильтрации при изменении частоты

- фиксированное число. По расчетам и результатам моделирования процессов фильтрации при изменении частоты  на

на  определяются допустимые величины ε изменения частоты квантования по соответствующей величине

определяются допустимые величины ε изменения частоты квантования по соответствующей величине  , где

, где - относительный текущий период квантования. Рассчитываются весовые векторы GJK, используемые при вычислении К-х векторов Dk, Uk, данные векторы размещаются в 2⋅(n+1)2 ячейках блока элементов памяти 12 блока перестройки кода фильтра 5. Соответствующие данные по параметрам опорного цифрового фильтра в виде числовых параметров заносятся в блок 2 хранения кода структуры фильтра. Данные параметры помещаются в память опорных параметров фильтра - блоки регистров, где каждый регистр определяет один из 2n+1 параметров фильтра.

- относительный текущий период квантования. Рассчитываются весовые векторы GJK, используемые при вычислении К-х векторов Dk, Uk, данные векторы размещаются в 2⋅(n+1)2 ячейках блока элементов памяти 12 блока перестройки кода фильтра 5. Соответствующие данные по параметрам опорного цифрового фильтра в виде числовых параметров заносятся в блок 2 хранения кода структуры фильтра. Данные параметры помещаются в память опорных параметров фильтра - блоки регистров, где каждый регистр определяет один из 2n+1 параметров фильтра.

При работе перестраиваемого цифрового фильтра сигналом от внешнего устройства запускается формирователь тактовых импульсов 1, обеспечивающий синхронный ввод в блок фильтрации 6 непрерывной фильтруемой последовательности данных. Эпизодически, например, с периодом  в процессе работы производится идентификация периода дискретности поступления информации. Для этого в блоке идентификации частоты квантования 4 по переднему фронту тактового импульса запускается Т-триггер 7 и своим первым выходом запускает первый генератор импульсов 8, частота которого в 100-200 раз больше расчетной частоты квантования

в процессе работы производится идентификация периода дискретности поступления информации. Для этого в блоке идентификации частоты квантования 4 по переднему фронту тактового импульса запускается Т-триггер 7 и своим первым выходом запускает первый генератор импульсов 8, частота которого в 100-200 раз больше расчетной частоты квантования  Счетчик импульсов 9 фиксирует число Nt импульсов с первого генератора импульсов 8 за период квантования. По переднему фронту следующего импульса генератор 8 отключается по сигналу со второго - инвертирующего выхода Т-триггера 7.

Счетчик импульсов 9 фиксирует число Nt импульсов с первого генератора импульсов 8 за период квантования. По переднему фронту следующего импульса генератор 8 отключается по сигналу со второго - инвертирующего выхода Т-триггера 7.

Все вышеперечисленные устройства могут быть реализованы на серийно выпускаемых интегральных микросхемах (ИМС). Так, например, Т-триггер 7 реализуется на КМ555ТМ2 или К155ТМ2 [4, стр. 76, 75], первый генератор импульсов 8 - К555АГ3(К155АГ3)[4, стр. 190], счетчик импульсов 9 может быть реализован на одной или нескольких микросхемах декадного двоично-десятичного счетчика К155ИЕ9 [4, стр 97]. Так, на указанной странице приведено соединение четырех таких микросхем в синхронный 16-разрядный счетчик (от 0 до 64000). Для описываемого устройства достаточно использовать три указанных микросхемы (12 разрядов, счет до 4096).

Значение параметра Nt передается на второй вход блока 5 пересчета кода фильтра. Далее в сумматоре 10 вычисляется разность dN между измеренным Nt и заданным N0 значением числа импульсов. Результат операции рассматривается по модулю, как положительное число. Данная операция для 12-разрядных чисел может реализовываться тремя микросхемами сумматора-вычитателя, например К555ИМ7, содержащими 4 последовательных сумматора [4, стр. 162], без учета знакового разряда на выходе. В случае, если изменение dN относительного периода Nt не превышает порог , реле 11 не срабатывает, первый переключатель 21 не передает сигнал, перестройка не выполняется, второй переключатель 20 передает на цифровой фильтр 6 опорные параметры из блока хранения кода фильтра 2. Если изменение dN относительного периода велико

, реле 11 не срабатывает, первый переключатель 21 не передает сигнал, перестройка не выполняется, второй переключатель 20 передает на цифровой фильтр 6 опорные параметры из блока хранения кода фильтра 2. Если изменение dN относительного периода велико , срабатывает специальное реле 11, построенное соединением компаратора и порогового элемента, так что компаратор сравнивает

, срабатывает специальное реле 11, построенное соединением компаратора и порогового элемента, так что компаратор сравнивает и ε и формирует логический сигнал 1 в случае

и ε и формирует логический сигнал 1 в случае а пороговый элемент формирует переключения. Реализация компаратора может выполняться на базе соединения компараторов К555СП1 или К561ИП2 [4, стр. 277, рис 2.68]. На данном рисунке представлено соединение трех 4-разрядных компараторов К561ИП2, реализующих 12-разрядный компаратор. Пороговый элемент можно реализовать триггером Шмидта (К155ТЛ1), возможно, при низких частотах

а пороговый элемент формирует переключения. Реализация компаратора может выполняться на базе соединения компараторов К555СП1 или К561ИП2 [4, стр. 277, рис 2.68]. На данном рисунке представлено соединение трех 4-разрядных компараторов К561ИП2, реализующих 12-разрядный компаратор. Пороговый элемент можно реализовать триггером Шмидта (К155ТЛ1), возможно, при низких частотах  использование усилителя и электромеханического реле, замыкающего переключатель, включающий устройства, выполняющие пересчет параметров фильтра.

использование усилителя и электромеханического реле, замыкающего переключатель, включающий устройства, выполняющие пересчет параметров фильтра.

Собственно перестройка параметров цифрового фильтра осуществляется путем применения матрицы преобразований Q(R) к опорным параметрам, хранящимся в блоке хранения кода структуры фильтра 2 и подаваемым на вход блока перестройки кода фильтра 5. Первоначально, по сигналу Nt на первом переключателе 21 в вычислителе параметров пересчета13 вычисляются параметр пересчета R=(Nt⋅V-N0)/(Nt⋅1/+N0), а также его степени R2…Rn, т.е. вычислитель подсчитывает параметр R по нелинейной функции R(Nt), затем вычисляет степени, последовательно используя перемножения R⋅R, R2⋅R, R3⋅R, …, Rn-1⋅R, и по окончании вычислений формирует сигнал на запуск второго генератора импульсов 22, тактирующего счетчик-коммутатор 16. Удобным способом вычислений R в блоке 13 может быть использование блоков памяти для вычисления нелинейной функции R(Nt) [5, стр. 219, 220]. Учитывая, что параметр Nt - целое число с ограниченным диапазоном, каждому значению № как адресу можно поставить в соответствие число R (Nt) и вычисление нелинейной функции заменить извлечением из памяти заранее рассчитанного результата по конкретному значению Nt. Для конкретности будем считать, что первый генератор импульсов 8 генерирует частоту, в 200 раз превышающую  т.е. N0=200, и идентификация текущей частоты

т.е. N0=200, и идентификация текущей частоты  по подсчету значения Nt счетчиком импульсов 9 дает ошибку в 0.5% (1/200). Пусть требуется удовлетворительная работа цифрового фильтра при изменении частоты в 10 раз, т.е. 20<Nt<2000. Следовательно, для размещения всевозможных значений R(Nt) достаточно памяти на 2000 слов. Если каждое слово задает 16-разрядное число (1 знаковый разряд), то объем памяти для размещения нелинейной функции составит 4 кбайта, при этом точность вычислений R составит 1/215=0.003%. Если под слово отводить 1 байт, то потребуются 2 кбайта памяти и точность вычислений составит 1/27=0.8%, что также вполне достаточно. Такая память может реализовываться на матрицах запоминающих элементов PROM К155РЕ3 (32×8, бит) или микросхемах серии К556, имеющих информационную емкость до 64 кбит [5, стр. 198, 200]. Обращение к памяти может выполняться по значению целого Nt. Структура такой реализации вычислителя параметров пересчета 13 представлена на фиг. 4. Характерно, что данная реализация вычислителя нелинейной функции R(Nt) может существенно упростить приборную реализацию за счет исключения сумматоров и делителя. Заполнение памяти значениями R(Nt) должно производиться на предварительном этапе подготовки цифрового фильтра. Для вычисления произведений R⋅R, R2⋅R, R3⋅R, …, Rn-1⋅R можно использовать умножитель. Такие умножители могут реализовываться на ИМС К1802ВП5, возможно использование перемножителя К555ИП9 и сумматора К555ИМ7 [4, стр. 165, 162]. Данные, полученные с вычислителя параметров пересчета 13, используются для вычисления отдельных i-х элементов вектора параметров. Для этого вычислитель параметров пересчета 13 по выполнению всех умножений формирует сигнал на запуск второго генератора импульсов 22, приводящего в действие счетчик-коммутатор 16. Период импульсов второго генератора 22 должен быть таким, чтобы за это время могли осуществиться операции извлечения из памяти и умножения. Реализация второго генератора импульсов 22 аналогична описанной выше реализации блока 8 - ИМС К555АГ3 (К155АГ3) [4, стр. 190]. По сигналам второго генератора импульсов 22, подаваемым на вход счетчика-коммутатора 16, начинает работать счетчик-коммутатор 16, управляющий работой блока элементов памяти 12, мультиплексора 15, сумматора накопителя 18 и обеспечивающий очередность перемножения RK⋅DK[i]. Для этого на входы умножителя 17 поочередно передаются из i-го блока элементов памяти 12 и вычислителя параметров пересчета 13 множители для К-й компоненты RK⋅DK[i] (К=0, 1, 2, …, n) скалярного произведения

по подсчету значения Nt счетчиком импульсов 9 дает ошибку в 0.5% (1/200). Пусть требуется удовлетворительная работа цифрового фильтра при изменении частоты в 10 раз, т.е. 20<Nt<2000. Следовательно, для размещения всевозможных значений R(Nt) достаточно памяти на 2000 слов. Если каждое слово задает 16-разрядное число (1 знаковый разряд), то объем памяти для размещения нелинейной функции составит 4 кбайта, при этом точность вычислений R составит 1/215=0.003%. Если под слово отводить 1 байт, то потребуются 2 кбайта памяти и точность вычислений составит 1/27=0.8%, что также вполне достаточно. Такая память может реализовываться на матрицах запоминающих элементов PROM К155РЕ3 (32×8, бит) или микросхемах серии К556, имеющих информационную емкость до 64 кбит [5, стр. 198, 200]. Обращение к памяти может выполняться по значению целого Nt. Структура такой реализации вычислителя параметров пересчета 13 представлена на фиг. 4. Характерно, что данная реализация вычислителя нелинейной функции R(Nt) может существенно упростить приборную реализацию за счет исключения сумматоров и делителя. Заполнение памяти значениями R(Nt) должно производиться на предварительном этапе подготовки цифрового фильтра. Для вычисления произведений R⋅R, R2⋅R, R3⋅R, …, Rn-1⋅R можно использовать умножитель. Такие умножители могут реализовываться на ИМС К1802ВП5, возможно использование перемножителя К555ИП9 и сумматора К555ИМ7 [4, стр. 165, 162]. Данные, полученные с вычислителя параметров пересчета 13, используются для вычисления отдельных i-х элементов вектора параметров. Для этого вычислитель параметров пересчета 13 по выполнению всех умножений формирует сигнал на запуск второго генератора импульсов 22, приводящего в действие счетчик-коммутатор 16. Период импульсов второго генератора 22 должен быть таким, чтобы за это время могли осуществиться операции извлечения из памяти и умножения. Реализация второго генератора импульсов 22 аналогична описанной выше реализации блока 8 - ИМС К555АГ3 (К155АГ3) [4, стр. 190]. По сигналам второго генератора импульсов 22, подаваемым на вход счетчика-коммутатора 16, начинает работать счетчик-коммутатор 16, управляющий работой блока элементов памяти 12, мультиплексора 15, сумматора накопителя 18 и обеспечивающий очередность перемножения RK⋅DK[i]. Для этого на входы умножителя 17 поочередно передаются из i-го блока элементов памяти 12 и вычислителя параметров пересчета 13 множители для К-й компоненты RK⋅DK[i] (К=0, 1, 2, …, n) скалярного произведения  Множители для каждой компоненты поступают в умножитель через регистр множителя 14 и мультиплексора, которыми управляет счетчик-коммутатор 16, приводимый в действие тактирующими импульсами. Данный счетчик поочередно выдает на своем первом выходе значения 0, 1, … (n+1)2-1 (для КИО фильтра), подаваемые на блок элементов памяти 12, по которым из блока 12 считывается число и подается на регистр множителя 14, передающий число на умножитель 17. Соответствующие последовательности данных чисел, извлекаемых из памяти 12, имеют вид: D0[i], D1[i], …, Dn[i]. На втором выходе счетчика-коммутатора 16, связанном со вторым адресным входом мультиплексора 15, формируется последовательность значений К=0, 1, …, n. По данной последовательности второй мультиплексор 15 передает на блок умножения 17 второй множитель, формируемый в вычислителе параметров пересчета 13. Последовательность сигналов на втором входе умножителя 17 при этом будет такой: 1, R, …, Rn-1, Rn. Первоначально на счетчике-коммутаторе 16 устанавливается 0, что соответствует К=0, i=1, сумматор-накопитель обнуляется. В умножителе 17 осуществляется умножение 1⋅D0[1], результат пересылается в сумматор-накопитель 18. Далее по приходу задающего импульса счетчик-коммутатор 16 сдвигается на 1 и вычисляется следующее произведения R⋅D1[1], которое складывается в сумматоре-накопителе 18 с предыдущим, затем для нового состояния счетчика вычисляется R2, для нового состояния счетчика вычисляется Rn-2⋅D2[i] и т.д. до К=n. В результате n+1 перемножений и сложений получается один элемент aN0, составляющий вектор AN. После вычисления второй выход счетчика-коммутатора 16 обнуляется, счетчик-коммутатор 16 подает на второй вход блока 19 сигнал записи в память вектора параметров 19 содержимого вектора накопителя 18, который затем обнуляется.

Множители для каждой компоненты поступают в умножитель через регистр множителя 14 и мультиплексора, которыми управляет счетчик-коммутатор 16, приводимый в действие тактирующими импульсами. Данный счетчик поочередно выдает на своем первом выходе значения 0, 1, … (n+1)2-1 (для КИО фильтра), подаваемые на блок элементов памяти 12, по которым из блока 12 считывается число и подается на регистр множителя 14, передающий число на умножитель 17. Соответствующие последовательности данных чисел, извлекаемых из памяти 12, имеют вид: D0[i], D1[i], …, Dn[i]. На втором выходе счетчика-коммутатора 16, связанном со вторым адресным входом мультиплексора 15, формируется последовательность значений К=0, 1, …, n. По данной последовательности второй мультиплексор 15 передает на блок умножения 17 второй множитель, формируемый в вычислителе параметров пересчета 13. Последовательность сигналов на втором входе умножителя 17 при этом будет такой: 1, R, …, Rn-1, Rn. Первоначально на счетчике-коммутаторе 16 устанавливается 0, что соответствует К=0, i=1, сумматор-накопитель обнуляется. В умножителе 17 осуществляется умножение 1⋅D0[1], результат пересылается в сумматор-накопитель 18. Далее по приходу задающего импульса счетчик-коммутатор 16 сдвигается на 1 и вычисляется следующее произведения R⋅D1[1], которое складывается в сумматоре-накопителе 18 с предыдущим, затем для нового состояния счетчика вычисляется R2, для нового состояния счетчика вычисляется Rn-2⋅D2[i] и т.д. до К=n. В результате n+1 перемножений и сложений получается один элемент aN0, составляющий вектор AN. После вычисления второй выход счетчика-коммутатора 16 обнуляется, счетчик-коммутатор 16 подает на второй вход блока 19 сигнал записи в память вектора параметров 19 содержимого вектора накопителя 18, который затем обнуляется.

Вычисление значений других компонент aNi вектора AN для других значений i выполняется аналогично, но с использованием новых элементов блока памяти 12. С использованием аналогичных процедур вычисляются все элементы вектора AN, которые размещаются в памяти вектора параметров 19. После вычисления всех компонент вектора AN аналогично вычисляется BN, при этом если цифровой фильтр 6 реализует фильтр КИО, вычисление BN не производится.

В описанных выше действиях возможна следующая схемная реализация на типовых ИМС или их комбинациях. Блоки элементов памяти 12 могут реализовываться на матрицах запоминающих элементов PROM К155РЕ3 (32×8 бит) или микросхемах серии К556 [5, стр. 198, 200]. Память вектора параметров 19 может реализовываться на микросхемах К537РУ8 - статическое ОЗУ объемом 2 Кбайта (по 8 бит) или набором микросхем К155РУ2 (ОЗУ 64 бит) [4, стр. 167], регистр множителя 14 - К555ИР8 [5, стр. 121], мультиплексор 15 - К555КП15 [4, стр. 154], умножители 17, 29-31 - К555ИП9 [4, стр. 165] либо 1802 ВП5. Счетчик-коммутатор 16 должен формировать на первом выходе последовательность 0, 1, …, (n+1)2-1 а на втором выходе 0, 1, 2, …, n, 0, 1, 2, … n, … 0, 1, 2, … n. Такое устройство можно сформировать из схем стандартных двоично-десятичных счетчиков КР1533ИЕ2 [5, стр. 160], которые включают секции с модулем 2 и 5, могут при подаче на вход тактирующих импульсов обеспечивать модуль счета М=n+1 (число состояний) до 10, а при наращивании нескольких ИМС и больше. Осуществляя сброс счетчика при достижении М-1 подачей сигнала с выхода на вход СБРОС, можно реализовать желаемую последовательность 0, 1, 2, …n, 0, 1, 2, … n, … 0, 1, 2, … n для управлений вторым мультиплексором 15 и формирования сигнала записи в память вектора параметров 19 и сигнала сброса сумматора-накопителя 18 после записи. Передавая 1 в момент сброса на точно такую же схему, получим на выходе последовательность с модулем (n+1)2 для управления чтением из блока элементов памяти 12 и формирования после окончания данной последовательности сигнала на переключатель 20 в случае КИО фильтра. Для авторегрессионного фильтра, после вычислений параметров aNi аналогично вычисляются параметры bNi - еще (n+1)2 такт таких же вычислений. Аналогично можно использовать ИМС- К155ИЕ9 [4, стр. 97, рис. 1.70] - где представлено соединение четырех микросхем в быстрый 16-разрядный счетчик. Пример реализации указанных функций счетчика-коммутатора приведен на фиг. 7. Сумматор-накопитель 18 может реализовываться композицией нескольких К555ИМ6 (сумматор на два 4-разрядных слова).

По окончании вычислений векторов параметров AN и BN счетчик-коммутатор 16 через второй переключатель 20 осуществляет переключение параметров фильтра с опорных параметров на пересчитанные параметры из памяти вектора параметров 19. Это реализуется подачей запрещающего и разрешающего сигналов на соответствующие регистры памяти. Далее параметры из блока 19 непосредственно участвуют в процессе фильтрации. Следует отметить, что все описанные вычисления по пересчету параметров фильтра проводятся однократно либо эпизодически при изменении частоты квантования, в связи с этим временные характеристики вычислений не имеют для фильтрации существенного значения, в отличие от вычислений в блоке фильтрации, которые выполняются на каждом шаге квантования и ограничены жесткими временными соотношениями.

Оценочно время Тв вычислений, без учета операций сложения, выборки из памяти и записи в память при перестройке определится для фильтра так:

Тв=Тумн*2⋅(n+1)2, где Тумн - время реализации умножения чисел.

Собственно процесс фильтрации заключается в формировании на выходе блока фильтрации 6 суммы координат состояния цифрового фильтра с определенными весами, формируемыми блоком 5 перестройки параметров фильтра. Эта стандартная операция может быть реализована различными известными устройствами, например из [1] или из [2].

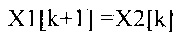

При другом подходе к организации этого процесса, в блоке фильтрации 6 используются ячейки памяти, образующие однородную среду, и коммутатор 23, реализуемый на кольцевом регистре-счетчике, отсчитывающим тактовые импульсы 1, 2 …n, 1, 2, … - фиг. 5. Коммутатор организует периодические подключения выходов ячеек и входного сигнала блока к векторным умножителям - блокам 24, 25. Для пояснения работы рассмотрим некоторые ячейки памяти А1, А2, А3, А4, в которых содержатся числовые данные, характеризующие состояние фильтра. Пусть для примера имеем цифровой фильтр 4-го порядка, описываемый четырьмя координатами состояния Х1, Х2, Х3, Х4, причем на определенном такте работы координата состояния X1 размещена в A1, Х2 в А2, Х3 в A3, а Х4 в А4. Цифровой фильтр реализуется методом прямого программирования [3, стр. 33], при котором уравнения изменения вектора состояния X и скалярного выхода Y имеют вид

где qI и cJ - параметры фильтра - константы, рассчитанные в блоке 5 при выполнении перестройки, либо константы из блока хранения кода структуры фильтра 2 в случае, когда перестройки нет.

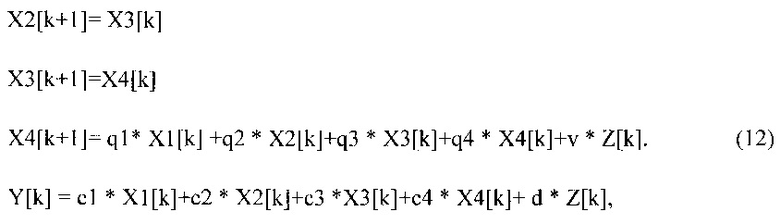

При поступлении нового входного сигнала коммутатор 23 передает на вторую группу входов 5, 6, 7, 8 второго векторного блока умножителя 24 содержимое ячеек А1, А2, А3, А4, а также входной сигнал Z. В блоке осуществляется соответствующее умножение координат на вычисленные ранее в блоке 5 (или блоке 2 без перестройки) константы и формируется выходной сигнал блока фильтрации в виде:

Y=c1*Х1+с2*Х2+с3*Х3+с4*Х4+d*Z.

Указанная сумма произведений формируется в первом регистре-накопителе 26 и поступает на выход фильтра.

Далее пересчитываются новые значения координат состояния по уравнениям и изменяется размещение координат состояния для следующего такта вычислений: координата Х4 (А4) становится Х3, Х3(А3) становится Х2, Х2(А2) становится X1, а координата Х4 вычисляется по соотношению:

Х4=q1*X1+q2*X2+q3*X3+q4*X4+v*Z.

Вычисление производится в блоке 25, суммирование частных произведений во втором регистре-накопителе 27, полученный результат записывается в А1. Таким образом координаты состояния поменяли расположение: X1(А2), Х2(А3), Х3(А4), Х4(А1), но перезапись произведена только в одной ячейке А1. На следующем такте все повторяется, но на входы 5, 6, 7, 8 блоков перемножения необходимо подавать сигналы с ячеек памяти в другом порядке: А2, А3, А4, А1, потом А3, А4, А1, А2, далее А4, А1, А2, А3 и, наконец, А1, А2, А3, А4. Все эти смещения связей ячеек памяти и входов блоков перемножения организуются блоком 23 коммутации, который может быть реализован с использованием кольцевого регистра-счетчика на 4 такта (в общем случае на n тактов) и мультиплексоров, коммутирующих поступление сигналов на различные входы блока перемножения - фиг. 6. В частности, каждый из 4 мультиплексоров передает сигнал на определенный вход из второй группы входов первого векторного умножителя 24 и второго векторного умножителя 25. На информационные входы мультиплексора подаются сигналы со всех ячеек, а также сигналы с первого векторного блока перемножителя 24. На адресные входы различных мультиплексоров 1, 2, 3, 4 подаются числа с различных выходов кольцевого регистра. Пусть в определенный такт квантования на мультиплексоры 1, 2, 3, 4 подаются соответственно адреса 1, 2, 3, 4. Так, 1-й мультиплексор получает адрес 1 и пропускает сигнал со своего входа 1 на 5 вход блока 24, 2-й мультиплексор - сигнал со своего входа 2 на 6 вход блока 24, 3-й мультиплексор - сигнал со входа 3 на 7 вход блока 24, 4-й мультиплексор - сигнал со входа 4 на 8 вход блока 24. На следующем такте кольцевой регистр сдвинет последовательность адресов - она поменяется и станет 2, 3, 4, 1, т.е. первый мультиплексор получает адрес 2 и пропустит на 5 вход блока 24 сигнал на его 2 входе, второй мультиплексор получает адрес 3 и передаст сигнал с 3 своего входа, третий мультиплексор получает адрес 4 и пропускает сигнал со своего 4 входа на 7 вход блока 24, четвертый мультиплексор по адресу 1 пропустит сигнал со своего первого входа на 8 вход блока 24. На следующем такте последовательность адресов будет 3, 4, 1, 2, затем 4, 1, 2, 3 и, наконец, снова 1, 2, 3, 4. При этом, хотя номера ячеек под координаты состояния изменяются на каждом шаге, первый и второй векторные блоки умножители 24, 25 выполняют неизменные операции по обработке сигнала.

Все блоки и устройства, входящие в блок фильтрации 6, также могут быть реализованы на серийно выпускаемых ИМС различных серий или их простых соединениях. Такая реализация умножителей сумматоров, счетчиков, мультиплексоров на конкретных элементах была раскрыта ранее при описании блока пересчета кода фильтра 5, в частности раскрыты процедура и реализация векторного умножения, выполняющая операцию  по соотношению (12). Память для записи коэффициентов q может реализовываться микросхемой К537 РУ8 - ОЗУ объемом 2 Кбайта (8 бит) или набором микросхем К155РУ2 (ОЗУ 64 бит) [4, стр. 167], мультиплексоры - К555КП15 [4, стр. 154], умножители - К555ИП9 [4, стр. 165,] либо 1802ВП5, первый и второй регистры-накопители 26, 27 могут реализовываться композицией нескольких К555ИМ6 (сумматор на два 4-разрядных слова), кольцевой регистр-счетчик - К155ИЕ9 [4, стр. 97] или КР1533ИЕ2 [5, стр. 160], аналогично счетчики в блоках векторного умножения 24, 25.

по соотношению (12). Память для записи коэффициентов q может реализовываться микросхемой К537 РУ8 - ОЗУ объемом 2 Кбайта (8 бит) или набором микросхем К155РУ2 (ОЗУ 64 бит) [4, стр. 167], мультиплексоры - К555КП15 [4, стр. 154], умножители - К555ИП9 [4, стр. 165,] либо 1802ВП5, первый и второй регистры-накопители 26, 27 могут реализовываться композицией нескольких К555ИМ6 (сумматор на два 4-разрядных слова), кольцевой регистр-счетчик - К155ИЕ9 [4, стр. 97] или КР1533ИЕ2 [5, стр. 160], аналогично счетчики в блоках векторного умножения 24, 25.

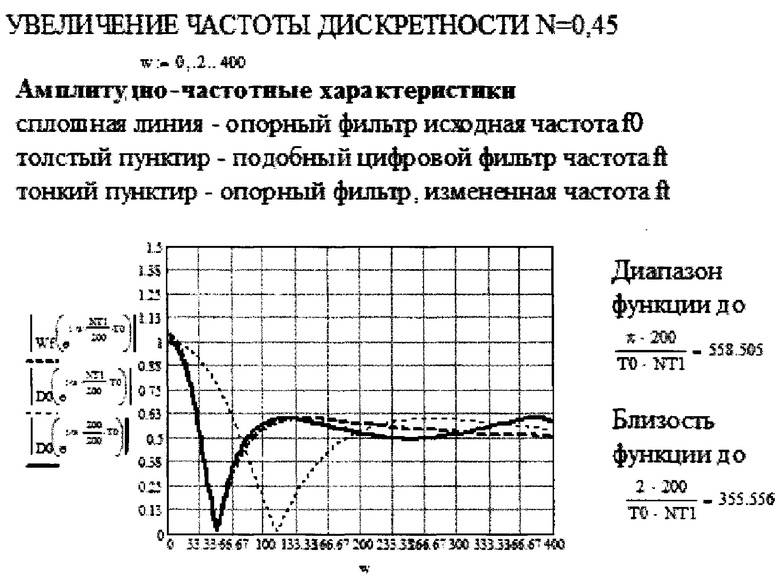

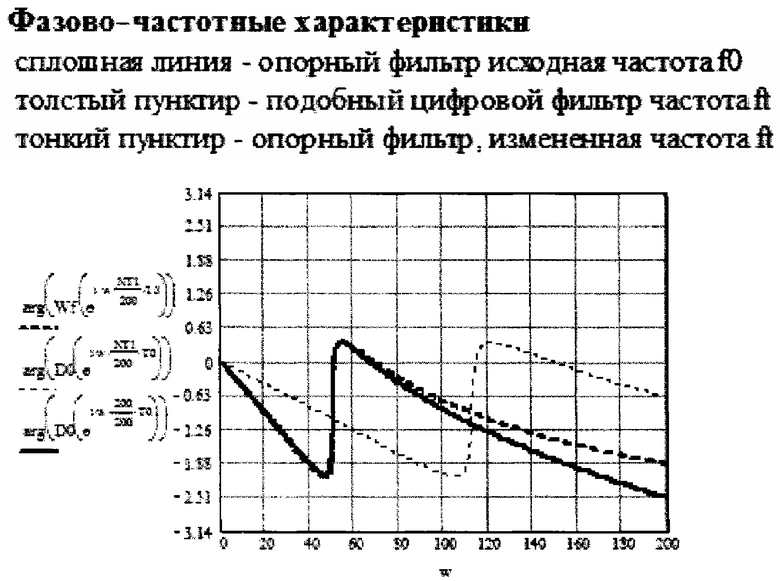

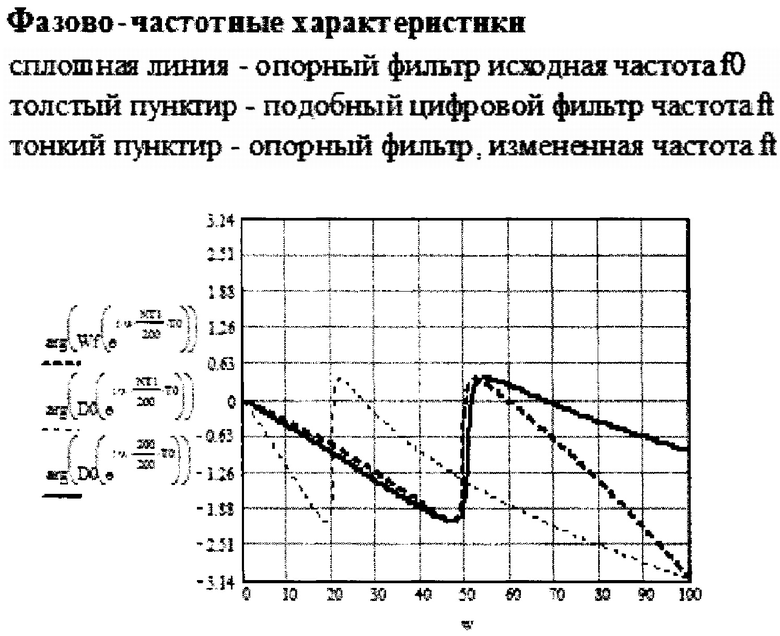

В ПРИЛОЖЕНИИ 2 приведены результаты математического моделирования реализации процессов перестройки для цифрового фильтра 4-го порядка с учетом конечной точности представления чисел. Как видно из графиков, полученных по результатам моделирования, частотные характеристики опорного и перестроенного цифрового фильтра практически очень близки в рабочем диапазоне частот при значительном изменении частоты дискретности: уменьшение в 2,5 раза и увеличение в 2,5 раза.

Таким образом, предлагаемый перестраиваемый цифровой фильтр с программируемой структурой позволяет путем введения новых блоков и организации новых связей между ними обеспечить улучшение свойств фильтрации за счет постоянства характеристик фильтрации при изменении частоты квантования  . Технический результат от использования изобретения заключается в уменьшении искажения характеристик цифрового фильтра, в частности обеспечении расчетных запасов устойчивости при изменении частоты дискретизации входного сигнала. Изобретательский уровень предложенного технического решения подтверждается отличительной частью формулы изобретения.

. Технический результат от использования изобретения заключается в уменьшении искажения характеристик цифрового фильтра, в частности обеспечении расчетных запасов устойчивости при изменении частоты дискретизации входного сигнала. Изобретательский уровень предложенного технического решения подтверждается отличительной частью формулы изобретения.

Используемые источники

1. Шамриков Б.М. Основы теории цифровых систем управления: Учебник для высших технических учебных заведений. - М., Машиностроение, 1985. - 286 с ил.

2. Патент РФ №2399152 - прототип.

3. Патент РФ №2037364 - аналог.

4. Шило В.Л. Популярные цифровые микросхемы. Справочник. - М., Радио и связь, 1989 г. - 352 с., с ил.

5. Угрюмов Е.П. Цифровая схемотехника. – СПб.: БХВ-Петербург, 2004. - 528 с., с ил.

ПРИЛОЖЕНИЕ 1

ПРИЛОЖЕНИЕ 2

МАТЕМАТИЧЕСКОЕ МОДЕЛИРОВАНИЕ РАБОТЫ ФИЛЬТРА.

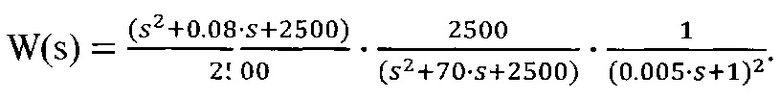

При моделировании рассматривался цифровой фильтр 4-го порядка, аналоговый прототип которого описывался передаточной функцией вида:

.

.

Расчетная частота квантования соответствовала f0=80 Гц, Т0=0.0125 с.

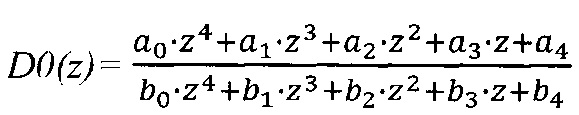

Опорный цифровой фильтр, соответствующий данной частоте, описывался z-передаточной функцией вида:

,

,

где коэффициенты {ai, bi} определяются следующими значениями:

а 0=0, a1=0.483, а2=-.705, а3=.368, а0=0.066;

b0=1, b1=-1.329, а2=.615, а3=-0.076, а0=0.0028.

Матрица пересчета в нормированном представлении имеет вид:

Откуда векторы GJK определятся выражениями:

Пересчитанные параметры {aNi, bNi} фильтра определятся с использованием матрицы пересчета в следующем виде:

Вычисления, производимые в блоке пересчета параметров фильтра для конкретного примера цифрового фильтра 4-го порядка, моделировались на вычислительной программе, реализованной в среде МАТКАД.

При этом выполнялись все математические операции пересчета в той последовательности, в которой они приведены в описании устройства, но со специальным ограничением точности представления чисел и точности выполнения вычислительных операций.

Параметр ограниченной точности вычислений составлял 4 десятичных разряда, что соответствует 14 двоичным разрядам, т.е. практически 2 байта.

Ниже приведены результаты моделирования - частотные характеристики исходного опорного фильтра, пересчитанного фильтра и исходного при увеличении и уменьшении частоты. Результаты подтверждают работоспособность представленных решений - характеристики подстроенного цифрового фильтра близки характеристикам опорного фильтра в рабочем диапазоне частот цифровой системы 0<ω<2 min(f0, ft).

| название | год | авторы | номер документа |

|---|---|---|---|

| Нерекурсивный цифровой фильтр-дециматор | 1989 |

|

SU1698953A2 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2006936C1 |

| СПОСОБ И УСТРОЙСТВО ДИАГНОСТИКИ СОСТОЯНИЯ АППАРАТУРЫ ЦИФРОВЫХ СИСТЕМ ПЕРЕДАЧИ | 1998 |

|

RU2132594C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Специализированный процессор для цифровой фильтрации | 1989 |

|

SU1631558A1 |

| СПОСОБ СЖАТИЯ РЕЧЕВОГО СИГНАЛА ПУТЕМ КОДИРОВАНИЯ С ПЕРЕМЕННОЙ СКОРОСТЬЮ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ, КОДЕР И ДЕКОДЕР | 1993 |

|

RU2107951C1 |

| Цифровой фильтр | 1987 |

|

SU1425840A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ДВУМЕРНОЙ СВЕРТКИ | 1992 |

|

RU2042209C1 |

Изобретение относится к области цифрового управления объектами авиационной техники, техники обработки и передачи дискретной информации в таких системах, и для создания цифровых фильтров. Технический результат заключается в уменьшении искажения характеристик цифрового фильтра. Перестраиваемый цифровой фильтр с программируемой структурой содержит внешнее устройство настройки, блок хранения кода типа фильтра, блок хранения кода структуры фильтра, блок формирования тактовых импульсов и блок фильтрации, при этом дополнительно введены блок идентификации частоты импульсов и блок пересчета кода фильтра. 2 з.п. ф-лы, 7 ил., 2 прилож.

1. Перестраиваемый цифровой фильтр с программируемой структурой, содержащий последовательно соединенные внешнее устройство настройки, блок хранения кода типа фильтра и блок фильтрации, выход внешнего устройство настройки соединен с входом блока хранения кода структуры фильтра, а через блок формирования тактовых импульсов - со вторым входом блока фильтрации, отличающийся тем, что он дополнительно содержит блок идентификации частоты импульсов и блок пересчета кода фильтра, выход блока хранения кода структуры фильтра через блок пересчета кода фильтра соединен с третьим входом блока фильтрации, а выход блока формирования тактовых импульсов через блок идентификации частоты импульсов - со вторым входом блока пересчета кода фильтра.

2. Перестраиваемый цифровой фильтр с программируемой структурой

по п. 1, отличающийся тем, что блок идентификации частоты импульсов содержит Т-триггер, первый генератор импульсов и счетчик импульсов, причем вход блока идентификации частоты импульсов соединен через последовательно подключенные Т-триггер, первый генератор импульсов и счетчик импульсов с выходом блока идентификации частоты импульсов, а второй выход Т-триггера соединен со вторым входом первого генератора импульсов.

3. Перестраиваемый цифровой фильтр с программируемой структурой

по п. 1, отличающийся тем, что блок пересчета кода фильтра содержит сумматор, реле с первым переключателем, блок элементов памяти, вычислитель параметров пересчета, регистр множителя, мультиплексор, счетчик-коммутатор, умножитель, сумматор-накопитель, память вектора параметров, второй генератор импульсов, второй переключатель, второй вход блока пересчета кода фильтра соединен со входом реле через сумматор, а через последовательно подключенные первый переключатель, вычислитель параметров пересчета, мультиплексор, умножитель, сумматор-накопитель, память вектора параметров и второй переключатель с выходом блока пересчета кода фильтра, выход блока элементов памяти через регистр множителя соединен со вторым входом умножителя, второй выход вычислителя параметров пересчета соединен через второй генератор импульсов со входом счетчика-коммутатора, а первый, второй, третий и четвертый выходы счетчика-коммутатора соединены соответственно со входом блока элементов памяти, вторыми входами мультиплексора, сумматора-накопителя и блока памяти вектора параметров, пятый выход счетчика-коммутатора соединен со вторым входом второго переключателя, третий вход которого подключен к первому входу блока пересчета кода фильтра.

| УНИВЕРСАЛЬНЫЙ ЦИФРОВОЙ ФИЛЬТР С ПРОГРАММИРУЕМОЙ СТРУКТУРОЙ | 2008 |

|

RU2399152C2 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| СПОСОБ ЦИФРОВОЙ РЕКУРСИВНОЙ ПОЛОСОВОЙ ФИЛЬТРАЦИИ И ЦИФРОВОЙ ФИЛЬТР ДЛЯ РЕАЛИЗАЦИИ ЭТОГО СПОСОБА | 2011 |

|

RU2460130C1 |

| ФИЛЬТР С КОНЕЧНЫМ ИМПУЛЬСНЫМ ОТКЛИКОМ НА БАЗЕ ПЗУ ДЛЯ ИСПОЛЬЗОВАНИЯ В МОБИЛЬНОМ ТЕЛЕФОНЕ | 1997 |

|

RU2189109C2 |

| RU 2001132755 A, 20.08.2003 | |||

| ГЛАЗУРЬ ДЛЯ ФАЯНСА | 2010 |

|

RU2418773C1 |

Авторы

Даты

2017-09-29—Публикация

2016-03-15—Подача