113

Изобретение относится к радиоизмерительной технике и может использоваться в системах обработки информа- I ции для анализа цифровых сигналов. Цель изобретения - повышение быстродействия обработки информации, что достигается путем уменьшения разрядности анализируемых сигналов за счет адаптивного подавления помехи в цифровом фильтре.

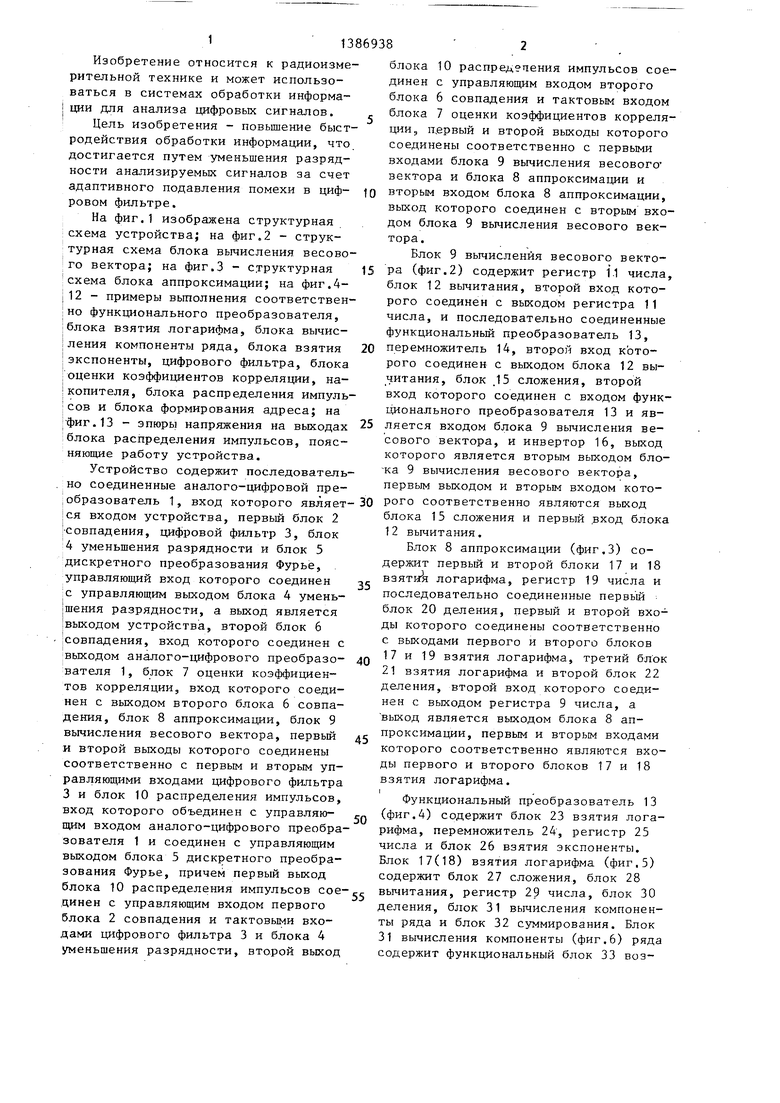

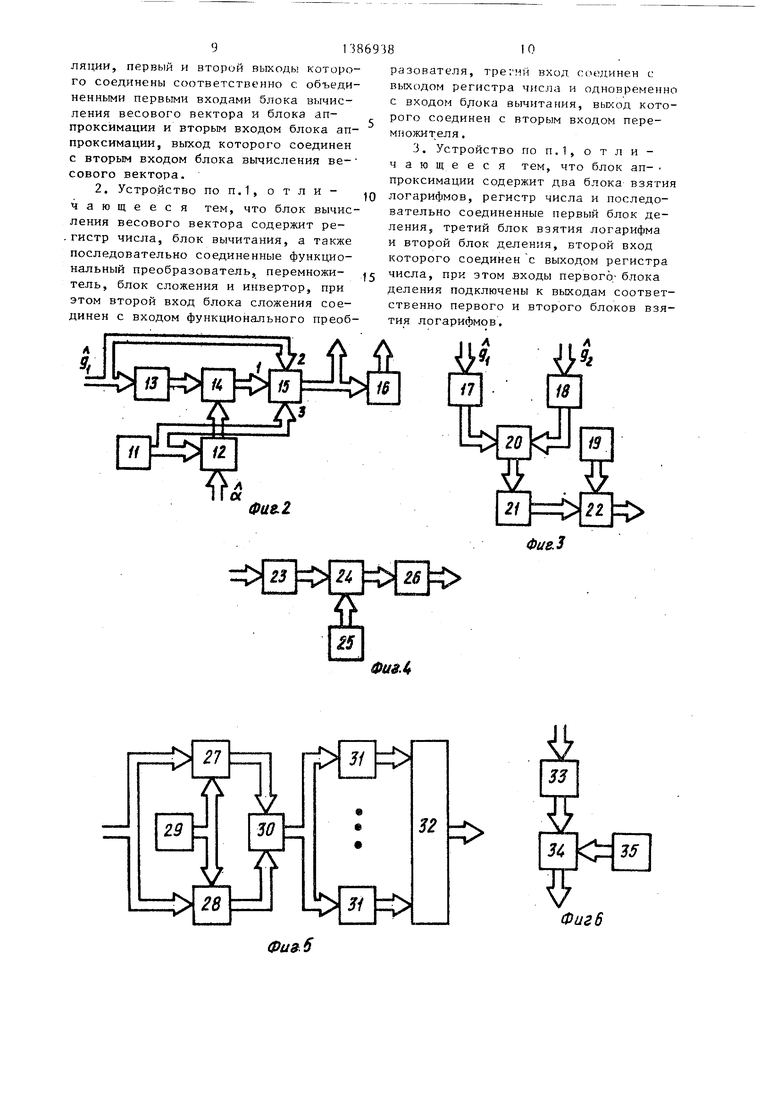

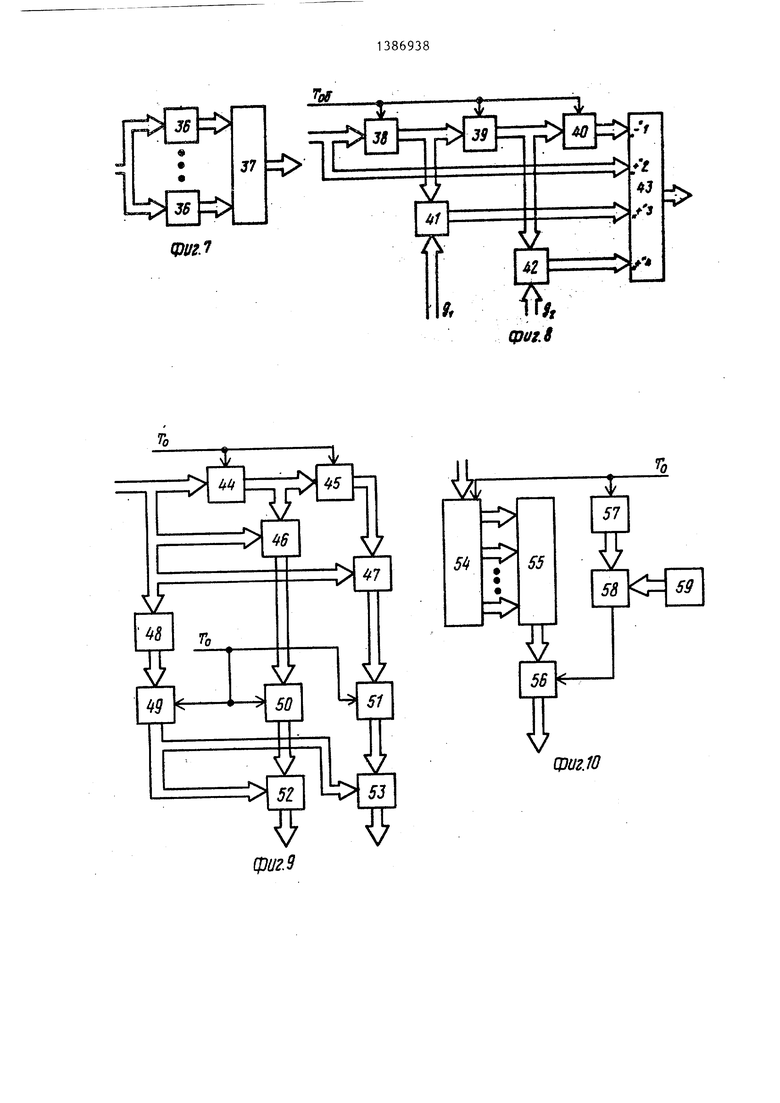

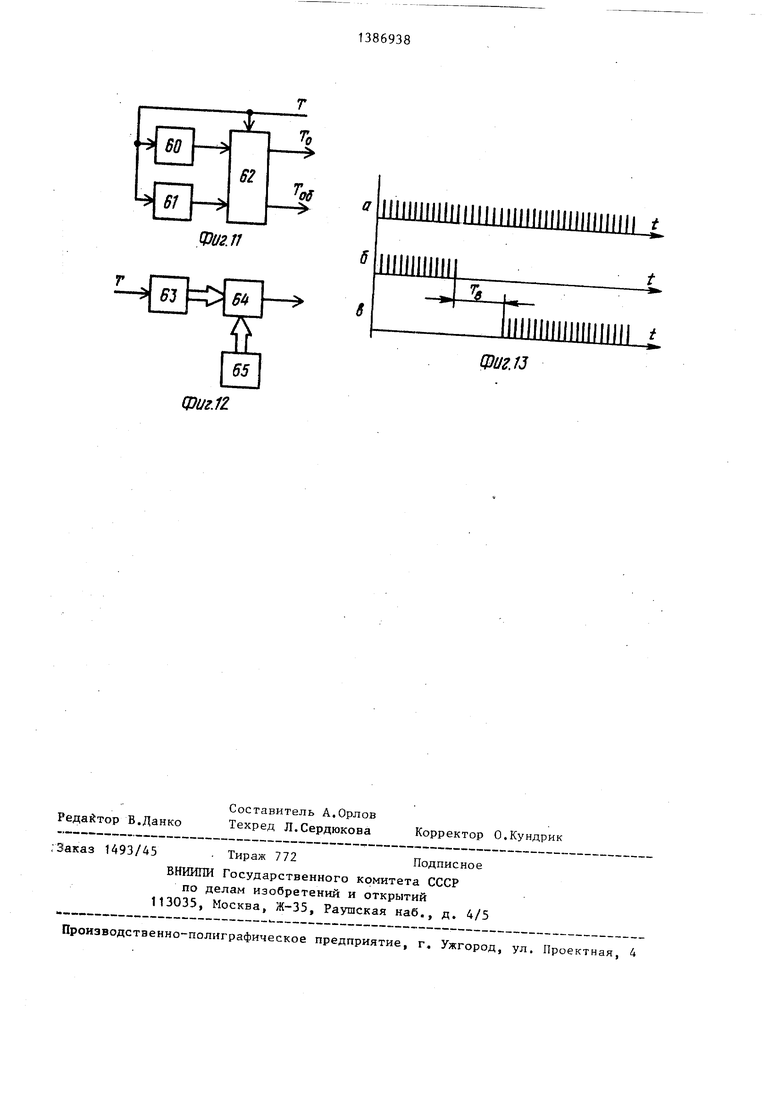

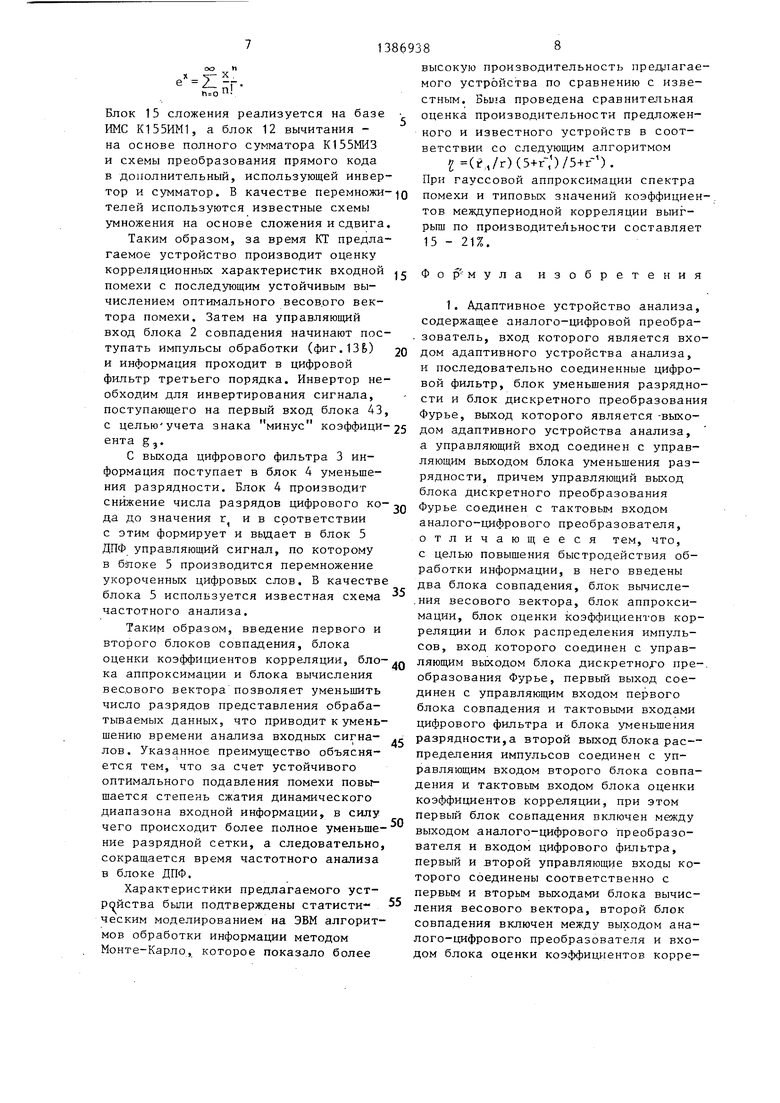

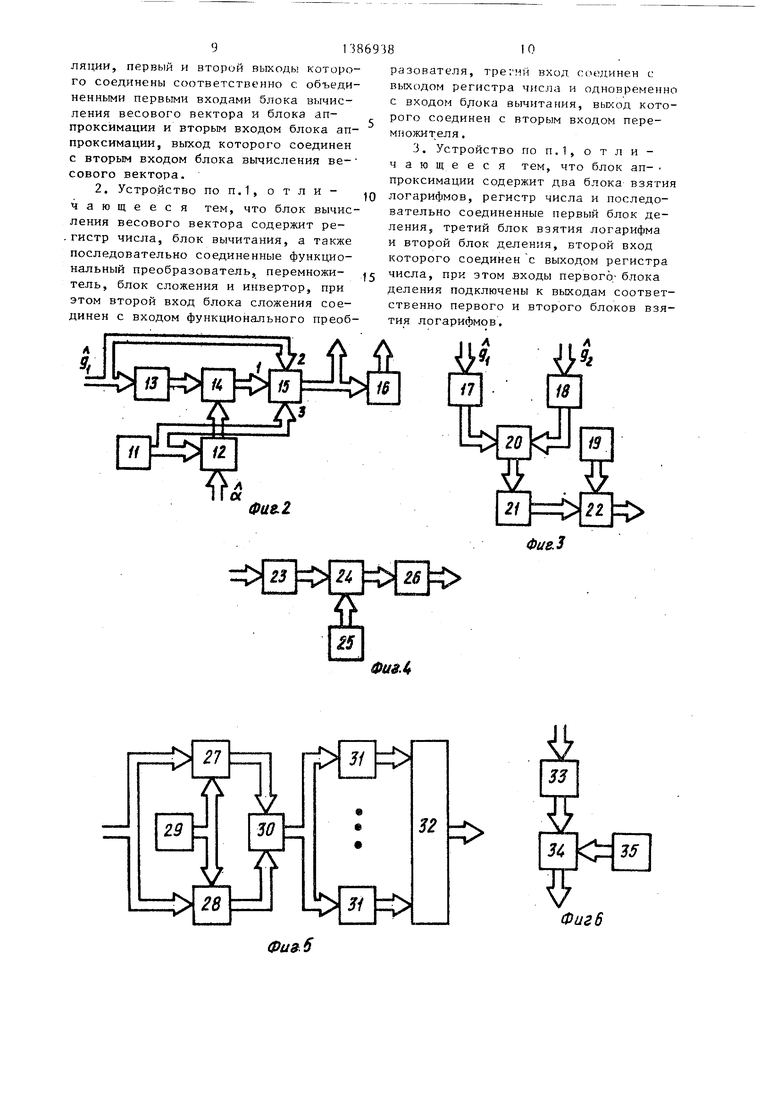

На фиг.1 изображена структурная схема устройства; на фиг.2 - структурная схема блока вычисления весового вектора; на фиг.З - структурная схема блока аппроксимации; на фиг.4- {12 - примеры вьшолнения соответственно функционального преобразователя, блока взятия логарифма, блока вычис- Iления компоненты ряда, блока взятия экспоненты, цифрового фильтра, блока iоценки коэффициентов корреляции, на- копителя, блока распределения импуль- I сов и блока формирования адреса; на Iфиг.13 - эпюры напряжения на выходах ;блока распределения импульсов, поясняющие работу устройства.

Устройство содержит последователь- . но соединенные аналого-цифровой пре

0

5

блока 10 распредепения импульсов соединен с управляющим входом второго блока 6 совпадения и тактовым входом блока 7 оценки коэффициентов корреляции,, п,ервый и второй выходы которого соединены соответственно с первыми входами блока 9 вычисления весового вектора и блока 8 аппроксимации и вторым входом блока 8 аппроксимации, выход которого соединен с вторым входом блока 9 вычисления весового вектора.

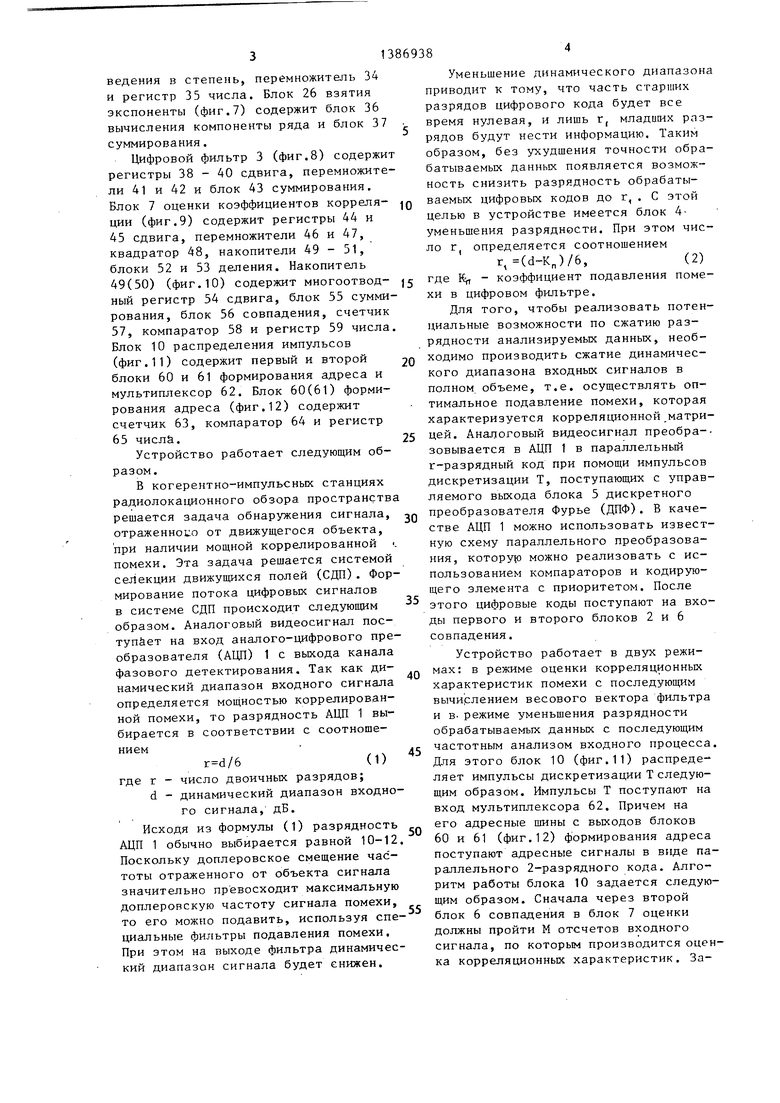

Блок 9 вычисления весового векто- Ра (фиг.2) содержит регистр 1.1 числа, блок 12 вычитания, второй вход которого соединен с выходом регистра 11 числа, и последовательно соединенные функциональньш преобразователь 13, перемножитель 14, второй вход которого соединен с выходом блока 12 вычитания, блок .15 сложения, второй вход которого соединен с входом функ- 1щонального преобразователя 13 и является входом блока 9 вычисления весового вектора, и инвертор 16, выход которого является вторьм выходом блока 9 вычисления весового вектора, первым выходом и вторым входом кото0

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный цифровой фильтр | 1987 |

|

SU1453593A2 |

| Адаптивный цифровой фильтр | 1986 |

|

SU1388896A1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ПАССИВНЫХ ПОМЕХ | 1982 |

|

SU1090136A1 |

| Адаптивный цифровой фильтр | 1987 |

|

SU1494212A1 |

| РАНГОВЫЙ АДАПТИВНЫЙ ПОСЛЕДОВАТЕЛЬНЫЙ ОБНАРУЖИТЕЛЬ СИГНАЛОВ | 1996 |

|

RU2100822C1 |

| Устройство для оценки параметров многолучевого канала связи | 1991 |

|

SU1781828A1 |

| АДАПТИВНОЕ УСТРОЙСТВО ЗАЩИТЫ РАДИОЛОКАЦИОННОЙ СТАНЦИИ ОТ ПАССИВНЫХ ПОМЕХ | 1994 |

|

RU2097781C1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1997 |

|

RU2115135C1 |

| СПОСОБ ОБРАБОТКИ СИГНАЛА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2409822C1 |

| Устройство для определения закона распределения случайной величины | 1987 |

|

SU1425715A1 |

Изобретение относится к радиотехнике и может быть использовано в системах обработки информации для анализа цифровых сигналов. Цель изобретения - повышение быстродействия обработки информации. Адаптивное устройство анализа содержит аналого- цифровой преобразователь 1, цифровой фильтр 3, блок 4 уменьшения разрядности и блок 5 дискретного преобразования числа. Введение блоков 2 и 6 совпадения, блока 7 оценки коэффициентов корреляции, блока 8 аппроксимации, блока 9 вычисления весового вектора и блока 10 распределения импульсов позволяет уменьшить число разрядов представления обрабатываемых данных, что приводит к уменьшению времени анализа входных сигналов. При этом устойчивое оптимальное подавление помехи повьш1ает степень сжатия динамического диапазона входной информации, благодаря чему происходит более полное уменьшение разрядной сетки, а следовательно, сокращается время частотного анализа в блоке 5 дискретного преобразования. В описании приведены примеры реализации блока 9 вычисления весового вектора и блока 8 аппроксимации. 2 з.п. ф-лы, 13 ил. i (Л

35

40

образователь 1, вход которого являет-30 Рого соответственно являются выход ся входом устройства, первый блок 2 {совпадения, цифровой фильтр 3, блок 4 уменьшения разрядности и блок 5 дискретного преобразования Фурье, управляющий вход которого соединен с управляющим выходом блока 4 умень- шения разрядности, а выход является {выходом устройства, второй блок 6 {совпадения, вход которого соединен с выходом аналого-цифрового преобразователя 1, блок 7 оценки коэффициентов корреляции, вход которого соединен с выходом второго блока 6 совпадения, блок 8 аппроксимации, блок 9 вычисления весового вектора, первый и второй выходы которого соединены соответственно с первым и вторым управляющими входами цифрового фильтра 3 и блок 10 распределения импульсов, вход которого объединен с управляю- 1ЦИМ входом аналого-цифрового преобразователя 1 и соединен с управляюЕШм выходом блока 5 дискретного преобразования Фурье, причем первый выход

45

50

блока 15 сложения и первый .вход блок 12 вычитания.

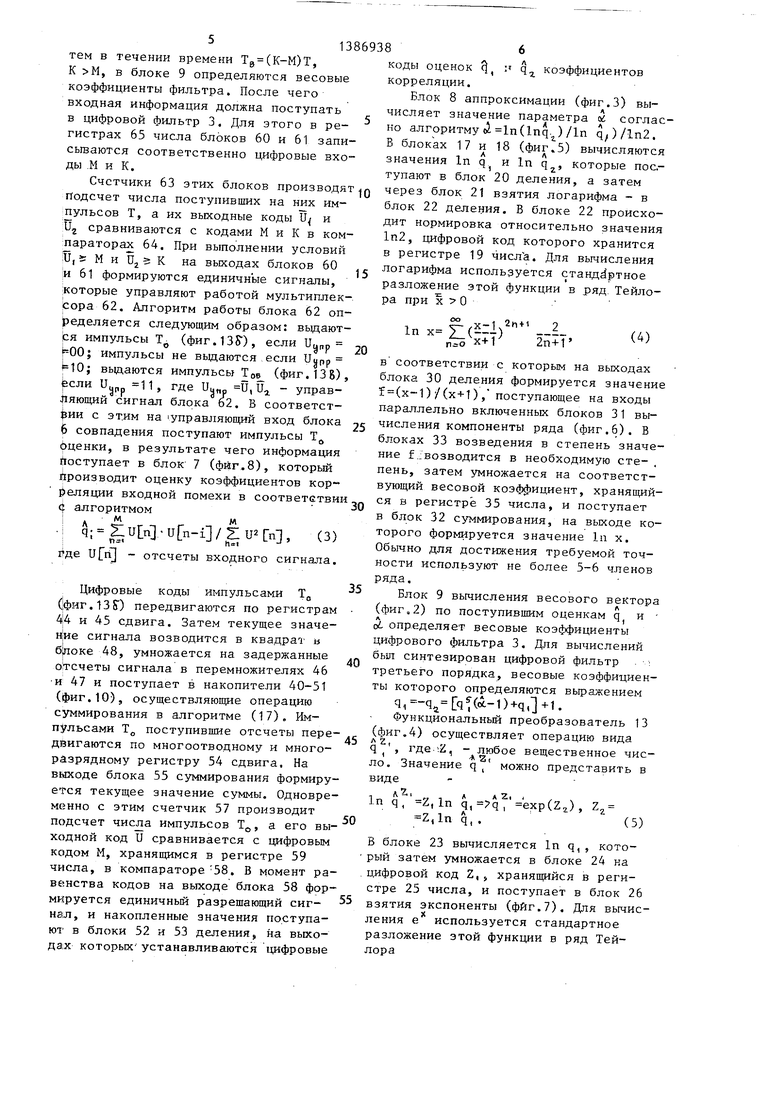

Блок 8 аппроксимации (фиг.З) содержит первый и второй блоки 17 и 18 взяти я логарифма, регистр 19 числа и последовательно соединенные первьй блок 20 деления, первый и второй вхо ды которого соединены соответственно с выходами первого и второго блоков 17 и 19 взятия логарифма, третий бло 21 взятия логарифма и второй блок 22 деления, второй вход которого соединен с выходом регистра 9 числа, а выход является выходом блока 8 аппроксимации, первым и вторым входами которого соответственно являются вхо ды первого и второго блоков 17 и 18 взятия логарифма.

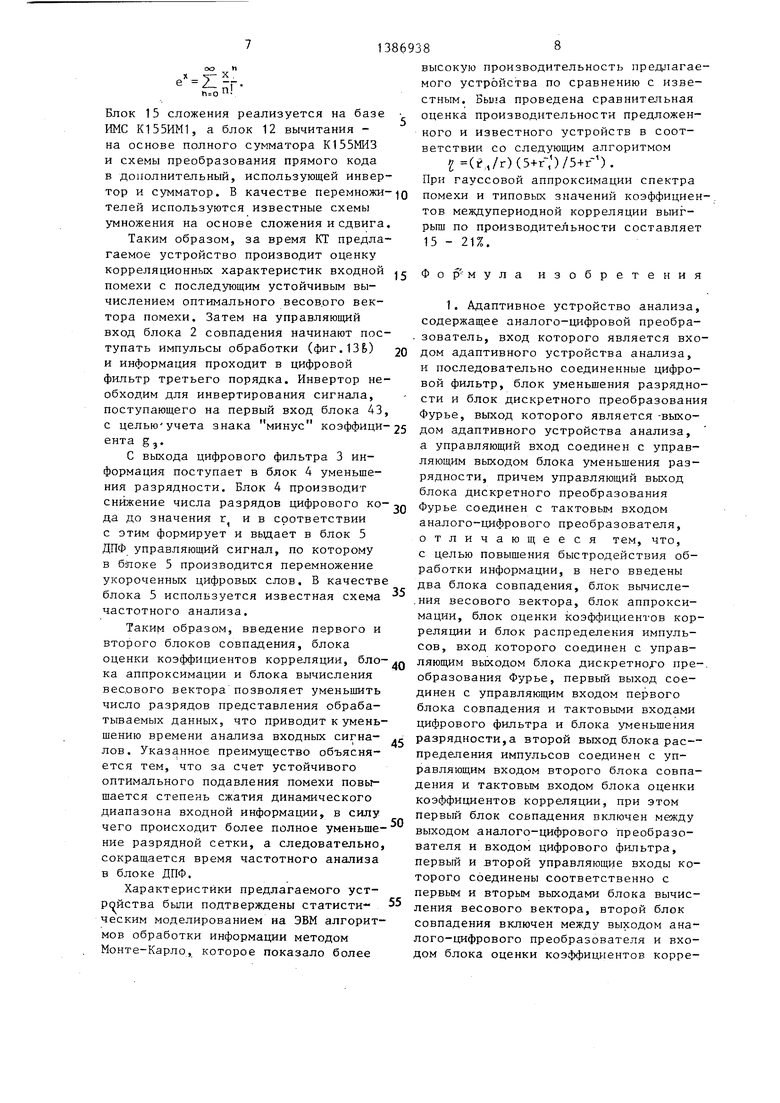

Функциональный преобразователь 13 (фиг.4) содержит блок 23 взятия лога рифма, перемножитель 24, регистр 25 числа и блок 26 взятия экспоненты. Блок 17(18) взятия логарифма (фиг,5) содержит блок 27 сложения, блок 28

блока 10 распределения импульсов вычитания, регистр 29 числа, блок 30

динен с управляющим входом первого блока 2 совпадения и тактовыми входами цифрового фильтра 3 и блока 4 уменьшения разрядности, второй выход

деления, блок 31 вычисления компонен ты ряда и блок 32 суммирования. Блок 31 вычисления компоненты (фиг.6) ряд содержит функциональный блок 33 воз

Рого соответственно являются выход

блока 15 сложения и первый .вход блока 12 вычитания.

Блок 8 аппроксимации (фиг.З) содержит первый и второй блоки 17 и 18 взяти я логарифма, регистр 19 числа и последовательно соединенные первьй блок 20 деления, первый и второй входы которого соединены соответственно с выходами первого и второго блоков 17 и 19 взятия логарифма, третий блок 21 взятия логарифма и второй блок 22 деления, второй вход которого соединен с выходом регистра 9 числа, а выход является выходом блока 8 аппроксимации, первым и вторым входами которого соответственно являются входы первого и второго блоков 17 и 18 взятия логарифма.

Функциональный преобразователь 13 (фиг.4) содержит блок 23 взятия логарифма, перемножитель 24, регистр 25 числа и блок 26 взятия экспоненты. Блок 17(18) взятия логарифма (фиг,5) содержит блок 27 сложения, блок 28

вычитания, регистр 29 числа, блок 30

деления, блок 31 вычисления компоненты ряда и блок 32 суммирования. Блок 31 вычисления компоненты (фиг.6) ряда содержит функциональный блок 33 возведения в степень, перемножитель 34 и регистр 35 числа. Блок 26 взятия экспоненты (фиг.7) содержит блок 36 вычисления компоненты ряда и блок 37 суммирования.

Цифровой фильтр 3 (фиг.8) содержи регистры 38 - 40 сдвига, перемножители 41 и 42 и блок 43 суммирования. Блок 7 оценки коэффициентов корреля- ции (фиг.9) содержит регистры 44 и 45 сдвига, перемножители 46 и 47, квадратор 48, накопители 49 - 51, блоки 52 и 53 деления. Накопитель 49(30) (фиг.10) содержит многоотвод- ный регистр 54 сдвига, блок 55 суммирования, блок 56 совпадения, счетчик 57, компаратор 58 и регистр 59 числа Блок 10 распределения импульсов (фиг.11) содержит первый и второй блоки 60 и 61 формирования адреса и мультиплексор 62. Блок 60(61) формирования адреса (фиг.12) содержит счетчик 63, компаратор 64 и регистр 65 числа.

Устройство работает следующим образом.

В когерентно-импульсных станциях радиолокационного обзора пространств решается задача обнаружения сигнала, отраженного от движущегося объекта, при наличии мощной коррелированной помехи. Эта задача решается системой селекции движущихся полей (СДП). Формирование потока цифровых сигналов в системе СДП происходит следующим образом. Аналоговый видеосигнал пос- туп&ет на вход аналого-цифрового преобразователя (АЦП) 1 с выхода канала фазового детектирования. Так как динамический диапазон входного сигнала определяется мощностью коррелированной помехи, то разрядность АЦП 1 выбирается в соответствии с соотношением

(1)

где г - число двоичных разрядов;

d - динамический диапазон входного сигнала, дБ.

Исходя из формулы (1) разрядность АЦП 1 обычно выбирается равной 10-12 Поскольку доплеровское смещение частоты отраженного от объекта сигнала значительно превосходит максимальную доплеровскую частоту сигнала помехи, то его можно подавить, используя специальные подавления помехи. При этом на выходе фильтра динамический диапазон сигнала будет снижен.

Q 5 0 5

Q

5

0

5

0

5

Уменьшение динамического диапазона приводит к тому, что часть старших разрядов цифрового кода будет все время нулевая, и лишь г, младимх разрядов будут нести информацию. Таким образом, без ухудшения точности обрабатываемых данных появляется возможность снизить разрядность обрабатываемых цифровых кодов до г, . С этой целью в устройстве имеется блок 4- уменьшения разрядности. При этом число г, определяется соотношением

г, (d-Kj/6,(2)

где К - коэффициент подавления помехи в цифровом фильтре.

Для того, чтобы реализовать потенциальные возможности по сжатию разрядности анализируемых данных, необходимо производить сжатие динамического диапазона входных сигналов в полном объеме, т.е. осуществлять оптимальное подавление помехи, которая характеризуется корреляционно матрицей. Аналоговый видеосигнал преобра-- зовывается в АЦП 1 в параллельный г-разрядный код при помощи импульсов дискретизации Т, поступающих с управляемого выхода блока 5 дискретного преобразователя Фурье (ДПФ). В качестве АЦП 1 можно использовать известную схему параллельного преобразования, КОТОРУ10 можно реализовать с использованием компараторов и кодирующего элемента с приоритетом. После этого цифровые коды поступают на входы первого и второго блоков 2 и 6 совпадения.

Устройство работает в двух режимах; в режиме оценки корреляционных характеристик помехи с последующим вычирлением весового вектора фильтра и в. режиме уменьшения разрядности обрабатываемых данных с последующим частотным анализом входного процесса. Для этого блок 10 (фиг. 11) распреде- ляет импульсы дискретизации Т следующим образом. Импульсы Т поступают на вход мультиплексора 62. Причем на его адресные шины с выходов блоков 60 и 61 (фиг.12) формирования адреса поступают адресные сигналы в виде параллельного 2-разрядного кода. Алгоритм работы блока 10 задается следующим образом. Сначала через второй блок 6 совпадения в блок 7 оценки должны пройти М отсчетов входного сигнала, по которым производится оценка корреляционных характеристик. Затем в течении времени Тд(К-М)Т, К М, в блоке 9 определяются весовые коэффициенты фильтра. После чего входная информация должна поступать в цифровой фильтр 3. Для этого в регистрах 65 числа блоков 60 и 61 запи- сьгоаются соответственно цифровые входы .М и К.

Счетчики 63 этих блоков производят4Q

Подсчет числа поступивших на них импульсов Т, а их выходные коды U и Uj сравниваются с кодами М и К в ком13869386

коды оценок с, - Ч коэффициентов корреляции.

Блок 8 аппроксимации (фиг.З) вычисляет значение параметра & согласно алгоритму tJ ln(lTiq. )/In q)/ln2. В блоках 17 и 18 (фиг.З) вычисляются значения In q и In q, которые поступают в блок 20 деления, а затем через блок 21 взятия логарифма - в блок 22 деления. В блоке 22 происходит нормировка относительно значения 1п2, цифровой код которого хранится в регистре 19 числ а. Для вычисления

параторах 64. При выполнении условий

iU, 5 М и DJг К на выходах блоков 60 логарифма используется стандартное |и 61 формируются единичные сигналы, разложение этой функции в ряд Тейло- |которые управляют работой мультиплексора 62. Алгоритм работы блока 62 определяется следующим образом: вьщают- ;я импульсы Т (фиг. 135), если Пцир НОО; импульсы не выдаются если вьщаются импульсы Тов (фиг. 13 8),

ра при X О

1 2h + i 2 In х IK--) ----,

(4)

20

в соответствии с которым на выходах блока 30 деления формируется значение f(x-1)/(х+1), поступающее на входы

в соответствии с которым на выходах блока 30 деления формируется значение f(x-1)/(х+1), поступающее на входы

если 11, где и,иг - управляющий сигнал блока 62. В соответст- параллельно включенных блоков 31 вы- ии с этим на управляющий вход блока 25 числения компоненты ряда (фиг.6). В 6 совпадения поступают импульсы Т блоках 33 возведения в степень значе- бценки, в результате чего информация поступает в блок 7 (фиг.8), который производит оценку коэффициентов кор реляции входной помехи в соответствии.

ние f„возводится в необходимую сте- . пень, затем умножается на соответст30

вующий весовой коэффициент, хранящийся в регистре 35 числа, и поступает в блок 32 суммирования, на выходе которого формируется значение In х. Обычно для достижения требуемой точности используют не более 5-6 членов ряда.

CJ алгоритмом

I А

М

q; 2:u n -u n-i /2:u2 n, (3)

(ПЛh

Ufrf - отсчеты входного сигнала.

35

40

Блок 9 вычисления весового вектора (фиг,2) по поступившим оценкам q и - oi определяет весовые коэффициенты цифрового фильтра 3. Для вычислений был синтезирован цифровой фильтр третьего порядка, весовые коэффициенты которого определяются вьфажением

(i-o+q,+i.

Функциональный преобразователь 13

Цифровые коды импульсами Тд (фиг.ТЗЮ передвигаются по регистрам 44 и 45 сдвига. Затем текущее значе- |ие сигнала возводится в квадрат ь б1поке 48, умножается на задержанные о тсчеты сигнала в перемножителях 46 и 47 и поступает в накопители 40-51 (фиг.10), осуществляющие операцию суммирования в алгоритме (17). Импульсами TO поступившие отсчеты пере- . осуществляет операцию вида двигаются по многоотводному и много- q, где..И, - любое вещественное чис- разрядному регистру 54 сдвига. На выходе блока 55 суммирования формируется текущее значение суммы. Одновременно с этим счетчик 57 производит подсчет числа импульсов Т,, а его выходной код и сравнивается с цифровым кодом М, хранящимся в регистре 59 числа, в компараторе 58, В момент ра- вешства кодов на выходе блока 58 фор- J

„ Z, ло. Значение q , можно представить в

виде

50

, -1 AZli,.

In q, Z, In q,q, exp(Zi), Z Z,ln q, .

(5)

мируется единичньм разрешающий сигнал, и накопленные значения поступают в блоки 52 и 53 деления, на выхо- да;х которых устанавливаются цифровые

В блоке 23 вычисляется In q,, который затем умножается в блоке 24 на цифровой код Z, , храняш:ийся в регистре 25 числа, и поступает в блок 26 взятия экспоненты (фиг.7). Для вычисления е используется стандартное разложение этой функции в ряд Тейлора

Блок 8 аппроксимации (фиг.З) вычисляет значение параметра & согласно алгоритму tJ ln(lTiq. )/In q)/ln2. В блоках 17 и 18 (фиг.З) вычисляются значения In q и In q, которые поступают в блок 20 деления, а затем через блок 21 взятия логарифма - в блок 22 деления. В блоке 22 происходит нормировка относительно значения 1п2, цифровой код которого хранится в регистре 19 числ а. Для вычисления

логарифма используется стандартное разложение этой функции в ряд Тейло-

ра при X О

1 2h + i 2 In х IK--) ----,

(4)

логарифма используется стандартное разложение этой функции в ряд Тейло-

в соответствии с которым на выходах блока 30 деления формируется значение f(x-1)/(х+1), поступающее на входы

параллельно включенных блоков 31 вы- числения компоненты ряда (фиг.6). В блоках 33 возведения в степень значе-

параллельно включенных блоков 31 вы- числения компоненты ряда (фиг.6). В блоках 33 возведения в степень значе-

ние f„возводится в необходимую сте- . пень, затем умножается на соответстпараллельно включенных блоков 31 вы- числения компоненты ряда (фиг.6). В блоках 33 возведения в степень значе-

вующий весовой коэффициент, хранящийся в регистре 35 числа, и поступает в блок 32 суммирования, на выходе которого формируется значение In х. Обычно для достижения требуемой точности используют не более 5-6 членов ряда.

Блок 9 вычисления весового вектора (фиг,2) по поступившим оценкам q и - oi определяет весовые коэффициенты цифрового фильтра 3. Для вычислений был синтезирован цифровой фильтр третьего порядка, весовые коэффициенты которого определяются вьфажением

(i-o+q,+i.

Функциональный преобразователь 13

осуществляет операцию вида q, где..И, - любое вещественное чис-

осуществляет операцию вида q, где..И, - любое вещественное чис-

„ Z, ло. Значение q , можно представить в

q,

виде

осуществляет операцию вида q, где..И, - любое вещественное чис-

, -1 AZli,.

In q, Z, In q,q, exp(Zi), Z Z,ln q, .

(5)

осуществляет операцию вида q, где..И, - любое вещественное чис-

В блоке 23 вычисляется In q,, который затем умножается в блоке 24 на цифровой код Z, , храняш:ийся в регистре 25 числа, и поступает в блок 26 взятия экспоненты (фиг.7). Для вычисления е используется стандартное разложение этой функции в ряд Тейлора

00 n

ZI-r оп

Блок 15 сложения реализуется на базе ИМС К155ИМ1, а блок 12 вычитания - на основе полного сумматора К155МИЗ и схемы преобразования прямого кода в дополнительный, использующей инвертор и сумматор. В качестве перемножителей используются известные схемы умножения на основе сложения и сдвига

Таким образом, за время КГ предлагаемое устройство производит оценку корреляционных характеристик входной помехи с последующим устойчивым вычислением оптимального весового вектора помехи. Затем на управляющий вход блока 2 совпадения начинают поступать импульсы обработки (фиг.13&) и информация проходит в цифровой фильтр третьего порядка. Инвертор необходим для инвертирования сигнала, поступающего на первый вход блока 43, с целью учета знака минус коэффициента gj.

С выхода цифрового фильтра 3 информация поступает в блок 4 уменьшения разрядности. Блок 4 производит снижение числа разрядов цифрового ко- да до значения г и в соответствии с этим формирует и вьщает в блок 5 ДПФ управляющий сигнал, по которому в блоке 5 производится перемножение укороченных цифровых слов. В качестве блока 5 используется известная схема частотного анализа.

Таким образом, введение первого и второго блоков совпадения, блока

оценки коэффициентов корреляции, ляющим выходом блока дискретного пре-.

45

ка аппроксимации и блока вычисления весового вектора позволяет уменьшить число разрядов представления обрабатываемых данных, что приводит к уменьшению времени анализа входных сигналов. Указанное преимущество объясняется тем, что за счет устойчивого оптимального подавления помехи повышается степень сжатия динамического диапазона входной информации, в силу чего происходит более полное уменьшение разрядной сетки, а следовательно, сокращается время частотного анализа в блоке ДПФ.

Характеристики предлагаемого устройства были подтверждены статисти- 55 ческим моделированием на ЭВМ алгоритмов обработки информации методом Монте-Карло, которое показало более

образования Фурье, первый выход соединен с управляющим входом первого блока совпадения и тактовыми входами цифрового фильтра и блока уменьшения разрядности,а второй выход блока рас- пределения импульсов соединен с управляющим входом второго блока совпадения и тактовым входом блока оценки коэффициентов корреляции, при этом первый блок совпадения включен между выходом аналого-цифрового преобразователя и входом цифрового фильтра, первый и второй управляющие входы которого соединены соответственно с первым и вторым выходами блока вычисления весового вектора, второй блок совпадения включен между выходом аналого-цифрового преобразователя и входом блока оценки коэффициентов коррееа.

1386938

высокую производительность предлагаемого устройства по сравнению с известным. Была проведена сравнительная оценка производительности предложенного и известного устройств в соответствии со следующим алгоритмом

I (f,,/r)(5+r-;)/5+r- ). При гауссовой аппроксимации спектра помехи и типовых значений коэффициентов междупериодной корреляции выиг- рьш по производительности составляет 15 - 21%.

20 25

15 Фор мула изобретения

on

35

с целью повышения быстродействия обработки информации, в него введены два блока совпадения, блок вычисле- .ния весового вектора, блок аппроксимации, блок оценки коэффициен1 ов корреляции и блок распределения импульсов, вход которого соединен с управ5

образования Фурье, первый выход соединен с управляющим входом первого блока совпадения и тактовыми входами цифрового фильтра и блока уменьшения разрядности,а второй выход блока рас- пределения импульсов соединен с управляющим входом второго блока совпадения и тактовым входом блока оценки коэффициентов корреляции, при этом первый блок совпадения включен между выходом аналого-цифрового преобразователя и входом цифрового фильтра, первый и второй управляющие входы которого соединены соответственно с первым и вторым выходами блока вычисления весового вектора, второй блок совпадения включен между выходом аналого-цифрового преобразователя и входом блока оценки коэффициентов корреляции, первый и второй выходы которого соединены соответственно с объединенными первыми входами блока вычисления весового вектора и блока ап- проксимации и вторым входом блока аппроксимации, выход которого соединен с вторым входом блока вычисления ве- сового вектора.

zC гд ф

27

-; / 1

Z9

лп

ф

Фи9б

разователя, трегнн вход соединен с выходом регистра числа и одновременно с входом бдока вычитар1ия, выход которого соединен с вторым входом перемножителя .

1

IS

18

1 Ы1ЛС± Г

L 3

21

Il

Ft

32

3i

Фиг 6

фиг. 9

цзигл

Фиг.1г

8

./J

| Адаптивное устройство анализа цифровых сигналов | 1985 |

|

SU1296958A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-04-07—Публикация

1986-11-22—Подача