1

(21)4390232/24-24

(22)09.03„88

(46) 28002„90.Бюл„ № 8

(71)Минский радиотехнический институт

(72)Л.М.Трубицын и А,Г.Саперов

(53)621.398 (088.8)

(56)Авторское свидетельство СССР И- 1325718, кло Н 03 М 13/00, 1986.

(54)УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДВОИЧНОГО КОДА

(57)Изобретение относится к технике передачи данных и может быть использовано для передачи двоичного кода по каналам связи„ Цель изобретения - повышение быстродействия устройства. Устройство содержит,на передающей стороне блок генераторов опорных сигналов, первый, второй и третий блоки перемножителей, блок сумматоров, блок регистров, цифроаналого- вый преобразователь, первый и второй фильтры, блок логического переключения, на приемной стороне блок генераторов опорных сигналов, первый, второй и третий блоки перемножителей, блок сумматоров, блок регистров, первый и второй фильтры, формирователь синхроимпульсов, аналого-цифровой преобразователь,- сумматор, блок памяти, блок счетчиков, пороговый элемент, блок логического переключения, первый и второй элементы задержки. Устройство позволяет распараллелить процесс суммирования значений базисной функции, в результате чего процесс формирования отсчета выходного сигнала не требует выполнения Q раз операции суммирования значений X-Y (К-Т),что позволяет повысить быстродействие устройства,. за.п0 ф-лы, 6 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Линейное устройство коррекции межсимвольной интерференции | 1984 |

|

SU1256213A1 |

| Цифровой формирователь сигналов с манипуляцией минимальным сдвигом | 1987 |

|

SU1494242A1 |

| Устройство для оценки параметров многолучевого канала связи | 1991 |

|

SU1781828A1 |

| Устройство для демодуляции двоичных сигналов | 1983 |

|

SU1085012A1 |

| Адаптивный цифровой корректор | 1979 |

|

SU794734A1 |

| ПРИЕМНИК ЦИФРОВЫХ СИГНАЛОВ | 2010 |

|

RU2423794C1 |

| Цифровой измеритель температуры | 1986 |

|

SU1362952A1 |

| ПРИЕМНИК ПОСЛЕДОВАТЕЛЬНЫХ МНОГОЧАСТОТНЫХ СИГНАЛОВ | 1999 |

|

RU2169993C1 |

| Нелинейно-нелинейное устройство коррекции межсимвольной интерференции при приеме коррелированного сигнала | 1983 |

|

SU1125750A1 |

| Цифровой фильтр с многоуровневой дельта-модуляцией | 1988 |

|

SU1587624A1 |

Изобретение относится к технике передачи данных и может быть использовано для передачи двоичного кода по каналам связи. Цель изобретения - повышение быстродействия устройства. Устройство содержит на передающей стороне блок генераторов опорных сигналов, первый, второй и третий блоки перемножителей, блок сумматоров, блок регистров, цифроаналоговый преобразователь, первый и второй фильтры, блок логического переключения, на приемной стороне блок генераторов опорных сигналов, первый, второй и третий блоки перемножителей, блок 25 сумматоров, блок регистров, первый и второй фильтры, формирователь синхроимпульсов, аналого-цифровой преобразователь, сумматор, блок памяти, блок счетчиков, пороговый элемент, блок логического переключения, первый и второй элементы задержки. Устройство позволяет распараллелить процесс суммирования значений базисной функции, в результате чего процесс формирования отсчета выходного сигнала не требует выполнения Q раз операции суммирования значений XIY(к.Т), что позволяет повысить быстродействие устройства. 1 з.п. ф-лы, 5 ил.

Изобретение относится к технике передачи данных и может быть использовано для передачи двоичного кода по каналам связи

Цель изобретения - повышение быстродействия устройства.

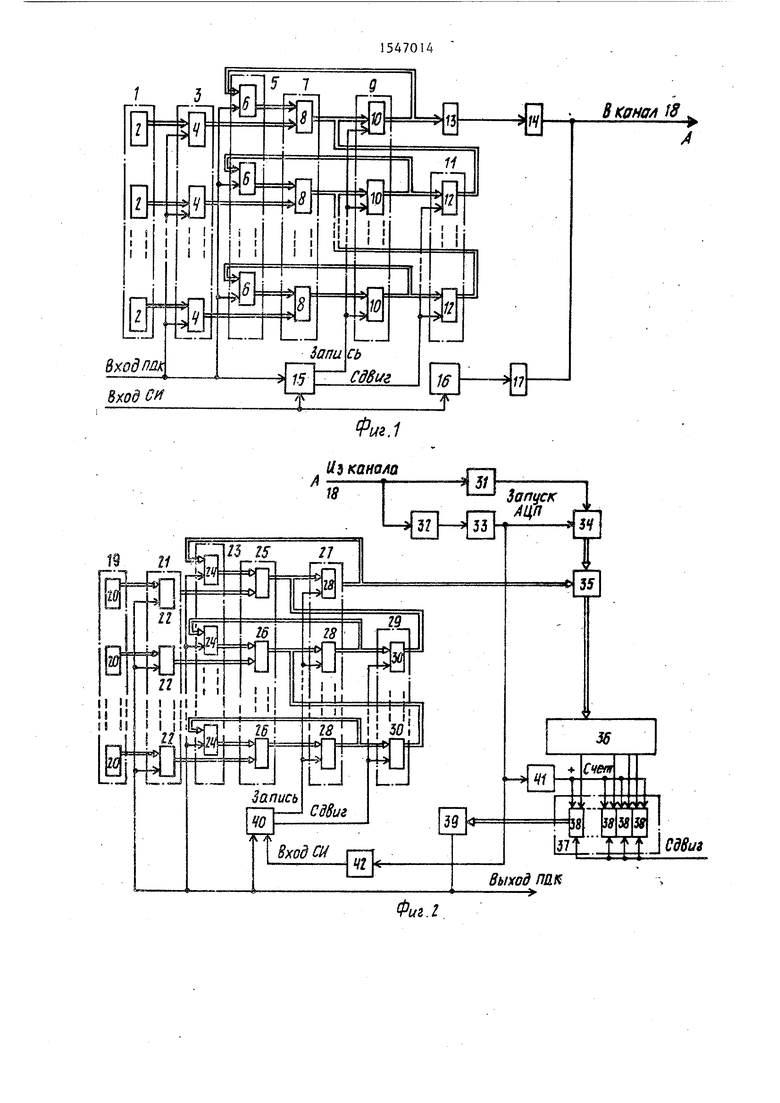

На фиг.1 и 2 представлена схема передающей и приемной стороны устройства; на фиг.З - схема блока логического переключения; на фиг,4 - схема регистра блока регистров; на фиг.З - схема перемножителя; на фиг.6 - временные диаграммы работы устройства.

Устройство для передачи двоичного кода содержит на передающей стороне блок 1 генераторов опорных сигналов, состоящий из Q генераторов 2 опорных сигналов, первый блок 3 перемно- жителей, состоящий из Q перемножите- лей 4, второй блок 5 перемножителей, содержащий Q перемножителей 6, блок 7 Q-двухвходовых сумматоров, содержащий сумматоры 8, блок 9 регистров, содержащий Q регистров 10, третий блок 11 перемножителей, состоящий из Q-1 перемножителей 12, цифроаналогоСП

Јь 1

вый npeoOpasoFSTcru I Зэ перльй фильтр 14, блок 13 ло чческою neot клю -ения, Фор- пов т -чь 16 пинфэ№f lot OBj З/ОрОЙ Ј с)Г 1 С1. JH ,

Чриеш-ая стоге и i о-срхчу 6j / 1 гснзрал иг ов опорных шг-чапои,, сотер якщлй енера-tOi Ob 21 , п- ьгн блс /1 ri гсп , t с -л OF t i

srci o-

OCTCFI J Ч

r j

из ™Ii i ремнозлЧ 1 22, f f

блп rtepoiv ото о Јnet

j O-i ю Јnet CF

с

ai JTJ .,

ч

3 -i , 7 i /iiMiiTopoB 2} (ло i/ e:iC i Co9 сглег/ч т i 0 i 28, vpe1) и блок Г -ioij i.iro т ТЕ. , cofi-p ниич O-I snep j1 i ет J

UerJjb b Jl И i 3 ГСМ 01 Ь j c u.y

одрива-ел

t -T I. (j U Tyj S

з -i J. (Ъ OBOli ДрОО iJSC -. л ЗЛ-i

эр 35 юн JC ijivno r

ччк 7, cccujr 4-ii из L с dr nop-i/j ось и .9 , i ( л С i iteper гю тет л, ci oin i / i

. C.i 4 D 12 „ t x

„ f 0} f и tiijecj or c xjr;o в/ ДЧ /т ((t, ; J-T ifif и тт 41 1Г1 J -IIJU.T 4 и ii ем« г , Ь 1Й 4 ,t i h С

iJ i J Z I . Л СОЯ

.П( С)о - lf

) rf er , i с 12,-2 . Г., о„а

..v ,- frs i-i , it

пио - . OCjJrijOi 1

) V iTir r О LI- titJH jTOT C4 1сЧл t- Чон4

p6-/T98n4P CW Т,ат с

рецаваа ой яво5чпот пекл чосоыо, .Е , : Д б фу tKtc. ч

U

v(r.) Т - Ь С

г vi HI

Гс i

с

С(С г

,. ПО I iа г ел т v

ч

,

L I

- гюряаховы-т

nnei i м 13) en;

(г.)

,/ч , i /1 ар i гелэ - i

ИЗТв| ч АГ ч Гг О T3S,

Цвоячиь. , it /, JJT,C .. т я OBd. еньло ia ( OCN t xriicieri 4a на втопы- я когорог гютсл г н гтя Q-i i слои фу 1 4 ; чз а о ттерем- ожэ я

а н,1ЮГСЯ Н Dti... .J1 1.Ы пгм ОЬ

3 fj y4eie з laic1- t ч„ et

члотг т сумматоров подается значение суммы которая хранился в регистрах 10, из передающего такта сдвига При

Нл

ер г даче

0

i тыгоцак первого и

второго бнгэкоз .с-г J1 -мо сите л ей О и оаер..цчи суммирования гс происходите Г течение качкого такт суммирования (-, змя длительности значения разряда Ч Н Олок 15 управляет запис о в ре

-ic гры 10 с ;ержимо о сумматоров 89 я- unvj з случае передачи 1 в блоЧ0 1Л1 сьпзаетс информация с выхо- .j.ns з Ь, а при передаче О aiy-л с Зат сь Блокируется,, и в ре- г ст 0 о г1аотся прежние значения цмт, Посла fJxia cvi мирования происходи тнкт сдьига (время между , , т умя сосг дт-Ltfl зчг чениями ПДК) В гг- шо оют с faKid блэк 1О влдает ко i Jw rr TJ г тз резуньта е гсго з-f „енис v.y т олг ого ii j (. м вания тог,1упает eprэ (Г j гве1 г jVic iif ч е i элит ели 12 г о IADT 10в «осле оаверпе1 г КО г- ПрО С СОВ б лОК 15 Д,-1

Bai FCb ч лЛоркациг таккь. г L/.f- с гея (пррепьсылается в сл eeji-ыг рьгист р И 1а этом та i „з с исо.ется и наступаем crte L4l TJ I Г ,porai 14.

ол i о пи с с ко о rteoe

, f с t аз i ( 1Спюпим .SOM (фиг(3

,ТС П С СГЧ . Сi.IO (lit luMTiyji fj (CIi „

1 -- i - r i-ie 1 7 - i 3 TO FC вьхо

( xd-ъ I i-i i олв е i ся i vi с 1р.оди1 через схс i Trtrl 44 i ибеспа шч г запись ия- Фо1зып it i л in iiCTDM в; гремя таг CVJMJJ O 5я, Fii ни е ттдтг 0, i& TJ ы чоп,- эте te II J О 1 и

)1 ГГЬ

ПлГ

Г

ь регистра

-i - с на з°п{-с1ъ г я v с Эттемерт 5 ic т i ЗА JCD/ явас г С/ Не1 tien-i, не- с o;n o r i cyi х чровакия тос та зге чаге1 cbop niPOT т-ел, 47 им- tyjrb or о л il б ю i вы- та .л - /т и г Зап с Эти импульсы л J riui гтгфииь чесг- 1 ь калдом ама

I С iЩ Ј.-иЛОГИЧTU пл Чд птсст хи-тул ем двит.

чн t ос за о I, . алло 1 гакге с г - п ва Т а ь л вом . ре 10

1 f Hi el-it o ло обсчета ct ч , г им oai-jajio -cm щэег иДЗО ТРГТ) Ij p - ipBbi . О 14

i а ч т п я в i а . сзч

515470

зи. Для синхронной работы приемника и передатчика в канал передаются, сигналы синхронизации, которые формируются формирователем 16, передаются через второй фильтр 1 7 и имеют форму, приемлемую д-кя передачи по каналу связи, и частоту, отличную от частоты передачи полезного сигнала.

На приемной стороне фильтр 32 настраивается на частоту следования синхросигнала, в результате чего с выхода формирователя 33 начинает поступать синхропоследовательность (Си), которая запускает аналоговый преоб- j 5 разователь 34 и поступает через элемент 42 задержки на вход блока 40

логического переключения. Задержка СИ в блоке 42 необходима на время, в течение которого происходит декоди- 20 рование ГЩК в блоках 34 - 37 и 39. Аналогично блок 41 выдает СИ +счет после окончания работы блоков 34-36.

При появлении импульса + счет в счетчики, на входах которых при- 25 сутствует 1, с выхода блока памяти будет добавлена единица, в противном случае в них ничего не добавяется. После этого по импульсу

Сдвиг состояние каждого j-ro счет- 30 чика заменяется на (j+ O-й (где. j 1,2,3,...,L).

Работа блоков 19,21,23,25,27,29 40 аналогична работе блоков 1,3„ 5,7,9,11 и 15035

Устройств позволяет распараллеить процесс суммирования значений базисной функции. Для каждого сумматора справедливо (с учетом сдвига после каждого такта суммирования) Q

Q-jc-и ( ,Y (K+D-TJ) +

+ X .YCjc-T),

(2)

где X | - значение i-го разряда передаваемого кода;

j - порядковый номер сумматора. Это означает, что процесс формирования отсчета выходного сигнала, опт ределяемого выражением (2), не требует выполнения Q раз операции суммирования значений Х(К-Т) как в из- вестном устройстве. Для этого необходимо лишь к содержимому каждого регистра добавить соответствующие значения базисной функции (в случае .

передачи и полученную сумму с выхода первого регистра направить для передачи в канал. После этого информация регистров сдвигается.

Следовательно,.время формирования отсчета на передаче и обработки на приеме уменьшается в несколько раз, поскольку время выполнения операции сдвига происходит за один такт (как и в известном устройстве в регистре сдвига), а время суммирования двух , слагаемых, входящих в выражение (2), значительно меньше времени суммирования Q значений X.-Y (К-Т).

ормул.а изобретения

0

5

0

5

Q

5

0 5

1„ Устройство для передачи двоичного кода, содержащее на передающей стороне блок генераторов опорных сигналов, соответствующие выходы которого соединены с соответствующими первы-: ми входами первого блока перемножи- телей, цифроаналоговый преобразователь, выход которого через первый фильтр подключен к каналу связи, на приемной стороне аналого-цифровой преобразователь, выходы которого соединены с соответствующими первыми входами сумматора, выходы которого через блок памяти соединены с соответствующими первыми входами блока счетчиков, объединенные вторые входы которого являются управляющим . входам устройства, выход блока счетчиков со- единен с входом порогового элемента, выход которого является выходом устройства, блок генераторов опорных сигналов, соответствующие выходы которого соединены с соответствующими первыми входами первого блока перемножителей, отличающееся тем, что, с целью повышения быстродействия, в устройство на передающей стороне введены блок логического переключения, второй фильтр, формирователь синхроимпульсов, второй и третий блоки леремножителей, блок сумматоров,блок регистров, объединенные вторые входы первого блока перемножителей, объединенные первые входы второго блока перемножителей и первый вход блока логического переключения объединены и являются информационным входом устройства, вход . Формирователя синхроимпульсов объединен с вторым входом блока логического переключения и является сшгхро- входом устройства соответствз ющие выходы первого блока перемножителей соединены с соответствующими гсрвыми входами блока сумматоров, соответствующие выходы которого соединены с соответствующими первыми входами бло ка регистров, соответствующие выходы которого соединены с соотлетствуклци- мл вторыми входами второго блока пе- ремиояштелей. соогвегствуищиа выходы которого соединены с соответствующими вторыыи входаик блока сумкагороЈ„ пар БЫ выход блока логч -еского переклю- чекия соединен с объединенными вторыми входами блока регистров, соотвси ствующие выходы которогоь за исотю- чечием последнею, соединена с соответствующими г ервыми входами ррэг. ье- го блока перемцожителзй соат вег ст-- вуюьще выходы которогэ соецг( с последующими, исключая nepsri, ее от- ветствующими нррвыми в л одами блока регистров, последние вьходы блока

регистров coep,i-iHeTibi с соответ сшую- щими входами дифроан юговохс преобразователя, второй вы .од оиоьа Л)и- чоского переключен -я zoедино обье- диненными вторыми входам -,. гп блока перемноимтелей, выход c Oi & po- вателя синхроямпуттьсс i через ВРОООЙ sjv:ubTp пЬдкяюи/ ы в сачалу связи ь. приампэй c ropcv ч i лю рои фичьтрьц (lop ipo arerrb CKHXIHTHH- пульса, первый т чторо элс мен г за деряски блок J.OTK пс°реклк гения второй и трегип бгок тере шол п ч блок сумма;оро:- d Oj оегнстрот входы первого и второ э фиотьтрок

объедиьены и подключен к канату связиs выход первого фччы)ег соединен с первым входом эналоге.-пифрово- го преобрачоватег яг вь, год второго фильтра через формирователь импульса соединен в вхоцси анапого-цисЬрового чобразователя,, первый вход блоча логического сре ключения объединен с обьетиненнып вторь я входами первого блока пррс- мно,чдателей и с объединенными первыми входами второго блока прреикохнте- лей и подключен к выходу пооогсвого элементаs яыход формировать синхроимпульса через первый jneiit- 17 aa/tepa-

ки соединен с объединенными третьими входами блока счетчиков, а через второй элемент задержки - с вторым входом блока логического переключения, соответствующие выходы первого блока перемножителей соединены с соответствующими первыми входами блока сумматоров, соответствующие выходы которого соединены с соответствующими первыми входами блока регистров, соответствующие выходы которого соединены с соответствующими вторыми входами второго блока перемножителей, со отвег/ствующие выходы которого соединены с соответствующими вторыми входами блока сумматоров, соответствующие выходы блока регистров, кроме последнего, соединен с соответствующими первыми входам третьего блока перемножителей, соответствующие выходы которого соединены с последующими, исключая первый, соответствующими первыми входами Олока ре1истров, последние выходы блока регистров соединены с соответствующими вторыми входа ми сумматора, первый выход блока логк иеского переключения соединен с оьъедиченчыл-т вторыми входами блока регистровj второй ыь.ход блока логического переключения соединен с объе- .ччненными вторыми входами третьего блока перемножителеи.

2„ стройсгво по п„1, о т л и - чающее з я тем,, что блок логическое перс л1 тючепия содержит элемент И элемент ИЛИе элементы задержка, формирователи импульсоз, первый i второй входы элемента И являются соответственно первыми и вторым входами блока лопичесгого переключения, второй вход элемента И объединен с входам: ггарво.го и второго элемента задержки, выход элемента И соединен с первым входом элемента ИЛИ8 выход устарого является первым выходом блока логического переключения, выход первого элемента задержки первый формирователь ичпульсов соединен с вторым входзхч эламента ИЛИ,, ьыход второго элемента задержки сое-- цинен с входам второго формировате- я импульсов, выход которого является вторым ЗЕПСОДОМ олока логического переключения„

gi юн 0)1 д

viomt

is/i ч:

X

J

LJWaJ

снмшпжоннайди у

1Щ

«7lOЈ 7Sl .

4(6,11,12,11,10)

Авторы

Даты

1990-02-28—Публикация

1988-03-09—Подача