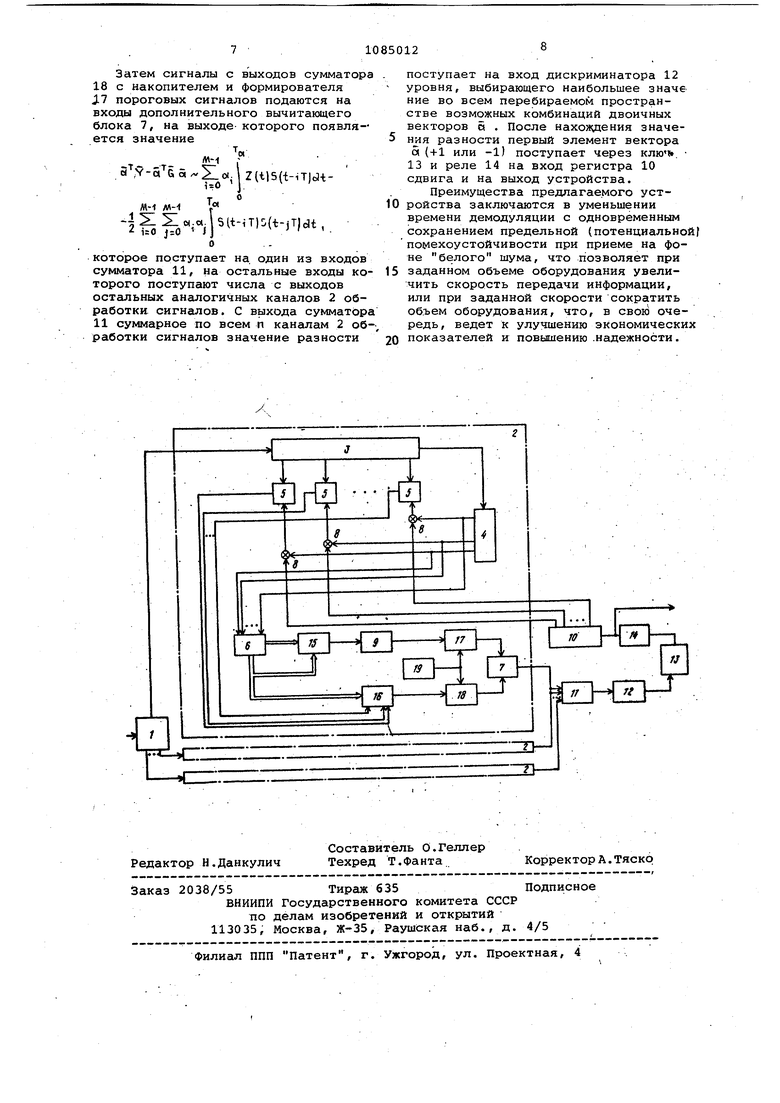

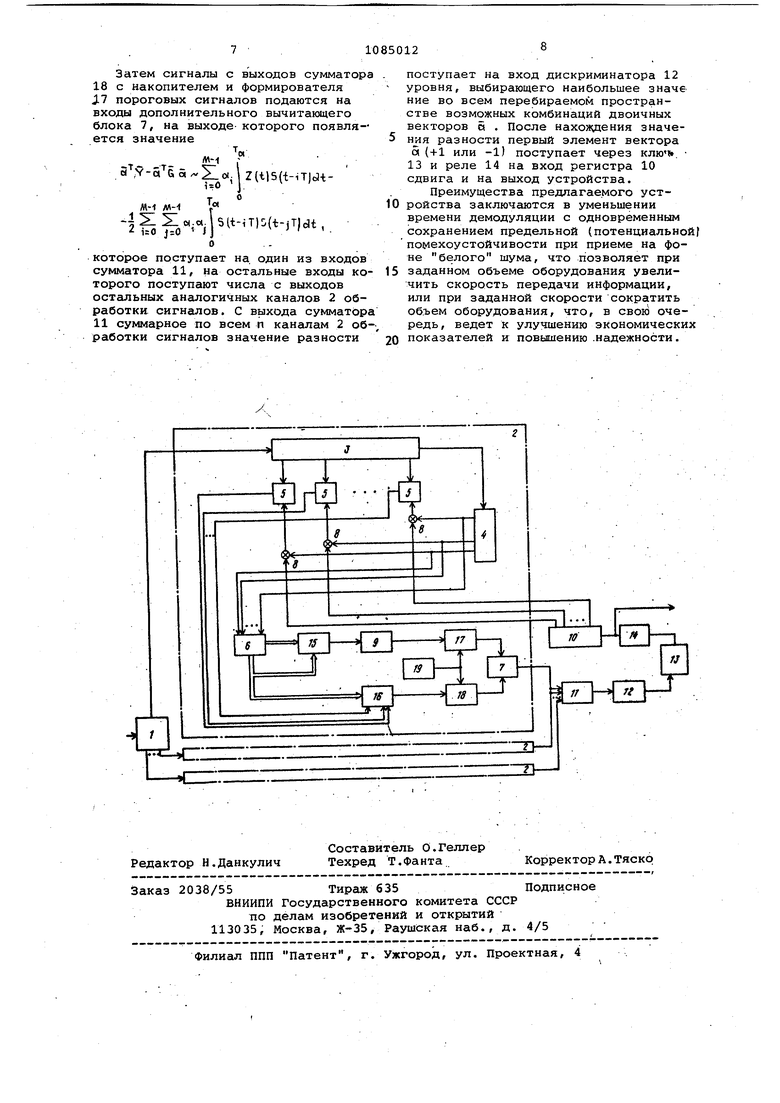

Изобретение относится к электро связи и .может быть использовано в системах передачи дискретной инЛормации по канашам связи с межсим вольной интерференцией. Известно устройство передачи двоичных сигналов в многолучевом канале связи, содержащее блок изме рения импульсной реакции канала, блок формирования опорного сигнала перемножитель, интегратор и регистр TI .Недостатком этого устройства яв ляется низкая помехоустойчивость. ; Наиболее близким техническим решением к изобретению является устройство для демодуляции двоичны сигналов, содержащее сумматор, вых которого через последовательно соединенные дискриминатор уровня и ключ подключен к входу реле, выход которого соединен с входом регистр сдвига, выходы которого подключены к первым входам каналов обработки сигналов, вторые входы которых под ключены к соответствующим выходам преобразователя входного сигнала, причем входы сумматора подключены выходам каналов обработки сигналов каждый из которых содержит линию задержки, первый выход которой соединен с входом блока оценки импульс ной реакции,.выходы которого соединены с первыми входами перемножителеи, вычитающие блоки, первые входы которых подключены к соответствующим вторым выходам линии кй, вход которой является вторым входом канала обработки сигналов, первыми входами которого являются вторые входы перемножителей 2. Однако известное устройство обладает большим временем демодуляции двоичных сигналов. Целью изобретения является умень шение времени демодуляции. Поставленная цель достигается тем, что в устройство для демодуляции двоичных сигналов, содержащее сумматор, выход которого через последовательно соединенные дискриминатор уровня и ключ подключен к входу реле, выход которого соединен с входом регистра сдвига, выходы которого подключены к первым входам каналов обработки сигналов, вторые входы которых подключены к соотве ; Ътвующим выходам преобразователя вх ного сигнала,причем входы сумматора подключены к выходам каналов обработ сигналов, каждый из которых содержит линию задержки, первый выход ко торой соединен с входом блока оценки импульсной реакции, выходы которого соединены с первыми входами пе ремножителей , вычитающие блоки, первые входы которых подключены к соответствующим вторым выходам линии задержки, вход которой- является вторым входом канала обработки сигналов , первыми входами которого являются вторые входы перемножителёй, введены в каждый канал обработки сигналов формирователь опорных сигналов , первый и второй вычислительные блоки, формирователь частичных сумм, формирователь пороговых сигналов, сумматор с накопителем, блок управления и дополнительный вычитающий блок, первый вход которого соединен с выходом сумматора с накопителем, первый вход которого соединен с выходом блока управления и с первым входом формирователя пороговых сигналов , второй вход которого соединен с выходом формирователя частичных сумм, вход которого подключен к выходу первого вычислительного блока, первые входы которого соединены с первыми входами второго вычислительного блока и с первыми выходами формирователя опорных сигналов, входы которого подключе.ны к первым входам перемножителей, выходы которых соединены с втор1ами входами соответствующих вычитающих блоков, выходы которых подключены к. соответствующим вторым входам второго вычислительного блока, выход которого соединен с вторым входом сумматора с накопителем, причем вторые выходы формирователя опорных сигналов соединены с вторыми входами первого вычислительного блока, а выход формирователя пороговых сигналов соединен с вторым входом дополни тельного вычитающего блока, выход которого является выходом канала обработки сигналов. На чертеже изображена структурная электрическая схема предлагаемого устройства. Устройство для демодуляции двоичных сигналов содержит преобразователь 1 входного сигнала, каналы 2 обработки сигналов, линию 3 задержки, блок 4 оценки импульсной реакции, вычитающие блоки 5, формирователь б опорных сигналов, дополнительнйй вычитающий блок 7, перемножители 8, формирователь 9 частичных сумм, регистр 10 сдвига, сумматор 11, дискриминатор 12 уровня, ключ 13, реле 14, первый и второй вычислительные блоки 15 и 16, формирователь 17 пороговых сигналов, сумматор 18 с накопителем, блок 19 управления. Устройство работает следующим образом. Алгоритм оптимального приема на фоне белого шума, предложенный в известном устройстве: MinU Z(,.5(t-,-T) dt «,, где5(|- реаки;ия канала на один ную посылку положитель полярности, Z(-t) - принимаемое колебание, преобразуем следующим образом. Раскрыв квадратные, иу Га тывая, что величина 1 Z(tldt нё висит от а, и потому, ни комбин цию,, доставляющую минимум приве ного выражения, влияния не оказ вает. (1) можно представить в с дующем виде: ГТ«Г 1 ГМ1 (,, .xS{biT fcli М-1 M-l Z{tJ5(t-a)c3t-li:5:a.« л.2 , .0 1 ) (t-iTlS(t-jT)clt В случае дискретной обработк сигналов, алгоритмы(1) и ( 2) м быть записаны в следующем виде: IN г М-1 -|21 SlvS.V.J). им где N - число Дискретных сигнало на интервале О - МТ. jy AIVI М-1 NAIVI М-1 |-o i Vriio|o«.-« -5 k-j Ч-1 Последнее выражение в силу с метричности второго члена в фиг ных .скобках представим в виде М-1 М-1 N Ммх|2 и. (с,.Ццо 1 K-i to triV Сравнивая выражения (Il и ( можно видеть, что устройство, р зующее алгоритм согласно (. 2) , бует гораздо меньшего числа опе ций, чем устройство, функционирующее согласно (). Действительно, при реализации алгоритма согласно V 2I при медленных изменениях параметров карала дечичины: о-- - 515 5 6ij 1,1 k-i k-j. M:- . ri f- f :+ fiiOT такi,j:0,l...W-l, a также.4r f )ri+1 M Iiri+l та к такту не меняются,и поэтому в.. их вычислении на каждом такте обрд-ботки нет необходимости .Поэтому для любого фиксированного числа М перекрывающихся посыпок на приеме, алгоритм, реализующий выражение (24 требует на каждом такте обработки M.-i- операций умножения и операдий обложения для образования . N cyMivi 51 Z, 5. . . где j 0,1,.. .М-1, . Кг-1 к и кроме того, изменений знака и 2 -1 операций сложения для образова Vri. ния всевозможных сумм а также (M-1J 2 операцийслЬжения гля обра.зования всевозможных сумм. «i- -j SMVi а также-2 . вычитаний для вычисления всевозможных значений выражения в фигурных скобках. В целом устройство, реализующее алгоритм в виде 12) требует на каждом такте обработки длительностью N+1 Т секунд М1 операций умножения. 2-1+2 (м-1| операций сложения вычитания). и изменения знака, а также 2 вычитаний выражений в фигурных скобках. Устройство же, реализующее алгоритм в виде (i 1 требует на каждом . такте обработки .Н+1 операций 2.М«4 изменения знака и сложения. 2S операций вычитания, а также 2 N умножений возведений в квадрат-). Отсюда видно, что устройство, реализующее UM , требует на каждом так2те в -. ..., раз меньше операций ум- м- м+1 ,2 ,-. ножения, как наиболее медленной .операции, чем устройство, реализующее алгоритм в виде (1И . Так например, при цифровой регшизации указанных алго)итмов , если П5 ивести операцию умножения к операциям сложения, можно сравнить численно оба алгоритма, при максимальном числе разрядов Q в каждом отсчете. Таким образом, сигнал с выхода канала связи поступает на преобразо ватель 1 входного сигнала, в котором осуществляется операция дискретизации и аналого-цифрового преобра зования. Преобразователь 1 входного сигна ла имеет п выходов, где Р - полоса частот принимаемого видеосигнала, а V - скорость передачи, квадратные скобки означают, что берется целая часть дроби. С .каждого ее выхода на второй .вход соответств ющего канала 2 обработки сигналов поступают отсчеты сигнала-Z (t) вз.ятые через один тактовый интервал каждом канале 2 обработки сигналов отсчеты входного сигнала поступают на вход линии 3 задержки и затем в блок 4 оценки импульсной реакции, где формируются величины SQ , 5 , ... ,5 - , которые представляют собой отсчеты реакции канала связи на одиночную пасьшку , С выхода блока 4 оценки импульсной реакции отсчеты сигнала поступают на первые входы перемножителей 8, на вторые входы которых поступают посылки + 1 с выходов регистра 10 сдвига, а выходы перемножителей 8 соединены со вторы-ми входами вычита ющих блоков 5, на первые входы которых поступают отсчеты сигнала Z(t Т.е. на выходе вычитающих блоков 5 формируются отсчеты разностного сиг нала z (tI.которые отличаются от отсчетов принимаемого сигнала Z{tl тем, что из них вычтены последействия от всех преддаествующих досылок, z((t)- a-s(biT). Кроме того, отсчеты с выхода бло ка 4 оценки импульсной .реакции поступают на формирователь б опорных сигналов., задачей которого является формирование матриц-столбцов которые; представляют собой совокупности отсчетов оценки реакции канала связи на одиночную посылку, сдвинутые друг относительно друга на интервал Т и ограниченные одним и тем же интервалом анализа Т.МТ: S, выхода формирователя 6 опорных сигналов матрип л S Q - S поочередно поступают на первые входы второго вычислительного блока 16, на вторые входы которого поступают значения отсчетов Zlt-l с выходов вычитающих блоков 5. Ыа выходе формируется мат рица-столбец и Матрица-столбец 5 поступает на второй вход сумматора 18 с накопителем, первый вход которого соединен с выходом блока 19 управления, который выдает всевозможные ва-рианты двоичных векторов: « «01«1 -.«M-Ji Ч. . т.е. получаем на выход«5 М-1 г. . а. Z(t)S(4:-iT)c|-t : Одновреме.нно с этим сдвинутые относительно друг друга сигналы ,. с первых и вторых выходов формирователя 6 опорных .сигналов поступа ют на первый и второй входы первого вычислительного блока 15, на выходе которого формируются элементы квадратной матрицы §,5Г5.- причем ,т.е. матрица треугольная выше диагонали 4§о5.(5;§,1---(§; vJ (5,)-. (5;v.) 0(S:-2VJ О .О которые поступают на вход формирователя 9 частичных сумм, на выходе которого формируется матрица-столбец X, элементами которой являются суммы элементов строк и столбцов матрицы Q с одинаковым сначала, первым индексом до достижения диагонали/ а затем-того же значения вторым индексом: . (§:,)K.h---(i,«i х (5: J---;К§.-,№;Д KvJ(sIvJ-45«Vi) с выхода формирователя 9 частичны. сумм матрицы-столбцы X поступают на второй вход формирователя 17 пороговых сигналов, на первый вход которого поступает двоичный вектор 01 ) а на выходе появляется величина М-1 Л-2 . N/ ,-i () . .- .a. S(t-iT)S(i-jT,lat . i i:o - J

Затем сигналы с выходов сумматора 18 с накопителем и формирователя Д7 пороговых сигналов подаются на входы дополнительного вычитающего блока 7, на выходе- которого появляется значение

.. и

Т - -т --Л I

,5 ,-5 .o.Z(tl5(b,T)cliт о

М-1 Л1-1 ..«

(HT)dt,

л

которое поступает на. один из входов сумматора 11, на остальные входы которого поступают числа с выходов остальных аналогичных каналов 2 обработки сигналов. С выхода сумматора 11 суммарное по всем п каналам 2 обработки сигналов значение разности

поступает на вход дискриминатора 12 уровня, выбирающего наибольшее значе ние во всем перебираемом пространстве возможных комбинаций двоичных векторов б . После нахоядаения значения разности первый элемент вектора «(+1 или -1) поступает через клю 13 и реле 14 на вход регистра 10 сдвига и на выход устройства.

Преимущества предлагаемого устройства заключаются в уменьшении времени демодуляции с одновременным сохранением предельной (потенциальной помехоустойчивости при приеме на фоне белого шума, что позволяет при

заданном объеме оборудования увеличить скорость передачи информации, или при заданной скорости сократить объем оборудования, что, в свою очередь, ведет к улучшению экономических

показателей и повышению .надежности.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДВОИЧНЫХ СИГНАЛОВ | 1991 |

|

RU2065668C1 |

| Устройство для демодуляции двоичных сигналов | 1983 |

|

SU1146827A2 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ В МНОГОЛУЧЕВОМ КАНАЛЕ СВЯЗИ | 2004 |

|

RU2267230C1 |

| Устройство демодуляции двоичных сигналов | 1986 |

|

SU1394457A1 |

| Линейное устройство коррекции межсимвольной интерференции | 1984 |

|

SU1256213A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ В МНОГОЛУЧЕВОМ КАНАЛЕ СВЯЗИ И ДЛЯ ОЦЕНКИ ПАРАМЕТРОВ КАНАЛА | 2004 |

|

RU2271070C2 |

| Цифровой когерентный демодулятор сигналов с двоичной относительной фазовой манипуляцией | 2020 |

|

RU2748858C1 |

| Демодулятор фазоманипулированного сигнала | 1978 |

|

SU758560A1 |

| Устройство для демодуляции двоичных сигналов | 1983 |

|

SU1107326A1 |

| СПОСОБ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2102836C1 |

УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ .ДВОИЧНЫХ СИГНАЛОВ, содержащее сумматор, выход которого через последовательно соединенные дискриминатор уровня и ключ подключен к входу реле, которого соединен с sxoдом регистра сдвига, выходы которо- . го подключены к первым входам каналов обработки сигналов, вторые входы которых подключены к соответствую щим выходам преобразователя входного сигнала, причем входы сумматора подключены к выходам каналов обработки сигналов, каждый из которых содержит линию задержки, первый выход которой соединен с входом блока оценки импульсной реакции,выходы которого соединены с первыми входами перемножителей, вычитающиэ блоки, первые входы которых подключены к соответствующим вторым выходам линии задержки, вход которой является вторым входом канала обработки сигналов,первыми входами которого являются вторые входы перемножителей, отличающееся тем, что, с целью уменьшения времени демодуляции, в него введены в каждый канал обработки сигналов формирователь опорных сигналов, первый и второй вычислительные блоки, формирователь частичных сумм, формирователь пороговых сигналов, сумг.1атор с накопителем, блок, управления и дополнительный вычитающий блок, первый, вход которого соединен с выходом сумматора с накопителем, первый вход которого соединен с выходом блока управлении и с первым входом формирователя пороговых сигналов, второй вход которого соединен с выходом формирователя частичных сумм, eg вход Которого подключен к -выходу (Л первого вычислительного блока, первые входы которого соединены с первыг и входами второго вычислительного блока и с первьции выходами формирователя опорных сигналов, входы которого подключены к первым входам перемножителей, выходы которых соединены с вторыми входами соответствующих вычитающих блоков, 00 выходы которых подключе ны к соответсд ствующим.вторым входам второго вычислительного блока,выход которого соединен с вторым входом сумматора с накопителем, причем вторые выходы формирбвателя опорных сигналов соединены i к с вторыми, входами первого вычислитель ного блока, а выход формирователя пороговых сигналов соединен с вторым входом дополнительного вычитающего блока, выход которого является выходом канала обработки сигналов.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| БИБЛИОТЕКА "'С. (С. Бек | 0 |

|

SU341170A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для демодуляциидВОичНыХ СигНАлОВ | 1979 |

|

SU794767A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-04-07—Публикация

1983-01-10—Подача