| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой формирователь сигналов с манипуляцией минимальным сдвигом | 1985 |

|

SU1282351A1 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Устройство для приема дискретной информации | 1987 |

|

SU1501298A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Устройство формирования кода фазы сигнала с линейной частотной модуляцией | 1984 |

|

SU1265986A1 |

| Устройство фазовой автоподстройки частоты | 1985 |

|

SU1288907A1 |

| Преобразователь фазового сдвига в цифровой код | 1982 |

|

SU1056073A1 |

| Устройство управления скоростью дискового носителя информации | 1986 |

|

SU1455361A1 |

| Приемник многочастотных сигналов | 1987 |

|

SU1478368A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1983 |

|

SU1840196A1 |

Изобретение относится к дискретной передаче информации и может найти применение в системах передачи сигналов с фазовой манипуляцией. Цель изобретения - повышение быстродействия. Формированитель содержит два источника сообщений 1,2, сумматор 5 по модулю два, инвертор 7, коммутаторы 9, 13, г-р 11 частот, полосовой фильтр 19. Поставленная цель достигается введением арифметическо-логического блока 3, двух сумматоров 4, 10, двух регистров 6, 14, перемножителя 8, блока 12 сравнения, элемента задержки 15, вычитающего блока 16, блока 17 постоянной памяти, ЦАП 18. 2 ил.

Фиг. /

Изобретение относится к дискретной передаче информации и может найти применение в системах передачи сигналов с фазовой манипуляцией.

Цель изобретения - повышение быстродействия .

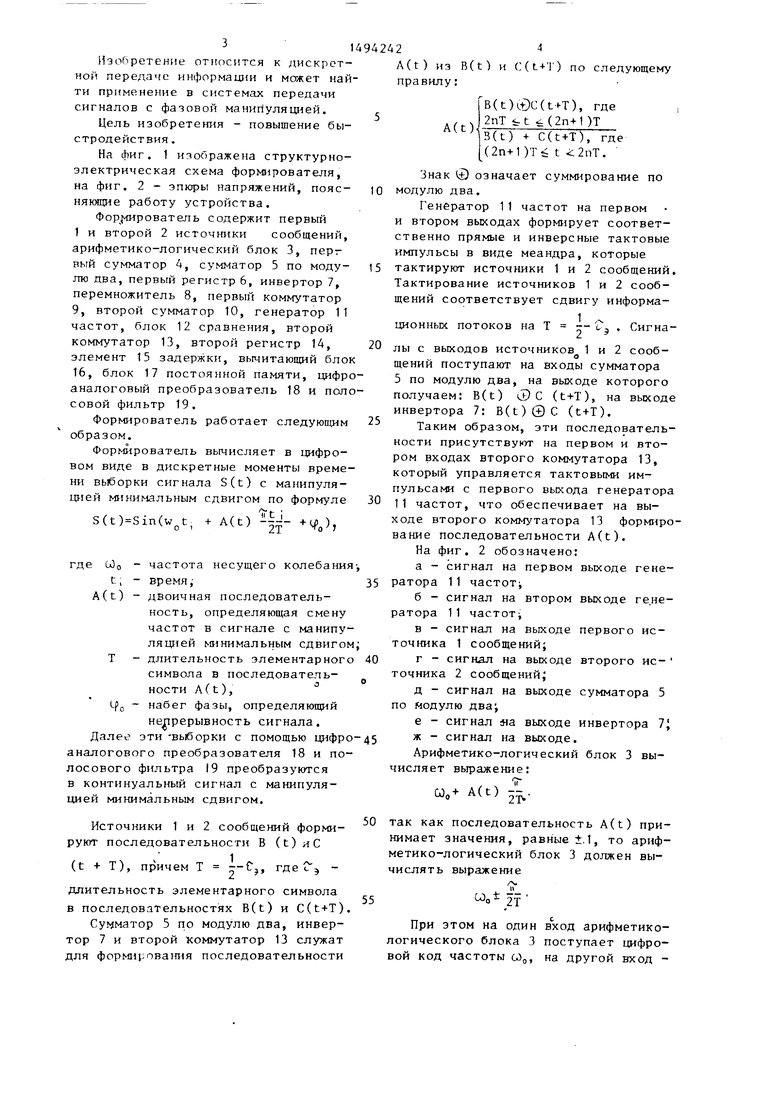

На фиг. 1 изображена структурно- электрическая схема формирователя, на фиг. 2 - эпюры напряжений, поясняющие работу устройства.

Фор шрователь содержит первый 1 и второй 2 источники сообщений, арифметико-логический блок 3, перт вый сумматор 4, сумматор 5 по модулю два, первый регистр 6, инвертор 7, перемножитель 8, первый коммутатор 9, второй сумматор 10, генератор 11 частот, блок 12 сравнения, второй коммутатор 13, второй регистр 14, элемент 15 задержки, вычитающий блок 16, блок 17 постоянной памяти, цифро аналоговый преобразователь 18 и полосовой фильтр 19.

Формирователь работает следующим образом.

Формирователь вычисляет в цифровом виде в дискретные моменты времени выборки сигнала S(t) с манипуляцией минимальным сдвигом по формуле

S(t)Sin(,

A(t) )

где ООо - частота несущего колебания-,

t, - время,-

A(t) - двоичная последовательность, определяющая смену частот в сигнале с манипуляцией минимальным сдвигом; Т - длительность элементарного символа в последователь- ности Aft), (-Рд - набег фазы, определяющий

непрерывность сигнала. Далее эти-выборки с помощью цифроаналогового преобразователя 18 и полосового фильтра 19 преобразуются в континуальный сигнал с манипуляцией минимальным сдвигом.

Источники 1 и 2 сообщений формируют последовательности В (t) иС

(t + Т), причем Т

.--..

где с э

длительность элементарного символа в последовательностях B(t) и C(t+T). Су матор 5 по модулю два, инвертор 7 и второй коммутатор 13 служат для формирования последовательности

А (t ) из правилу;

B(t) и C(t-i-T) по следующему

A(t)

B(t)0C(t-t-T), где i2nT t ( )Т B(t) + C(t+T), где (2n+l )Ть t 2пТ.

Знак 0 означает суммирование по модулю два.

Генератор 1 1 частот на первом и втором выходах формирует соответственно прямые и инверсные тактовые импульсы в виде меандра, которые тактируют источники 1 и 2 сообщений. Тактирование источников 1 и 2 сообщений соответствует сдвигу информационных потоков на

1 Т 2- -э

Сигна0

5

0

5

0

з

лы с выходов источников 1 и 2 сообо

щений поступают на входы сумматора 5 по модулю два, на выходе которого получаем: B(t) CD С (t+T), на вькоде инвертора 7: B(t)(±)C (t+T).

Таким образом, эти последовательности присутствуют на первом и втором входах второго коммутатора 13, который управляется тактовыми импульсами с первого выхода генератора 11 частот, что обеспечивает на выходе второго коммутатора 13 формирование последовательности A(t).

На фиг. 2 обозначено:

а - сигнал на первом выходе генератора 1 1 частот

б - сигнал на втором выходе генератора 1 1 частот

в - сигнал на выходе первого источника 1 сообщений;

г - сигнал на выходе второго не- точника 2 сообщений

д - сигнал на выходе сумматора 5 по Модулю два

е - сигнал на выходе инвертора 7i

ж - сигнал на выходе.

Арифметико-логический блок 3 вычисляет вьфажение:

СО

0- A(t) --.

так как последовательность A(t) принимает значения, равные. 1, то арифметико-логический блок 3 должен вычислять выражение

COot 2f

При этом на один вход арифметико- логического блока 3 поступает цифровой код частоты сОд, на другой вход цифровой код

частоты -на управляющий вход - с выхода второго коммутатора 13 последовательность A(t). В зависимости от последовательности A(t) арифмед-ико-логический блок 3 работает либо в режиме сложения, либо в режиме вычитания.

Дискретные моменты времени, в ко- торые вычисляются выборки сигнала S(t), задаются с помощью второго сумматора 10 и второго регистра 14 следующим образом.

На вход второго сумматора 10 с вы хода второго регистра 1.4 поступает цифровой код предьщущего значения

времени t,,. На другой вход второго сумматора 10 поступает цифровой код приращения времени &t, причем &t

--, где Fg - частота дискретизации

сигнала S(t), выбираемая по теореме Котельникова,

На выходе второго сумматора 10 имеется цифровой код текущего значения времени t-, которьй записьгоается во второй регистр 14 по заднему фронту тактовых импульсов с частотой дискретизации, поступающих с третьего выхода генератора 11 частот.

На первый вход перемножителя 8 поступает с выхода арифметико-логического блока 3 цифровой код выражения :

W

с A(t) -На второй вход перемножителя 8 поступает с выхода второго регистра 14 цифровой код значения времени. На выходе перемножителя 8 имеется цифровой код выражения

(Uo- A(t) 5т Ч .

Цифровой код с выхода перемножителя 8. поступает на первый вход первого сумматора 4, на второй вход которого поступает с выхода первого регистра 6 цифровой код начальной фазы ,

На выходе первого сумматора 4 получаем цифровой код выражения:

W«t

+ A(t) --- -Цр„.

С выхода первого сумматора 4 цифровой код поступает на первый вход вычитающега блока 16 и на первый вход блока 12 сравнения, где он

ю

«242

сравнивается с цифрозы .м . -ла 2 п п , поступаюпрчм на второй иход блока 12 сравнения. На второй вход вычитающего блока 16 с выходом первого коммутатора 9 поступает либо нуль, либо число 2 и ь . В том случае, если

i

Cj,t;-bA(t)---- -ьц 2nG-, на выходе блока 12 сравнения бу дет

I на выходе первого ком9 также О,

т,е, на выходе вычитающего блока ровой код выражения:

7-ti С0„1.+ A(t) - - -Q o .

2Т

Если

7t;

C0,t;+ A(t) --- .i 2п ,

то на выходе блока 12 сравнения будет лог, 1, На выходе первого коммутатора 9 - число 2 пТ, а на выходе вычитающего блока 16 при условии 51п(х-2п1Г) sinx - цифровой код

li i CJot;+ A(t) +4-0- 2п7,

Задержанная с помощью элемента 15 задержки на время, необходимое для срабатывания первого коммутатора 9 и вычитающего блока 16, лог. 1 с выхода блока 12 сравнения своим фронтом записывает в первый регистр 6 выражение

(.. W,t;-H A(t) ---- +t;, -2пГ,

которое далее представляет собой значение начальной фазы и обнуляет второй регистр 14, Дгшее работа осуществляется аналогично изложенному.

С выхода вычитающего блока 16 цифровой код поступает на адресные входы блока 17 постоянной памяти, в котором записана таблица синусов, и на его выкоде присутствует двоичное чи-

ело, равное

Vi SinCu.t; + A(t) --- -t-cf,,

С помощью цифроаналоговбго преоб- разователя 18 информация с выхода блока 17 постоянной памяти преобразуется в сигнал с амплитудно-импульсной модуляцией. Амплитуда импульсов в этом сигнале соответствует числу

Sin(Q.t;

A(t) ),

период импульсов равен Т, длительность импульса задается сигналом с выхода генератора 11 частот и определяется из необходимой точности восстановления сигнала.

С помощью полосового фильтра 19 из сигнала с амплитудно-импульсной модуляцией выделяется первая гармоника и на его выходе присутствует аналоговый сигнал S(t).

Формула изобретения Цифровой формирователь сигналов с манипуляцией минимальным сдвигом, содержащий два источника сообщений, первый коммутатор, полосовой фильтр, генератор частот и последовательно соединенные сумматор по модулю два, инвертор и второй коммутатор, причем выходы источников сообщений подключены к входам сумматора по модулю два, выход которого подключен к второму входу второго коммутатора, первый выход генератора частот подключен к третьему входу второго коммутатора и входу первого источника сообщений, а второй выход генератора частот подключен к входу второго источника сообщений, отличающийся тем, что, с целью повышения быстродействия, в него введены первый регистр, последовательно сое- .диненные арифметико-логический блок, перемножитель, первый сумматор, вычитаюошй блок, блок постоянной памяти и цифроаналоговый преобразователь, последовательно соединенные

второй сумматор и второй регистр, последовательно соединенные блок сравнения и элемент задержки, выход которого подключен к тактовому входу первого регистра и установочному вхоДУ второго регистра, выход которого подключен к второму входу перемножителя и входу второго сумматора, выход вычитающего блока подключен к информационному входу первого регистра, выход которого подключен к второму входу первого сумматора, выход которого подключен к первому входу блока сравнения, второй вход и выход которого соединен соответственно

с информационным и управляющим входами первого коммутатора, выход которого подключен к второму входу вычитающего блока, выход второго коммутатора подключен к управляющему вхоДУ арифметико-логического блока, выход цифроаналогового преобразователя подключен к входу полосового фильтра, а третий выход генератора частот подключен к тактовым входам второго регистра и дифроаналогового преобразователя ,

| Цифровой формирователь сигналов с манипуляцией минимальным сдвигом | 1985 |

|

SU1282351A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-07-15—Публикация

1987-08-10—Подача