1

(21)4137793/24-24

(22)28.07.86

(46) 07.03.90. Бюл. N- 9

(71)Пензенский политехнический институт

(72)А.Л.Држевецкий, Р.А.Абульханов, С.Т,Баканов и А.Б.Левин

(53)681.327.12 (088.8)

(56)Авторское свидетельство СССР № 424191, кл. G 06 К 9/00, 1974.

Авторское свидетельство СССР № 1527646, кл. G 06 К 9/46, 1985.

(54)УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ И КОДИРОВАНИЯ ИЗОБРАЖЕНИЙ ОБЪЕКТОВ

(57)Изобретение относится к области

автоматики, в частности к устройству для считывания и кодирования изображений объектов, и может быть использовано при распознавании образов. Цель изобретения состоит в расширении функциональных возможностей устройства. Цель достигается путем введения кодового описания и коррекции структуры изображений объектов, что обеспечивается введением пяти блоков памяти, двух дешифраторов, пятого элемента И, четвертого элемента задержки, первого и второго элементов ИЛИ, блока маркирования изображений и коммутатора. 9 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания и кодирования изображений объектов | 1988 |

|

SU1631563A1 |

| Устройство для селекции дефектов изображений объектов | 1988 |

|

SU1631562A1 |

| Устройство для селекции изображений | 1988 |

|

SU1638718A1 |

| Устройство для селекции изображений | 1991 |

|

SU1837335A1 |

| Устройство для определения углового положения указателя стрелочных приборов | 1987 |

|

SU1532812A1 |

| УСТРОЙСТВО ДЛЯ СЕЛЕКЦИИ ИЗОБРАЖЕНИЙ ОБЪЕКТОВ | 1990 |

|

RU2032218C1 |

| Устройство для селекции изображений объектов | 1987 |

|

SU1608710A1 |

| Устройство для подсчета количества изображений объектов | 1986 |

|

SU1383413A1 |

| КОДОИМПУЛЬСНОЕ ПЕРЕДАЮЩЕЕ УСТРОЙСТВО С СОКРАЩЕНИЕМ ИЗБЫТОЧНОСТИ ИНФОРМАЦИИ | 2001 |

|

RU2234738C2 |

| Устройство для селекции изображений объектов | 1988 |

|

SU1608711A1 |

Изобретение относится к области автоматики, в частности к устройству для считывания и кодирования изображений объектов, и может быть использовано при распознавании образов. Цель изобретения состоит в расширении функциональных возможностей устройства. Цель достигается путем введения кодового описания и коррекции структуры изображений объектов, что обеспечивается введением пяти блоков памяти, двух дешифраторов, пятого элемента И, четвертого элемента задержки, первого и второго элементов ИЛИ, блока маркирования изображений и коммутатора. 9 ил.

Изобретение относится к автоматике, в частности к устройствам для считывания и кодирования изображений объектов, и может быть использовано при решении задач распознавания изображений объектов.

Цель изобретения - расширение функциональных возможностей устройства путем введения кодового описания и коррекции структуры изображений объектов.

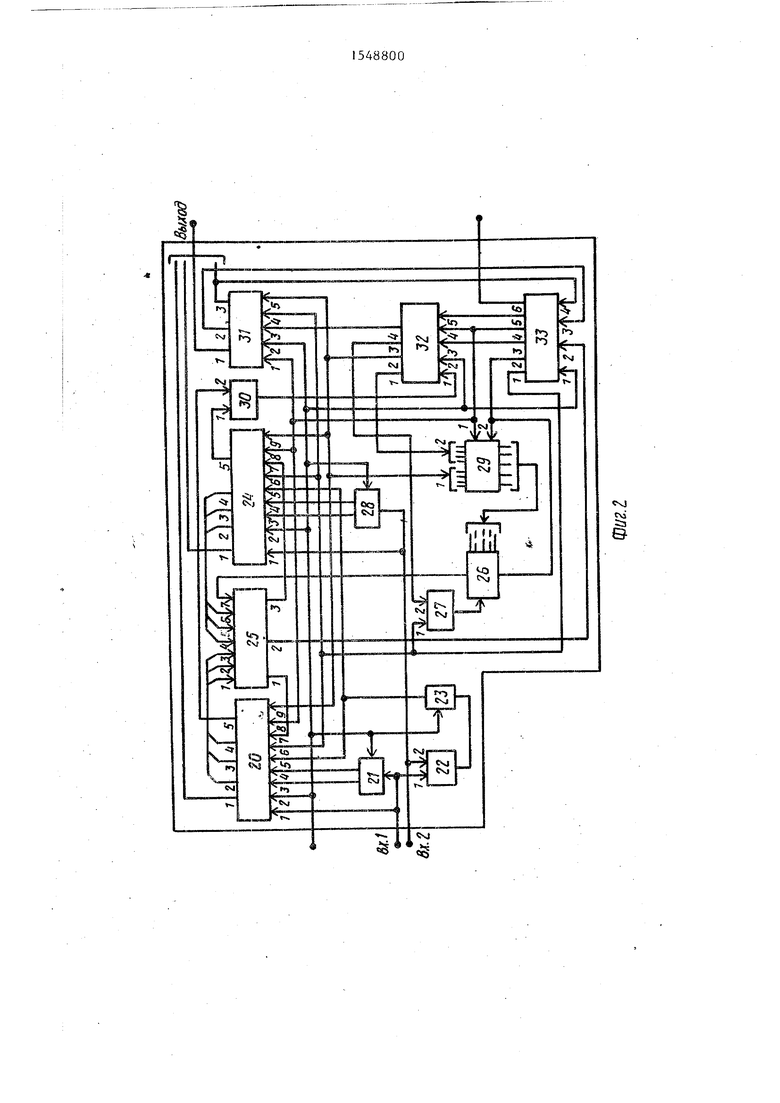

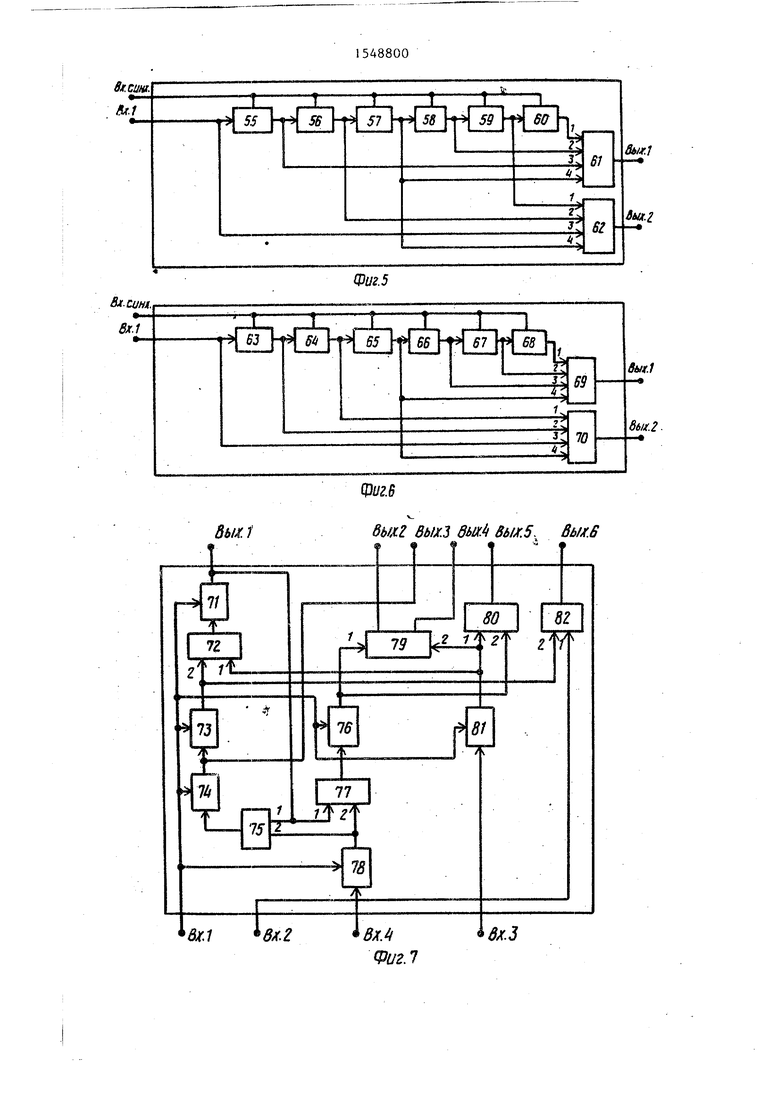

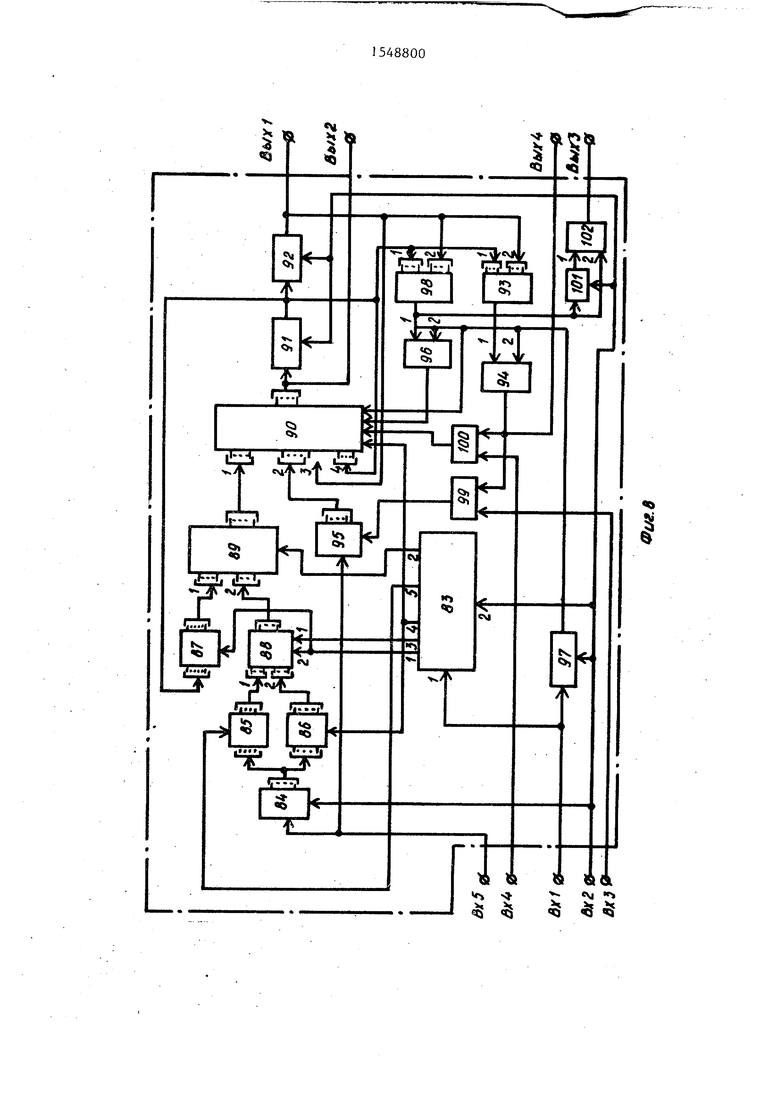

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - конкретное конструктивное выполнение узла структурного описания изображений; на фиг. 3 - первый и второй блоки памяти; на фиг. 4 - пятый блок памяти; на фиг. 5 и 6 - первый и второй дешифраторы соответственно; на фиг. 7 - управления; на фиг. 8 - узел маркировки; на фиг. 9 - схема управления.

Устройство (фиг. 1) содержит блок 1 ввода изображений, блок 2 преобразования изображений, включающий узел 2-1 цифровой фильтрации и узел 2-2 расфокусировки, блок 3 синхронизации, первый селектор 4 признаков изображений объектов, включающий узел 4- 1 цифровой фильтрации, узел 4-2 расфокусировки и узел 4-3 выделения признаков, второй селектор 5 признаков изображений объектов, включающий узел 5-1 цифровой фильтрации, узел 5-2 расфокусировки и узел 5-3 выделения признаков, первый элемент 6 задержки, первый элемент И 7, второй элемент 8 задержки, второй 9, третий 10 и четвертый П элементы И, элемент 12 задержки и узел 13 структурного описания изображений объектов.

На фиг. 1 также показаны блок 14 вывода и выходы 15-19.

Узел 13 структурного описания .(фиг. 2) содержит первый блок 20 памяти, первый дешифратор 21, пятый элеС/

с

Сг

4 ос

ос

;ент И 22, четвертый элемент 23 задержки, второй блок 24 памяти, третий блок памяти 25 j, выполненный в виде ПЗУ, четвертьй блок 26 памяти, выполненный в виде ОЗУ, первый элемент ИЛИ 27, второй дешифратор 28, коммутатор 29, второй элемент ИЛИ 30, пятый блок 31 памяти, блок 32 маркирования изображения и блок 33 управления.

Первый 20 и второй 24 блоки памяти (фиг. 3), выполняющие функции накопления признаков, содержит ОЗУ 34, узлы 35-37 памяти ОЗУ 38, элементы 39

и 40 задержки, узел 41 маркировки, элемент 42 задержки, элемент ИЛИ 43, элемент И 44, элементы ИЛИ 45 и 46 и элемент 47 задержки.

Пятый блок 31 памяти (. 4), предназначенный для хранения координат узлов, содержит счетчик 48, дешифратор 49, ОЗУ 50 и 51, элементы ИЛИ 52 и 53 и элемент НЕ 54.

Первый дешифратор 21 (фиг. 5), предназначенный для выделения фрагментов вертикали, содержит элементы 55-60 задержки и узлы 61 и 62 дешифрации .

Второй дешифратор 28 (фиг. 6), предназначенный для выделения фрагментов горизонтали, содержит элементы 63-68 задержки и узлы 69 и 70 дешифрации.

Блок 33 управления (йиг. 7) содержит элемент 71 задержки., элемент ИЛИ 72, элементы 73 и 74 задержки, дешиф- ратор 75, элемент 76 задержки, элемент И 77Э элемент 78 задержки, триггер 79, элемент ИЛИ 80, элемент 81 задержки и дешифратор 82.

Узел 41 маркировки (фиг. 8) содержит блок 83 управления, счетчик 84, регистры 85 и 86, коммутаторы 87 и 88 ОЗУ 89, коммутатор 90, элементы 91 и 92 задержек, дешифратор 93, элемент И 94, счетчик 95, дешифратор 96, элемент 97 задержки, блок 98 сравнения, элементы ИЛИ 99 и 1009 элемент 101 задержки и дешифратор 102.

Блок 83 управления (фиг. 9) содержит элемент 103 задержки, дешифратор 104, элементы 105 и 106 задержки, элемент ИЛИ 107, элемент И 108, элемент 109 задержки и элемент ИЛИ 110.

Устройство работает в двух режимах в режиме считывания и в режиме вьда- чи информации.

В режиме считывания отсчеты бинарного изображения, полученные на вы

Q

5

0

5

30

45

50

ходе блока 1 отсчет за отсчетом вдоль строк изображения и строка за строкой поперек строк, подаются с частотой, определяемой блоком 3 синхронизации, на вход узла 2-1 блока 2. С выхода узла 2-1 сигнал поступает,на вход узла 2-2. Сигналы с выхода блока 1 одновременно с поступлением на вход блока 2 поступают также на элемент 8 задержки, пройдя через который также одновременно поступают на элемент 6 задержки на m тактов и на один из входов элемента И 9, С выхода элемента 6 задержки сигнал отсчетов исходного изображения, пройдя через элемент И 7, поступает на вход блока 4. С выхода элемента И 9 сигнал отсчетов исходного бинарного изображения поступает на вход блока 5. Коррекция матрицы горизонтали производится на элементах И 7 и 10 при помощи узла , а матрицы вертикали -«. на элементах И 9 и 11 при помощи узла 5-3.

Отсчеты откорректированной матрицы горизонтали с выхода элемента И 10 поступают через вход 16 узла 13 на первые входы дешифратора 21, блока 20 памяти и элемента И 22, На первом выходе дешифратора 21 формируются отсчеты, соответствующие началу горизонтали, а на втором выходе - отсчет:i, соответствующие концу горизонтали которые поступают соответственно через входы блока 20 на первые входы узлов

36и 37 памяти и на второй и третий входы элемента ИЛИ 43, на выходе которого образуется частичньй узел горизонтали.

Отсчеты откорректированной матрицы вертикали с выхода элемента И 11 через элемент 12 задержки поступают через вход узла 13 структурного описания изображения на первый вход дешифратора 28, на первый вход блока 24 и второй вход элемента И 22. На первом выходе дешифратора 28 формируются отсчеты, соответствующие началу вертикали, а на втором выходе - отсчеты, соответствующие концу вертикали, которые через входы блока 24 поступают на первые входы узлов 36 и

37памяти и на второй и третий входы элемента ИЛИ 43, на выходе которого образуется частный узел вертикали направления.

На выходе элемента И 22 формируются фрагменты пересечения горизонта

51

ли и вертикали и с задержкой с выход

элемента 23 задержки поступают через входы блоков 20 и 24 на четвертый вход элемента ИЛИ 43 каждого из блоков. Элемент 23 задержки уравнивает задержку формирования отсчетов фрагментов начал и концов горизонтали и вертикали. Отсчеты с узла горизонтали и вертикали с выхода элемента ИЛИ 43 через вход блоков 20 и 24 поступают на входы элемента ИЛИ 30, на выходе которого формируются отсчеты обобщенного узла и поступают на вход блока 32.

В каждом из блоков 20 и 24 запись кодов номеров линий в ОЗУ 38 и 34 и соответствующих фрагментов псевдоузлов, начал и концов линий происходит аналогично. Поэтому достаточно рассмотреть работу блока на примере горзонтали.

Отсчеты, соответствующие фрагмента псевдоузла горизонтали, начала тори

зонтали или конца горизонтали, посту- 25 случае, если на выходе блока 32 марпают соответственно через первый вход узлов 35-37 памяти, через элемент 39 задержки на вход записи ОЗУ и через элемент ИЛИ 45 на его информационный

вход. Одновременно отсчеты фрагментов 0 на вход записи ОЗУ 50. Признак Конец узла горизонтального направления с вы- описания появляется на выходе де- хода элемента ИЛИ 43 через элемент 42шифратора 49 после считывания всего

задержки и элемент ИЛИ 45 поступают на входы записи ОЗУ 34 и 38, на информационные входы которых подаются коды номеров горизонтальных линий соответственно с выходов узлов 41 маркировки.

При этом код адреса ОЗУ 34 и 38, а также ОЗУ узлов 35-37 памяти определяется кодом номера узла, который снимается с второго выхода блока 32 маркировки и через девятый вход блоков 20 и 24 поступает на адресный вход указанных ОЗУ. .

В режиме считывания изобр блок 33 управления не функци

В процессе считывания информационные признаки начал, концов, пересечений, Псевдоузлов линий как горизонтального, так и вертикального направлений

появляются не одновременно. Поэто.му 50 также уровень в ОЗУ 34 и 38 происходит постепенноеуправляются только по входу,

накопление информации об узлах изображения, кодовое описание которого в форме таблицы формируется только после считывания всего изображения. При этом с выходов блоков 20 и 24 может быть получена информация о фрагментах описания узлов и кодов номеров горизонтальных и вертикальных линий.

и на его втором выходе уровен на остальных выходах уровень При этом на входах блоков ма О и блок 32

Отсчеты изображения с пер да блока с задержкой на элем задержки поступают на второй , элемента И 94, второй вход д ра 96 и четвертый управляемы коммутатора 90.

Код текущего номера изобр хранится в маркировочном сче

0

Информация о координатах узла и признак Конец описания снимаются с выходов ОЗУ 50 и 51 соответственно и через выходы блока 31 поступают совместно с информацией о фрагментах описания узлов и кодов номеров горизонтальных и вертикальных линий с первых выходов блоков 20 и 24 через выход блока 13 на входы блока 14.

Код адреса ОЗУ 50 и 51 блока 31 также определяется кодом номера узла, который с второго выхода блока 32 маркировки через пятый вход блока 31 поступает на адресные входы ОЗУ 50 и 51. Код на информативном входе ОЗУ 50 определяется кодом адресного счетчика 48. Код последнего в свою очередь определяет номер элемента изображения,

0 который пропорционален числу тактовых импульсов на входе счетчика, начиная с момента считывания изображения, и отражает координату узла. Координаты узла записаны в ОЗУ 50 только в том

кировки появляется импульс, соответствующий начальному элементу связных элементов узла, который через входы блока 31 и элемента ИЛИ 52 поступает

кадра изображения и через элемент ИЛИ 53 записывает 1 в ОЗУ 51.

При наличии сложного узла на выходе блока 32 появляется импульс, который через элемент ИЛИ 25 поступает на вход записи ОЗУ 26 и так как на информативном входе ОЗУ 26 1 и адресный вход ОЗУ через коммутатор 29 соединен с первым выходом блока 32 маркировки, то в ОЗУ записывается 1 по адресу, определяемому кодом узла с выхода блока 32 маркировки.

В режиме считывания изображения блок 33 управления не функционирует

также уровень управляются только по входу,

и на его втором выходе уровень 1, а на остальных выходах уровень О. При этом на входах блоков маркировки О и блок 32 и узел 41

также уровень управляются только по входу,

Отсчеты изображения с первого входа блока с задержкой на элементе 97 задержки поступают на второй вход элемента И 94, второй вход дешифратора 96 и четвертый управляемый вход коммутатора 90.

Код текущего номера изображения хранится в маркировочном счетчрке 95,

двоичный код с выхода которого поступает на второй информационный вход коммутатора 90.

Код элементов изображения с присвоенным номером с выхода коммутатора 90 поступает на вход элемента 91 задержки, в котором задерживается на один такт.

С выхода элемента 91 задержки сни- 1 мается код номера изображения объекта предшествующего элемента строки и поступает на первый дешифратора 93, четвертьй информационный вход коммутатора 90, вход информационного j коммутатора 07 и на первый вход блока 98 сравнения, а также на вход элемента 92 задержек.

С выхода элемента 92 задержек сни1

мается код номера изображения объекта „ поступает на вход записи информации

соответствующий соседнему элементу предшествующей строки, и поступает на второй вход дешифратора 93, третий информационный вход коммутатора 90 и на второй вход блока 98 сравнения. 25

Еспи коды номеров элементов изображения объектов на выходах элементов 91 и 92 задержек нулевые, то на выхо- где дешифратора 93 устанавливается уровень 1, который разрешает через о элемент И 94 занесение очередного импульса в маркировочный счетчик 95 текущего номера изображения через элементы И 99 и ИЛИ 100.

Одновременно на выходе коммутатора 90 маркировки появляется ход номера изображения объекта в соответствии с кодом маркировочного счетчика, так как при наличия 1 на втором управляющем входе коммутатора 90 обеспечивается подключение второго информационного входа к выходу. Длительность импульса занесения на выходе элемента И 94 равна одному такту, так

35

40

в регистр 85, ив регистр 85 при эт заносится код адресного счетчика 95 Этот же импульс с выхода дешифратор 104 задерживается на элементе 105 з держки и поступает на второй вход эл мента И 108, на вход занесения дешиф ратора 96 и первый управляющий вход коммутатора 90, а также на второй вх элемента ИЛИ 107 и через однотактны элемент 106 задержки на первый вход элемента ИЛИ 107 и второй вход элеме та ИЛИ ПО, с выходов которых посту пает на второй вход адресного комму татора 88 и вход Запись ОЗУ 89 со ответственно. При наличии этого сигн ла в первый такт в регистр 86 переп сывается код адресного счетчика 84, происходит коммутация выхода регистр 86 с адресным входом ОЗУ 89 и перепись кода номера изображения объекта из ОЗУ в элементе 91 задержек.

Во второй такт по тому же адресу ОЗУ 89 обнуляется за счет подачи импульса записи с выхода элемента ИЛИ

как с задержкой на один такт на выхо- 110 на вход записи ОЗУ 89. Коммутаде элемента 91 появляется код, отличный от нуля, и на выходе дешифратора 93 присутствует потенциал, который запрещает прохождение отсчетов изображения объектов на выход элемента И 94.

Принимая во внимание, что подключение кода номера изображений объектов с выхода элемента 91 задержек к выходу коммутатора 90 осуществляется при наличии 1 на четвертом управляющем входе коммутатора 90, то связанным элементам строки присваивается

50

55

ция информации из ОЗУ 89 происходит на такт раньше, чем поступает первый отсчет связанных элементов в стр ке, так как элемент 97 задержки задерживает отсчеты изображения. При записи кода номера изображения в ОЗУ 89 на выходе элемента И 108 формируе ся импульс длительностью в один такт и с задержкой на два такта на элемен те 109 задержки поступает на управля ющий вход коммутатора 87, первый управляющий вход адресного коммутатора 88 и через элемент ИЛИ 110 на вход записи ОЗУ 89.

один и тот же код номера изображения объекта.

Управление первым коммутирующим входом коммутатора 90 и режимом работы ОЗУ 89 осуществляется блоком 83 управления, с входа которого поступают отсчеты изображения на перйЫй вход дешифратора 104 и через элемент 103 задержки с задержкой на один такт на второй вход дешифратора 104 и на первый вход элемента И 108. На выходе дешифратора формируется импульс длительностью в один такт, когда на первбм входе дешифратора 104 1, а на втором входе О. Момент появления этого импульса соответствует первому элементу из связных элементов в строке. Импульс с выхода дешифратора 104

о

5

0

в регистр 85, ив регистр 85 при этом заносится код адресного счетчика 95. Этот же импульс с выхода дешифратора 104 задерживается на элементе 105 задержки и поступает на второй вход элемента И 108, на вход занесения дешифратора 96 и первый управляющий вход коммутатора 90, а также на второй вход элемента ИЛИ 107 и через однотактный элемент 106 задержки на первый вход элемента ИЛИ 107 и второй вход элемента ИЛИ ПО, с выходов которых поступает на второй вход адресного коммутатора 88 и вход Запись ОЗУ 89 соответственно. При наличии этого сигнала в первый такт в регистр 86 переписывается код адресного счетчика 84, происходит коммутация выхода регистра 86 с адресным входом ОЗУ 89 и перепись кода номера изображения объекта из ОЗУ в элементе 91 задержек.

Во второй такт по тому же адресу ОЗУ 89 обнуляется за счет подачи импульса записи с выхода элемента ИЛИ

110 на вход записи ОЗУ 89. Коммута

ция информации из ОЗУ 89 происходит на такт раньше, чем поступает первый отсчет связанных элементов в строке, так как элемент 97 задержки задерживает отсчеты изображения. При записи кода номера изображения в ОЗУ 89 на выходе элемента И 108 формируется импульс длительностью в один такт и с задержкой на два такта на элементе 109 задержки поступает на управляющий вход коммутатора 87, первый управляющий вход адресного коммутатора 88 и через элемент ИЛИ 110 на вход записи ОЗУ 89.

При этом адрес ОЗУ 89 определяется кодом на выходе регистра 85. Информация о номере изображения объекта с выхода блока 91 задержек через коммутатор 87 записывается в ОЗУ 89 по адресу, определяемому кодом регистра 85, который соответствует адресу начала отсчетов областей следующей строки связанного изображения.

Код номера изображения объекта с выхода ОЗУ 89 формируется в этом случае только для элементов изображения последующей строки в момент коммутации информации из ОЗУ 89 по первому управляющему входу коммутатора 90.

Если код из ОЗУ 89 выдается нулевым, то в этом случае смежные связанные элементы на соседних строках получают код номеров элементов предыдущей строки за счет того, что с выхода элемента 92 задержек коды,- поступая на третий информационный вход коммутатора 90, появляются на его выходе при наличии разрешения на третьем коммутирующем входе коммутатора 90. Разрешающий сигнал на третьем коммутирующем входе коммутатора 90 снимается с выхода дешифратора 96 в том случае, если на его первом входе О, а на втором - единичные отсчеты бинарного изображения. Такое условие соответствует отсутствию пересечений между областями одного и того же изображения объекта на смежных кодах.

При наличии области пересечений элементов изображения на выходе блока 98

о

сравнения формируется импульс, соответствующий области пересечений, который поступает на. первый вход дешифратора 96, на выходе которого формируется запрещающий О, и код на входе элемента 91 задержек в этом случае определяется только кодом предыдущих элементов строки, снимаемым с выхода элемента 91 задержек. Элемент 101 задержки и дешифратор 102 служат для выделения начального элемента области пересечений.

После считывания кадра изображения на выходе дешифратора 49 блока 31 вырабатывается импульс длительностью в один такт и через второй выход блока 31 поступает на вход блока 33 управления, который с задержкой в один такт на элементе 81 задержки устанав- ливает первый триггер 79 в состояние выдачи и через элемент ИЛИ 80 поступает на выход блока, а также через

0

5

0

5

0

5

0

5

0

элемент ИЛИ 72 с задержкой в один такт на элементе 71 задержки на выход блока 33. При этом на выходе блока 33 управления устанавливается уровень 1, который поступает через восьмые входы блоков 20 и 24, устанавливая счетчики 84 и 95 узла 41 маркировки в исходное состояние и обеспечивая разрешение коррекции по первому входу элемента И 44, на второй вход которого через элемент ИЛИ 46 и элемент 47 задержки1-с задержке в один такт через седьмые входы блоков 20 и 24 поступают корректирующие импульсы соответственно с выходов блока 24. Одновременно счетчик 48 блока 31 также устанавливается в исходное состояние. С выхода блока 33 на четвертый вход блока 41 поступает также разрешающий уровень 1, по которому через элемент ИЛИ 100 по второму управляющему входу коммутаторы подключают выходы счетчика 95 к выходу коммутатора, код на выходе которого через второй выход блока задает адрес ОЗУ 34 и 38 блоков 20 и 24 и ОЗУ 50 и 51 блока 31.

С выхода блока 33 импульсы длительностью в один такт поступают через пятый вход блока 32, устанавливая счетчики 84 и 95 в исходное состояние. Импульс с первого выхода блока 33 через шестые входы блоков 20 и 24 и через четвертьй вход блока 31 поступает на входы записи ОЗУ 34, 38, 50 и 51, зануляя записанную в них информацию по адресу, задаваемому кодом счетчика 95 блока 32.

Импульс с выхода элемента 78 задержки блока 33 поступает на вход дешифратора (ДШ) 75 и второй вход элемента И 77. Так как на вторых входах ДШ 75 и элемента И 77 действует импульс, снимаемый с выхода ОЗУ 51 блока 31 с задержкой в один такт, то к моменту появления импульса на выходе элемента 7I задержки на вторых входах ДШ 75 и элемента И 77 будет О. Поэтому на выходе элемента И 77 О, а импульс появляется на выходе ДШ 75 с задержкой в один такт на элементе 74 задержки поступает на вход элемента 73 задержки и через третий выход блока 33 через третий вход блока 32, элемент ИЛИ 99 на счетный вход счетчика 95, увеличивая код счетчика на единицу. При этом на входах блока 25 уста- вливается код, который определяется информацией о структуре узла, кото10

15

20

25

111548800

рая записана в ОЗУ 34, 38 и блоков 35-37 памяти, установленных в блоках

20 и 24. В соответствии с таблицей состояний на выходах блока 25 появлятся соответствующие уровни сигнала. сли 1 на первом выходе, то с заержкой на один такт на элементе 47 задержки блока 20 зануляется информация в ОЗУ 34 и 38 и блоков памяти. сли 1 на третьем выходе, то зануляется информация в одноименных ОЗУ блока 24.

Далее импульс с выхода элемента 73

задержки поступает на второй вход элемента ИЛИ 72 и второй вход дешиф ратора 82, на первый вход которого поступает сигнал с второго выхода бло ка 25. Если на выходе блока 25 О, то на выходе дешифратора 82 формируется импульс, который через шестой выход блока 33, через выход синхронизации узла 13 поступает на синхронизирующий вход блока 14 вывода и при наличии синхроимпульса информация с выхода блока воспринимается в блоке 14 вывода.

В этом случае, если на выходе блока 25 анализа 1, импульс синхронизации не вырабатывается и информация, записанная в ОЗУ по данному адресу узла, исключается из описания. Затем импульс с выхода элемента ИЛИ 72 с задержкой в один такт на элементе 71 задержки поступает на первый выход блока 33, зануляя информацию в ОЗУ. Процесс модификации кода адреса узлов, анализа информации в ОЗУ и зану- ления информации в ОЗУ блоков 20 и 24 накопления признаков и блока 31 продолжается до тех пор, пока на выходе ОЗУ 51 блока 31 не появится 1 (сигнал Конец считывания), запрещающая циркуляции импульса с выхода элемента 71 задержки на выход дешифратора 75, на разрешающая передачу импульса с входа блока 33 на выход элемента И 77, который с задержкой в один такт на элементе 76 задержки переводит триггер 79 в состояние Считывание и через элемент ИЛИ 80 устанавливает счетчики 48 и 95 блока 32 в исходное состояние. Затем цикл считывания информации повторяется.

30

35

40

45

жа ни бл че об ру бл за не по за вх то вх из ко с по ме ко эл со бр вт ма пр щи бл хО г д щ ж в с п кл д в

50

р т о

Формула изобретения Устройство для считывания и кодирования изображений объектов, содер0

5

0

5

8800

30

35

40

12

жащее блок ввода изображений, синхронизирующий вход которого соединен с блоком синхронизации, а выход подключен к информационному входу блока преобразования изображений, синхронизирующие входы которого подключены к блоку синхронизации, первый элемент задержки, один вход которого соединен с блоком синхронизации, другой подключен к выходу второго элемента задержки, а выход соединен с одним входом первого элемента И, выход которого подключен к информационному входу первого селектора признаков изображения, синхронизирующие входы которого соединены с выходом блока синхронизации, а управляющий выход подключен к другому входу первого элемента И9 второй элемент И, один вход которого соединен с выходом второго элемента задержки, входы которого соединены с выходами блоков ввода изображений и синхронизации, а выход второго элемента И подключен к информационному входу второгр селектора признаков изображений, синхронизирующие входы которого соединены с выходом блока синхронизации, управляющий вы- хОд подключен к другому входу второго элемента И, третий элемент И, входы которого подключены к соответствующим выходам первого селектора изображений объектов, четвертый элемент И, входы которого соединены с соответствующими выходами второго селектора признаков изображений, а выход подключен к входу третьего элемента задержки, при этом информационный вход второго селектора признаков изображений соединен с выходом блока преобразования изображений, и ин

формационный вход первого селектора признаков изображений подключен к- соответствующему выходу второго селектора признаков изображений, отличающееся тем, что, с целью расширения функциональных возможностей путем введения кодового описания и коррекции структуры изображений, оно содержит первый и второй блоки памяти, синхронизирующие входы которых соединены с выходом блока синхронизации, первый информационный вход первого блока памяти подключен к выходу третьего элемента И, а первый информационный вход второго блока памяти соединен с выходом третьего

элемента задержки, блок управления, синхронизирующий вход которого подключен к выходу блока синхронизации, пятый элемент И, входы которого сое-. динены с выходами третьего элемента задержки и третьего элемента И, четвертый элемент задержки, входы которого подключены к выходам блока синхронизации и пятого элемента И, а выход соединен с вторым входом синхронизации первого и второго блоков памяти, первый дешифратор, входы которого подключены к выходам блока синхронизации и третьего элемента И, а выходы подключены к адресным входам группы первого блока памяти, второй дешифратор, входы которого соединены с выходами блока синхронизации и тре- етьего элемента задержки, а выходы подключены к адресным входам группы второго блока памяти, третий блок памяти, адресные входы которого соединены с соответствующими выходами первого, и второго блоков памяти, первый выход подключен к второму информационному входу первого блока памяти, второй соединен с информационным входом блока управления, а третий подключен к второму информационному входу второго блока памяти, первый элемент ИЛИ, один вход которого соединен с первым выходом блока управления, подключенным к управляющим входам первого и второго блоков памяти, четвертый блок памяти, управляющие входы которого соединены с выходом первого элемента ИЛИ и вторым выходом блока управления, а выход подключен к управляющему входу третьего блока памя

0

ти, второй элемент ИЛИ, входы которого соединены с соответствующими выходами первого1 и второго блоков памяти, блок маркирования изображений, первый синхронизирующий вход которого соединен с выходом второго элемента ИЛИ, второй синхронизирующий вход подключен к выходу блока синхронизации, управляющие входы соединены с третьим, четвертым и пятым выходами блока управления соответственно, коммутатор, адресные входы которого подключены к первому и второму выходам блока маркирования изображений, управляющие входы соединены с соответствующими выходами блока управления, а выход подключен к адресным входам четвертого блока памяти и пятый блок памяти, управляющие входы которого соединены с соответствующими выходами блока управления, синхронизирующий вход подключен к выходу блока синхронизации, информационные входы соединены с соответствующими выходами блока маркирования изображений, первый выход пятого блока памяти является первым информационным выходом устройства, а второй и третий выходы соединены с управляющими входами блока управления соответственно, при этом дру гой вход первого элемента ИЛИ подключен к третьему выходу блока маркирования изображений, вторые адресные входы первого и второго блоков памяти 35 соединены с четвертым выходом блока управления, а третьи адресные выходы первого и второго блоков памяти подключены к второму выходу блока маркирования изображений.

0

5

40

«4J

I

ar/j

Av/4 «Aw 5

teJ

Ц 63

Ц Д 1 J

1гЖ

57

Ьых.1

8ы.1

Лых.1

Фиг. 5

1 J

1гЖ

57

-f

«у

8ых.1

4

70

вых.2

дым 8ШЗ выхА Вш.5. 8ых.6

Фиг. 7

I

Авторы

Даты

1990-03-07—Публикация

1986-07-28—Подача