Изобретение относится к автоматике, в частности к устройству для считывания и кодирования изображений, и может быть использовано в системах с техническим зрением для выделения дефектов изображений фотошаблонов, печатных плат.

Цель изобретения - повышение точности устройства.

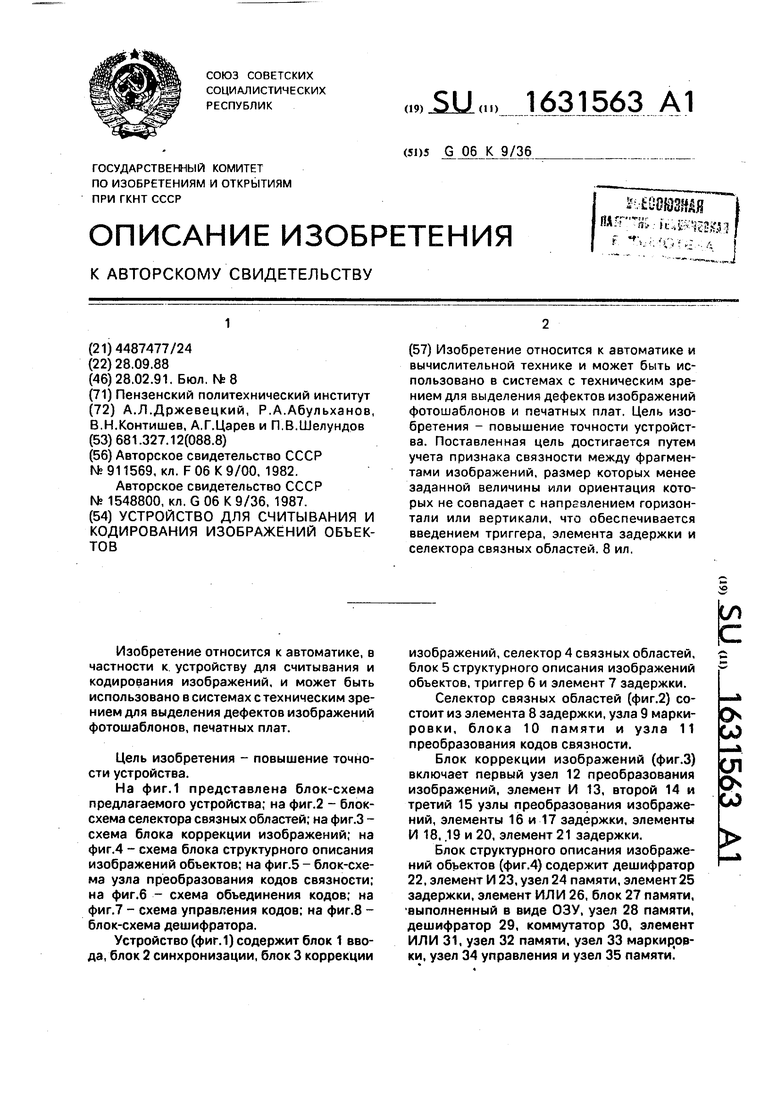

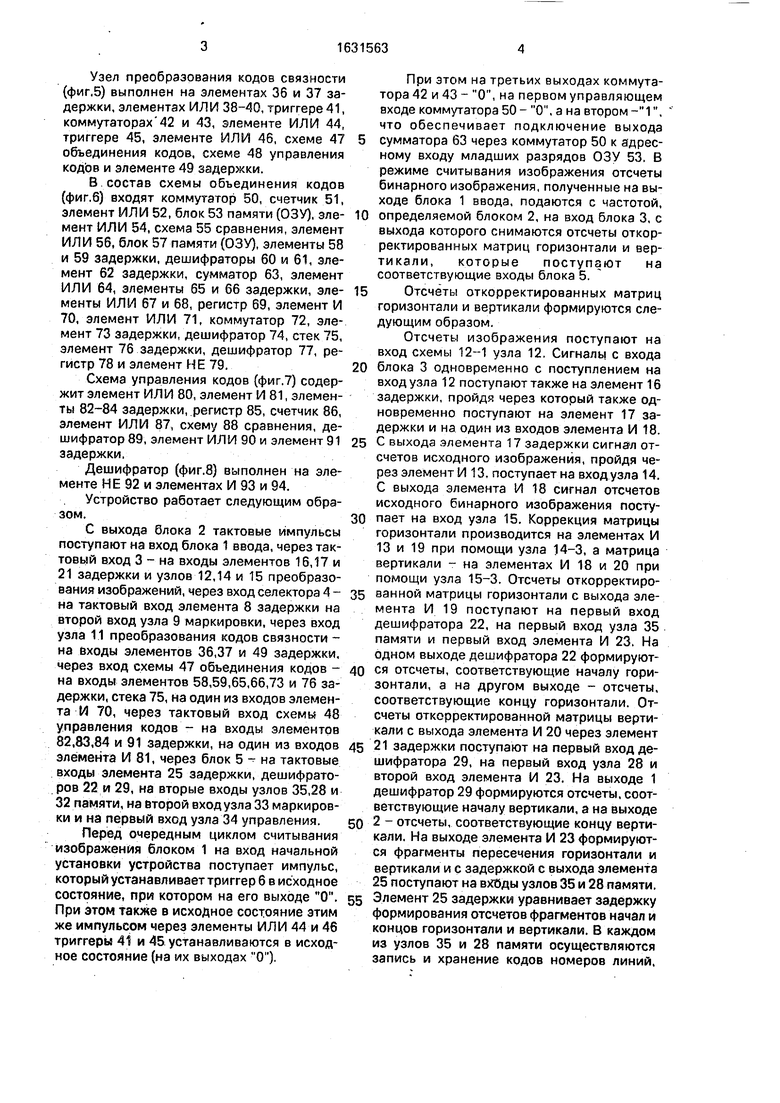

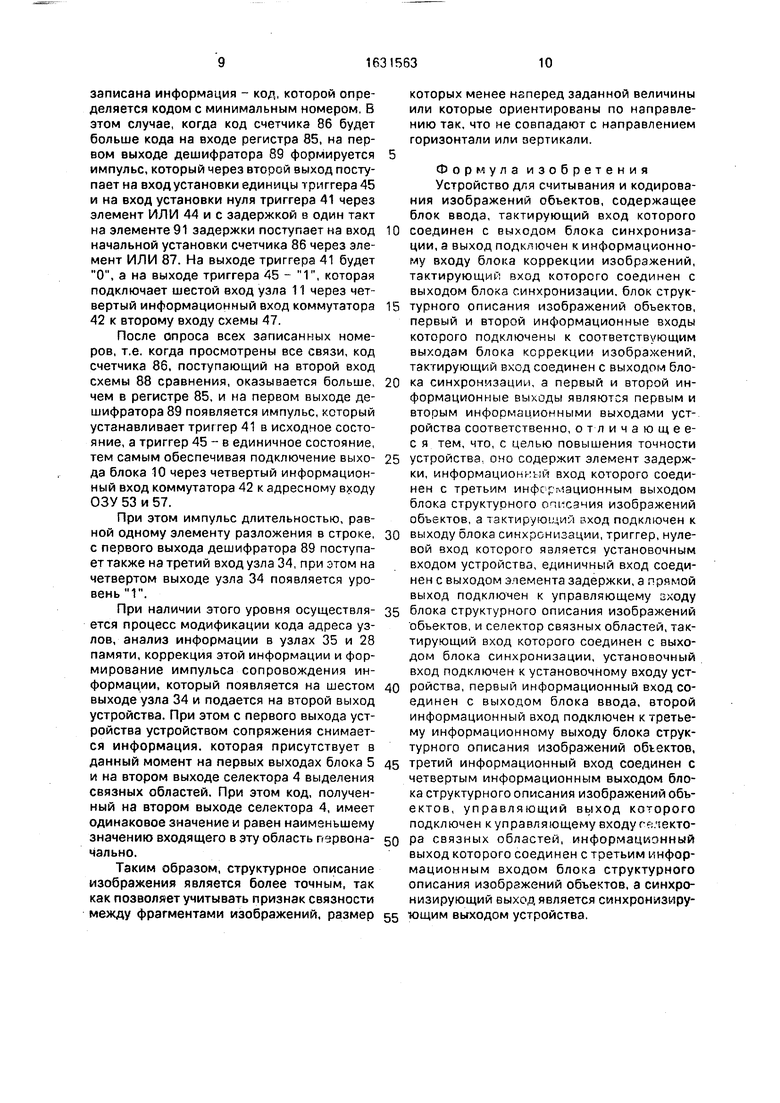

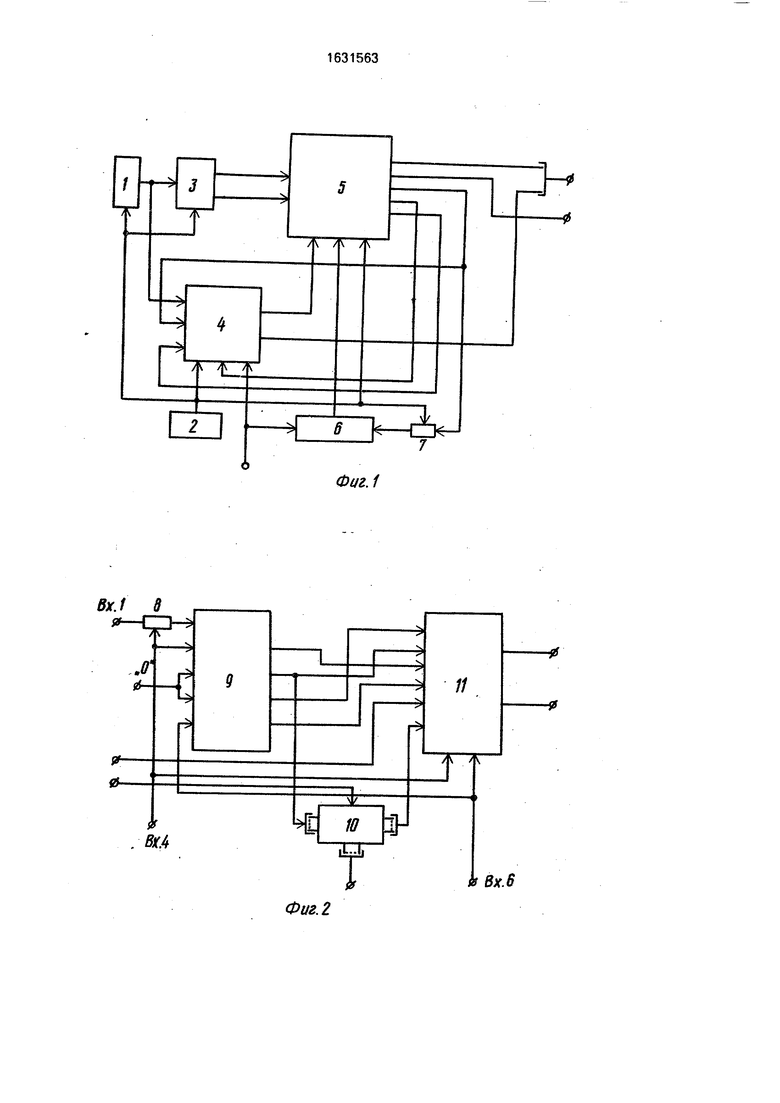

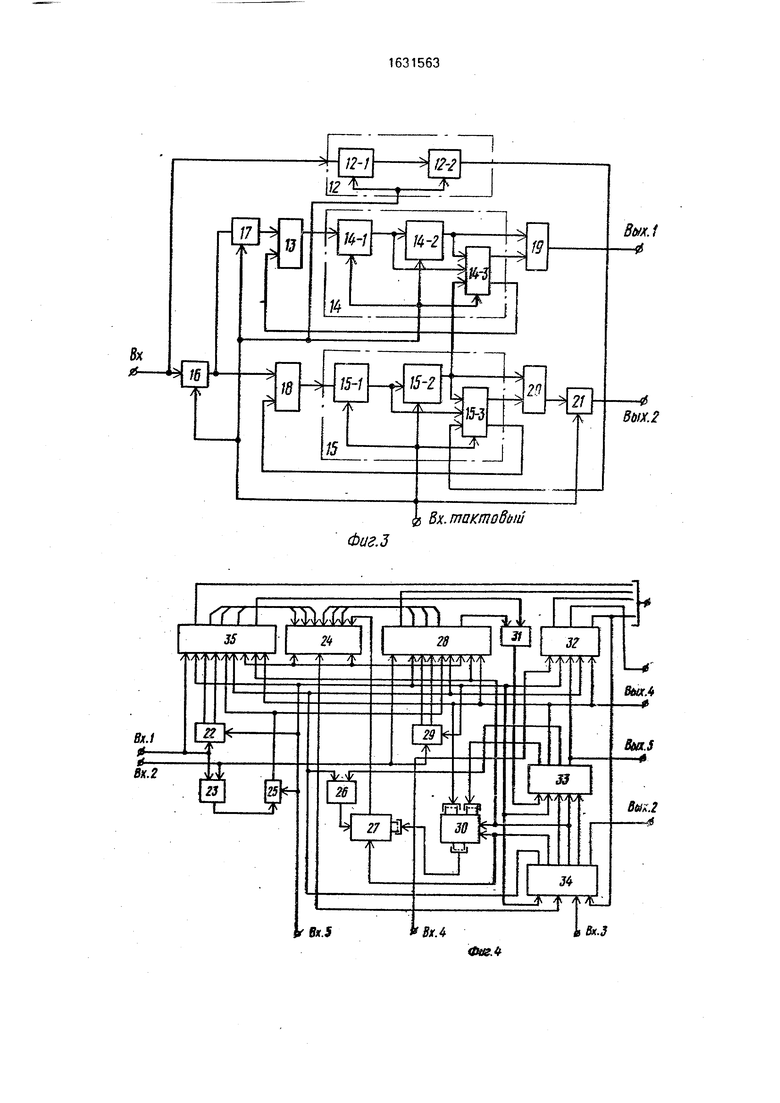

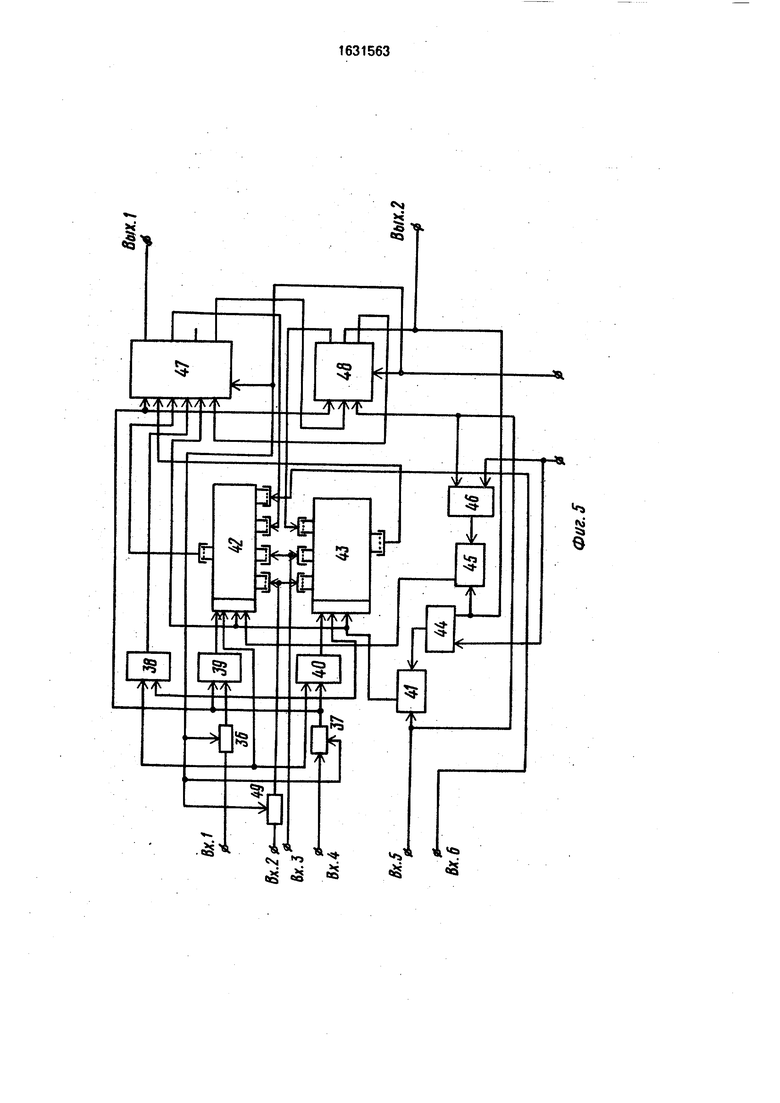

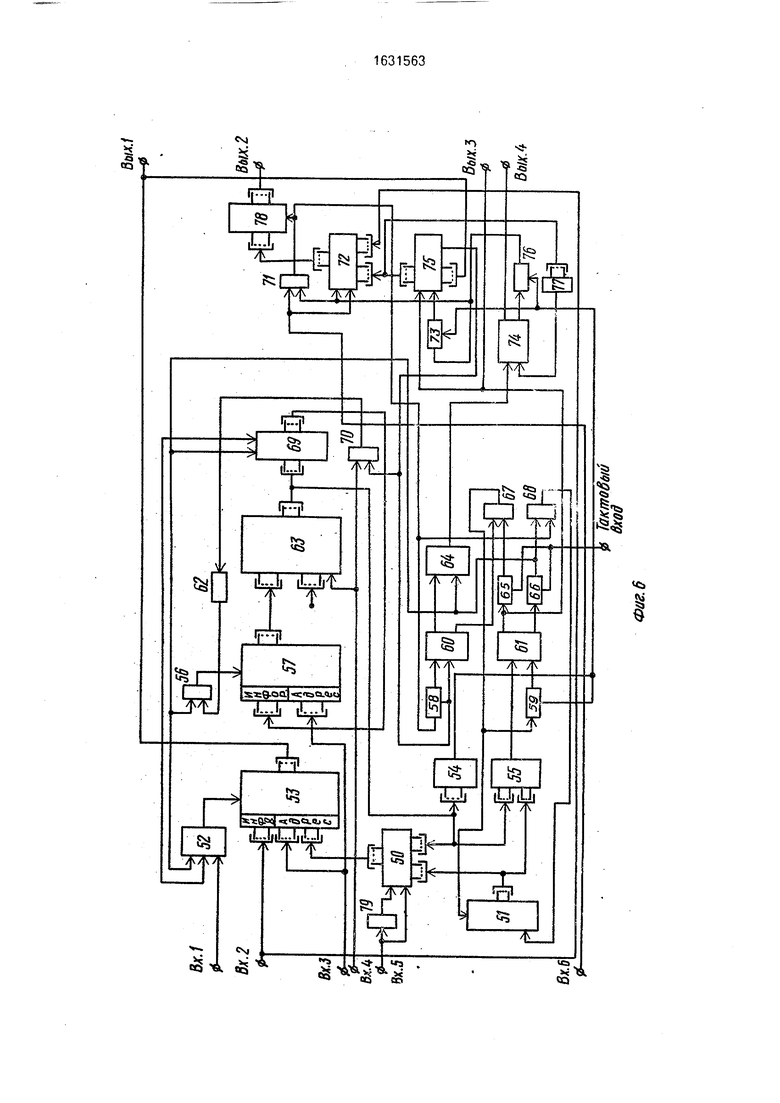

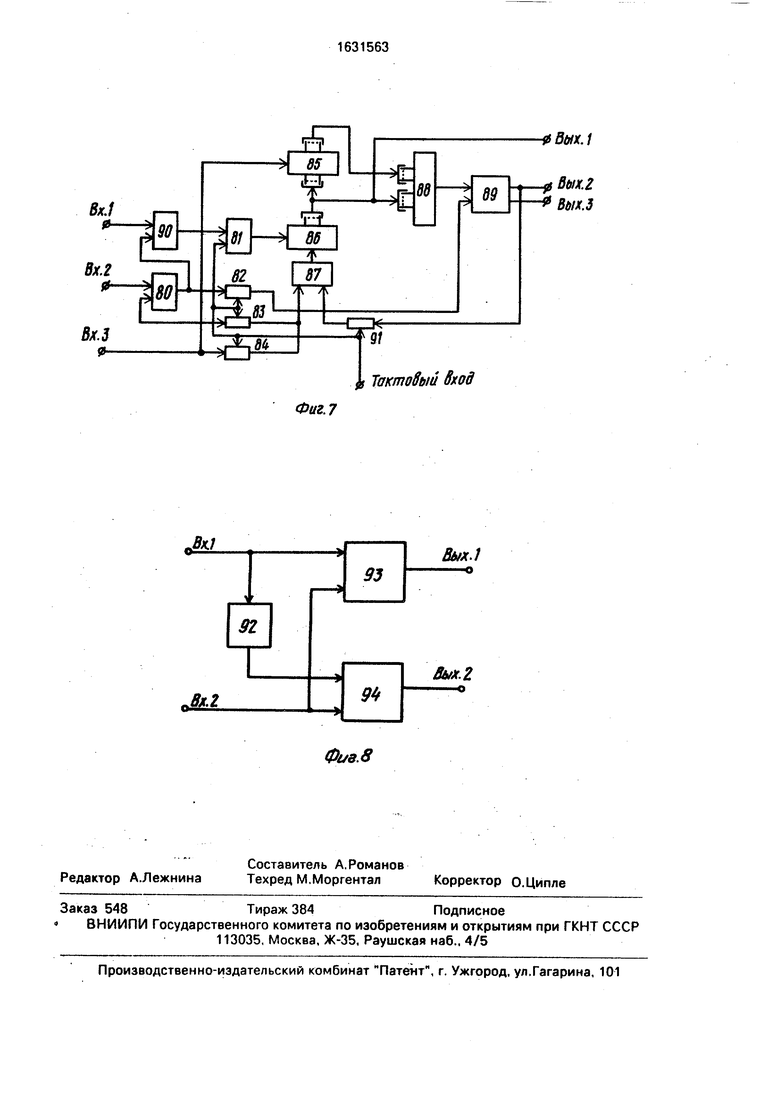

На фиг.1 представлена блок-схема предлагаемого устройства; на фиг.2 - блок- схема селектора связных областей; на фиг.З - схема блока коррекции изображений; на фиг.4 - схема блока структурного описания изображений объектов; на фиг.5 - блок-схема узла преобразования кодов связности; на фиг.6 - схема объединения кодов; на фиг.7 - схема управления кодов; на фиг.8 - блок-схема дешифратора.

Устройство (фиг.1) содержит блок 1 ввода, блок 2 синхронизации, блок 3 коррекции

изображений, селектор 4 связных областей, блок 5 структурного описания изображений объектов, триггер 6 и элемент 7 задержки.

Селектор связных областей (фиг.2) состоит из элемента 8 задержки, узла 9 марки- ровки, блока 10 памяти и узла 11 преобразования кодов связности.

Блок коррекции изображений (фиг.З) включает первый узел 12 преобразования изображений, элемент И 13, второй 14 и третий 15 узлы преобразования изображений, элементы 16 и 17 задержки, элементы И 18. .19 и 20, элемент 21 задержки.

Блок структурного описания изображений объектов (фиг.4) содержит дешифратор 22, элемент И 23, узел 24 памяти, элемент25 задержки, элемент ИЛИ 26, блок 27 памяти, выполненный в виде ОЗУ, узел 28 памяти, дешифратор 29, коммутатор 30, элемент ИЛИ 31, узел 32 памяти, узел 33 маркировки, узел 34 управления и узел 35 памяти.

W

Ё

Узел преобразования кодов связности (фиг.5) выполнен на элементах 36 и 37 задержки, элементах ИЛИ 38-40, триггере 41, коммутаторах 42 и 43, элементе ИЛИ 44, триггере 45, элементе ИЛИ 46, схеме 47 объединения кодов, схеме 48 управления кодов и элементе 49 задержки.

В состав схемы объединения кодов (фиг.б) входят коммутатор 50, счетчик 51, элемент ИЛИ 52, блок 53 памяти (ОЗУ), элемент ИЛИ 54, схема 55 сравнения, элемент ИЛИ 56, блок 57 памяти (ОЗУ), элементы 58 и 59 задержки, дешифраторы 60 и 61, элемент 62 задержки, сумматор 63, элемент ИЛИ 64, элементы 65 и 66 задержки, элементы ИЛИ 67 и 68, регистр 69, элемент И 70, элемент ИЛИ 71, коммутатор 72, элемент 73 задержки, дешифратор 74, стек 75, элемент 76 задержки, дешифратор 77, регистр 78 и элемент НЕ 79.

Схема управления кодов (фиг.7) содержит элемент ИЛИ 80, элемент И 81, элементы 82-84 задержки, регистр 85, счетчик 86, элемент ИЛИ 87, схему 88 сравнения, дешифратор 89, элемент ИЛИ 90 и элемент 91 задержки,

Дешифратор (фиг.8) выполнен на элементе НЕ 92 и элементах И 93 и 94.

Устройство работает следующим образом.

С выхода блока 2 тактовые импульсы поступают на вход блока 1 ввода, через тактовый вход 3 - на входы элементов 16,17 и 21 задержки и узлов 12,14 и 15 преобразования изображений, через вход селектора 4 - на тактовый вход элемента 8 задержки на второй вход узла 9 маркировки, через вход узла 11 преобразования кодов связности - на входы элементов 36,37 и 49 задержки, через вход схемы 47 объединения кодов - на входы элементов 58,59,65,66,73 и 76 задержки, стека 75, на один из входов элемента И 70, через тактовый вход схемы 48 управления кодов - на входы элементов 82,83,84 и 91 задержки, на один из входов элемента И 81, через блок 5 - на тактовые входы элемента 25 задержки, дешифраторов 22 и 29, на вторые входы узлов 35,28 и 32 памяти, на второй вход узла 33 маркировки и на первый вход узла 34 управления.

Перед очередным циклом считывания изображения блоком 1 на вход начальной установки устройства поступает импульс, который устанавливает триггер 6 в исходное состояние, при котором на его выходе О. При этом также в исходное состояние этим же импульсом через элементы ИЛИ 44 и 46 триггеры 41 и 45 устанавливаются в исходное состояние (на их выходах О).

При этом на третьих выходах коммутатора 42 и 43 - О, на первом управляющем входе коммутатора 50 - О, а на втором , что обеспечивает подключение выхода

сумматора 63 через коммутатор 50 к адресному входу младших разрядов ОЗУ 53, В режиме считывания изображения отсчеты бинарного изображения, полученные на выходе блока 1 ввода, подаются с частотой,

определяемой блоком 2, на вход блока 3, с выхода которого снимаются отсчеты откорректированных матриц горизонтали и вертикали, которые поступают на соответствующие входы блока 5.

Отсчеты откорректированных матриц горизонтали и вертикали формируются следующим образом.

Отсчеты изображения поступают на вход схемы 12-1 узла 12. Сигналы с входа

блока 3 одновременно с поступлением на вход узла 12 поступают также на элемент 16 задержки, пройдя через который также одновременно поступают на элемент 17 задержки и на один из входов элемента И 18.

С выхода элемента 17 задержки сигнал отсчетов исходного изображения, пройдя через элемент И 13, поступает на вход узла 14. С выхода элемента И 18 сигнал отсчетов исходного бинарного изображения поступает на вход узла 15. Коррекция матрицы горизонтали производится на элементах И 13 и 19 при помощи узла 14-3, а матрица вертикали - на элементах И 18 и 20 при помощи узла 15-3. Отсчеты откорректированной матрицы горизонтали с выхода элемента И 19 поступают на первый вход дешифратора 22, на первый вход узла 35 памяти и первый вход элемента И 23. На одном выходе дешифратора 22 формируются отсчеты, соответствующие началу горизонтали, а на другом выходе - отсчеты, соответствующие концу горизонтали. Отсчеты откорректированной матрицы вертикали с выхода элемента И 20 через элемент

21 задержки поступают на первый вход дешифратора 29, на первый вход узла 28 и второй вход элемента И 23. На выходе 1 дешифратор 29 формируются отсчеты, соответствующие началу вертикали, а на выходе

2 - отсчеты, соответствующие концу вертикали. На выходе элемента И 23 формируются фрагменты пересечения горизонтали и вертикали и с задержкой с выхода элемента 25 поступают на вхйды узлов 35 и 28 памяти.

Элемент 25 задержки уравнивает задержку формирования отсчетов фрагментов начал и концов горизонтали и вертикали. В каждом из узлов 35 и 28 памяти осуществляются запись и хранение кодов номеров линий,

фрагментов псевдоузлов, начал и концов линий.

Информация о координатах узла и признаков Конец описания снимается с первого и третьего выходов узла 32 памяти и совместно с информацией о фрагментах описания узлов и кодов номеров горизонтальных и вертикальных линий с первых выходов узлов 35 и 28 памяти поступает на первый выход устройства.

Координаты узлов записываются в узел 32 памяти только в том случае, если на четвертом выходе узла 33 появляется импульс, соответствующий начальному элементу связных элементов узла. При наличии сложного узла на третьем выходе узла 33 появляется импульс, который через элемент ИЛИ 26 поступает на вход записи блока 27, и так как на информационном входе блока 27 1 и адресный вход блока 27 через коммутатор 30 соединен с первым выходом узла 33, то в блоке 27 будет записана 1 по адресу, определяемому кодом узла с выхода узла 33.

При считывании изображения узел 34 не функционирует. Одновременно с выхода блока ввода отсчеты бинарного изображения поступают на первый вход селектора 4, где задерживаются на время, равное обработке сигналов в блоке 3 на элементе 8 задержки, и поступают на первый вход узла 9. На первом и втором выходах узла 9 формируются коды номеров связных элементов изображения, на четвертом выходе - импульс, соответствующий начальному элементу связного изображения, а на третьем выходе - импульс, соответствующий первому элементу области пересечений.

Коды с первого выхода узла 9 через третий вход узла 11 поступают на вторые информационные входы коммутаторов 42 и 43. Коды с второго выхода узла 9 поступают на информационный вход блока 10 и через второй вход узла 11 преобразования кодов связности с задержкой в один такт на элементе 49 задержки подаются на первые информационные входы коммутаторов 42 и 43. Адресный вход блока 10 определяется кодом номера узла, который поступает с второго выхода узла 33 блока 5. При этом код номера объекта в блоке 10 записывается в момент выделения начального элемента узла с четвертого выхода узла 33. В момент появления первого элемента, входящего в состав связного изображения, на четвертом выходе узла 9 формируется импульс, равный одному элементу разложения в строке, и поступает через четвертый вход узла 11с задержкой в один такт на элементе 37 задержки на первые входы схемы 47 объединения кодов и схемы 48 управления, а также

через элементы ИЛИ 39 и 40 на первые управляющие входы коммутаторов 42 и 43. При этом первые информационные входы коммутаторов 42 и 43 подключаются соответственно с выходами одноименных коммутаторов, задавая код информации на информационном входе ОЗУ 53, на адресном входе старших разрядов ОЗУ 53 и адресном входе ОЗУ 57. Запись информации

0 в ОЗУ 53 производится по импульсу занесения первого элемента, поступающему с первого входа схемы 47 объединения кодов через элемент ИЛИ 52 на вход записи ОЗУ 53. При этом код адресного входа младших

5 разрядов ОЗУ 53 - нулевой, а коды на информационном и адресном входах старших разрядов имеют одинаковые значения. По этому же импульсу занесения, поступающему через первый вход схемы 48 управления,

0 через элементы ИЛИ 90 и И 81 по тактовому импульсу в счетчик 86 заносится очередной импульс, тем самым увеличивая его код на единицу. В том случае, если существует область пересечений, на третьем выходе узла

5 9 формируется уровень 1, который через первый вход узла 11 поступает на вход элемента 36 задержки, на второй управляющий вход коммутатора 42 и нч первый управляющий вход коммутатора 43 через элемент

0 ИЛИ 40, а также на четвертый вход схемы 47 объединения кодов через элемент ИЛИ 38. С выхода элемента 36 задержки, имеющего задержку в один такт, импульс поступает на второй управляющий вход коммутатора 43 и

5 первый управляющий вход коммутатора 42 через элемент ИЛИ 39, а также на четвертый вход схемы 47 чяерез элемент ИЛИ 38. Код адресного входа младших разрядов ОЗУ 53 на единицу больше, чем код на выходе ОЗУ

0 57, за счет того, что на вход младшего разряда сумматора 63 с четвертого входа схемы 47 подается уровень 1, который поступает также на один из входов элемента И 70. В момент появления тактового импульса на

5 Другом входе формируется сигнал, по которому осуществляется запись кода с выхода сумматора 63 в регистр 69 и запись информации в ОЗУ 53 через элемент ИЛИ 52 с задержкой, несколько большей длительно0 сти тактового импульса. На элементе 62 задержки осуществляется запись кода с выхода регистра 69 информации в ОЗУ 57 по импульсу записи через элемент ИЛИ 56. В результате в первый такт относитель5 «о момента появления импульса, соответствующего области пересечений, в ОЗУ 53 записывается код номера изображения (по адресу, определяемому кодом номера изо- бражения.-с которым происходит пересечение, во второй- такт происходит запись в

ОЗУ 53 по адресу определяемого кодом номера изображения, с которым происходит пересечение, кода номера изображения, т.е. во второй такт адрес и информация вза- имообращаются местами.

В конце считывания кадра изображения в ОЗУ 53 для значений нулевых кодов в младших адресных разрядах записаны коды начальных элементов, для значений с кодами, отличными от нулевых, записываются коды связей и их последовательная запись определяет локальный список связных областей. После считывания кадра на втором выходе узла 32 формируется импульс, который через третий выход блока 5 поступает на вход элемента 7 задержки, устанавливает триггер 6 в единичное состояние с задержкой в один такт, а также подается на второй вход селектора 4. При этом триггер 41 устанавливается в единичное состояние, обеспечивая подключения кода с выхода регистра 78 через коммутатор 42 к адресным входам ОЗУ 53 и 57, а также выход счетчика 86 через коммутатор 43 к информационному входу ОЗУ 53 и второму информационному входу коммутатора 72. С поступлением этого же импульса код счетчика 86 переписывается в регистр 85, затем с задержкой в один такт (на элементе 84 задержки) устанавливает счетчик 86 через элемент ИЛИ 87 в исходное состояние и с задержкой на элементе 83 задержки в один такт через элементы ИЛИ 90 и 80 и элемент И 81 поступает на счетный вход счетчики 86. Тот же импульс с выхода элемента ИЛИ 80 задерживается на один такт на элементе 82 задержки и поступает на второй вход дешифратора 89, на первом выходе которого появляется импульс только в том случае, если код на первом входе схемы 88 сравнения меньше, чем на втором, а на втором выходе - в том случае, если это условие не выполняется.

В момент появления импульса на втором выходе дешифратора 89, который через третий выход узла 48 поступает на второй вход коммутатора 72, обеспечивается подключение информационного входа ОЗУ 53 к входу регистра 78 и запись этого кода через элемент ИЛИ 71 в регистр 78. С выхода элемента ИЛИ 71 данный импульс устанавливает счетчик 51 через элемент ИЛИ 68 в исходное состояние и с задержкой в один такт на элементе 58 задержки поступает на второй вход дешифратора 60. Если код на выходе ОЗУ 57 нулевой, то на выходе элемента ИЛИ 54- нуль и при том на втором выходе дешифратора 60 появляется импульс, который через элемент ИЛИ 64 поступает на второй вход дешифратора 74. Если код на выходе стека 75 при этом нулевой, то

на выходе дешифратора 77 - единица и при этом на первом входе дешифратора 74 так

же единица.

Следовательно, если при поступлении

5 на шестой вход схемы 47 код на выходе ОЗУ 57 и код на выходе стекла 75 также нулевые, то на четвертом выходе схемы 47 появляется импульс с задержкой в один такт и поступает на второй вход схемы 48, устанавливая

10 счетчик 86 в очередное состояние. Если код ОЗУ 57 отличается от нуля, то импульс появляется на первом выходе дешифратора 60 и поступает на вход элемента 59 задержки, где задерживается на один такт, и на счет15 ный вход счетчика 51, выход которого в этом режиме через коммутатор 50 подключен к адресному входу младших разрядов ОЗУ 53. Если код счетчика 51 меньше или раве« коду ОЗУ 57, то в момент появления импуль20 са на втором входе дешифратора 61 на втором выходе появляется импульс, который поступает на вход записи информации стека 75 и при этом с вьгхода ОЗУ 53 код переписывается в стек 75. Тот же импульс задержи25 вается на один такт нз элементе 65 задержки и через с-лемент ИЛИ 67 поступает снова на счетный вход счетчика 51, увеличивая его состояние на единицу. Данный цикл повторяется до тех пор, пока код на

30 выходе счетчика не станет меньше или равным коду на выходе ОЗУ 57. В этом случае, если это условие не выполняется, появляется импульс на первом выходе дешифратора 61, который с задержкой в один такт на

35 элементе 66 задержки поступает через элемент ИЛИ 68 на вход начальной установки счетчика 51, на вход начальной установки регистра 69 и на входы записи ОЗУ 53 и 57. При этом в ОЗУ 57 записывается нулевой

40 ОД с выхода регистра 69, а в ОЗУ 53 - код, определяемый кодом на выходе регистра 78. Импульс с выхода элемента 66 задержки также поступает через элемент ИЛИ 64 на второй вход дешифратора 74. В том случае,

45 если код на выходе стека ненулевой, то в момент появления импульса на втором входе дешифратора 74 на его втором выходе появляется импульс, который с задержкой в один такт на элементе 76 задержки поступа50 ет на первый управляющий вход коммутатора 72 и на второй вход элемента ИЛИ 71. переписывая код с выхода стека 75 в регистр 78, и с задержкой в один такт на элементе 73 задержки подается на вход сдвига

55 информации, сдвигая очередно на выход. Цикл записи информации в стек 75 и его выдача происходит до тех пор, пока код на выходе стека не будет нелевым. В результате данного цикла в ОЗУ 53 по всем адресам, которые входят в сводные области, будет

записана информация - код, которой определяется кодом с минимальным номером, В этом случае, когда код счетчика 86 будет больше кода на входе регистра 85, на первом выходе дешифратора 89 формируется импульс, который через второй выход поступает на вход установки единицы триггера 45 и на вход установки нуля триггера 41 через элемент ИЛИ 44 и с задержкой в один такт на элементе 91 задержки поступает на вход начальной установки счетчика 86 через элемент ИЛИ 87. На выходе триггера 41 будет О, а на выходе триггера 45 - 1, которая подключает шестой вход узла 11 через четвертый информационный вход коммутатора 42 к второму входу схемы 47.

После опроса всех записанных номеров, т.е. когда просмотрены все связи, код счетчика 86, поступающий на второй вход схемы 88 сравнения, оказывается больше, чем в регистре 85, и на первом выходе дешифратора 89 появляется импульс, который устанавливает триггер 41 в исходное состояние, а триггер 45 - в единичное состояние, тем самым обеспечивая подключение выхода блока 10 через четвертый информационный вход коммутатора 42 к адресному входу ОЗУ 53 и 57.

При этом импульс длительностью, равной одному элементу разложения в строке, с первого выхода дешифратора 89 поступает также на третий вход узла 34, при этом на четвертом выходе узла 34 появляется уровень 1.

При наличии этого уровня осуществляется процесс модификации кода адреса узлов, анализ информации в узлах 35 и 28 памяти, коррекция этой информации и формирование импульса сопровождения информации, который появляется на шестом выходе узла 34 и подается на второй выход устройства. При этом с первого выхода устройства устройством сопряжения снимается информация, которая присутствует в данный момент на первых выходах блока 5 и на втором выходе селектора 4 выделения связных областей. При этом код, полученный на втором выходе селектора 4, имеет одинаковое значение и равен наименьшему значению входящего в эту область первоначально.

Таким образом, структурное описание изображения является более точным, так как позволяет учитывать признак связности между фрагментами изображений, размер

которых менее наперед заданной величины или которые ориентированы по направлению так, что не совпадают с направлением горизонтали или вертикали.

Формула изобретения Устройство для считывания и кодирования изображений объектов, содержащее блок ввода, тактирующий вход которого

соединен с выходом блока синхронизации, а выход подключен к информационному входу блока коррекции изображений, тактирующий вход которого соединен с выходом блока синхронизации, блок структурного описания изображений объектов, первый и второй информационные входы которого подключены к соответствующим выходам блока коррекции изображений, тактирующий вход соединен с выходом бло«а синхронизации, а первый и второй информационные выходы являются первым и вторым информационными выходами устройства соответственно, отличающее- с я тем, что, с целью повышения точности

устройства, оно содержит элемент задержки, информационном вход которого соединен с третьим инфс рмационным выходом блока структурного списания изображений объектов, а тактирующий вход подключен к

выходу блока синхронизации, триггер, нулевой вход которого является установочным входом устройства, единичный вход соединен с выходом элемента задержки, а примой выход подключен к управляющему зходу

блока структурного описания изображений объектов, и селектор связных областей, тактирующий вход которого соединен с выходом блока синхронизации, установочный вход подключен к установочному входу устройства, первый информационный вход соединен с выходом блока ввода, второй информационный вход подключен к третьему информационному выходу блока структурного описания изображений объектов,

третий информационный вход соединен с четвертым информационным выходом блока структурного описания изображений обь- ектов, управляющий выход которого подключен к управляющему входу гедектора связных областей, информационный выход которого соединен с третьим информационным входом блока структурного описания изображений объектов, а синхронизирующий выход является синхронизиручощим выходом устройства.

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для селекции изображений | 1988 |

|

SU1638718A1 |

| Устройство для считывания и кодирования изображений объектов | 1986 |

|

SU1548800A1 |

| Устройство для селекции дефектов изображений объектов | 1988 |

|

SU1631562A1 |

| Устройство для селекции изображений | 1991 |

|

SU1837335A1 |

| Устройство для определения углового положения указателя стрелочных приборов | 1987 |

|

SU1532812A1 |

| УСТРОЙСТВО ДЛЯ СЕЛЕКЦИИ ИЗОБРАЖЕНИЙ ОБЪЕКТОВ | 1990 |

|

RU2032218C1 |

| Устройство для селекции изображений объектов | 1987 |

|

SU1525718A1 |

| Устройство для подсчета количества изображений объектов | 1986 |

|

SU1383413A1 |

| Устройство для селекции изображений объектов | 1987 |

|

SU1608710A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах с техническим зрением для выделения дефектов изображений фотошаблонов и печатных плат. Цель изобретения - повышение точности устройства. Поставленная цель достигается путем учета признака связности между фрагментами изображений, размер которых менее заданной величины или ориентация которых не совпадает с напргалением горизонтали или вертикали, что обеспечивается введением триггера, элемента задержки и селектора связных областей. 8 ил.

Фиг. 2

.Ј

eg

«з a. 5

S

«с.

I

OQ Ј

Фиг. 7

Фиа.8

it

Тактовый Вход

| Устройство для селекции изображений объектов | 1980 |

|

SU911569A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

| Устройство для считывания и кодирования изображений объектов | 1986 |

|

SU1548800A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-02-28—Публикация

1988-09-28—Подача