Изобретение относится к автоматике и вычислительной технике и может быть ис- полыювано для определения параметров изоб|)ажений в системах с техническим зрением и в устройствах для распознавания обра: ов.

и ель изобретения - расширение области п зименения за счет обеспечения опре- дeлe ия связности объекта.

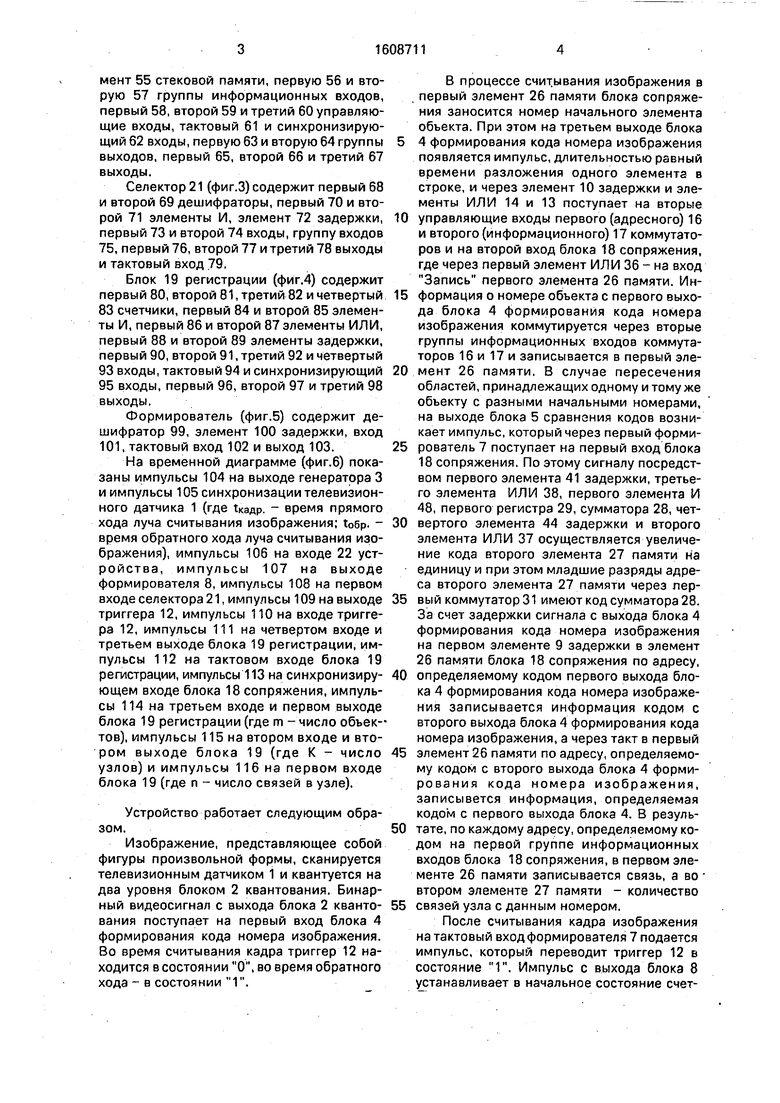

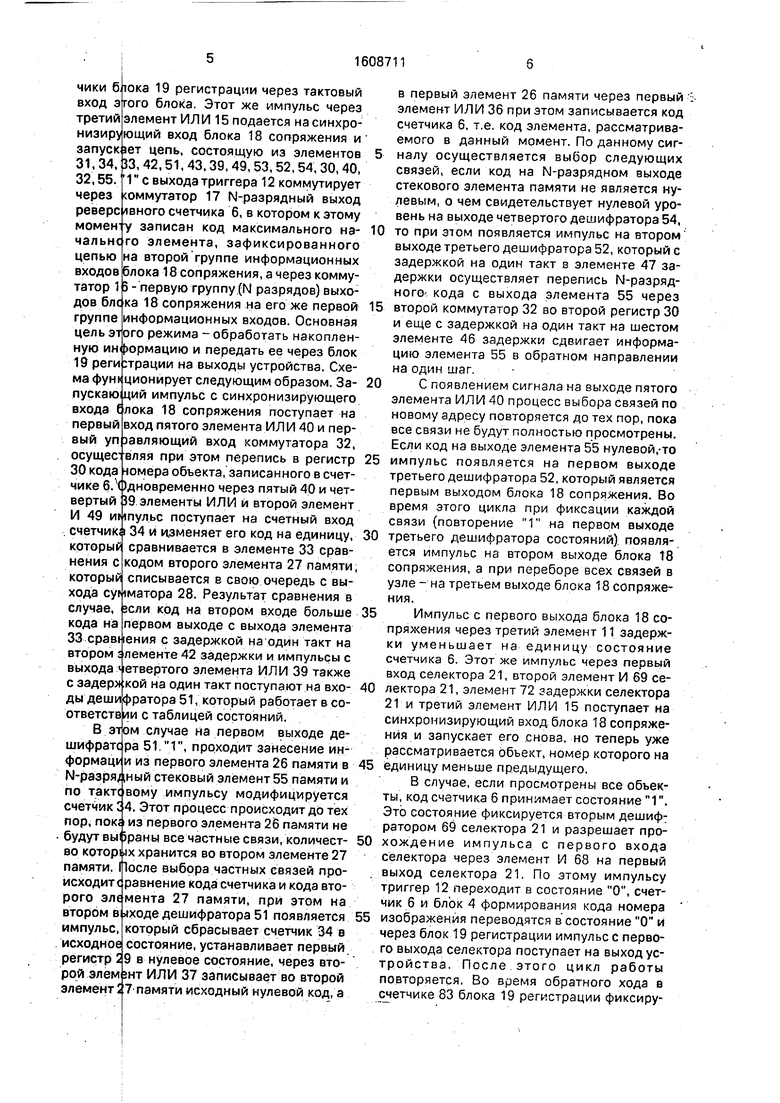

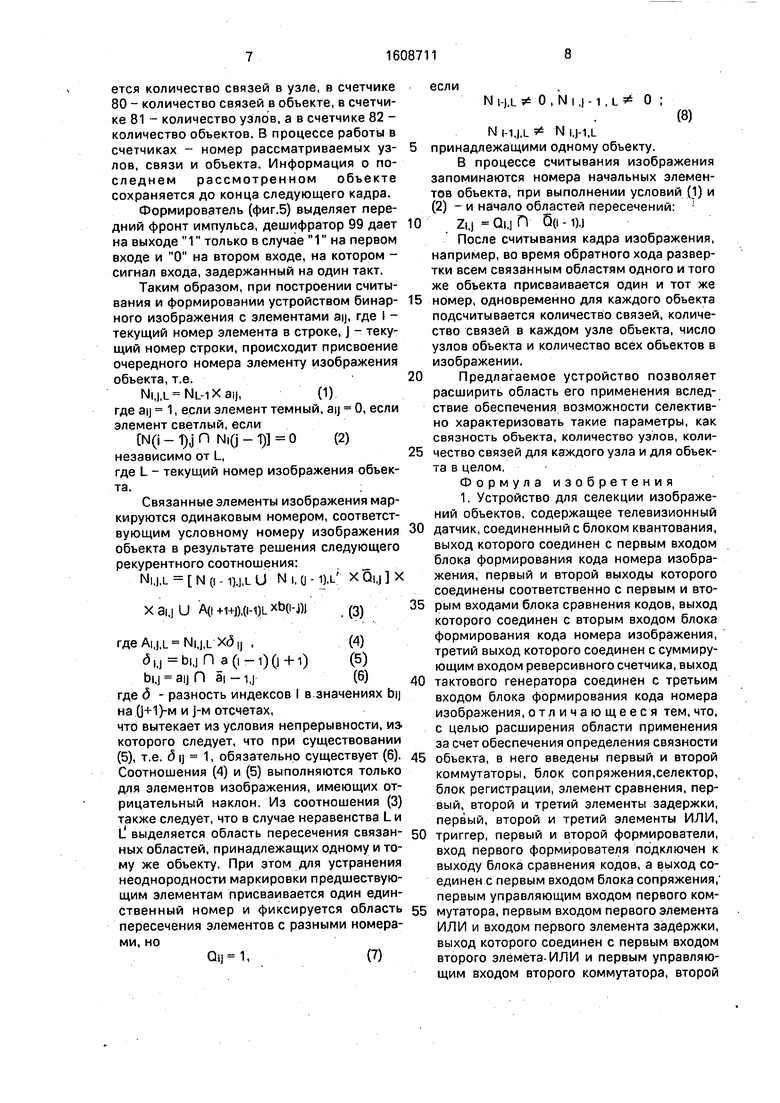

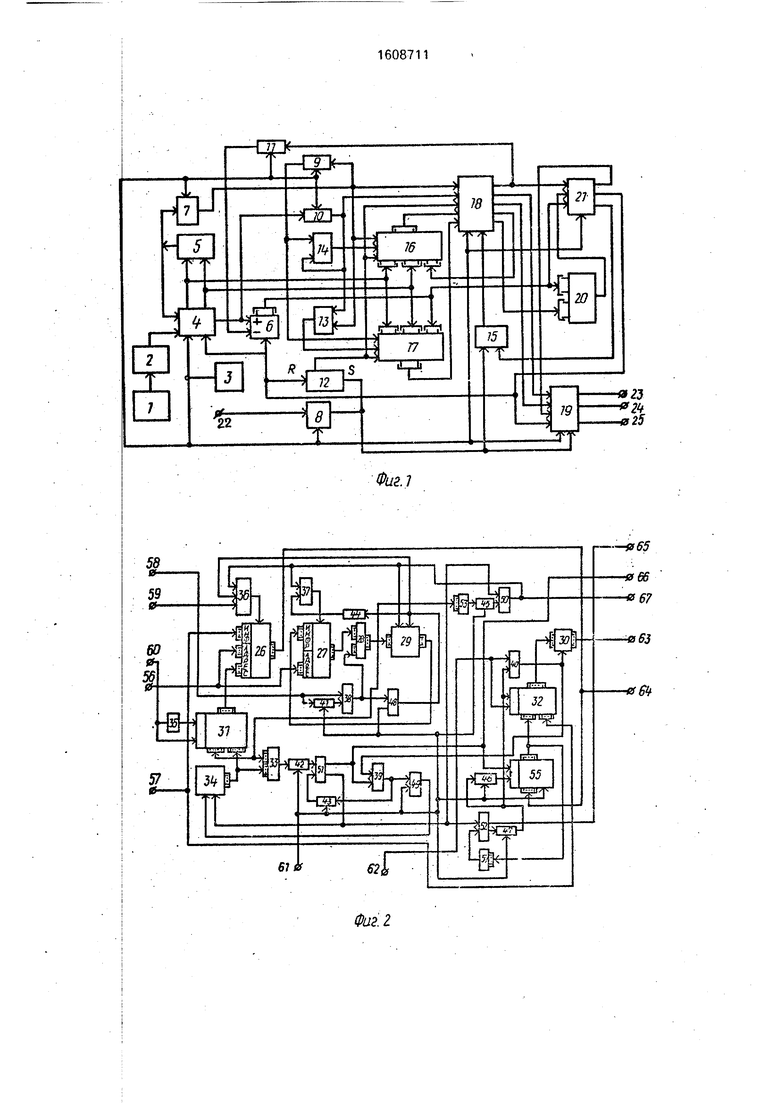

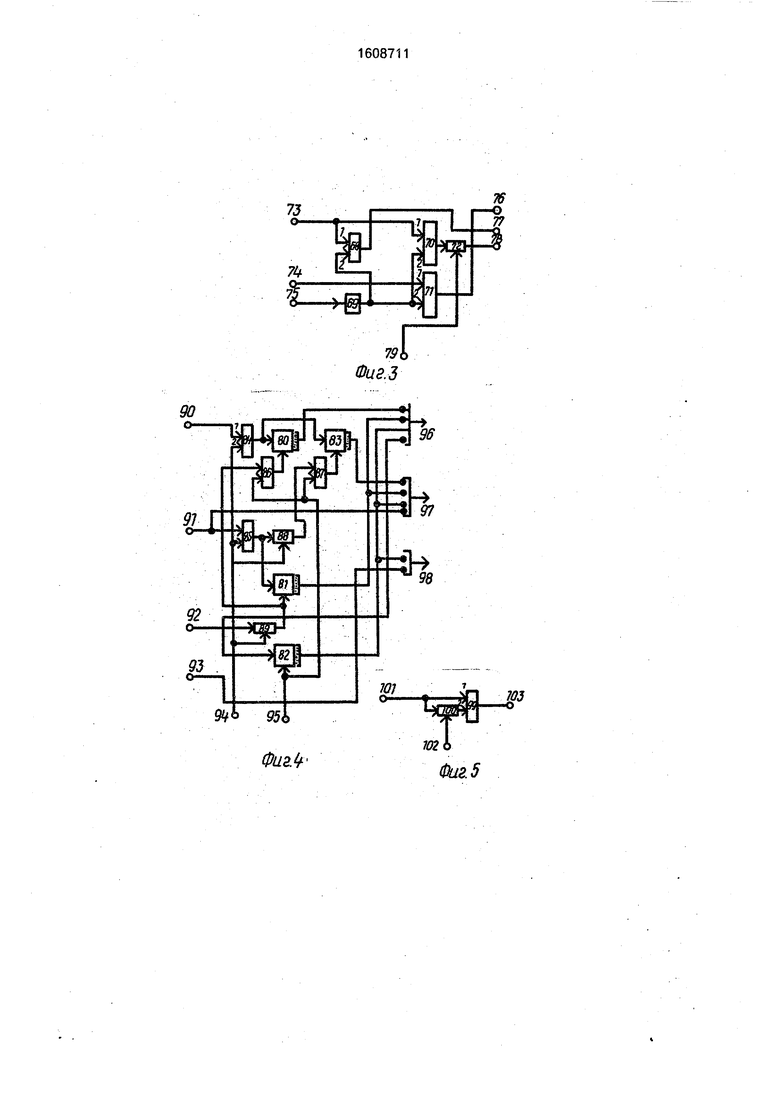

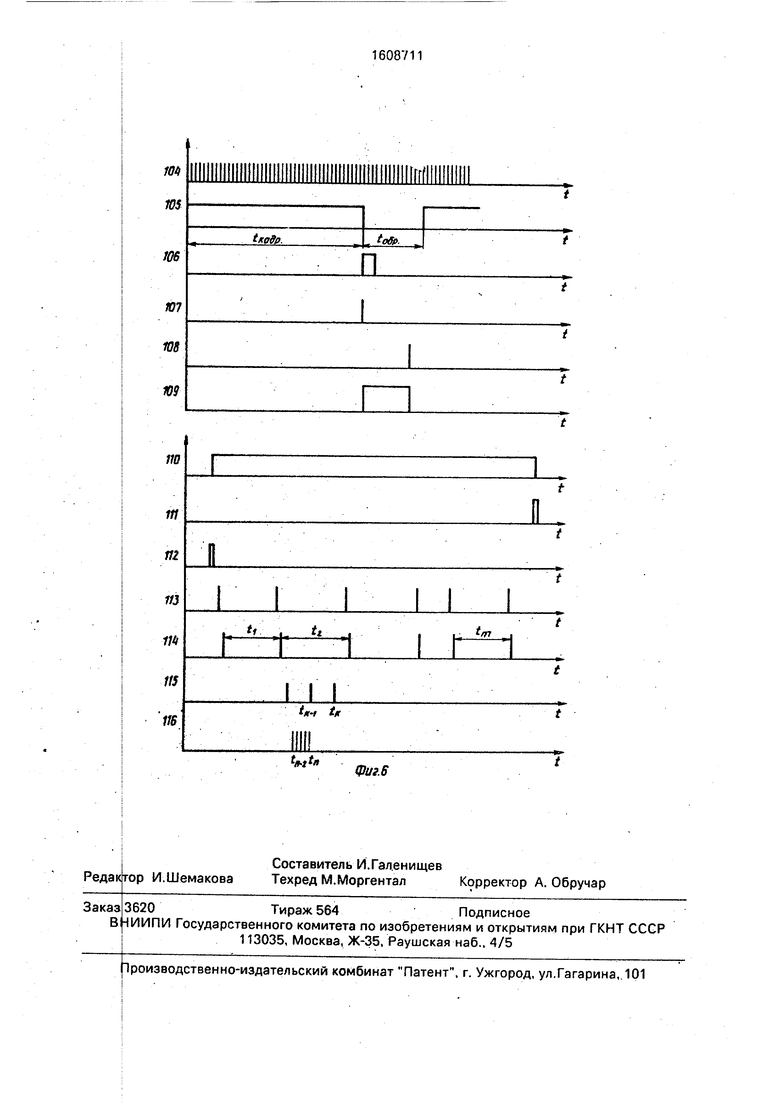

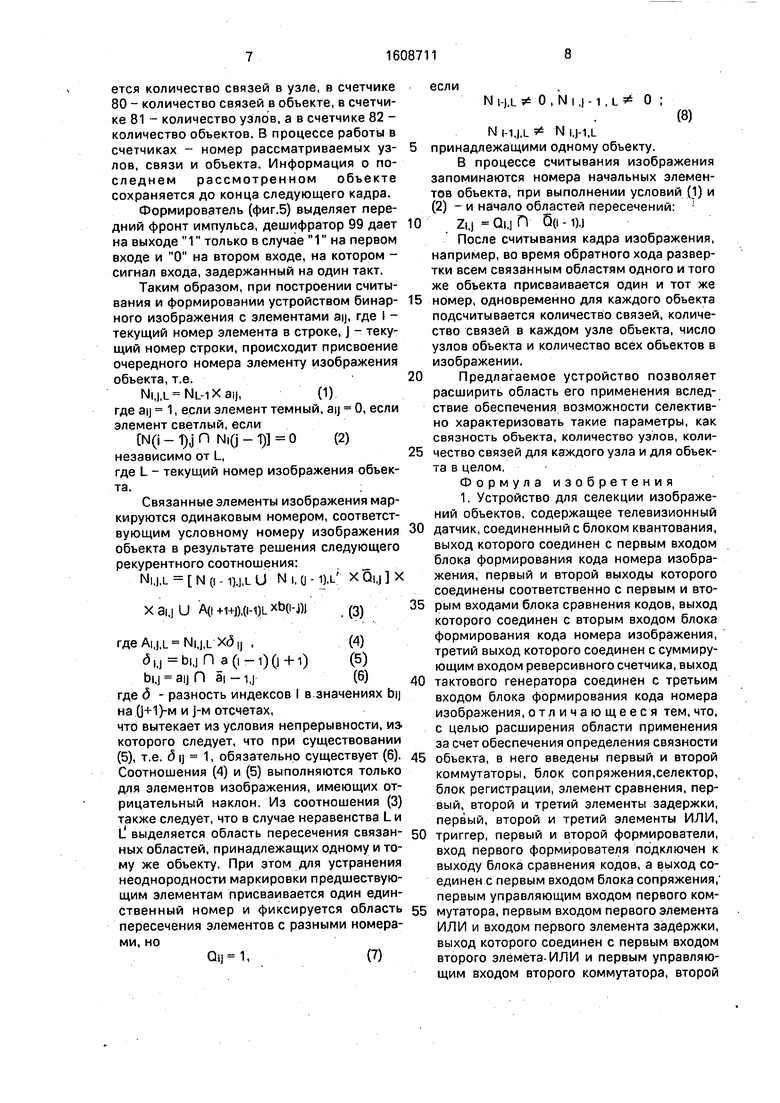

На фиг.1 представлена блок-схема устройства; на фиг.2 - функциональная схема блока сопряжения,- на фиг.З - примег выполнения функциональной схемы селектора;-На фиг.4 - пример выполнения функьиональной схемы блока регистрации; на ф11г.5 - пример выполнения функциональной схемы формирователя; на фиг.6 - временная диаграмма, поясняющая основные ц/1клы работы устройства.

Устройство содержит телевизионный. датчик 1, блок 2 квантования, генератор 3 тактовых импульсов, блок 4 формирования

кода номера изображения, блок 5 сравнения кодов, реверсивный счетчик 6, первый 7 и второй 8 формирователи, первый 9, второй 10 и третий 11 элементы задержки, тр иггер 12, первый 13, второй 14 и третий 15 элементы ИЛИ, первый 16 и второй 17 коммутаторы, блок 18 сопряжения, блок 19 регистрации, элемент 20 сравнения, селектор 21, вход 22 синхронизации, первый 23, второй 24 и третий 25 выходы устройства.

Блок 18 сопряжения (фиг.2) содержит первый 26 и второй 27 элементы памяти, сумматор 28, первый 29 и второй 30 регистры, первый 31 и второй 32 коммутаторы, элемент 33 сравнения, счетчик 34, элемент НЕ 35,- первый 36, второй 37, третий 38, четвертый 39 и пятый 40 элементы ИЛИ, первый 41, второй 42, третий 43, четвертый 44, пятый 45, шестой 46 и седьмой 47 элементы задержки, первый 48, второй 49 и третий 50 элементы И, первый 51, второй 52, третий 53 и четвертый 54 дешифраторы, эле

О О 00 VI

мент 55 стековой памяти, первую 56 и вторую 57 группы информационных входов, первый 58, второй 59 и третий 60 управляющие входы, тактовый 61 и синхронизирующий 62 входы, первую 63 и вторую 64 группы выходов, первый 65, второй 66 и третий 67 выходы.

Селектор 21 (фиг.З) содержит первый 68 и второй 69 дешифраторы, первый 70 и второй 71 элементы И, элемент 72 задержки, первый 73 и второй 74 входы, группу входов 75, первый 76, второй 77 и третий 78 выходы и тактовый вход 79.

Блок 19 регистрации (фиг.4) содержит первый 80, второй 81, третий 82 и четвертый 83 счетчики, первый 84 и второй 85 элементы И, первый 86 и второй 87 элементы ИЛИ, первый 88 и второй 89 элементы задержки, первый 90, второй 91, третий 92 и четвертый 93 входы, тактовый 94 и синхронизирующий 95 входы, первый 96, второй 97 и третий 98 выходы.

Формирователь (фиг.5) содержит дешифратор 99, элемент 100 задержки, вход 101, тактовый вход 102 и выход 103.

На временной диаграмме (фиг.6) показаны импульсы 104 на выходе генератора 3 и импульсы 105 синхронизации телевизионного датчика 1 (где 1кадр. - время прямого хода луча считывания изображения; to6p. время обратного хода луча считывания изображения), импульсы 106 на входе 22 устройства, импульсы 107 на выходе формирователя 8, импульсы 108 на первом входе селектора 21, импульсы 109 на выходе триггера 12, импульсы 110 на входе триггера 12, импульсы 111 на четвертом входе и третьем выходе блока 19 регистрации, импульсы 112 на тактовом входе блока 19 регистрации, импульсы 113 на синхронизирующем входе блока 18 сопряжения, импульсы 114 на третьем входе и первом выходе блока 19 регистрации (где m - число объек-- тов), импульсы 115 на втором входе и втором выходе блока 19 (где К - число узлов) и импульсы 116 на первом входе блока 19 (где п - число связей в узле).

Устройство работает следующим образом.

Изображение, представляющее собой фигуры произвольной формы, сканируется телевизионным датчиком 1 и квантуется на два уровня блоком 2 квантования. Бинарный видеосигнал с выхода блока 2 квантования поступает на первый вход блока 4 формирования кода номера изображения. Во время считывания кадра триггер 12 находится в состоянии О, во время обратного хода - в состоянии 1.

В процессе счит.ывания изображения в первый элемент 26 памяти блока сопряжения заносится номер начального элемента обьекта. При этом на третьем выходе блока 4 формирования кода номера изображения появляется импульс, длительностью равный времени разложения одного элемента в строке, и через элемент 10 задержки и элементы ИЛИ 14 и 13 поступает на вторые

0 управляющие входы первого (адресного) 16 и второго (информационного) 17 коммутаторов и на второй вход блока 18 сопряжения, где через первый элемент ИЛИ 36- на вход Запись первого элемента 26 памяти. Ин5 формация о номере объекта с первого выхода блока 4 формирования кода номера изображения коммутируется через вторые группы информационных входов коммутаторов 16 и 17 и записывается в первый эле0 мент 26 памяти. В случае пересечения областей, принадлежащих одному и тому же объекту с разными начальными номерами, на выходе блока 5 сравнения кодов возникает импульс, который через первый форми5 рователь 7 поступает на первый вход блока 18 сопряжения. По этому сигналу посредством первого элемента 41 задержки, третьего элемента ИЛИ 38, первого элемента И 48, первого регистра 29, сумматора 28, чет0 вертого элемента 44 задержки и второго элемента ИЛИ 37 осуществляется увеличение кода второго элемента 27 памяти на единицу и при этом младшие разряды адреса второго элемента 27 памяти через пер5 вый коммутатор 31 имеют код сумматора 28. За счет задержки сигнала с выхода блока 4 формирования кода номера изображения на первом элементе 9 задержки в элемент 26 памяти блока 18 сопряжения по адресу,

0 определяемому кодом первого выхода блока 4 формирования кода номера изображения записывается информация кодом с второго выхода блока 4 формирования кода номера изображения, а через такт в первый

5 элемент 26 памяти по адресу, определяемому кодом с второго выхода блока 4 формирования кода номера изображения, записывется информация, определяемая кодом с первого выхода блока 4. В резуль0 тате, по каждому адресу, определяемому кодом на первой группе информационных входов блока 18 сопряжения, в первом элементе 26 памяти записывается связь, а во втором элементе 27 памяти - количество

5 связей узла с данным номером.

После считывания кадра изображения на тактовый вход формирователя 7 подается импульс, который переводит триггер 12 в состояние 1. Импульс с выхода блока 8 устанавливает в начальное состояние счетчикивход э третий низирующий запуск1ет 33,

этого

г

10

15

б|1ока 19 регистрации через тактовый ого блока. Этот же импульс через элемент ИЛИ 15 подается на синхро- вход блока 18 сопряжения и цепь, состоящую из элементов 1, 42,51, 43,39, 49,53, 52,54, 30, 40, с выхода триггера 12 коммутирует ;оммутатор 17 N-разрядный выход явного счетчика 6, в котором к этому записан код максимального на- элемента, зафиксированного на второй группе информационных 18 сопряжения, а через комму- - первую группу (N разрядов) выхо- блс ка 18 сопряжения на его же первой информационных входов. Основная режима - обработать накоплен- ин ормацию и передать ее через блок :трации на выходы устройства. Схе- функ ционирует следующим образом. За- 20 э ций импульс с синхронизирующего Слока 18 сопряжения поступает на вход пятого элемента ИЛИ 40 и пер- уп завляющий вход коммутатора 32, вляя при этом перепись в регистр hioMepa объекта, записанного в счет- )дновременно через пятый 40 и чет- J9 элементы ИЛИ и второй элемент щпульс поступает на счетный вход 34 и изменяет его код на единицу, сравнивается в элементе 33 срав- кодом второго элемента 27 памяти списывается в свою очередь с вы- сугйматора 28. Результат сравнения в зсли код на втором входе больше первом выходе с выхода элемента сравнения с задержкой на один такт на лементе 42 задержки и импульсы с етвертого элемента ИЛИ 39 также на один такт поступают на вхо- дешифратора 51, который работает в со- с таблицей состояний, случае на первом выходе де- 51 1, проходит занесение ин- и из первого элемента 26 памяти в ный стековый элемент 55 памяти и тактс вому импульсу модифицируется 4. Этот процесс происходит до тех из первого элемента 26 памяти не )раны все частные связи, количест- 4х хранится во втором элементе 27 После выбора частных связей про- кода} счетчика и кода вто- эле|мента 27 памяти, при этом на заходе дешифратора 51 появляется который сбрасывает счетчик 34 а состояние, устанавливает первый 9 в нулевое состояние, через вто- энт ИЛИ 37 записывает во второй 7 памяти исходный нулевой код, а

31,34,

32,55.

через

реверс

моменту

чальн(|го

цепью

входов |блока

татор

дов

группе

цель

ную

19 реги

ма

лускаю|ций

входа

первый

вый

осущес

30 кода номера объекта,

чике 6вертый

И 49 .счетчик который нения с который хода случае, кода на 33

втором; выхода с задер;| кой ды

ответствии В этом шифратора формаци N-разря по

счетчик С пор, пок; будут вы во котор памяти.

исходит (равнение i ого втором в мпульс, сходное егистр ой элем лемент

25

30

35

40

45

50

55

10

15

20

25

30

5

0

5

0

5

в первый элемент 26 памяти через первый элемент ИЛИ 36 при этом записывается код счетчика 6. т.е. код элемента, рассматриваемого в данный момент. По данному сигналу осуществляется выСзор следующих связей, если код на N-разрядном выходе стекового элемента памяти не является нулевым, о чем свидетельствует нулевой уровень на выходе четвертого дешифратора 54, то при этом появляется импульс на втором выходе третьего дешифратора 52, который с задержкой на один такт в элементе 47 задержки осуществляет перепись N-разряд- ного кода с выхода элемента 55 через второй коммутатор 32 во второй регистр 30 и еще с задержкой на один такт на шестом элементе 46 задержки сдвигает информацию элемента 55 в обратном направлении на один шаг,

С появлением сигнала на выходе пятого элемента ИЛИ 40 процесс выбора связей по новому адресу повторяется до тех пор, пока все связи не будут полностью просмотрены. Если код на выходе элемента 55 нулевой,-то импульс появляется на первом выходе третьего дешифратора 52, который является первым выходом блока 18 сопряжения. Во время этого цикла при фиксации каждой связи (повторение 1 на первом выходе третьего дешифратора состояний), появляется импульс на втором выходе блока 18 сопряжения, а при переборе всех связей в узле - на третьем выходе блока 18 сопряжения.

Импульс с первого выхода блока 18 сопряжения через третий элемент 11 задержки уменьшает на единицу состояние счетчика 6. Этот же импульс через первый вход селектора 21, второй элемент И 69 селектора 21, элемент 72 задержки селектора 21 и третий элемент ИЛИ 15 поступает на синхронизирующий вход, блока 18 сопряжения и запускает его снова, но теперь уже рассматривается объект, номер которого на единицу меньше предыдущего.

В случае, если просмотрены все объекты, код счетчика 6 принимает состояние 1. Это состояние фиксируется вторым дешифратором 69 селектора 21 и разрешает прохождение импульса с первого входа селектора через элемент И 68 на первый выход селектора 21. По этому импульсу триггер 12 переходит в состояние О, счетчик 6 и блок 4 формирования кода номера изображения переводятся в состояние О и через блок 19 регистрации импульсе первого выхода селектора поступает на выход устройства. После этого цикл работы повторяется. Во время обратного хода в счетчике 83 блока 19 регистрации фиксируется количество связей в узле, в счетчике 80 - количество связей в объекте, в счетчике 81 - количество узлов, а в счетчике 82 - количество объектов. В процессе работъ в счетчиках - номер рассматриваемых узлов, связи и объекта. Информация о последнем рассмотренном объекте сохраняется до конца следующего кадра,

Формирователъ (фиг.5) выделяет передний фронт импульса, дешифратор 99 дает на выходе 1 только в случае 1 на первом входе и О на втором входе, на котором - сигнал входа, задержанный на один такт.

Таким образом, при построении считывания и формировании устройством бинарного изображения с элементами aij, где 1 - текущий номер элемента в строке, J - текущий номер строки, происходит присвоение очередного номера элементу изображения объекта, т.е.

Ni,j,L NL-I X aij,(1)

где ai 1, если элемент темный, aij О, если элемент светлый, если

N(i - 1)j П Ni(j - 1) О(2)

независимо от L,

где L - текущий номер изображения объекта.;

Связанные элементы изображения маркируются одинаковым номером, соответствующим условному номеру изображения объекта в результате решения следующего рекурентного соотношения:

NIJ.L N о - i),j,L и N i. О - i).L X Qi.j X

xai.j и A(n-Hj),(M)LXb(i-j)j(3)

где Ai,j,L Ni.j.L Х(5 ij ,(4)

a,..jn a(i-i)(j + i)(5)

bi,j aij n ai -i,j(6)

где д - разность индексов I в значениях bij на 0+1 )-м и J-M отсчетах, что вытекает из условия непрерывности, из- которого следует, что при существовании (5), т.е. (5ij 1, обязательно существует (6). Соотношения (4) и (5) выполняются только для элементов изображения, имеющих отрицательный наклон. Из соотношения (3) также следует, что в случае неравенства L и L выделяется область пересечения связанных областей, принадлежащих одному и тому же объекту. При этом для устранения неоднородности маркировки предшествующим элементам присваивается один единственный номер и фиксируется область пересечения элементов с разными номерами, но

Qil 1,(7)

если

N 1-J.L О , N I ,j -1 , L 5 О ;

(8)

N i-i.j,L N i,j-i.L

принадлежащими одному объекту.

В процессе считывания изображения запоминаются номера начальных элементов объекта, при выполнении условий (1) и (2) - и начало областей пересечений:

Zi,j Qi.n 6(i-i),j

После считывания кадра изображения, например, во время обратного хода развертки всем связанным областям одного и того же объекта присваивается один и тот же

номер, одновременно для каждого объекта подсчитывается количество связей, количество связей в каждом узле объекта, число узлов объекта и количество всех объектов в изображении.

Предлагаемое устройство позволяет расширить область его применения вследствие обеспечения возможности селективно характеризовать такие параметры, как связность объекта, количество узлов, количество связей для каждого узла и для объекта в целом,

Формула изобретения 1. Устройство для селекции изображений объектов, содержащее телевизионный

датчик, соединенный с блоком квантования, выход которого соединен с первым входом блока формирования кода номера изображения, первый и второй выходы которого соединены соответственно с первым и вторым входами блока сравнения кодов, выход которого соединен с вторым входом блока формирования кода номера изображения, третий выход которого соединен с суммирующим входом реверсивного счетчика, выход

тактового генератора соединен с третьим входом блока формирования кода номера изображения,отличающееся тем,что, с целью расширения области применения за счет обеспечения определения связности

объекта, в него введены первый и второй коммутаторы, блок сопряжения,селектор, блок регистрации, элемент сравнения, первый, второй и третий элементы задержки, первый, второй и третий элементы ИЛИ,

триггер, первый и второй формирователи, вход первого формирователя подключен к выходу блока сравнения кодов, а выход соединен с первым входом блока сопряжения, первым управляющим входом первого коммутатора, первым входом первого элемента ИЛИ и входом первого злемента задержки, выход которого соединен с первым входом второго элемёта-ИЛИ и первым управляющим входом второго коммутатора, второй

уг

ксторого

НС

сопряжения ключены

жки,

со 51

мера

ле тора,

мутатора,

первого

ны

из

втс

АОЕ1 XOjEl К Г

блс

ЦИС

ГРУ fine

Bbii

пефым I

эле

иен

сче

рой вых

сопряжения

пероым

ции

под

втор ому

которого

его

нен

сопряжения,

импульсов

первэго

держки

ции

орг

ера

ЛИ

10

равляющий вход которого подключен к ВЕ 1ходу первого элемента ИЛИ, второй вход го соединен с выходом второго эле- 1 задержки, вход которого подключен к тр|етьему выходу блока формирования кода изображения, вторые входы блока -ния и второго элемента ИЛИ под- к выходу второго элемента задер- л, группа выходов реверсивного счетчика единена с первыми группами входов се- -э. элемента сравнения и второго ком- -ta, вторая и третья группы входов I и второго коммутаторов подключе- соответственно к первому и второму вы- 1ам блока формирования кода номера 15 юбражения, второй управляющий вход коммутатора подключен к выходу :ррго элемента ИЛИ, первая группа вхо- I -к первой группе информационных вы- . ов блока сопряжения, а группа выходов - 20 ераой группе информационных входов : ка сопряжения, вторая группа информа- -жных входов которого подключена к 1пе выходов второго коммутатора, пер- выход блока сопряжения соединен с 25 шм входом селектора и входом третьего мента задержки, выход которого соеди- с вычитающим входом реверсивного гчика, вторая группа информационных выхэдов блока сопряжения соединенас вто- 30

группой входов элемента сравнения : )Д которого соединен с вторым входом селектора, второй и третий выходы блока |я соединены соответственно с и вторым входами блока регистра- 35 третий и четвертый входы которого ,|{:лючены соответственное первому и выходам селектора, третий выход ). соединен с первым входом треть- шемента ИЛИ, выход которого соеди- 40 с синхронизирующим входом блока , выход генератора тактовых соединен с тактирующими вхо- первого.и второго формирователей, -о,второго и третьего элементов за- 1, блока сопряжения, блока регистра- и селектора, выход второго ормирователя соединен с S-входом триг- вторым входом третьего элемента

и синхронизирующим входом блока 50 егистрации, второй выход селектора сое- иненс R-входом триггера и установочными ходс ми реверсивного счетчика и блока ормирования кода номера изображения, ыхол триггера соединен с третьими управ- 55 яющими входами первого и второго коммуаторов и блока сопряжения, вход второго ормирователя является синхронизирую- Е ходом устройства, а первый, второй и

45

я в д го уп эл пе вт су ны Ет

10

15 20 5 0

5

третий выходы блока регистрации являются соответствующими выходами устройства,

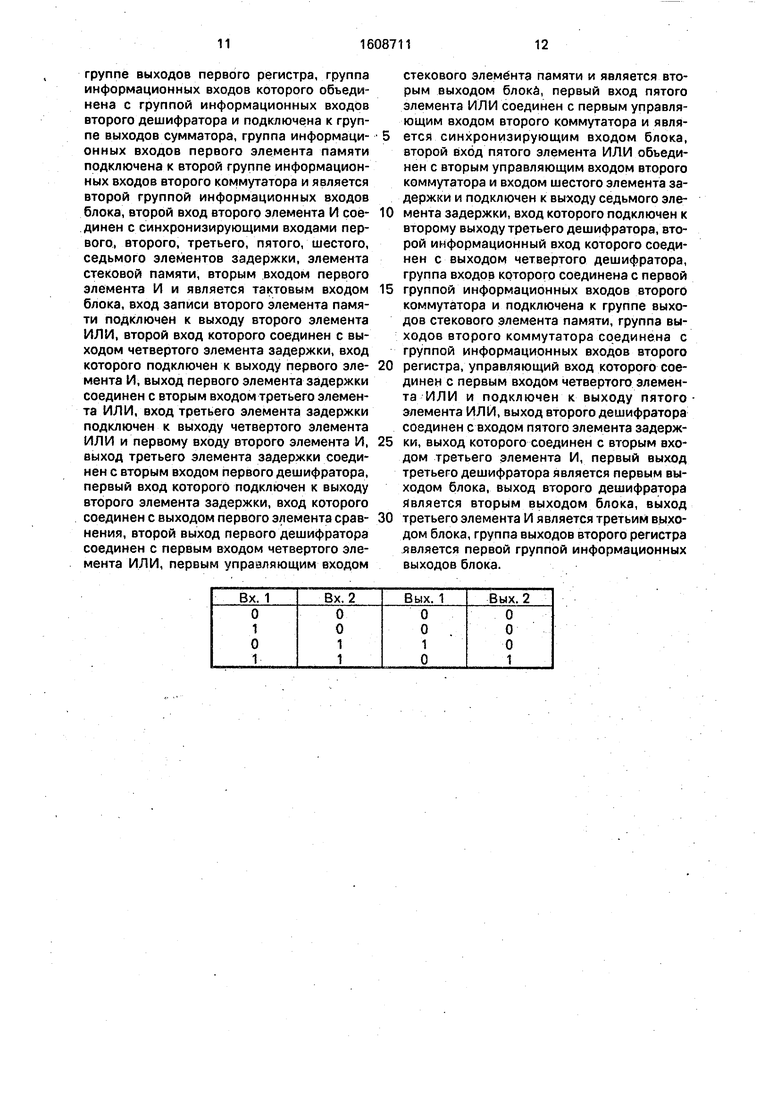

2. Устройство по П.1, отл ича ющее- с я тем, что блок сопряжения содержит элемент НЕ, с первой по пятый элементы ИЛИ, с первой по седьмой элементы задержки первый, второй и третий элементы И, элемент сравнения, счетчик, первый и второй коммутаторы, первый и второй элементы памяти, сумматор, первый и второй регистр первый, второй, третий и четвертый дешифраторы и элемент стековой памяти, первая группа адресных входов первого элемента памяти соединена с группой адресных входов второго элемента памяти и является первой группой информационных входов блока, вторая группа адресных входов первого элемента памяти подключена к выходу первого коммутатора, первый управляющий вход которого подключен к выходу первого элемента НЕ, а второй управляющий вход является третьим управляющим входом блока и соединен с входом первого элемента НЕ, первая и вторая группы информационных входов первого коммутатора соединены соответственно с первой и второй группами информационных входов первого элемента сравнения и подключены соответственно к группам выходов сумматора и счетчика, счетный и установочный входы которого подключены соответственно к выходу второго элемента И и второму выходу первого дешифратора, первые входы первого и второго элементов ИЛИ соединены с первым управляющим входом первого регистра и подключены к выходу третьего элемента И,первый вход которого объединен с первым входом третьего дешифратора и подключен к второму выходу второго дешифратора, второй вход первого элемента ИЛИ и второй управляющий вход первого регистра подключены к выходу первого элемента И, третий вход первого элемента ИЛИ является вторым управляющим входом блока, а выход первого элемента ИЛИ соединен с входом записи первого элемента памяти выход которого соединен с информационным входом стекового элемента памяти и является второй группой информационных выходов блока, вход первого элемента задержки объединен с первым входом третьего элемента ИЛИ и является первым управляющим входом блока, выход третьего элемента ИЛИ соединен с первым входом первого элемента И и последним разрядом второй группы информационных входов сумматора, первая группа информационных входов которого подключена к выходу Еторого элемента памяти, группа информа- ц ионных входов которого подключена к

группе выходов первого регистра, группа информационных входов которого объединена с группой информационных входов второго дешифратора и подключена к группе выходов сумматора, группа информаци- онных входов первого элемента памяти подключена к второй группе информационных входов второго коммутатора и является второй группой информационных входов блока, второй вход второго элемента И сое- динен с синхронизирующими входами первого, второго, третьего, пятого, шестого, седьмого элементов задержки, элемента стековой памяти, вторым входом первого элемента И и является тактовым входом блока, вход записи второго элемента памяти подключен к выходу второго элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента задержки, вход которого подключена выходу первого эле- мента И, выход первого элемента задержки соединен с вторым входом третьего элемента ИЛИ, вход третьего элемента задержки подключен к выходу четвертого элемента ИЛИ и первому входу второго элемента И, выход третьего элемента задержки соединен с вторым входом первого дешифратора, первый вход которого подключен к выходу второго элемента задержки, вход которого соединен с выходом первого элемента срав- нения, второй выход первого дешифратора соединен с первым входом четвертого элемента ИЛИ, первым управляющим входом

стекового элемента памяти и является вторым выходом блоки, первый вход пятого элемента ИЛИ соединен с первым управляющим входом второго коммутатора и является синхронизирующим входом блока, второй вход пятого элемента ИЛИ объединен с вторым управляющим входом второго коммутатора и входом шестого элемента задержки и подключен к выходу седьмого элемента задержки, вход которого подключен к второму выходу третьего дешифратора, второй информационный вход которого соединен с выходом четвертого дешифратора, группа входов которого соединена с первой группой информационных входов второго коммутатора и подключена к группе выходов стекового элемента памяти, группа выходов второго коммутатора соединена с группой информационных входов второго регистра, управляющий вход которого соединен с первым входом четвертого элемента ИЛИ и подключен к выходу пятого элемента ИЛИ, выход второго дешифратора соединен с входом пятого элемента задержки, выход которого соединен с вторым входом третьего элемента И, первый выход третьего дешифратора является первым выходом блока, выход второго дешифратора Является вторым выходом блока, выход третьего элемента И является третьим выходом блока, группа выходов второго регистра является первой группой информационных выходов блока.

23

7 г 25

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания и кодирования изображений объектов | 1986 |

|

SU1548800A1 |

| Устройство для считывания и кодирования изображений объектов | 1988 |

|

SU1631563A1 |

| Устройство для обмена информацией | 1979 |

|

SU826328A1 |

| Устройство для обработки выражений языков программирования | 1981 |

|

SU1016790A1 |

| Устройство для селекции изображений | 1991 |

|

SU1837335A1 |

| Устройство для контроля работы оператора | 1990 |

|

SU1718263A2 |

| Устройство для распознавания подвижных объектов | 1989 |

|

SU1649575A1 |

| Устройство для идентификации признаков объектов | 1989 |

|

SU1626258A1 |

| Устройство для управления параллельным выполнением команд в электронной вычислительной машине | 1982 |

|

SU1078429A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1983 |

|

SU1119065A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для определения параметров изображений в системах с техническим зрением и в устройствах для распознавания образов. Цель изобретения - расширение области применения за счет обеспечения возможности определения связности объекта. Устройство содержит телевизионный датчик, блок квантования, генератор, блок формирования кода номера изображения, блок сравнения кодов, реверсивный счетчик, два формирователя, три элемента задержки, триггер, три элемента ИЛИ, два коммутатора, блок сопряжения, блок регистрации, элемент сравнения и селектор. 1 з.п. ф-лы., 6 ил., 1 табл.

-IS 65

75 o74

cz;

Фиг.

76

Ю

77

I

p

7J

7ffb

ФцгЗ

и 9ff

Фиг. 5

| Устройство для селекции изображений объектов | 1980 |

|

SU911569A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-11-23—Публикация

1988-01-18—Подача