Изобретение относится к автомати- ке и вычислительной технике и может быть использовано в системах с техническим зрением для селекции изображений.

Цель изобретения - расширение области применения устройства за счет обеспечения возможности подсчета количества отверстий для каждого объекта на изображении.

Сущность изобретения состоит в том, что при построчном считывания изображений формируется бинарное позиционное изображение. Структура матрицы, представляющая бинарное позитивное изображение .такова, что темным элементам изображения объектов соответствуют отсчеты а ; , равные 1, а светлым -элементам, соответствующим отверстиям объекта и фрну,равные О, где i - текущий номер элемента в строке, меняющийся от 0 до п (п - число элементов отсчета в строке, включая обратный ход); j - текущий номер строки.

Одновременно формируется бинарное негативное изображение путем преобразования позитивного следующим образом:

п

а -. h ;; Ч Ч

г

а Ч

(1)

при этом h

М

при 0ЈiЈn и

(m - число строк разложения кадра) и h 0 на строках, соответствующих, например, обратному ходу кадра.

Связным элементам позитивного изображения присваиваются одинаковые номера, соответствующие условному

О

GO

оо 1

00

номеру позитивного изображения объек- та в результате решения следующего

.рекуррентного соотношения:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для считывания и кодирования изображений объектов | 1988 |

|

SU1631563A1 |

| Устройство для селекции дефектов изображений объектов | 1988 |

|

SU1631562A1 |

| Устройство для селекции изображений объектов | 1987 |

|

SU1525718A1 |

| Устройство для определения площади изображений | 1988 |

|

SU1644183A1 |

| Устройство для считывания и кодирования изображений объектов | 1986 |

|

SU1548800A1 |

| УСТРОЙСТВО ДЛЯ СЕЛЕКЦИИ ИЗОБРАЖЕНИЙ ОБЪЕКТОВ | 1990 |

|

RU2032218C1 |

| Устройство для определения углового положения указателя стрелочных приборов | 1987 |

|

SU1532812A1 |

| Устройство для подсчета изображений объектов | 1988 |

|

SU1640720A1 |

| Устройство для подсчета количества изображений объектов | 1986 |

|

SU1383413A1 |

| Устройство для селекции изображений объектов | 1988 |

|

SU1608711A1 |

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах технического зрения. Целью изобретения является расширение области применения устройства. Поставленная цель достигается тем, что в устройство, содержащее телевизионный датчик, блок квантования, первый блок сравнения кодов, первый блок формирования кода изображения, введены два блока определения связности,блок кодирования связей, блок памяти кодов, вторые блоки сравнения кодов и формирования кода изображения, два элемента И, формирователь импульсов, блок анализа объектов, элемент НЕ. За счет подсчета количества отверстий для каждого объекта расширяется область применения устройства, 9 ил. S

; , к,,.е лц..,.в. (2)

Связным элементам печатного изоб- номера в результате решения рекур- ражения также присваивают одинаковые 10 рентного соотношения

i

I W-M-IM, V4 a;jUA yj.,u. в . о)

(4) (5) (6)

В соотношениях (2) и (3)

AiJL -HJilJijS Јij -В-Па;.чЧ|«

ьч ачП5и-г

Соотношения (4) и (5) выполняются только для элементов изображения, имеющих отрицательный наклон. Из соотношений (2) и (3)следует,чт в случае неравенства L и Lr выделяется область пересечения связных зон принадлежащих одному и тому же объекту.

Область пересечений

если

Qij

i,

(7)

HJ-,i,b °« N.H.U 0; нЧл ым- Л- ()

Присвоение очередного номера изображения объекту происходит для элементов изображения

(9)

N

,-jb , J.

если

Кч HN .,-,- °. 00)

где М - текущий номер изображения

объекта.

При выполнении (7) формируется начальный элемент области пересечений для позитивного изображения

H-j- S. п)

и для негативного изображения

Hli ,р 02)

а при выполнении (9) и (10) формируется метка S для позитивного изображения и метка S для негативного изображения.

0

5

0

5

0

5

0

5

Элементы, для которых формируются метки S |j или S , соответствуют начальным элементам либо позитивного, либо негативного изображения соответственно.

По начальным элементам областей пересечения (11) и (12) и по меткам S jj и устанавливаются связи между связными областями. Причем признаком связи номера данной области с самой областью является наличие меток S ;; или , признаком связи пересекающихся областей - наличие начальных элементов Нц или Hj: .Для номера данной области число начальных элементов или Н : областей пересечения определяет число связей, а их последовательная запись - локальный список связных областей.

Кроме выявления связей между связными областями только для п,озитивно- го или только для негативного изображения, устанавливаются связи между номером позитивного изображения и связанным с ним номером негатив- . ного изображения. При этом для номера области позитивного изображения число начальных элементов Sу ,соответствующих негативному изображению, определяет число взаимных связей области позитивного и негативного изображений, а их последовательная запись - список взаимно связных областей.

По локальному списку связных областей определяются все связные области путем присвоения им номера,соответствующего минимальному номеру в данной связной системе. По такому принципу устанавливается связность одновременно как для позитивного, так и для негативного изображения.

3,16

Причем для негативного изображения всем номерам, связанным с фоном изображения, присваивается номер фона, т.е. первый номер, а номера отверс- тий объектов имеют номера больше единицы.

Число отверстий для каждого объекта подсчитывается путем суммирования связей из списка взаимно связан ных областей. При этом суммируются только те связи, для которых номера

и

начальных элементов S в списке равны минимальным в связанной системе для негативного изображения и не рав ны первому номеру.

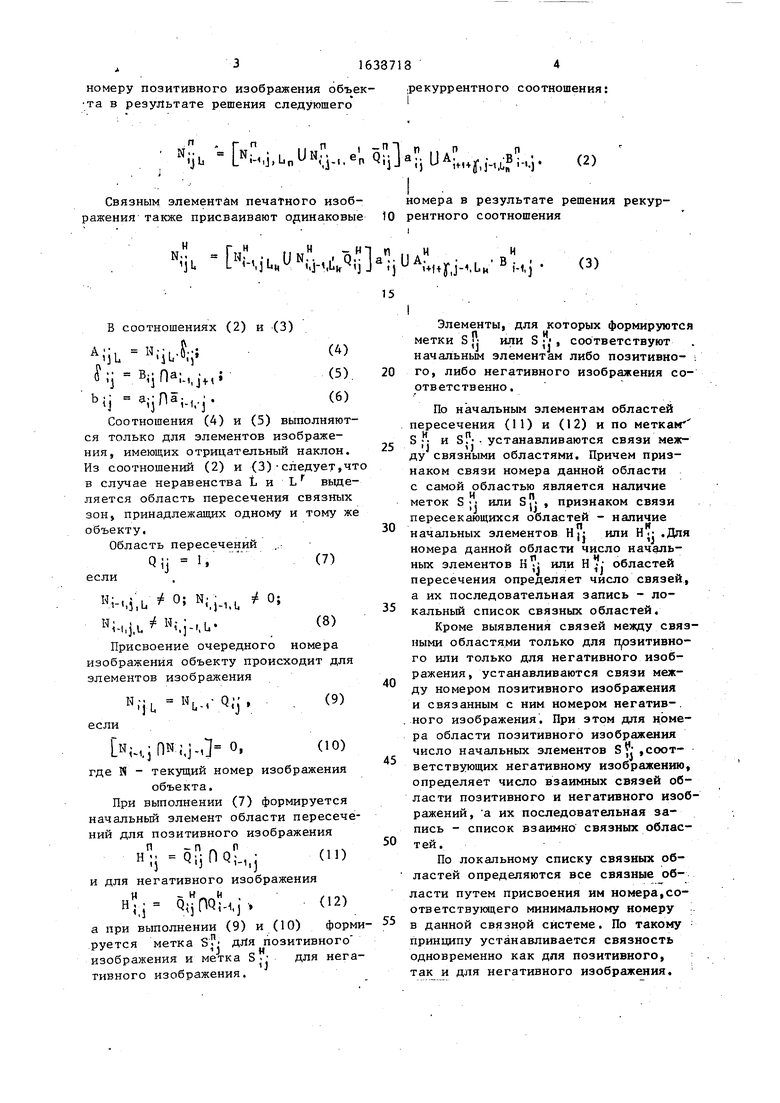

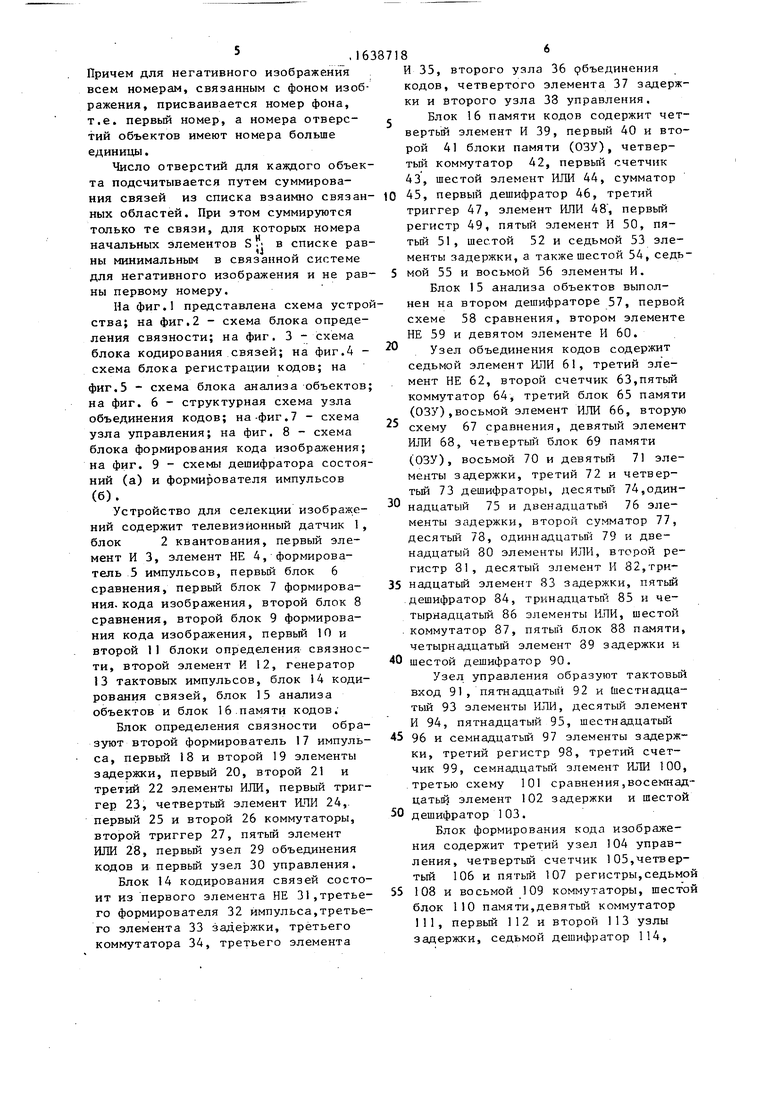

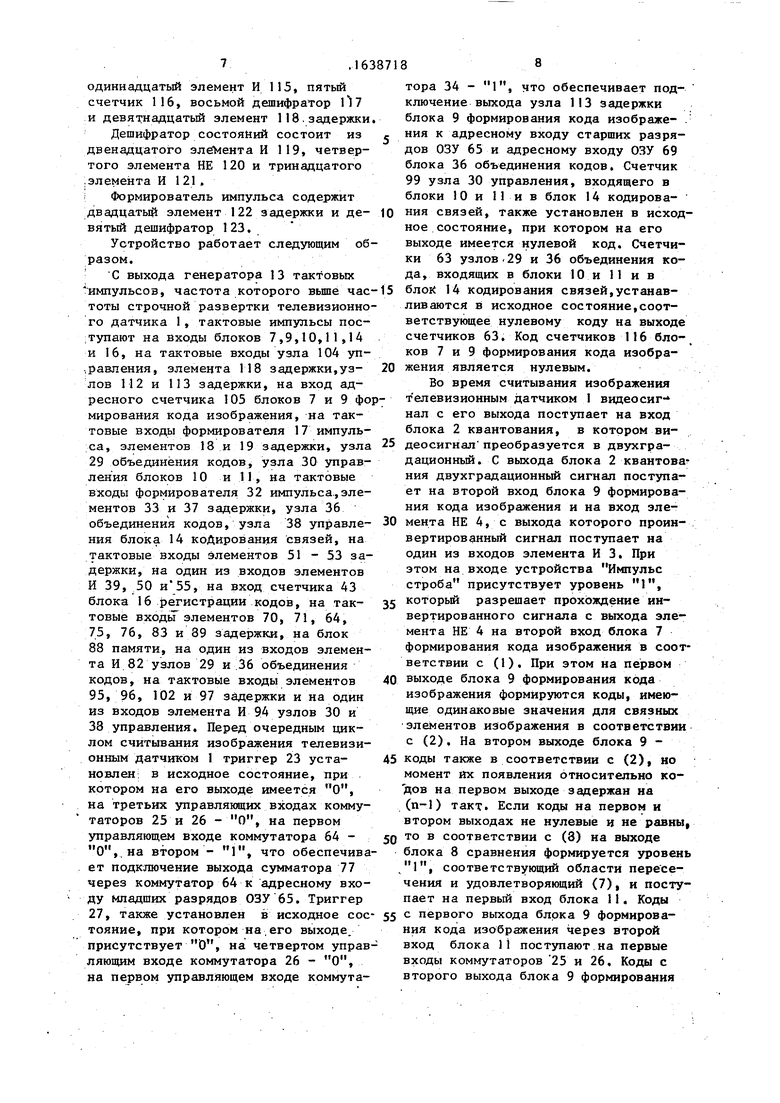

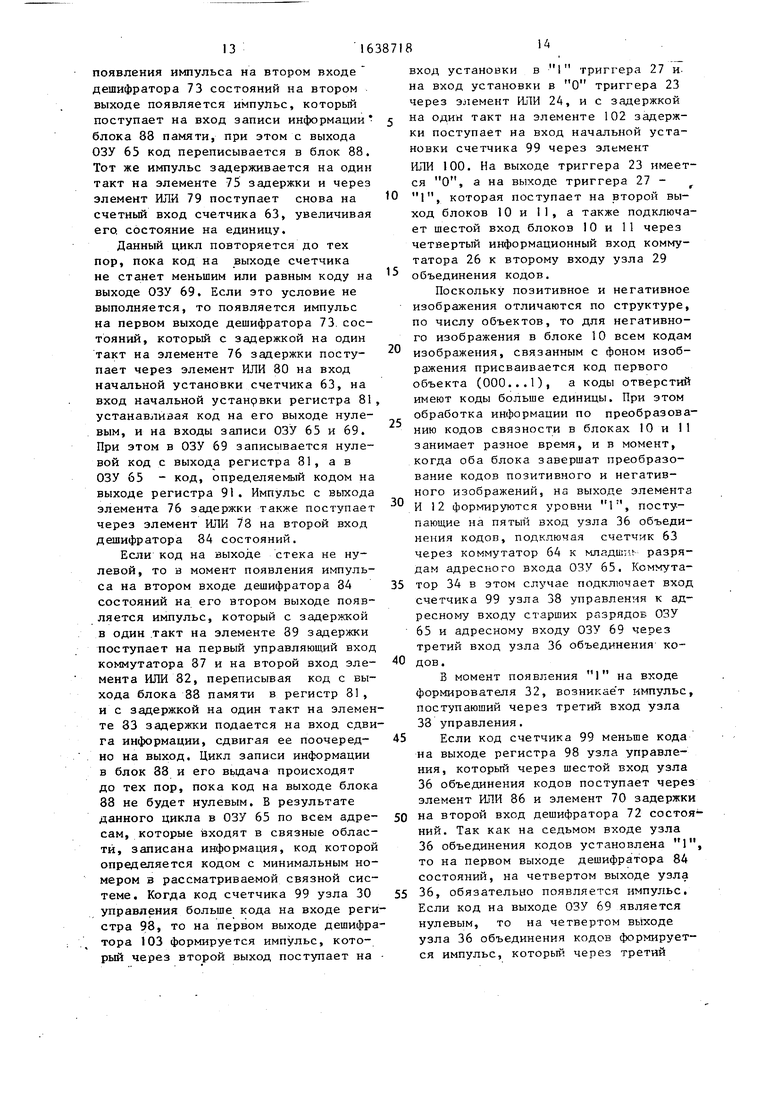

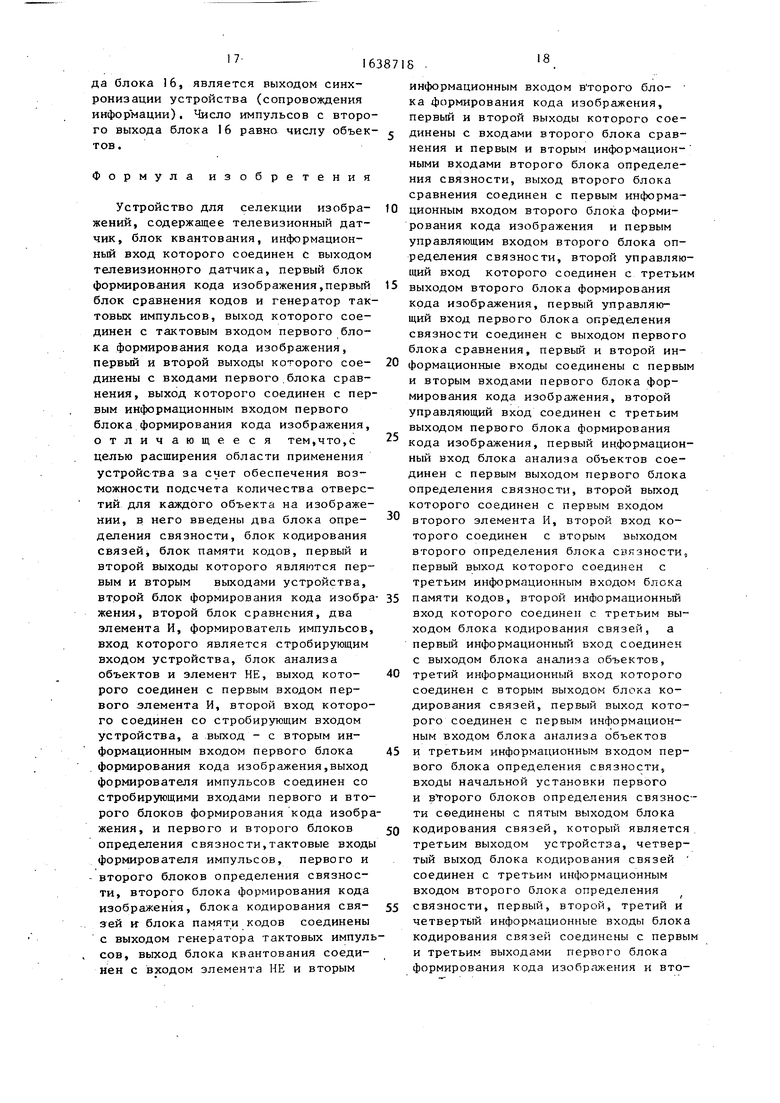

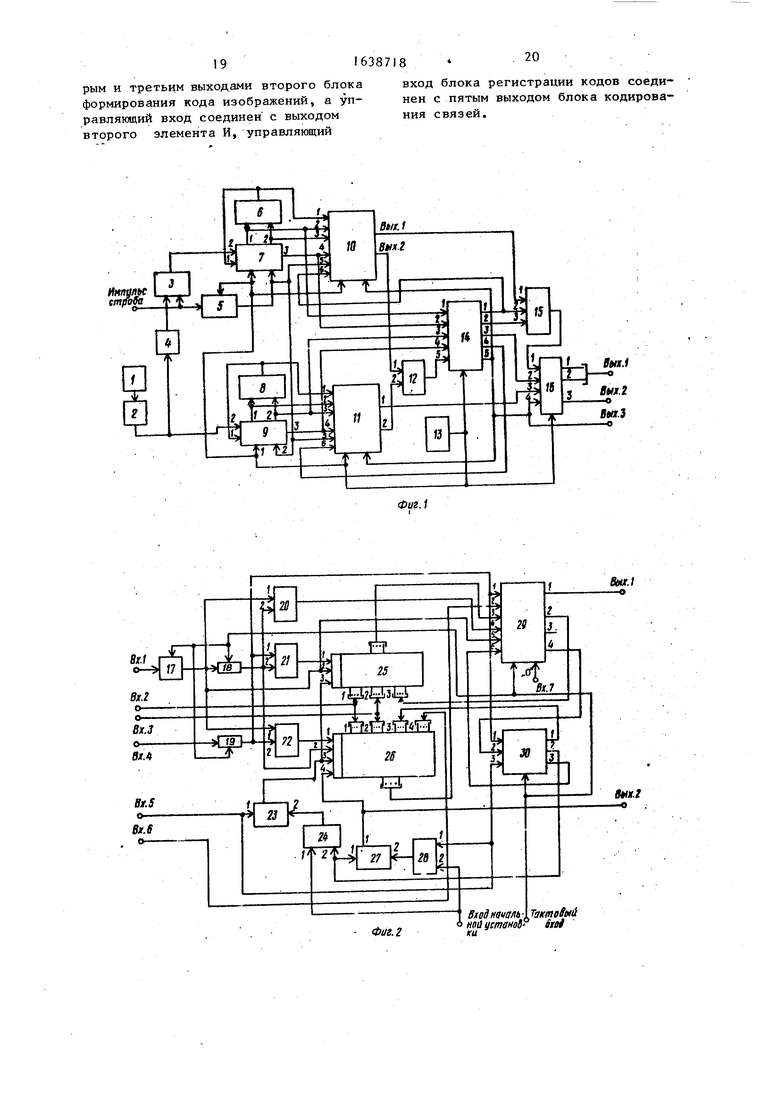

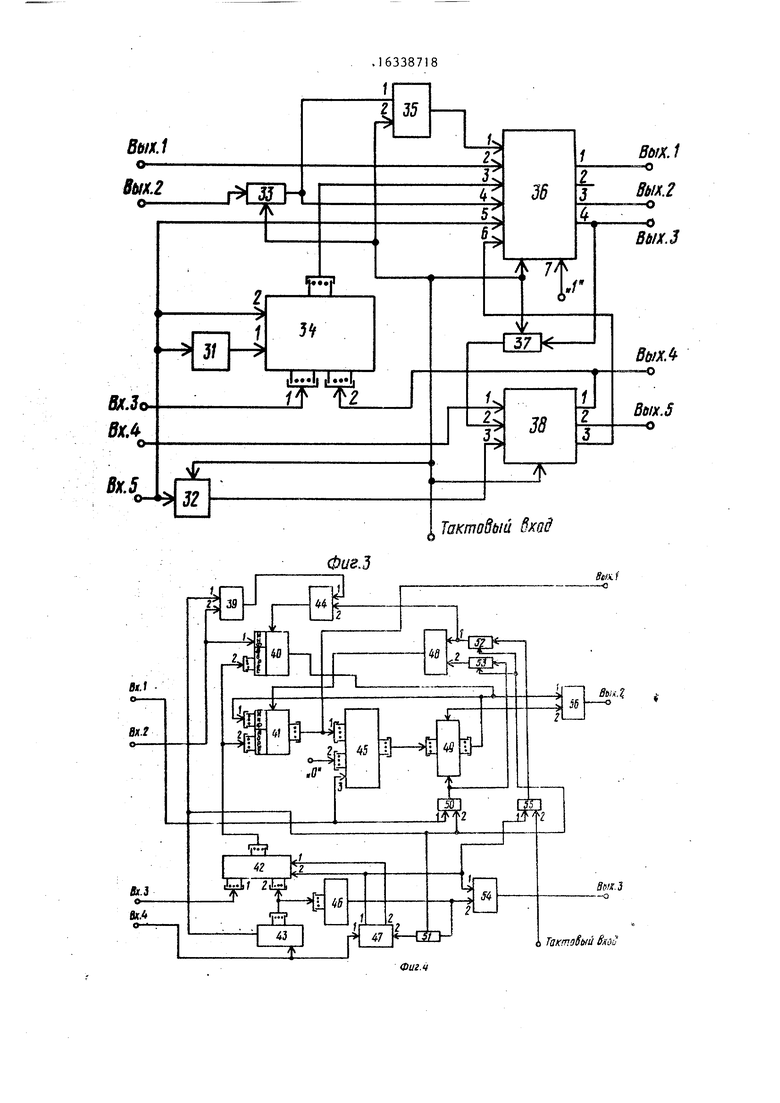

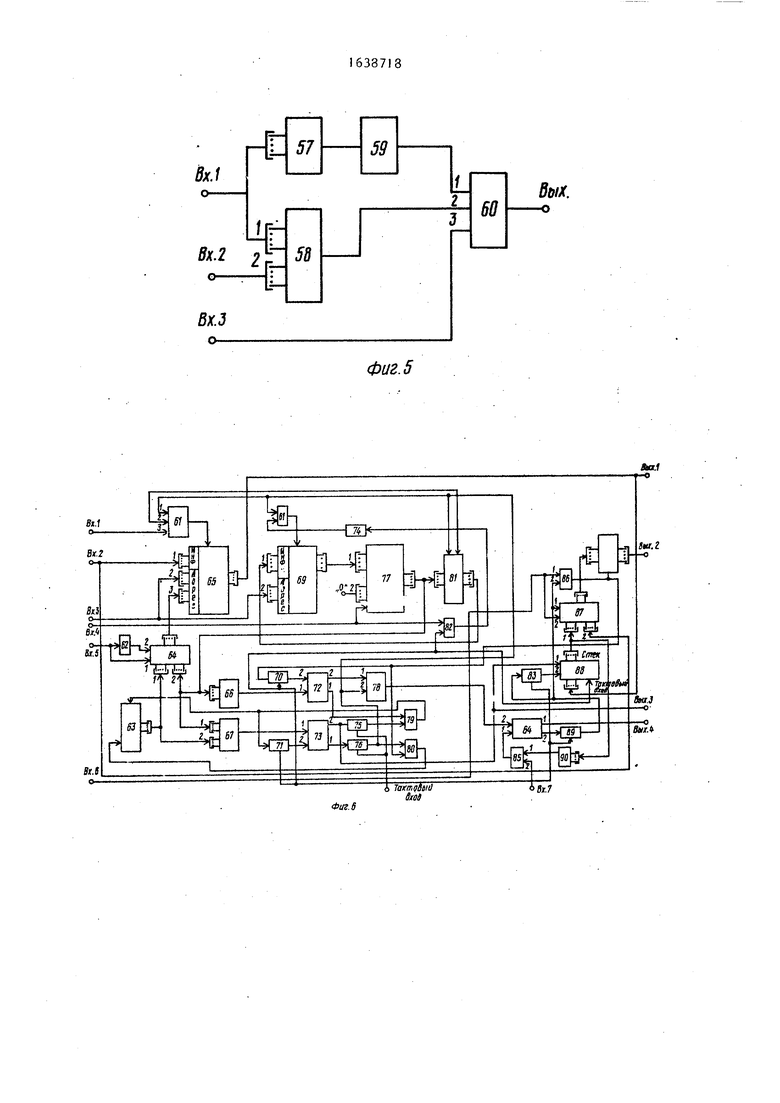

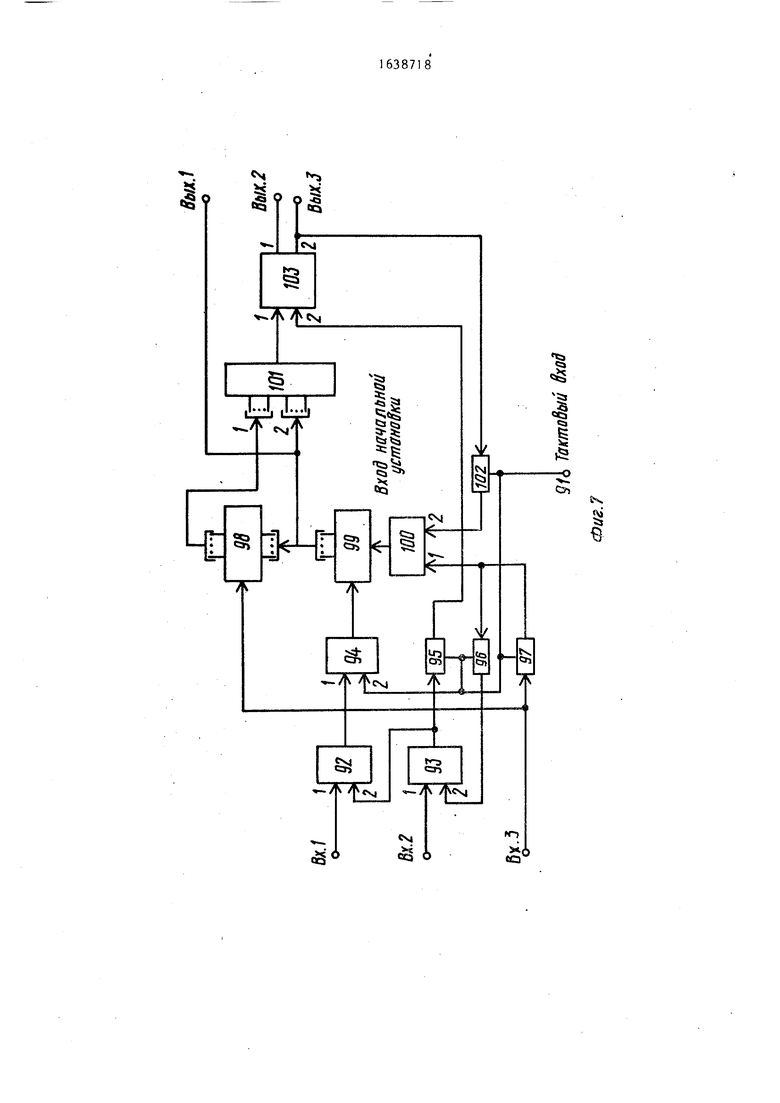

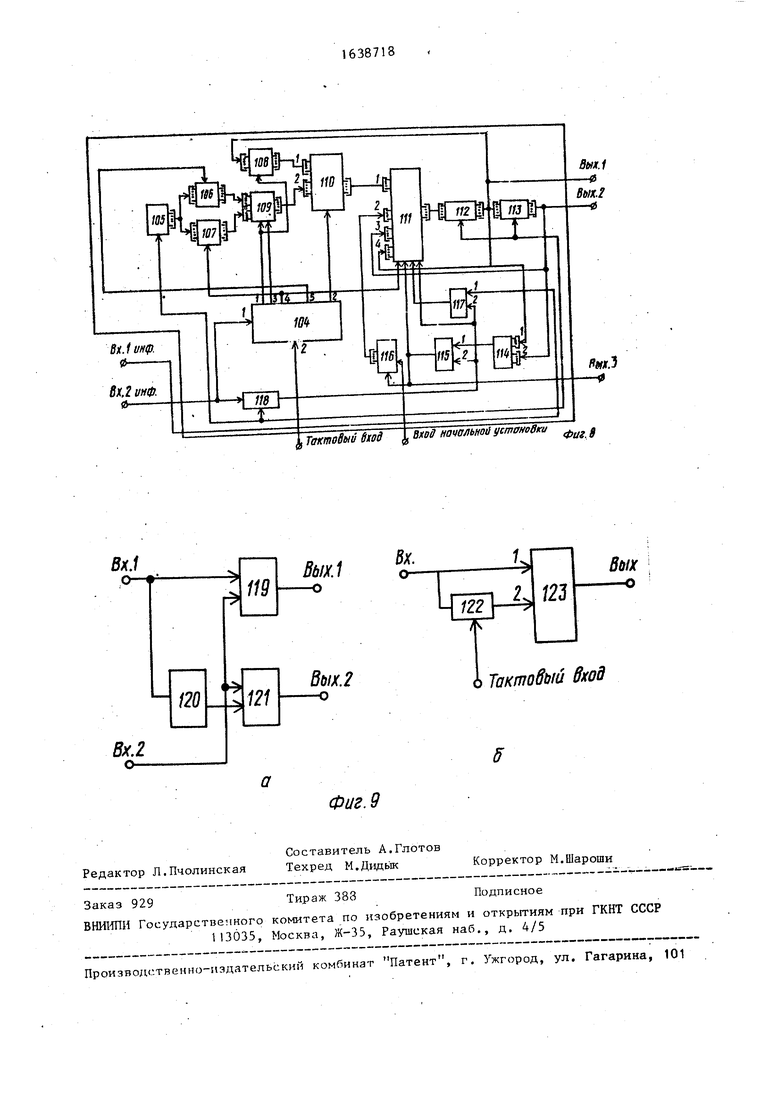

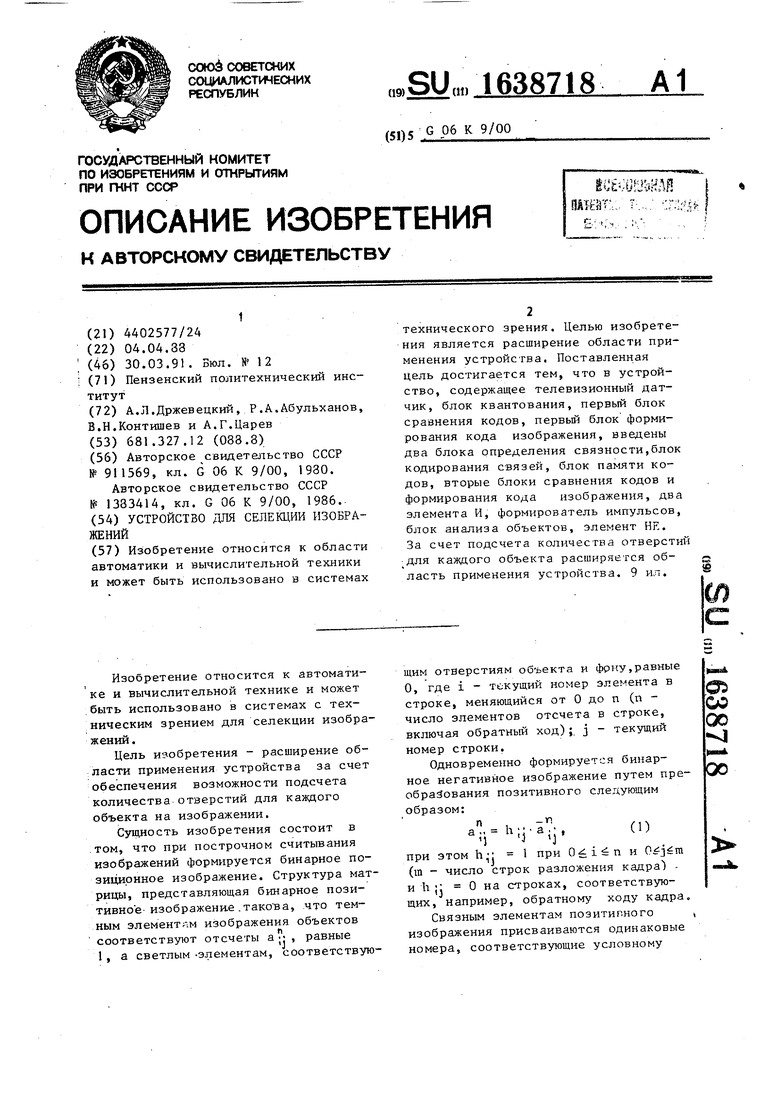

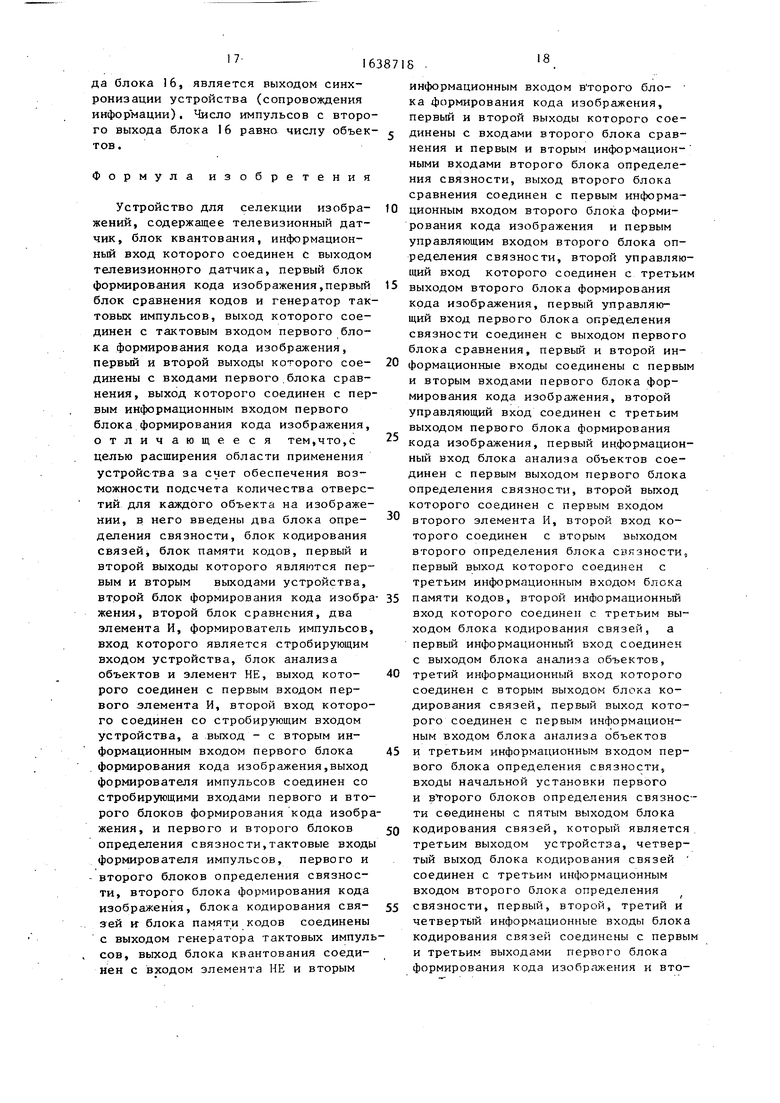

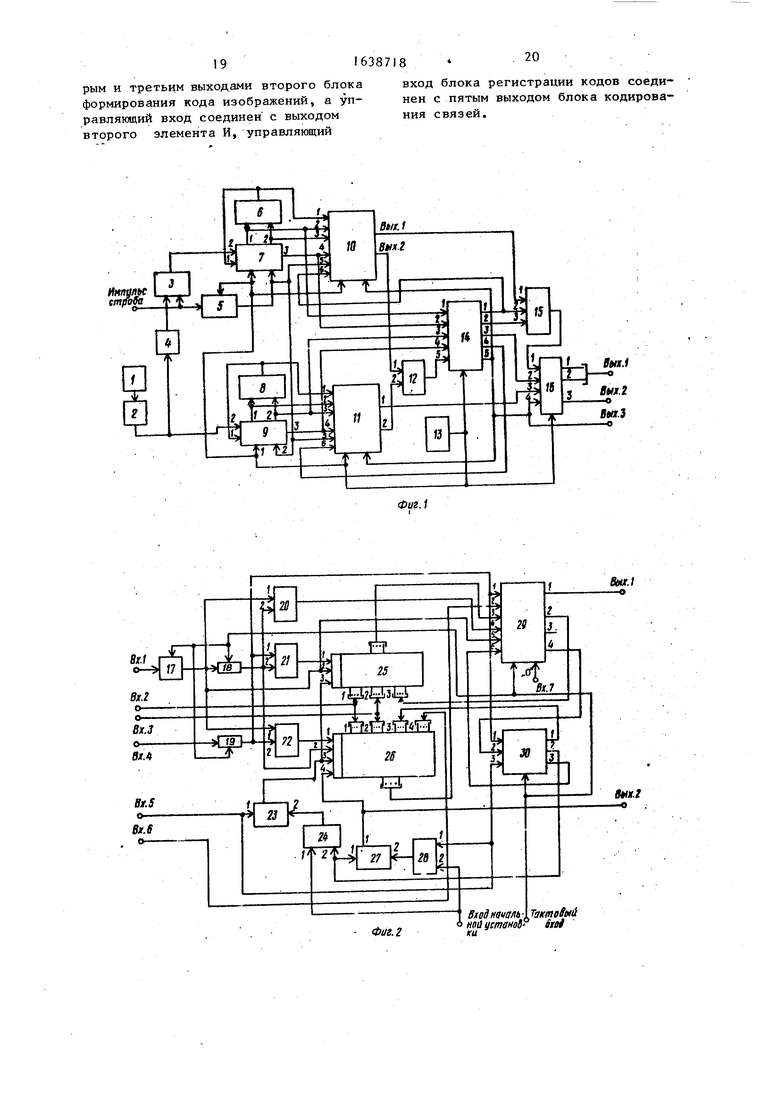

На фиг.1 представлена схема устроства; на фиг,2 - схема блока определения связности; на фиг. 3 - схема блока кодирования связей; на фиг.4 - схема блока регистрации кодов; на

фиг.5 - схема блока анализа объектов на фиг. 6 - структурная схема узла объединения кодов; на-фиг.7 - схема узла управления; на фиг. 8 - схема блока формирования кода изображения; на фиг. 9 - схемы дешифратора состояний (а) и формирователя импульсов (б).

Устройство для селекции изображений содержит телевизионный датчик 1, блок 2 квантования, первый элемент ИЗ, элемент НЕ 4, формирователь 5 импульсов, первый блок 6 сравнения, первый блок 7 формирова- ния. кода изображения, второй блок 8 сравнения, второй блок 9 формирования кода изображения, первый 10 и второй 11 блоки определения связности, второй элемент И 12, генератор 13 тактовых импульсов, блок 14 кодирования связей, блок 15 анализа объектов и блок 16 памяти кодов.

Блок определения связности образуют второй формирователь 17 импуль- са, первый 18 и второй 19 элементы задержки, первый 20, второй 21 и третий 22 элементы ИЛИ, первый триггер 23, четвертый элемент ИЛИ 24, первый 25 и второй 26 коммутаторы, второй триггер 27, пятый элемент ИЛИ 28, первый узел 29 объединения кодов и первый узел 30 управления.

Блок 14 кодирования связей состоит из первого элемента НЕ 31,третье- го формирователя 32 импульса,третьего элемента 33 задержки, третьего коммутатора 34, третьего элемента

5

71

г

0

5

35

45

55

0

50

86

И 35, второго узла 36 9бъединения кодов, четвертого элемента 37 задержки и второго узла 38 управления,

Блок 16 памяти кодов содержит четвертый элемент И 39, первый 40 и второй 41 блоки памяти (ОЗУ), четвертый коммутатор 42, первый счетчик 43, шестой элемент ИЛИ 44, сумматор 45, первый дешифратор 46, третий триггер 47, элемент ИЛИ 48, первый регистр 49, пятый элемент И 50, пятый 51, шестой 52 и седьмой 53 элементы задержки, а также шестой 54, седьмой 55 и восьмой 56 элементы И.

Блок 15 анализа объектов выполнен на втором дешифраторе 57, первой схеме 58 сравнения, втором элементе НЕ 59 и девятом элементе И 60.

Узел объединения кодов содержит седьмой элемент ИЛИ 61, третий элемент НЕ 62, второй счетчик 63,пятый коммутатор 64, третий блок 65 памяти (ОЗУ) ,восьмой элемент ИМ 66, вторую схему 67 сравнения, девятый элемент ИЛИ 63, четвертый блок 69 памяти (.ОЗУ), восьмой 70 и девятый 71 элементы задержки, третий 72 и четвертый 73 дешифраторы, десятый 74,одиннадцатый 75 и двенадцатый 76 элементы задержки, второй сумматор 77, десятый 78, одиннадцатый 79 и двенадцатый 80 элементы ИЛИ, второй регистр 31, десятый элемент И 82,тринадцатый элемент 83 задержки, пятый дешифратор 84, тринадцатью 85 и четырнадцатый 86 элементы ИЛИ, шестой коммутатор 87, пятый блок 88 памяти, четырнадцатый элемент 39 задержки и шестой дешифратор 90.

Узел управления образуют тактовый вход 91, пятнадцатыи 92 и Шестнадцатый 93 элементы ИЛИ, десятый элемент И 94, пятнадцатый 95, шестнадцатый 96 и семнадцатый 97 элементы задерж ки, третий регистр 98, третий счетчик 99, семнадцатый элемент ИЛИ 100, третью схему 101 сравнения,восемнадцатый элемент 102 задержки и шестой дешифратор 103.

Блок формирования кода изображения содержит третий узел 104 управления, четвертый счетчик 105,четвертый 106 и пятый 107 регистры,седьмой 108 и восьмой 109 коммутаторы, шестой блок 110 памяти,девятый коммутатор 111, первый 112 и второй 113 узлы задержки, седьмой дешифратор 114,

одиннадцатый элемент И 115, пятый счетчик 116, восьмой дешифратор П7 и девятнадцатый элемент 118.задержки.

Дешифратор состояний состоит из двенадцатого элемента И 119, четвертого элемента НЕ 120 и тринадцатого элемента И 121,

Формирователь импульса содержит двадцатый элемент 122 задержки и девятый дешифратор 123.

Устройство работает следующим образом.

С выхода генератора 13 тактовых

10

тора 34 - 1, что обеспечивает подключение выхода узла 113 задержки блока 9 формирования кода изображения к адресному входу старших разрядов ОЗУ 65 и адресному входу ОЗУ 69 блока 36 объединения кодов. Счетчик 99 узла 30 управления, входящего в блоки 10 и 11 ив блок 14 кодирования связей, также установлен в исход ное состояние, при котором на его выходе имеется нулевой код. Счетчики 63 узлов.29 и 36 объединения кода, входящих в блоки 10 и 11 ив

импульсов, частота которого выше час-15 блок 14 кодирования связей,устанав- тоты строчной развертки телевизионноливаются в исходное состояние,соответствующее нулевому коду на выходе счетчиков 63. Код счетчиков 116 блоков 7 и 9 формирования кода иэобраго датчика 1, тактовые импульсы поступают на входы блоков 7,9,10,11,14 и 16, на тактовые входы узла 104 управления, элемента 118 задержки,узлов 112 и 113 задержки, на вход адресного счетчика 105 блоков 7 и 9 фомирования кода изображения, на тактовые входы формирователя 17 импульса, элементов 18 и 19 задержки, узла 29 объединения кодов, узла 30 управления блоков 10 и 11, на тактовые

входы формирователя 32 импульса,элементов 33 и 37 задержки, узла 36 объединения кодов, узла 38 управления блока 14 кодирования связей, на тактовые входы элементов 51-53 задержки, на один из входов элементов И 39, 50 , на вход счетчика 43 блока 16 регистрации кодов, на тактовые входы элементов 70, 71, 64, 75, 76, 83 и 89 задержки, на блок 88 памяти, на один из входов элемента И 82 узлов 29 и 36 объединения кодов, на тактовые входы элементов 95, 96, 102 и 97 задержки и на один из входов элемента И 94 узлов 30 и 38 управления. Перед очередным циклом считывания изображения телевизионным датчиком 1 триггер 23 установлен в исходное состояние, при котором на его выходе имеется О, на третьих управляющих входах коммутаторов 25 и 26 - О, на первом управляющем входе коммутатора 64 - О, на втором - 1, что обеспечивает подключение выхода сумматора 77 через коммутатор 64 к адресному входу младших разрядов ОЗУ 65. Триггер 27, также установлен в исходное состояние, при котором на.его выходе, присутствует О, на четвертом управляющим входе коммутатора 26 - О, на первом управляющем входе коммута

тора 34 - 1, что обеспечивает подключение выхода узла 113 задержки блока 9 формирования кода изображения к адресному входу старших разрядов ОЗУ 65 и адресному входу ОЗУ 69 блока 36 объединения кодов. Счетчик 99 узла 30 управления, входящего в блоки 10 и 11 ив блок 14 кодирования связей, также установлен в исходное состояние, при котором на его выходе имеется нулевой код. Счетчики 63 узлов.29 и 36 объединения кода, входящих в блоки 10 и 11 ив

блок 14 кодирования связей,устанав-

ливаются в исходное состояние,соответствующее нулевому коду на выходе счетчиков 63. Код счетчиков 116 блоков 7 и 9 формирования кода иэображения является нулевым.

Во время считывания изображения телевизионным датчиком 1 видеосиг- нал с его выхода поступает на вход блока 2 квантования, в котором видеосигнал преобразуется в двухгра- дационный. С выхода блока 2 квантования двухградационный сигнал поступает на второй вход блока 9 формирования кода изображения и на вход элемента НЕ 4, с выхода которого проин- вертированный сигнал поступает на один из входов элемента И 3. При этом на входе устройства Импульс строба присутствует уровень 1, который разрешает прохождение инвертированного сигнала с выхода элемента НЕ 4 на второй вход блока 7 формирования кода изображения в соответствии с (1). При этом на первом выходе блока 9 формирования кода изображения формируются коды, имеющие одинаковые значения для связных элементов изображения в соответствии с (2). На втором выходе блока 9 коды также в соответствии с (2), но момент их появления относительно кодов на первом выходе задержан на (п-1) такт. Если коды на первом и втором выходах не нулевые и не равны,

то в соответствии с (3) на выходе блока 8 сравнения формируется уровень ,1, соответствующий области пересечения и удовлетворяющий (7), и поступает на первый вход блока 11. Коды

с первого выхода блока 9 формирования кода изображения через второй вход блока 11 поступают на первые входы коммутаторов 25 и 26. Коды с второго выхода блока 9 формирования

кода изображения через второй вход блока 11 поступают на вторые входы коммутаторов 25 и 26 и через третий вход блока 14 кодирования связей через коммутатор на адресный вход старших разрядов ОЗУ 65 и адресный вход ОЗУ 69 блока 36 объединения кодов.

Аналогично для негативного изображения на первом выходе блока 7 фор- мирования кода изображения формируются коды, имеющие одинаковые значения для связных элементов изображения в соответствии с (3), на втором выходе блока 7 - коды также в соот- ветствии с (3), но момент их появления относительно кодов на первом выходе задержан на (п-1) такт. Если коды на первом и втором выходах не нулевые и не равны, то в соответствии с (8) на выходе блока 6 сравнения формируется уровень 1, соответствующий области пересечения и удовлетворяющий (7), и поступает на первый вход блока 10. Коды с второго выхо- да блока 7 формирования кода изображения через третий вход блока 11 поступают на вторы е входы коммутаторов 25 и 26, коды с первого выхода блока 7 через второй вход блока 10 - на первые входы коммутаторов 25 и 26 и через первый вход блока 14 кодирования связей, второй вход блока 36 объединения кодов, на информационный вход ОЗУ 65.

.В момент появления первого элемента, входящего в состав очередного позитивного изображения, в соответствии с (9) и (10) на выходе блока 9 формирования кода изображения форми- руется импульс, равный одному элементу разложения в строке, и поступает через четвертый вход блока 11 с задержкой на один такт на элементе 19 задержки на первые входы узла 29 объединения кодов и узла 30 управления, а также через элементы ИЛИ 21 и 22 - на первые управляющие входы коммутаторов 25 и 26. При этом первые информационные входы коммутаторов 25 и 26 подключаются соответственно к выходам одноименных коммутаторов,задавая код информации на информационном входе ОЗУ 65, на адресном входе старших разрядов ОЗУ 65 и адресном входе. ОЗУ 69. Информация в ОЗУ 65 записывается по импульсу занесения первого элемента, поступающего с первого входа узла 29 объединения кода

8Ю

через элемент ИЛИ 61 на. вход записи. ОЗУ 65. При этом код адресного входа младших разрядов ОЗУ 65 является нулевым, а коды на информационном входе и адресном входе старших разрядов имеют одинаковое значение. По этому же импульсу занесения,поступающему через первый вход узла 30 управления, через элементы ИЛИ 92 и И 94, по тактовому импульсу в счетчик 99 заносится очередной импульс, увеличивая его код на единицу. Если существует область пересечений, в соответствии с (1) на выходе блока 8 сравнения кодов формируется уровень 1м, который через первый вход блока 11 поступает на вход формирователя 17 импульсов в соответствии с (11) и (12) соответственно для позитивного и негативного изображений, где происходит сравнение с тем же импульсом,задержанным на один такт элементом 122 задержки. При этом с выхода формирователя 17 импульс поступает на вход элемента 13 задержки, на второй управляющий вход коммутатора 25, на первый управляющий вход коммутатора 26 через элемент ИЛИ 22 и на четвертый вход узла 29 объединения кодов через элемент ИЛИ 20. Длительность импульса, снимаемого с выхода формг °вате- ля 17, равна длительности одного элемента разложения в строке. С выхода элемента 18 задержки имеющий задержку на один такт импульс поступает на второй управляющий вход коммутатора 26 и на первый управляющий вход коммутатора 25 через элемент ИЛИ 21, а также на четвертый вход узла 29 объединения кодов через элемент ИЛИ 20, при этом в момент появления импульса на выходе формирователя 17 код адресного входа младших разрядов ОЗУ 65 на единицу больше, чем код на выходе ОЗУ 69 за счет того, что на вход младшего разряда сумматора 77 с четвертого выхода узла 29 объединения кодов подается уровень 1, который поступает также на один из входов элемента И 82, в момент появления тактового импульса на другом его входе формируется сигнал,, по которому осуществляется запись кода с выхода сумматора 77 в регистр 81 и запись информации в ОЗУ 65 через элемент ИЛИ 61. С задержкой,несколько большей длительности тактово. 1116

го импульса, на элементе Ik задержки осуществляется запись кода с выхода регистра 81 информации в ОЗУ 69 по импульсу записи через элемент ИЛИ 68. В результате на первом такте относительно момента появления импульса, соответствующего области пересечений, в соответствии с (7) в ОЗУ 65 записывается код изображения по адресу, оп- ределяемому кодом изображения, с которым происходит пересечение, на втором такте адрес и информация меняются местами.

В конце считывания кадра изобра- жения в ОЗУ 65 для значений нулевых кодов в младших адресных разрядах записаны коды начальных элементов, а для значений с кодами, отличными от нулевых, записываются коды связей и их последовательная запись определяет локальный список связных областей

Код, записанный в ОЗУ 69 по соответствующему адресу, определяет число связей данной локальной области. Аналогичным образом в блоки 10, в ОЗУ 65 узла 29 объединения кодов,записываются коды для негативного изображения. По окончании считывания кадра на входе Импульс строба уст- ройства устанавливается уровень О, при этом на выходе формирователя 5 импульса возникает импульс длительностью в один такт, который устанавливает счетчик 116 блоков 7 и 9 фор- мирования кода изображения и через пятые входы блоков 10 и 11 триггер 23 в единичное состояние, подтверждает через элемент ИЛИ 28 исходное состояние триггера 27 и через третий вход узла 30 управления переписывает код счетчика 99 в регистр 98. Затем с задержкой на один такт на элементе 97 задержки устанавливает счетчик 99 через элемент ИЛИ 100 в исходное состояние, затем еще с задержкой на элементе 96 задержки на один такт через элементы ИЛИ 93 и 92 и элемент И 94 поступает на счетный вход счетчика 99. Тот же импульс с выхода элемента ИЛИ 93 задерживается на один такт на элементе 95 задержки и поступает на второй вход дешифратора 103 состояний на первом выходе которого появляется импульс только в том случае, если код на первом выходе схемы 101 сравнения меньше,чем на втором, а на втором выходе дешиф,ратора 103 состояний - в том случае,

12

ю

5 0

5 0 5 0

0

5

если это условие не выполняется. С момента устанояки триггера 23 в единичное состояние на третьих управляю) щих входах коммутаторов 25 и 26 также присутствует 1, что обеспечивает подключение через коммутатор 25 выхода регистра .81 через второй выход узла 29 объединения кодов к адресному входу старших разрядов ОЗУ 65 и адресному входу ОЗУ 69, а выхода счетчика 99 узла 30 управления - к информационному входу ОЗУ 65.

В момент появления импульса на втором выходе дешифратора 103 состояний, который через третий выход узла 30 управления и шестой вход узла 29 объединения кодов поступает на второй вход коммутатора 87,обеспечивая подключения информационного входа ОЗУ 65 к входу регистра 81 и запись этого кода через элемент ИЛИ 86 в регистр 81. С выхода элемента ИЛИ 86 данный импульс устанавливает счетчик 63 через элемент ИЛИ 80 в исходное состояние и с задержкой на один такт на элементе 70 задержки поступает на второй вход дешифратора 72 состояний. Если код на выходе ОЗУ 69 является нулевым, то на выходе элемента ИЛИ 66 присутствует О, при этом на втором выходе дешифратора 72 состояний появляется импульс, который через элемент ИЛИ 78 поступает на второй вход дешифратора 84 состояний. Если код на выходе блока памяти является нулевым, на выходе дешифратора 90 имеется 1 при этом на первом входе дешифратора 84 состояний присутствует . Следовательно, если при поступлении на вход 6 узла 29 коды с выходов ОЗУ 69 и блока 88 памяти являются нулевыми, то на четвертом выходе узла 29 объединения кодов появляется импульс с задержкой на один такт и поступает на второй вход узла 30 управления, устанавливая счетчик 99 в очередное состояние. Если код ОЗУ 69 отличается от нуля, то импульс появляется на первом выходе дешифратора 72 состояний и поступает на вход элемента 71 задержки, где задерживается на один такт, и на счетный вход счетчика 63, выход которого в этом режиме через коммутатор 64 подключен к адресному входу младших разрядов ОЗУ 65. Если код счетчика 63 меньше или равен коду ОЗУ 69, то в момент

появления импульса на втором входе дешифратора 73 состояний на втором выходе появляется импульс, который поступает на вход записи информации блока 88 памяти, при этом с выхода ОЗУ 65 код переписывается в блок 88. Тот же импульс задерживается на один такт на элементе 75 задержки и через элемент ИЛИ 79 поступает снова на счетный вход счетчика 63, увеличивая его. состояние на единицу.

Данный цикл повторяется до тех пор, пока код на выходе счетчика не станет меньшим или равным коду на выходе ОЗУ 69. Если это условие не выполняется, то появляется импульс на первом выходе дешифратора 73 состояний, который с задержкой на один такт на элементе 76 задержки посту- пает через элемент ИЛИ 80 на вход начальной установки счетчика 63, на вход начальной устанрвки регистра 81 устанавливая код на его выходе нулевым, и на входы записи ОЗУ 65 и 69. При этом в ОЗУ 69 записывается нулевой код с выхода регистра 81, а в ОЗУ 65 - код, определяемый кодом на выходе регистра 91. Импульс с выхода элемента 76 задержки также поступает через элемент ИЛИ 78 на второй вход дешифратора 84 состояний.

Если код на выходе стека не нулевой, то в момент появления импульса на втором входе дешифратора 84 состояний на его втором выходе появляется импульс, который с задержкой в один такт на элементе 39 задержки поступает на первый управляющий вход коммутатора 87 и на второй вход эле- мента ИЛИ 82, переписывая код с выхода блока 88 памяти в регистр 81, и с задержкой на один такт на элементе 83 задержки подается на вход сдвига информации, сдвигая ее поочеред- но на выход. Цикл записи информации в блок 88 и его выдача происходят до тех пор, пока код на выходе блока 88 не будет нулевым. В результате данного цикла в ОЗУ 65 по всем адре- сам, которые входят в связные области, записана информация, код которой определяется кодом с минимальным номером в рассматриваемой связной системе. Когда код счетчика 99 узла 30 управления больше кода на входе регистра 98, то на первом выходе дешифратора 103 формируется импульс, который через второй выход поступает на 5

0

5 0 5 0 5

вход установки в 1 триггера 27 и. на вход установки в О триггера 23 через элемент ИЛИ 24, и с задержкой на один такт на элементе 102 задержки поступает на вход начальной установки счетчика 99 через элемент ИЛИ 100. На выходе триггера 23 имеется О, а на выходе триггера 27 - 1, которая поступает на второй выход блоков 10 и 11, а также подключает шестой вход блоков 10 и 11 через четвертый информационный вход коммутатора 26 к второму входу узла 29 объединения кодов.

Поскольку позитивное и негативное изображения отличаются по структуре, по числу объектов, то для негативного изображения в блоке 10 всем кодам изображения, связанным с фоном изображения присваивается код первого объекта (000...1), а коды отверстий имеют коды больше единицы. При этом обработка информации по преобразованию кодов связности в блоках 10 и 11 занимает разное время, и в момент, когда оба блока завершат преобразование кодов позитивного и негативного изображений, на выходе элемента И 12 формируются уровни 1, поступающие на пятый вход узла 36 объединения кодов, подключая счетчик 63 через коммутатор 64 к младишь разрядам адресного входа ОЗУ 65. Коммутатор 34 в этом случае подключает вход счетчика 99 узла 38 управления к адресному входу старших разрядов ОЗУ 65 и адресному входу ОЗУ 69 через третий вход узла 36 объединения кодов.

В момент появления 1 на входе формирователя 32, возникае т импульс, поступающий через третий вход узла 33 управления.

Если код счетчика 99 меньше кода на выходе регистра 98 узла управления, который через шестой вход узла 36 объединения кодов поступает через элемент ИЛИ 86 и элемент 70 задержки на второй вход дешифратора 72 состояний. Так как на седьмом входе узла 36 объединения кодов установлена 1, то на первом выходе дешифратора 84 состояний, на четвертом выходе узла 36, обязательно появляется импульс. Если код на выходе ОЗУ 69 является нулевым, то на четвертом выходе узла 36 объединения кодов формируется импульс, который через третий

выход блока 14 кодирования, связей поступает через второй вход блока Ч 6 на информационный вход ОЗУ 40, в которое записывается 1 по тактовому импульсу через элемент И 39 и элемент ИЛИ 44 по адресу, который определяется кодом на третьем входе блока 16, так как в этом случае на первом выходе триггера - О, а на втором - 1. В этом случае код адреса ОЗУ 40 и 41 определяется кодом позитивного изображения с выхода ОЗУ 65 который входит в узел 29 объединения кодов блока 11.

Если код на выходе ОЗУ 69 не нулевой, то происходит последовательный перебор всех адресов младших разрядов ОЗУ 65, и для каждого нового адреса на третьем выходе узла 36 объе динения кодов формируется импульс, который через второй выход блока 14 кодирования связей поступает на третий вход блока 15 анализа, на первый вход которого поступает код номера негативного изображения с выхода ОЗУ 65 узла 29 объединения кодов через первый выход блока 10. При этом на второй вход блока 15 анализа и на шестой вход блока 10 поступает код с выхода ОЗУ 65 узла 36 объединения кодов блока 14 кодирования связей. На выходе элемента И 60 блока 15 формируется уровень 1 в том случае, если на третьем входе имеется 1, а коды на входе схемы 58 сравнения равны между собой. Код на -первом входе блока 15 не равен 000...1. Анализ этого кода производится дешифратором 57, выделяющим данную комбинацию, и элементом НЕ 59. Таким образом с выхода блока 15 анализа на вход элемента И 50 и младший разряд сумматора 45 через первый вход блока 16 регистрации кодов. При этом в момент поступления тактового импульса на выходе элемента И 50 фиксируется сигнал, по которому в регистр 49 заносится код с выхода сумматора 45 и с задержкой на элементе 53 задержки, несколько большей длительности тактового импульса, через элемент ИЛИ 48 записывает в него код с выхода регистра 49.

В результате в ОЗУ 41 по адресу, соответствующему наименьшему коду связных областей негативного изображения и не равных первому, номеру,

18

16

т.е. числу отверстий. В ОЗУ 40 записана 1 только для адресов,соответствующих наименьшему коду связных областей позитивного изображения.

После опроса всех кодов позитивного изображения с второго выхода узла 38 управления через пятый выход блока 14 кодирования связей формируется импульс, по которому триггеры 23 и 27 устанавливаются в исходное состояние через входы начальной установки блоков 10 и 11, триггер 47 - в единичное состояние, счетчик 43 - в нулевое через четвертый вход блока 16 регистрации кодов. Кроме того, данный импульс через третий выход всего устройства является сигналом, который позволяет производить считывание очередного кадра и используется как сигнал запроса для управления считывающим устройством. С установкой триггера 47 в единичное состояние выход счетчика 43 через коммутатор 42 подключается к адресным входам ОЗУ 40 и 41 и разрешает прохождение тактовых импульсов через элемент И 55, устанавливая нулевой код на выходе регистра 49 по входу начальной установки, и опрашивает состояние ОЗУ 40 с помощью элемента И 56.

При этом ОЗУ 40 и 41 устанавливаются в исходные (нулевые) состояния импульсом, задержанным на элементе 52 задержки на время, несколько боль- Щее длительности тактового импульса, через элементы ИЛИ 44 и 48. Так

как на счетный вход счетчика 43 поступают тактовые импульсы, то коды адреса ОЗУ 40 и 41 последовательно модернизируются. На выходе дешифратора 46, формируется 1 в том случае, если код на его входе 111...1. При этом на выходе элемента И 54 формируется сигнал, свидетельствующий, что вся информация из ОЗУ 40 и 41 выдана, и являющийся сигналом для начала решения задач устройствами, подключаемыми к первому выходу. Триггер 47 с задержкой на один такт на элементе 51 задержки устанавливается в исходное состояние. Код, соответствующий числу отверстий объектов, с выхода ОЗУ 41 через четвертый выход блока 16 регистрации кодов является информационной шиной устройства, а сигнал с выхода элемента И 56, поступающий с второго выхо17163

да блока 16, является выходом синхронизации устройства (сопровождения информации), Число импульсов с второго выхода блока 16 равно числу объек- тов.

Формула изобретения

Устройство для селекции изобра- жений, содержащее телевизионный датчик, блок квантования, информационный вход которого соединен с выходом телевизионного датчика, первый блок формирования кода изображения,первый блок сравнения кодов и генератор тактовых импульсов, выход которого соединен с тактовым входом первого блока формирования кода изображения, первый и второй выходы которого сое- динены с входами первого блока сравнения, выход которого соединен с первым информационным входом первого блока формирования кода изображения,

отличающееся тем,что,с

целью расширения области применения устройства за счет обеспечения возможности подсчета количества отверстий для каждого объекта на изображении, в него введены два блока опре- деления связности, блок кодирования связей, блок памяти кодов, первый и второй выходы которого являются первым и вторым выходами устройства, второй блок формирования кода изобра жения, второй блок сравнения, два элемента И, формирователь импульсов, вход которого является стробирующим входом устройства, блок анализа объектов и элемент НЕ, выход кото- рого соединен с первым входом первого элемента И, второй вход которого соединен со стробирующим входом устройства, а выход - с вторым информационным входом первого блока формирования кода изображения,выход формирователя импульсов соединен со стробирующими входами первого и второго блоков формирования кода изображения, и первого и второго блоков определения связности,тактовые входы формирователя импульсов, первого и второго блоков определения связности, второго блока формирования кода изображения, блока кодирования свя- зей и блока памяти кодов соединены с выходом генератора тактовых импульсов, выход блока квантования соединен с входом элемента НЕ и вторым

1;

0

5

5 0 5 0 5

информационным входом в торого блока формирования кода изображения, первый и второй выходы которого соединены с входами второго блока сравнения и первым и вторым информационными входами второго блока определения связности, выход второго блока сравнения соединен с первым информационным входом второго блока формирования кода изображения и первым управляющим входом второго блока определения связности, второй управляющий вход которого соединен с третьим выходом второго блока формирования кода изображения, первый управляющий вход первого блока определения связности соединен с выходом первого блока сравнения, первый и второй информационные входы соединены с первым и вторым входами первого блока формирования кода изображения, второй управляющий вход соединен с третьим выходом первого блока формирования кода изображения, первый информационный вход блока анализа объектов соединен с первым выходом первого блока определения связности, второй выход которого соединен с первым входом второго элемента И, второй вход которого соединен с вторым выходом второго определения блока связности, первый выход которого соединен с третьим информационным входом блока памяти кодов, второй информационный вход которого соединен с третьим выходом блока кодирования связей, а первый информационный вход соединен с выходом блока анализа объектов, третий информационный вход которого соединен с вторым выходом блока кодирования связей, первый выход которого соединен с первым информационным входом блока анализа объектов и третьим информационным входом первого блока определения связности, входы начальной установки первого и в торого блоков определения связности соединены с пятым выходом блока кодирования связей, который является третьим выходом устройства, четвертый выход блока кодирования связей соединен с третьим информационным входом второго блока определения связности, первый, второй, третий и четвертый информационные входы блока кодирования связей соединены с первым и третьим выходами первого блока формирования кода изображения и вторым и третьим выходами второго блока формирования кода изображений, а управляющий вход соединен с выходом второго элемента И, управляющий

вход блока регистрации кодов соединен с пятым выходом блока кодирования связей.

Фаг. г

тактовый ноа дстаноИ Sal

Bwx.1

о-

ВШ.2 о--

НОГИ

1

2

J/

f

И.

3V

ш.

ЙГ.4

0JT.J

±

32

Фие.З

4

36

/

J

Вых. 1

o

Л/Ж./ -о

/JT.J

л

f. ВыхА

-о

Jr

38

Вш.5 -о

ТактоШ дкоё

TsKmnStriii ими

Фиг S

Фиг. 5

Тактобыи бход начальной установки фцг 9

Вых.2

Фиг. 9

Составитель А.Глотов Редактор Л.Пчопинская Техред М.Дидык Корректор М.Шароши

Заказ 929

Тираж 383

ВНИИПИ Государствечного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Электрофильтр для очистки газов от пыли | 1985 |

|

SU1333414A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-03-30—Публикация

1988-04-04—Подача