Изобретение относится к техник связи и может использоваться при построении квадратурного типа передатчиков сигналов минимальной частотной манипуляции с предмодуляционной . фильтрацией.

Целью изобретения является повышение точности формирования квадратурных сигналов путем снижения уровня шумов квантования при одновременном уменьшении объема залиси постоянных запоминающих устройств.

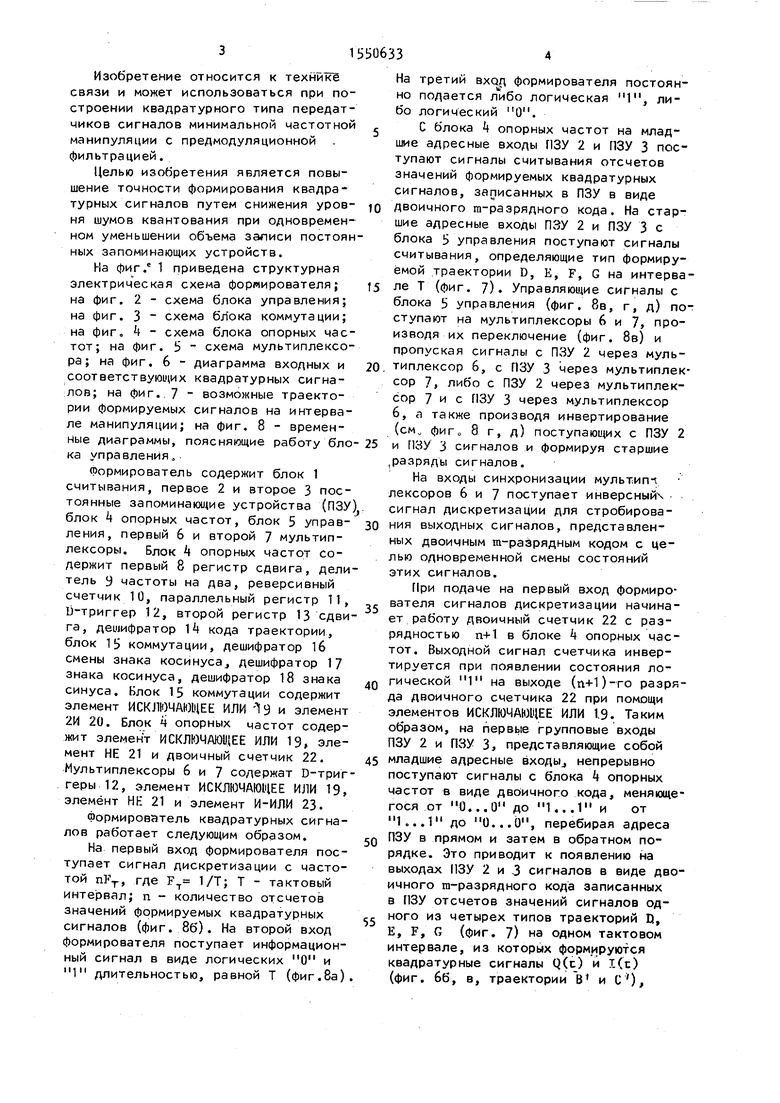

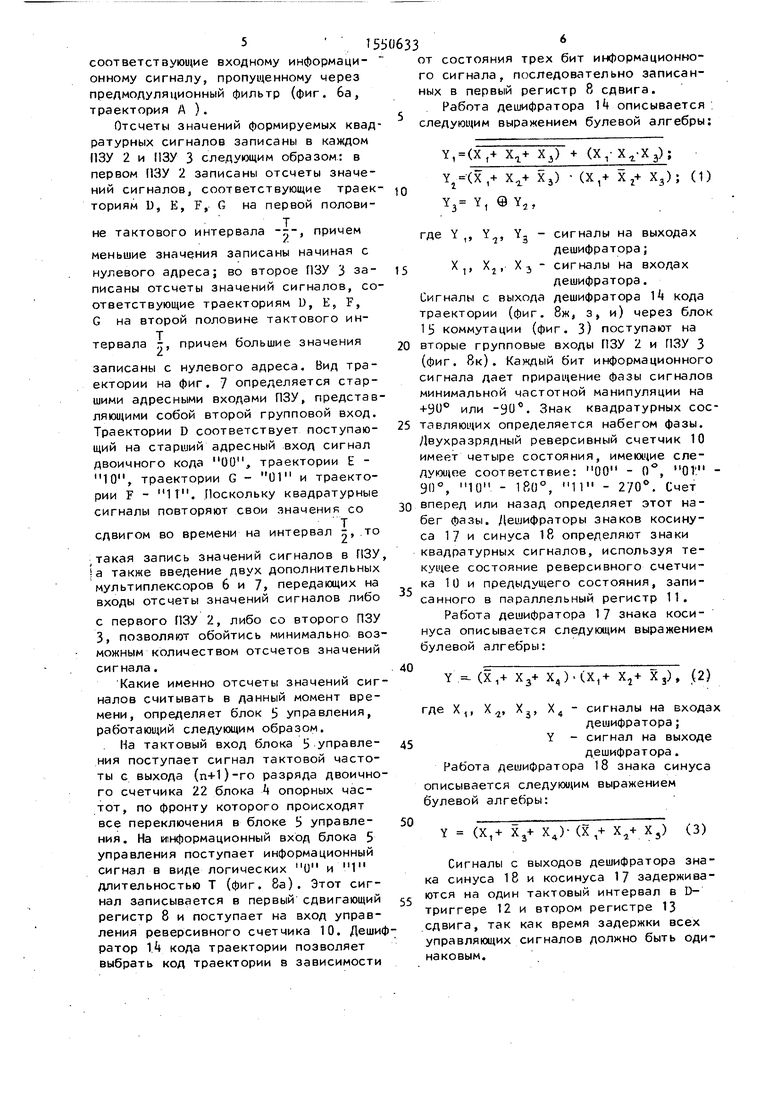

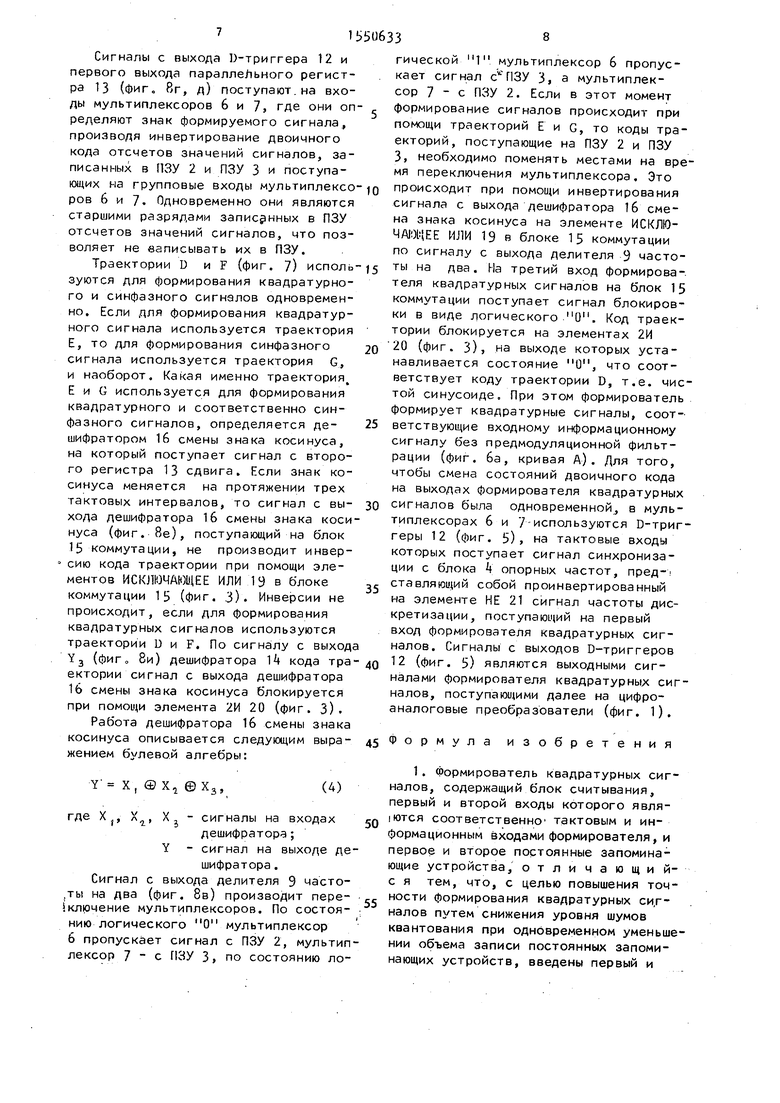

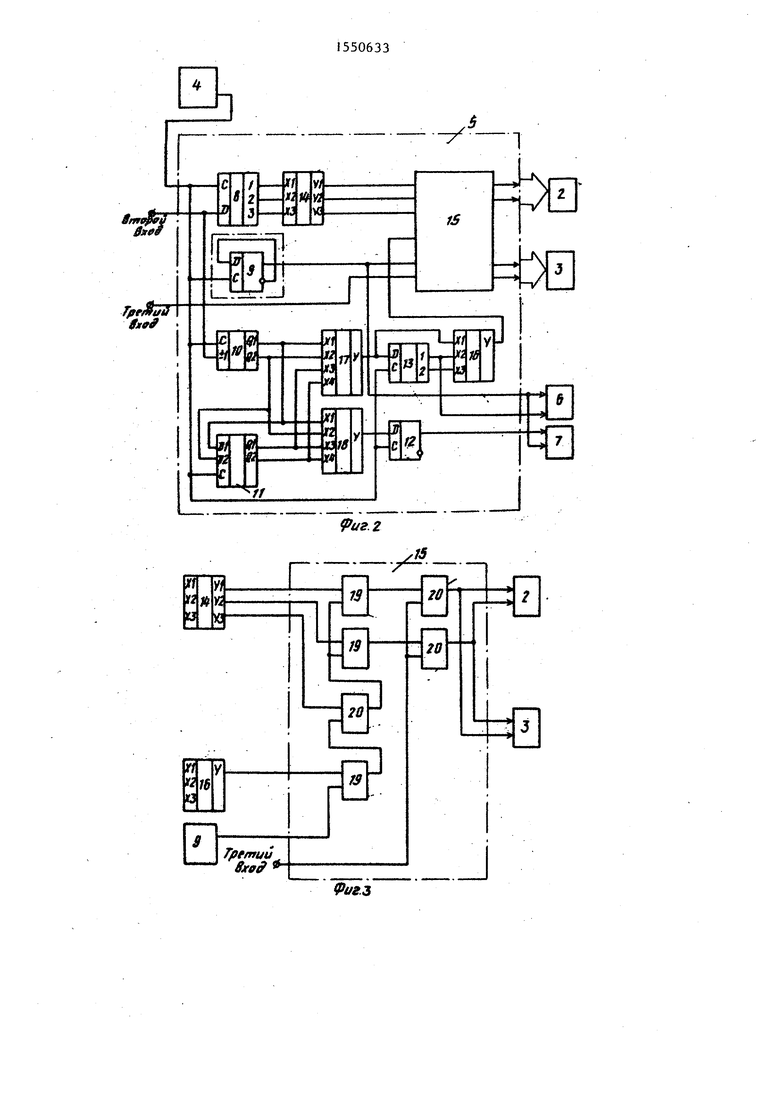

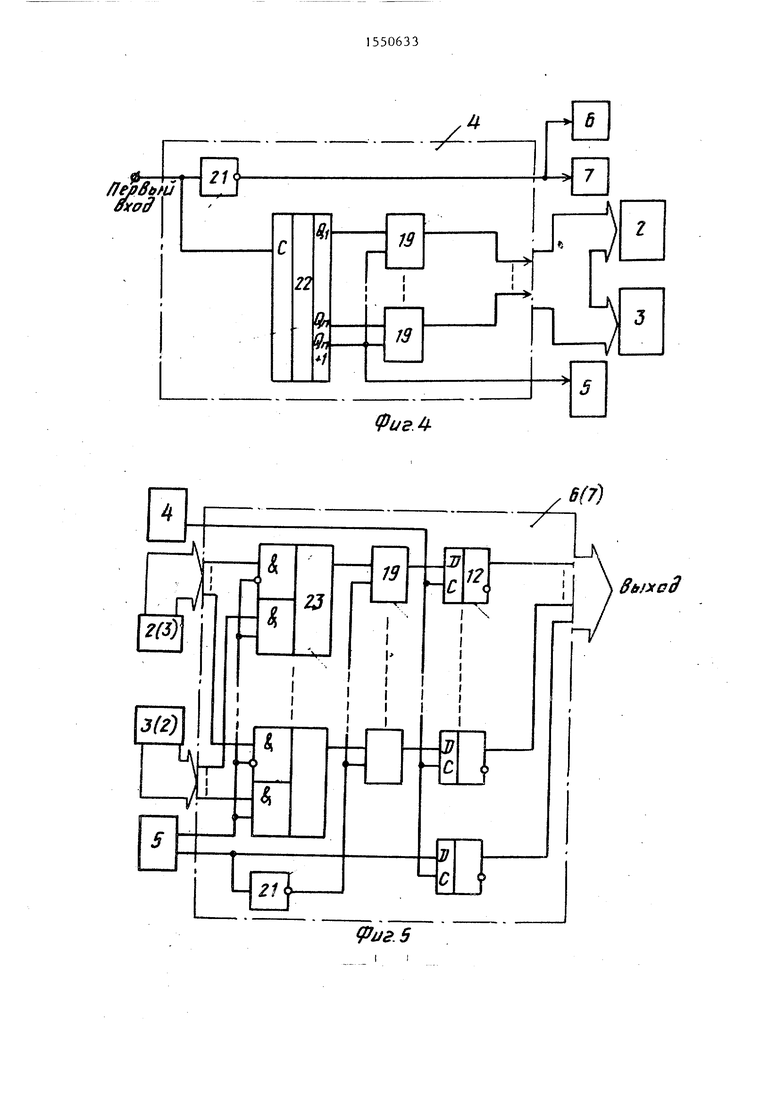

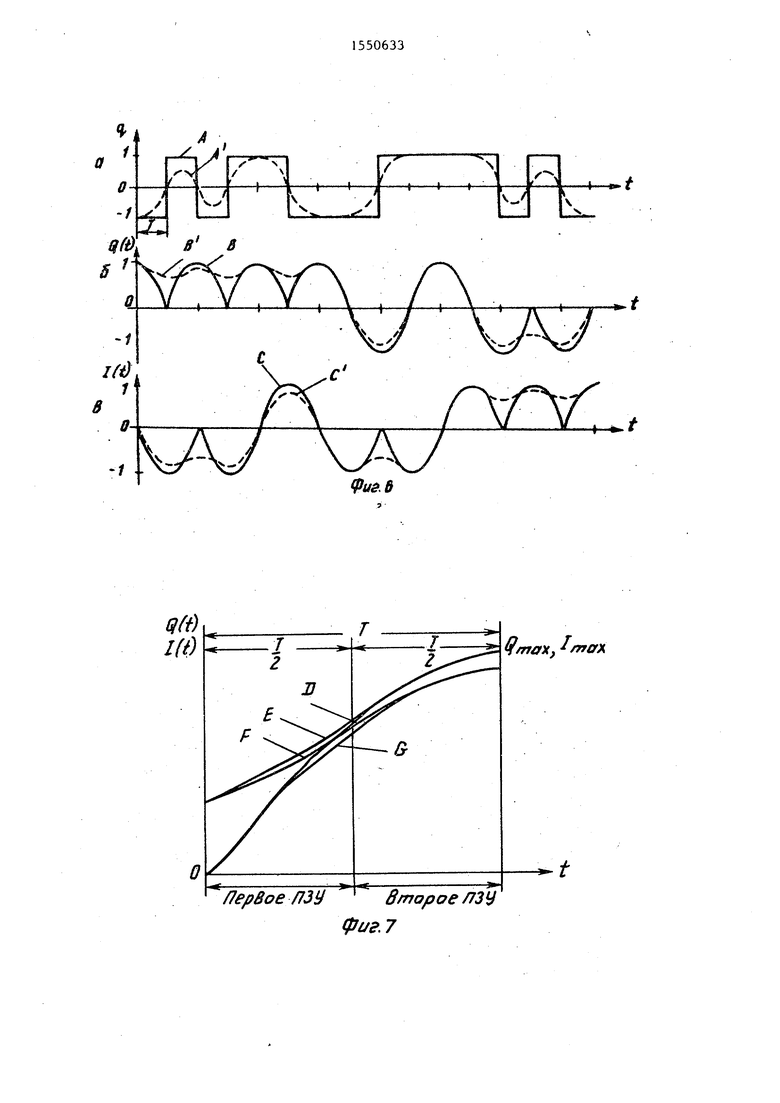

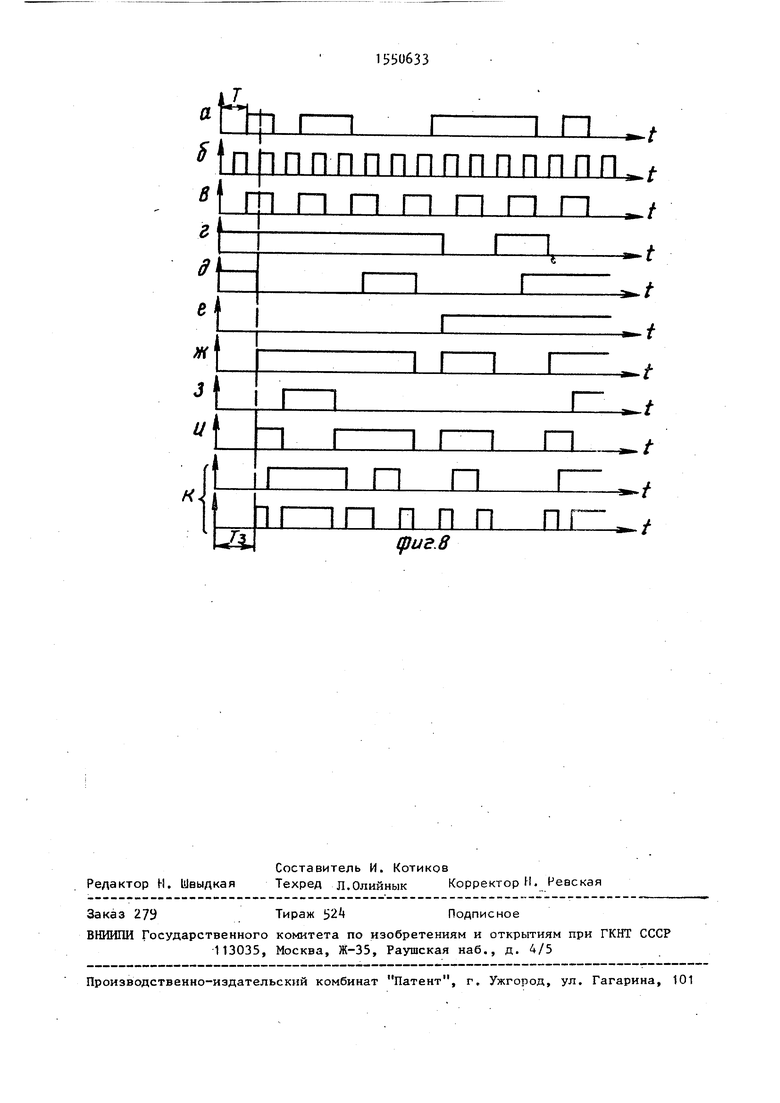

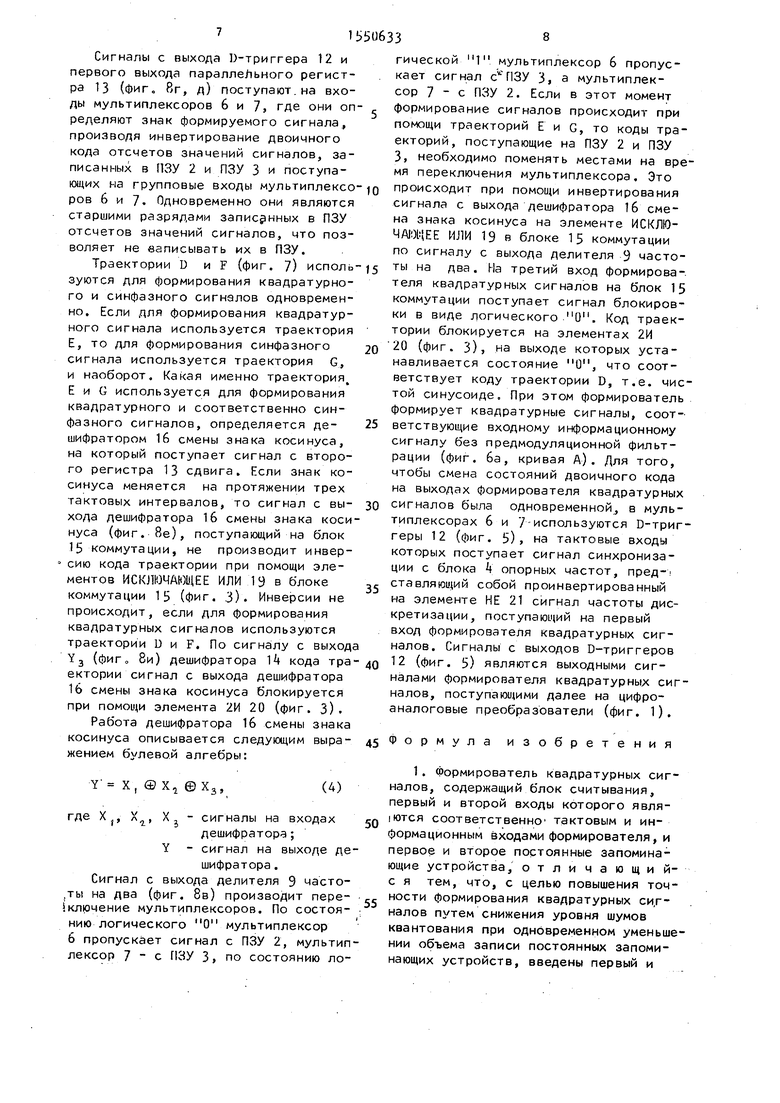

На фиг.е 1 приведена структурная электрическая схема формирователя; на фиг. 2 - схема блока управления; на фиг. 3 схема бЛока коммутации; на фиг, k - схема блока опорных частот; на фиг. 5 - схема мультиплексора; на фиг. 6 - диаграмма входных и соответствующих квадратурных сигналов; на фиг. 7 возможные траектории формируемых сигналов на интервале манипуляции; на фиг. 8 - временные диаграммы, поясняющие работу блока управления

Формирователь содержит блок 1 считывания, первое 2 и второе 3 постоянные запоминающие устройства (ПЗУ блок k опорных частот, блок 5 управления, первый 6 и второй 7 мультиплексоры. Блок опорных частот содержит первый 8 регистр сдвига, делитель 9 частоты на два, реверсивный счетчик 10, параллельный регистр 11, U-триггер 12, второй регистр 13 сдвига, дешифратор 14 кода траектории, блок 1 $ коммутации, дешифратор 16 смены знака косинусал дешифратор 17 знака косинуса, дешифратор 18 знака синуса. Блок 15 коммутации содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ Ч 9 и элемент 2И 20. Блок ч опорных частот содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 19, элемент НЕ 21 и двоичный счетчик 22. Мультиплексоры 6 и 7 содержат D-триг геры 12, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 19, элемент НЕ 21 и элемент И-ИЛИ 23.

оормирователь квадратурных сигналов работает следующим образом.

На первый вход формирователя поступает сигнал дискретизации с частотой nFT, где FT 1/T; Т - тактовый интервал; п - количество отсчетов значений формируемых квадратурных сигналов (фиг. 86). На второй вход формирователя поступает информационный сигнал в виде логических О и 1 длительностью, равной Т (фиг.ба)

0

5

0

5

0

5

0

5

0

5

На третий вход формирователя постоянно подается либо логическая 1, либо логический О.

С блока k опорных частот на младшие адресные входы ПЗУ 2 и ПЗУ 3 поступают сигналы считывания отсчетов значений формируемых квадратурных сигналов, записанных в ПЗУ в виде двоичного m-раэрядного кода. На старшие адресные входы ПЗУ 2 и ПЗУ 3 с блока i управления поступают сигналы считывания, определяющие тип формируемой траектории D, Е, F, G на интервале Т (фиг. 7). Управляющие сигналы с блока 5 управления (фиг. 8в, г, д) поступают на мультиплексоры 6 и 7, производя их переключение (фиг. 8в) и пропуская сигналы с ПЗУ 2 через мультиплексор 6, с ПЗУ 3 через мультиплексор 7} либо с ПЗУ 2 через мультиплексор 7 и с ПЗУ 3 через мультиплексор 6, а также производя инвертирование (см„ фиг 8 г, д) поступающих с ПЗУ 2 и ПЗУ 3 сигналов и формируя старшие ,разряды сигналов.

На входы синхронизации мультипп лексоров 6 и 7 поступает инверсныйх сигнал дискретизации для стробирова- ния выходных сигналов, представленных двоичным m-разрядным кодом с целью одновременной смены состояний этих сигналов.

При подаче на первый вход формирователя сигналов дискретизации начинает работу двоичный счетчик 22 с разрядностью п+1 в блоке k опорных частот. Выходной сигнал счетчика инвертируется при появлении состояния логической 1 на выходе (п+1)-го разряда двоичного счетчика 22 при помощи элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 19. Таким образом, на первые групповые входы ПЗУ 2 и ПЗУ 3, представляющие собой младшие адресные входы непрерывно поступают сигналы с блока 4 опорных частот в виде двоичного кода, меняющегося от 0...0 до 1...1 и от 1...1 до 0...0, перебирая адреса ПЗУ в прямом и затем в обратном порядке. Это приводит к появлению на выходах ПЗУ 2 и 3 сигналов в виде двоичного m-разрядного кода записанных в ПЗУ отсчетов значений сигналов одного из четырех типов траекторий D, Е, F, G (фиг. 7) на одном тактовом интервале, из которых формируются квадратурные сигналы Q(c) и I(t) (фиг. 6б, в, траектории В1 и С )

соответствующие входному информаци- онному сигналу, пропущенному через предмодуляционный фильтр (фиг. 6а, траектория А ).

Отсчеты значений формируемых квадратурных сигналов записаны в каждом ПЗУ 2 и ПЗУ 3 следующим образом: в первом ПЗУ 2 записаны отсчеты значений сигналов, соответствующие траекториям D, Е, F, G на первой половине тактового интервала п, причем меньшие значения записаны начиная с нулевого адреса; во второе ПЗУ 3 записаны отсчеты значений сигналов, соответствующие траекториям D, Es F, G на второй половине тактового интервала - причем большие значения

записаны с нулевого адреса. Вид траектории на фиг. 7 определяется старшими адресными входами ПЗУ, представляющими собой второй групповой вход. Траектории D соответствует поступающий на старший адресный вход сигнал двоичного кода 00, траектории Е - 10, траектории G - 01 и траектории F - 1Т. Поскольку квадратурные сигналы повторяют свои значения со

Т 2

такая запись значений сигналов в ПЗУ а также введение двух дополнительных мультиплексоров 6 и 7, передающих на входы отсчеты значений сигналов либо

с первого ПЗУ 2, либо со второго ПЗУ 3, позволяют обойтись минимально возможным количеством отсчетов значений сигнала.

Какие именно отсчеты значений сигналов считывать в данный момент времени, определяет блок 5 управления, работающий следующим образом.

На тактовый вход блока $ управления поступает сигнал тактовой частоты с выхода (п-И)-го разряда двоичного счетчика 22 блока Ц опорных частот, по фронту которого происходят все переключения в блоке 5 управления. На информационный вход блока 5 управления поступает информационный сигнал в виде логических О и 1 длительностью Т (фиг. 8а). Этот сигнал записывается в первый сдвигающий регистр 8 и поступает на вход управления реверсивного счетчика 10. Дешифратор 1 кода траектории позволяет выбрать код траектории в зависимости

от состояния трех бит информационного сигнала, последовательно записанных в первый регистр 8 сдвига.

Работа дешифратора 1 описывается следующим выражением булевой алгебры:

Y,(X,+

Y

Y3

хг+

Х3) + (Хп Хг-Х3);

(1)

Y, @ Y

2

5

0

0

5

где Y

Y3 1

1

сигналы на выходах дешифратора; сигналы на входах дешифратора.

Сигналы с выхода дешифратора 1 кода траектории (фиг. 8ж, з, и) через блок 15 коммутации (фиг. 3) поступают на вторые групповые входы ПЗУ 2 и ПЗУ 3 (фиг. 8к). Каждый бит информационного сигнала дает приращение фазы сигналов минимальной частотной манипуляции на +9U0 или -4.0°. Знак квадратурных сос- 5 товляющих определяется набегом фазы. Двухразрядный реверсивный счетчик 10 имеет четыре состояния, имеющие следующее соответствие: 00 - 0°, 01 90°, 10 - 180°, 11 - 270°. Счет вперед или назад определяет этот набег Фазы. Дешифраторы знаков косинуса 1 7 и синуса 18 опрелеляют знаки квадратурных сигналов, используя текущее состояние реверсивного счетчика 1 0 и предыдущего состояния, записанного в параллельный регистр 11.

Работа дешифратора 17 знака косинуса описывается следующим выражением булевой алгебры:

it 5

0

Y (Х,+ где X,, X

Х3+ Х4)ЧХ,+ Х2+ Х3), (2)

2

V3

4 сигналы на входах дешифратора; Y - сигнал на выходе

дешифратора. Работа дешифратора 18 знака синуса

описывается следующим выражением булевой алгебры:

Y (X,хз+

х4)-(х1+

Х4+ Х3)

(3)

Сигналы с выходов дешифратора знака синуса 18 и косинуса 17 задерживаются на один тактовый интервал в D- триггере 12 и втором регистре 13 сдвига, так как время задержки всех управляющих сигналов должно быть одинаковым.

7

Сигналы с выхода 1)-триггера 12 и первого выхода параллельного регистра 13 (фиг „ 8г, д) поступают, на входы мультиплексоров 6 и 7Э где они оп- ределяют знак формируемого сигнала, производя инвертирование двоичного кода отсчетов значений сигналов, записанных в ПЗУ 2 и ПЗУ 3 и поступающих на групповые входы мультиплексоров 6 и 7. Одновременно они являются старшими разрядами записанных в ПЗУ отсчетов значений сигналов, что позволяет не ваписывать их в ПЗУ.

15

Траектории D и F (фиг. 7) исполо- з ты на Лва а третий вход формирователя квадратурных сигналов на блок 15 коммутации поступает сигнал блокировки в виде логического О. Код траектории блокируется на элементах 2И

20 20 (фиг. 3), на выходе которых устанавливается состояние О, что соответствует коду траектории D, т.е. чистой синусоиде. При этом формирователь формирует квадратурные сигналы, соот25 ветствующие входному информационному сигналу без предмодуляционной фильтрации (фиг. 6а, кривая А). Для того, чтобы смена состояний двоичного кода на выходах формирователя квадратурных

30 сигналов была одновременной, в мультиплексорах 6 и 7-используются D-триг- геры 12 (фиг. 5), на тактовые входы которых поступает сигнал синхронизации с блока k опорных частот, пред,с ставляющий собой проинвертированный на элементе НЕ 21 сигнал частоты дискретизации, поступающий на первый вход формирователя квадратурных сигналов. Сигналы с выходов D-триггеров

(фиг. 5) являются выходными сигналами формирователя квадратурных сигналов, поступающими далее на цифро- аналоговые преобразователи (фиг. 1).

зуются для формирования квадратурного и синфазного сигналов одновременно. Если для формирования квадратурного сигнала используется траектория Е, то для формирования синфазного сигнала используется траектория G, и наоборот. Какая именно траектория, Е и С используется для формирования квадратурного и соответственно синфазного сигналов, определяется дешифратором 16 смены знака косинуса, на который поступает сигнал с второго регистра 13 сдвига. Если знак косинуса меняется на протяжении трех тактовых интервалов, то сигнал с выхода дешифратора 16 смены знака косинуса (фиг. 8е), поступающий на блок 15 коммутации, не производит инвер- сию кода траектории при помощи элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 19 в блоке коммутации 15 (фиг. 3). Инверсии не происходит, если для формирования квадратурных сигналов используются траектории U и F. По сигналу с выхода

Y3 (фиг, 8и) дешифратора 14 кода тра- до ектории сигнал с выхода дешифратора 16 смены знака косинуса блокируется при помощи элемента 2И 20 (фиг. 3) .

Работа дешифратора 16 смены знака косинуса описывается следующим выражением булевой алгебры:

45 Формула изобретения

т х, ® х, ех3,

(4)

где X., X,

- сигналы на входах

дешифратора; Y - сигнал на выходе дешифратора .

Сигнал с выхода делителя 9 часто- ,ты на два (фиг. 8в) производит пере- ключение мультиплексоров. По состоянию логического О мультиплексор 6 пропускает сигнал с ПЗУ 2, мультиплексор 7 с ПЗУ 3, по состоянию ло,. JQ506338

гической 1 мультиплексор 6 пропускает сигнал 3, а мультиплексор 7 с ПЗУ 2. Если в этот момент- формирование сигналов происходит при помощи траекторий Е и с, то коды траекторий, поступающие на ПЗУ 2 и ПЗУ 3, необходимо поменять местами на время переключения мультиплексора. Это происходит при помощи инвертирования сигнала с выхода дешифратора 16 смена знака косинуса на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 19 в блоке 15 коммутации по сигналу с выхода делителя 9 часто45 Формула изобретения

0

5

1. Формирователь квадратурных CHI- налов, содержащий блок считывания, первый и второй входы которого является соответственно1 тактовым и информационным входами формирователя, и первое и второе постоянные запоминающие устройства, отличающий- с я тем, что, с целью повышения точности формирования квадратурных си.г- налов путем снижения уровня шумов квантования при одновременном уменьшении объема записи постоянных запоминающих устройств, введены первый и

второй мультиплексоры, выходы которых являются выходами формирователя, а блок считывания содержит последова- тельно соединенные блок опорных частот и блок управления, третий вход блока считывания является входом управления формирователем, первый и второй выходы устройства считывания соединены соответственно с первым и вторым входами первого и второго мультиплексоров, третий и четвертый выходы устройства считывания подключены к третьему входу соответственно первого и второго мультиплексоров,

первая группа выходов устройства считывания соединена с первыми группами входов первого и второго постоянных запоминающих устройств, вторая и третья группы выходов устройства считыва- ния подключены к второй группе входов соответственно первого и второго постоянных запоминающих устройств, выходы которых соединены с первыми и вторыми группами входов первого и второ- го мультиплексоров, первый, второй и третий входы устройства считывания являются соответственно входом блока опорных частот, вторым и третьим входами блока управления, первый, вто- рой, третий и четвертый выходы устройства считывания являются соответственно вторым выходом блока опорных частот, первым, вторым и третьим выхода, ми блока управления ,а первая,вторая и третья группы выходов устройства считывания являются соответственно группой выходов блока опорных частот первой и второй группой выходов блока управления.

2. Формирователь по п. 1, отличающийся тем, что блок управления содержит последовательно соединенные первый регистр сдвига, дешифQs

0 5 0

5

0

ратор кода траектории и блок коммутации, делитель частоты на два, последовательно соединенные реверсивный счетчик, дешифратор знака косинуса, второй регистр сдвига и дешифратор смены знака косинуса и последовательно соединенные параллельный регистр, дешифратор знака синуса и D- триггер, выход которого является третьим выходом блока управления, тактовый вход первого регистра сдвига соединен с входом делителя частоты на два, с тактовыми входами реверсивного счетчика, параллельного регистра, D-триггера и второго регистра сдвига и является первым входом блока управления, информационный вход первого регистра сдвига соединен с входом управления счетом реверсивного счетчика и является вторым входом блока управления, первый управляющий вход блока коммутации является третьим входом блока управления, выход делителя частоты на два соединен с вто- рым управляющим входом блока коммутации и является первым выходом блока управления, выход дешифратора знака косинуса подключен к другому входу дешифратора смены знака косинуса, выход которого соединен с третьим управляющим входом блока коммутации, первый выход второго регистра сдвига является вторым выходом блока управления, выходы реверсивного счетчика соединены с другими входами дешифратора знака синуса и с соответствующими информационными входами параллельного регистра, выходы которого подключены к соответствующим входам дешифратора знака косинуса, а первая и вторая группы выходов блока коммутации являются соответственно первой и второй группами выходов блока управления.

Pit г. 2

8ыхе8

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный групповой приемник многочастотного кода с импульсно-кодовой модуляцией | 1989 |

|

SU1830632A1 |

| ШЕСТИКАНАЛЬНЫЙ ПАРАЛЛЕЛЬНЫЙ КОРРЕЛЯТОР ДЛЯ ПРИЕМНИКОВ СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 1998 |

|

RU2144210C1 |

| Преобразователь угла поворота вала в код | 1990 |

|

SU1758875A1 |

| Устройство для отладки и контроля микропроцессорных систем | 1988 |

|

SU1647568A1 |

| Адаптивный групповой приемник многочастотного кода с импульсно-кодовой модуляцией | 1989 |

|

SU1635273A1 |

| ФОРМИРОВАТЕЛЬ СИГНАЛОВ МНОГОЧАСТОТНОЙ ЧАСТОТНОЙ ТЕЛЕГРАФИИ | 2002 |

|

RU2212110C1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ГРУППОВОЙ ПРИЕМНИК СИГНАЛОВ УПРАВЛЕНИЯ И ВЗАИМОДЕЙСТВИЯ С НЕЛИНЕЙНОЙ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ (ИКМ) | 1998 |

|

RU2143790C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ БЫСТРОЙ СИНХРОНИЗАЦИИ В СИСТЕМАХ С ШУМОПОДОБНЫМИ СИГНАЛАМИ | 1989 |

|

SU1841074A1 |

| Многоканальное устройство для регистрации информации | 1984 |

|

SU1236452A1 |

Изобретение относится к технике связи. Цель изобретения - повышение точности формирования квадратурных сигналов путем снижения уровня шумов и квантования при одновременном уменьшении объема записи постоянных запоминающих устройств (ПЗУ). Формирователь содержит блок считывания 1, состоящий из блока опорных частот (БОЧ) 4 и блока управления (БУ) 5, ПЗУ 2 и 3 и мультиплексоры 6 и 7. Нв БОЧ 4 поступает сигнал дискретизации, а на БУ 5 - информационный сигнал и логические сигналы. С БОЧ 4 на младшие адресные входы ПЗУ 2 и 3 поступают сигналы считывания отсчетов значений формируемых квадратурных сигналов, записанных в ПЗУ 2 и 3, а на старшие адресные входы ПЗУ 2 и 3 с БУ 5 поступают сигналы считывания, определяющие тип формируемой траектории. Управляющие сигналы с БУ 5 поступают на мультиплексоры 6 и 7, производя их переключение и пропуская сигналы с ПЗУ 2 через мультиплексор 6 (7) и с ПЗУ 3 через мультиплексор 7 (6), а также производя инвертирование поступающих с ПЗУ 2 и 3 сигналов и формируя старшие разряды сигналов. Цель достигается введением мультиплексоров 6 и 7. 1 з.п. ф-лы, 8 ил.

Фиг. 5

Первое ЛЗУВторое ЛЗУ

фиг. 7

Фиг 6

2 Q/nax, 1таж

фиг.8

| Suzuki Н | |||

| , Yamao Y., Momma К | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Electronics Letters, v | |||

| Прибор для промывания газов | 1922 |

|

SU20A1 |

| p | |||

| Устройство для электрического освещения, нагревания и вентиляции железнодорожных вагонов | 1925 |

|

SU875A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-03-15—Публикация

1987-12-28—Подача