СП СП

со

00

ю

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации | 1986 |

|

SU1338099A1 |

| Устройство для определения достоверности информации,передаваемой циклическим кодом | 1974 |

|

SU501491A2 |

| Система цикловой синхронизации для многоканальных систем связи | 1988 |

|

SU1598193A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ ТОЧНОГО ВРЕМЕНИ | 1990 |

|

RU2033640C1 |

| Устройство определения конца блока циклического кода | 1987 |

|

SU1515381A2 |

| Устройство определения конца блока циклического кода | 1986 |

|

SU1401631A2 |

| Устройство определения конца блока циклического кода | 1982 |

|

SU1061279A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| Устройство для контроля электронной вычислительной машины | 1981 |

|

SU1019451A1 |

Изобретение относится к электросвязи. Цель изобретения - уменьшение вероятности ложного фазирования. Устройство содержит регистр 1 сдвига, дешифратор 2, элемент И 3, счетчик 4, инвертор 5, блокировочный 6 и установочный 7 триггеры. В устройство введены элемент 8 задержки, блок 9 памяти, триггер 10 запрета, блок 11 вычитания, два элемента ИЛИ 13, 14 и дополнительные дешифратор 12, счетчик 15 и элемент И 16. Уменьшение вероятности ложного фазирования обеспечивается за счет дополнительной проверки и защиты текущей фазовой координаты. 2 ил.

14)

(риг.1

}I5l5

Изобретение OTJIOCHTCH к электросвязи, и может быть использовано в системах передачи данных для циклово синхронизации в дискретном канале связи и является усовершенствованием известного устройства по основному авт.св. № 1338099.

Цель изобретения - уменьшение вероятности ложного фазирования.

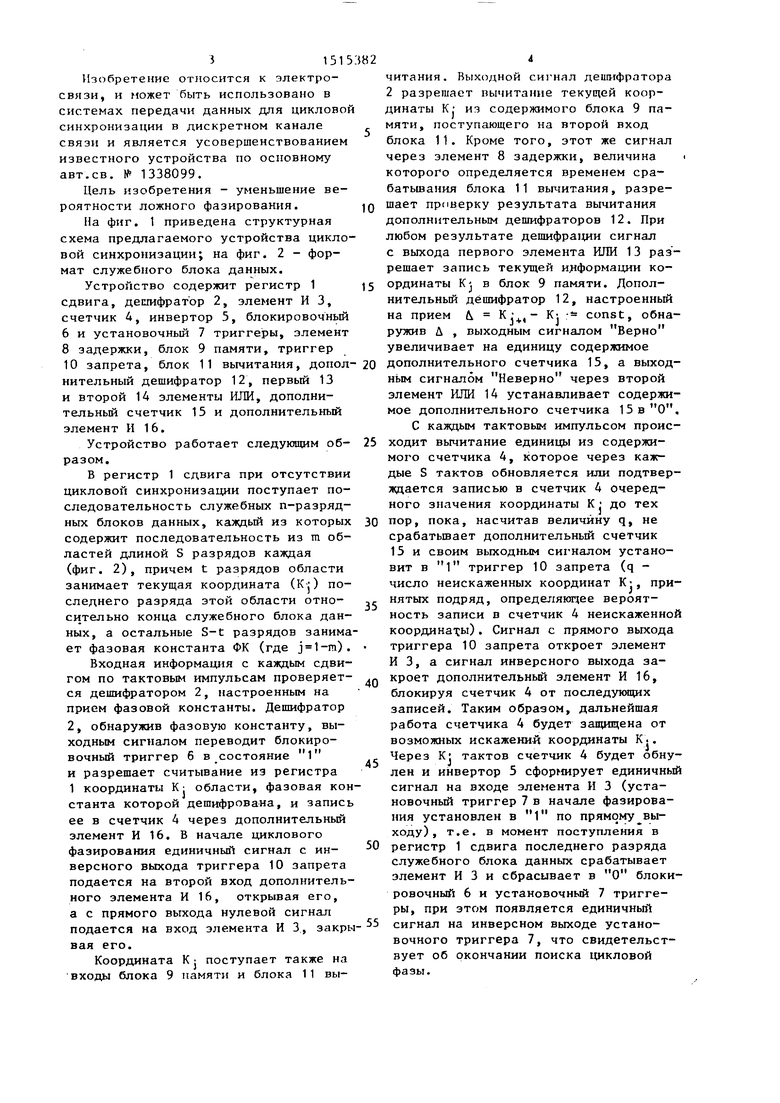

На фиг. 1 приведена структурная схема предлагаемого устройства цикловой синхронизации; на фиг. 2 - формат служебного блока данных.

Устройство содержит регистр 1 сдвига, дешифратор 2, элемент И 3, счетчик 4, инвертор 5, блокировочный 6 и установочный 7 триггеры, элемент 8 задержки, блок 9 памяти, триггер 10 запрета, блок 11 вычитания, дополнительный дешифратор 12, первьш 13 и второй 1А элементы ИЛИ, дополнительный счетчик 15 и дополнительный элемент И 16.

Устройство работает следующим образом.

В регистр 1 сдвига при отсутствии цикловой синхронизации поступает последовательность служебных п-разряд- ных блоков данных, каждый из которых содержит последовательность из m областей длиной S разрядов каждая (фиг. 2), причем t разрядов области занимает текущая координата (K j) последнего разряда этой области относительно конца служебного блока данных, а остальные S-t разрядов занимает фазовая константа ФК (где ). Входная информация с каждым сдвигом по тактовым импульсам проверяется дешифратором 2, настроенным на прием фазовой константы. Дешифратор 2, обнаружив фазовую константу, выходным сигналом переводит блокировочный триггер 6 в состояние 1 и разрешает считывание из регистра 1 координаты К: области, фазовая константа которой дешифрована, и запись ее в счетчик 4 через дополнительный элемент И 16, В начале циклового фазирования единичный сигнал с инверсного выхода триггера 10 запрета подается на второй вход дополнительного элемента И 16, открывая его, а с прямого выхода нулевой сигнал подается на вход элемента И 3, закры вая его.

Координата К: поступает также на ВХОДЫ блока 9 памяти и блока 11 вы

читания. Выходной сигнал дешифратора 2 разрешает вычитание текущей координаты К; из содержимого блока 9 памяти, поступающего на второй вход блока 11. Кроме того, этот же сигнал через элемент 8 задержки, величина которого определяется временем сра- батьшания блока 11 вычитания, разре Q шает приверну результата вычитания дополнительным дешифраторов 12. При любом результате дешифрации сигнал с выхода первого элемента ИЛИ 13 раз - решает запись текущей и 1формации ординаты Kj в блок 9 памяти. Дополнительный дешифратор 12, настроенный на прием ( К , - К: г- const, обнаружив Л , выходным сигналом Верно увеличивает на единицу содержимое

20 дополнительного счетчика 15, а выход- нь1м сигналом Неверно через второй элемент ИЛИ К устанавливает содержимое дополнительного счетчика 15 в О. С каждым тактовым импульсом проис25 ходит вычитание единицы из содержимого счетчика 4, которое через каждые S тактов обновляется или подтвер- лдается записью в счетчик 4 очередного значения координаты К ; до тех

30 пор, пока, насчитав величину q, не срабатьшает дополнительный счетчик 15 и своим выходным сигналом установит в 1 триггер 10 запрета (q - число неискаженных координат Kj, принятых подряд, определяющее вероятность записи в счетчик 4 неискаженной координат;ы). Сигнал с прямого выхода триггера 10 запрета откроет элемент И 3, а сигнал инверсного выхода закроет дополнительный элемент И 16, блокируя счетчик 4 от последующих записей. Таким образом, дальнейшая работа счетчика 4 будет защищена от возможных искажений координаты К.. Через К тактов счетчик 4 будет обнулен и инвертор 5 сформирует единичный сигнал на входе элемента И 3 (установочный триггер 7 в начале фазирования установлен в 1 по прямому выходу), т.е. в момент поступления в

50 регистр 1 сдвига последнего разряда служебного блока данных срабатывает элемент И 3 и сбрасывает в О блокировочный 6 и установочный 7 триггеры, при этом появляется единичньй 55 сигнал на инверсном выходе установочного триггера 7, что свидетельствует об окончании поиска цикловой фазы.

35

40

5151

В качестве триггера 10 запрета может быть использован, например, триггер RS-типа. Блок 9 памяти может быть выполнен, например, в виде совокупности триггеров D-типа с объединенными входами разрешения записи и объединенными установочными входами.

В качестве блока 11 вычитания может быть использован t-разрядный сумматор, на прямые входы которого подается уменьшаемое, д. на инверсные входы - вычитаемое. Дополнительный дешифратор 12 может быть вьтолнен, например, в виде последовательно соединенной схемы сравнения типа СП-1 (выходного сигнала блока 11 вычитания с константой Д) с ключом (управляемым выходным сигналом элемента 8 задержки) и инвертором. Выход,ключа при сравнении является сигналом Верно, а выход инвертора при несравнении - сигналом Неверно.

Таким образом, предлагаемое устройство обеспечивает по Сравнению с известным уменьшение вероятности ложного фазирования за счет дополнительной проверки и защиты текущей фазовой координаты.

Формула изобретения

Устройство цикловой синхронизации по авт. св. № 1338099, отличающееся тем, что, с целью

3826

уменьшения вероятности ложного фазирования, в него введены элемент задержки, два элемента ИЛИ, дополнительный элемент И и последовательно соединенные блок памяти, блок вычитания, дополнит ел ьньп дешифратор, дополнительный счетчик и триггер запрета, при этом вход элемента задержjQ ки и управляющий вход блока вычитания соединены с выходом дешифратора, прямой выход триггера запрета подключен к четвертому входу элемента И, выход элемента задержки подключен

15 к управляющему входу дополнительного дешифратора, второй выход которого подключен к первым входам первого и второго элементов ИЛИ, а первый выход подключен к второму входу первого элемента ИЛИ, выход которого подключен к управляющему входу блока памяти, информационные входы которого и входы вычитаемого блока вычитания соединены с информационны25 ми входами счетчика, установочный вход дополнительного счетчика соединен с выходом второго элемента ИЛИ, установочньп вход которого и установочные входы триггера запрета, счетчика и блока памяти соединены с установочным входом устано вочного триггера, а вход записи счетчика соединен с выходом дешифратора через дополнительный элемент И, второй вход которого соединен с

35 инверсным выходом триггера запрета

20

30

| Устройство цикловой синхронизации | 1986 |

|

SU1338099A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-10-15—Публикация

1987-07-13—Подача