Изобретение относится к электросвязи и может быть использовано в системах цифровой коммутации и является усовершенствованием устройства по авт. св. № 1485429.

Целью изобретения является повышение скорости коммутации.

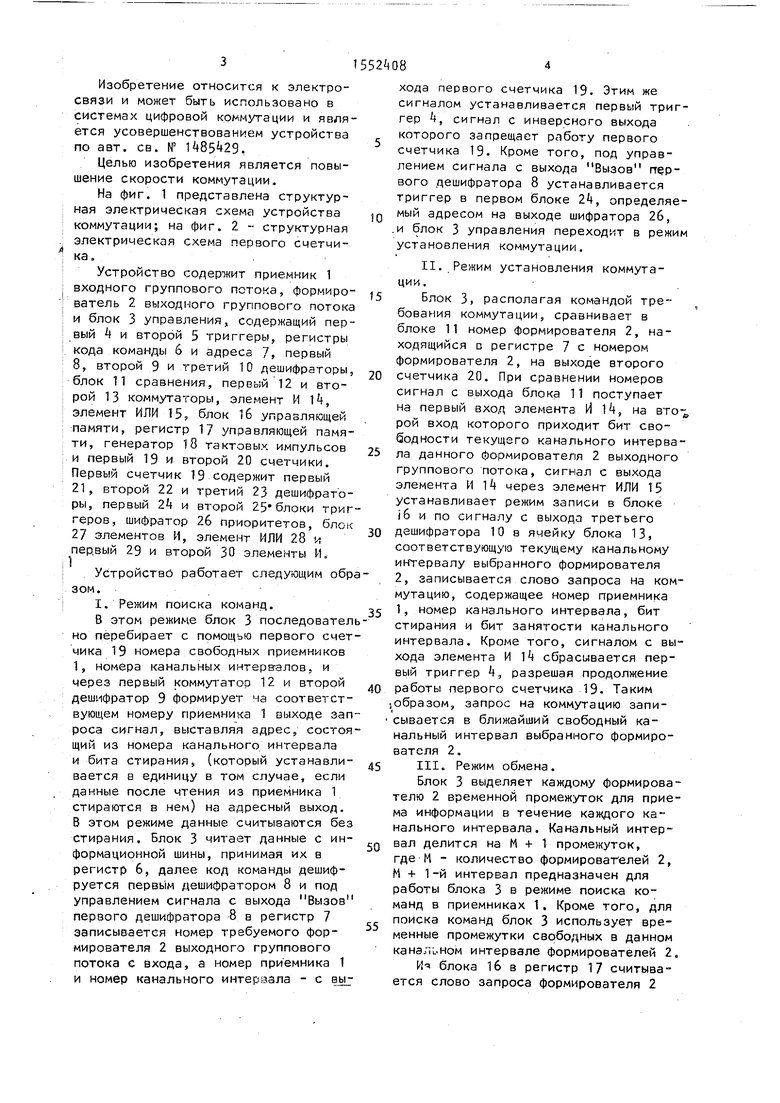

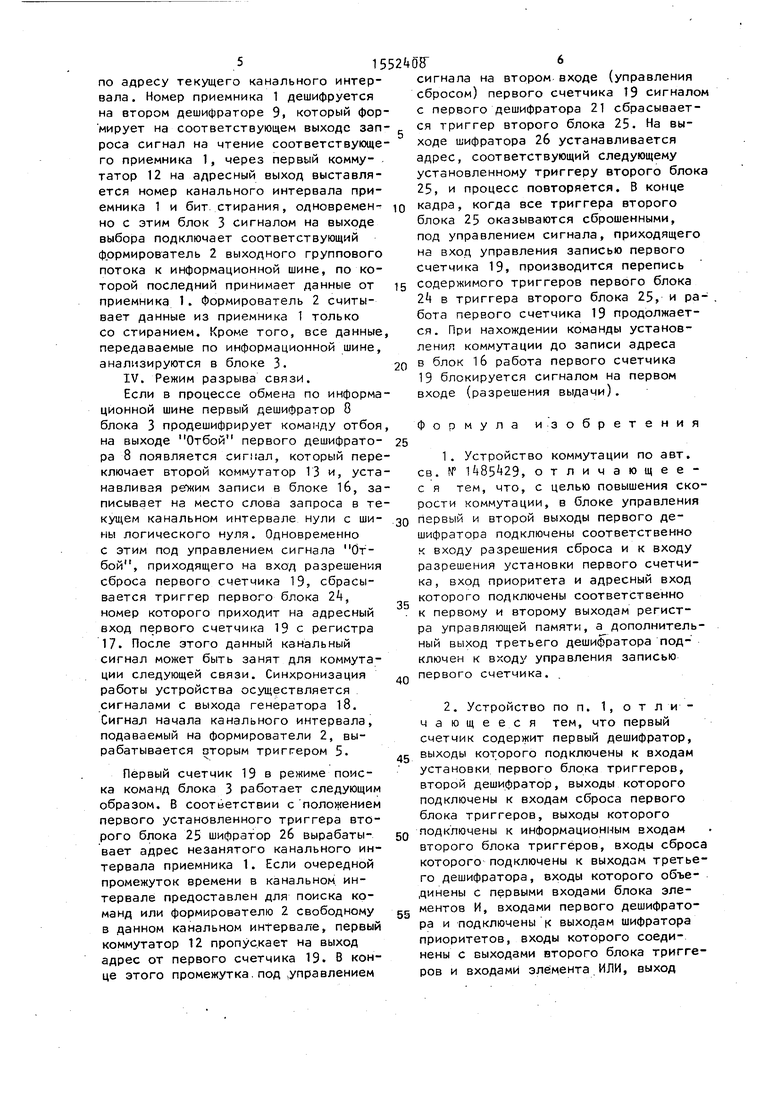

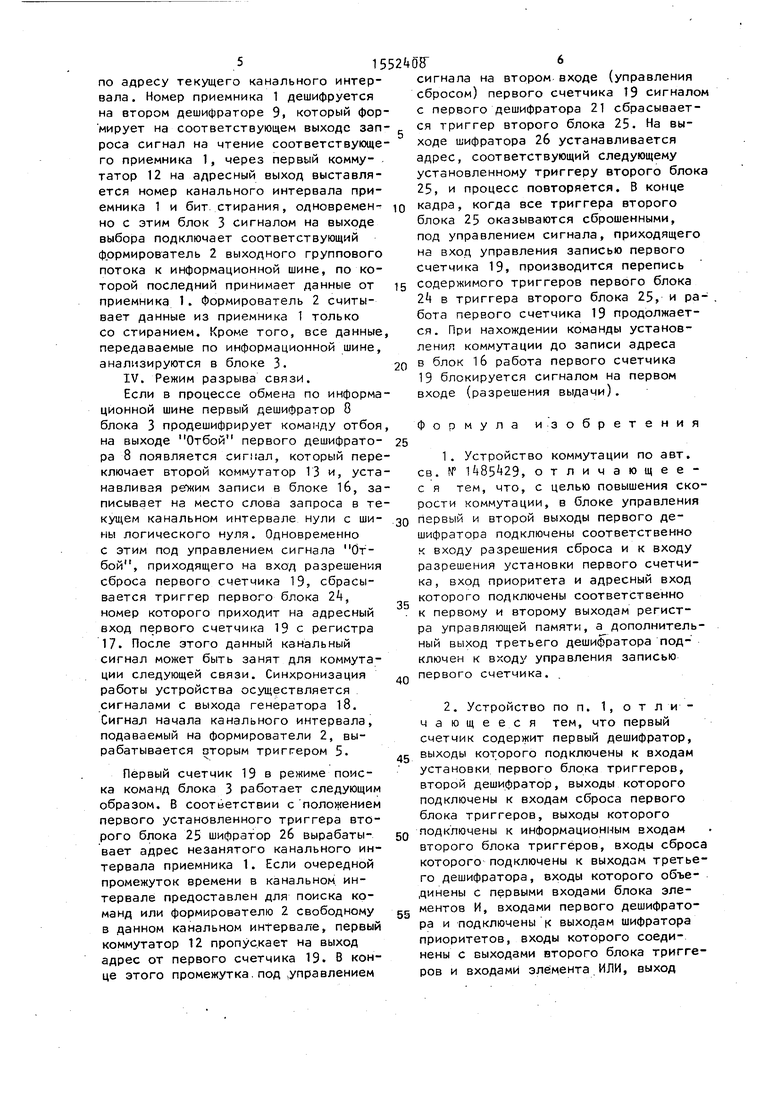

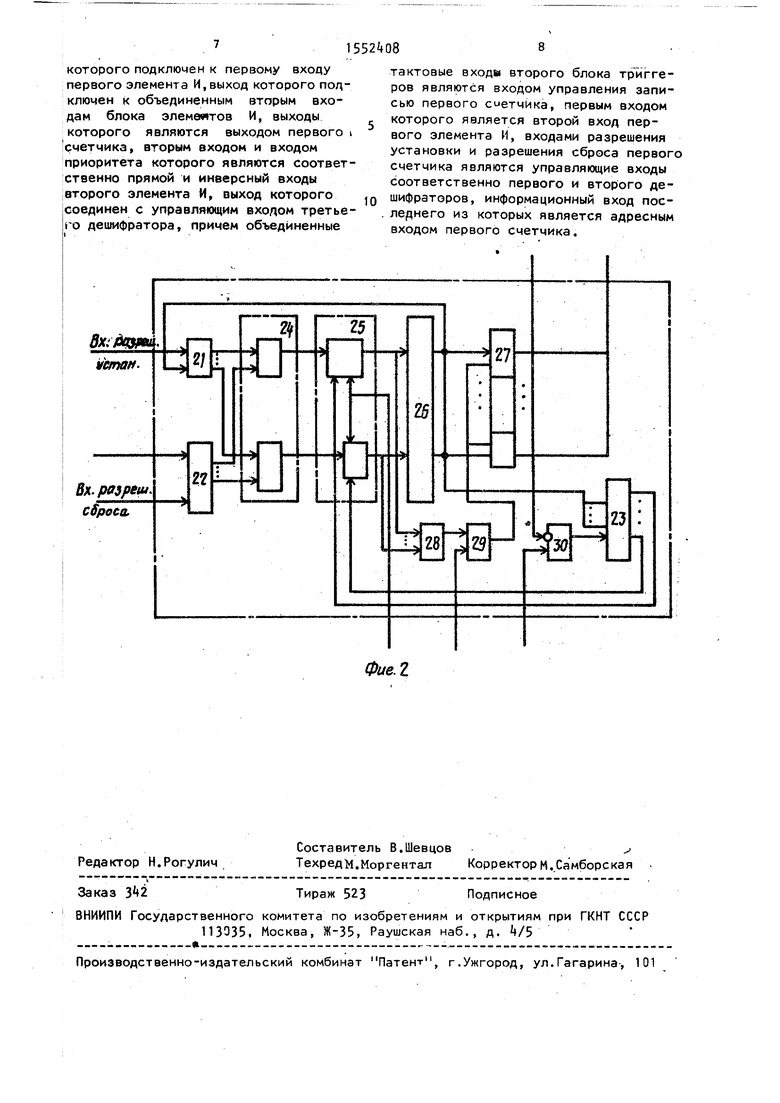

На фиг. 1 представлена структурная электрическая схема устройства коммутации; на фиг. 2 - структурная электрическая схема первого счетчика.

Устройство содержит приемник 1 входного группового потока, формирователь 2 выходного группового потока и блок 3 управления, содержащий первый 4 и второй 5 триггеры, регистры кода команды 6 и адреса 7, первый 8, второй 9 и третий 10 дешифраторы, блок 11 сравнения, первый 12 и второй 13 коммутаторы, элемент И 14, элемент ИЛИ 15, блок 16 управляющей памяти, регистр 17 управляющей памяти, генератор 18 тактовых импульсов и первый 19 и второй 20 счетчики. Первый счетчик 19 содержит первый 21, второй 22 и третий 23 дешифраторы, первый 2k и второй 25 блоки триггеров, шифратор 26 приоритетов, блек 27 элементов И, элемент ИЛИ 28 и первый 29 и второй 30 элементы И.

Устройство работает следующим обра зом.

I. Режим поиска команд.

В этом режиме блок 3 последовательно перебирает с помощью первого счетчика 19 номера свободных приемников 1, номера канальных интервалов, и через первый коммутатоэ 12 и второй дешифратор 9 формирует ча соответствующем номеру приемника 1 выходе запроса сигнал, выставляя адрес, состоящий из номера канального интервала и бита стирания, (который устанавливается а единицу в том случае, если данные после чтения из приемника 1 стираются в нем) на адресный выход. В этом режиме данные считываются без стирания. Блок 3 читает данные с информационной шины, принимая их в регистр 6, далее код команды дешифруется первым дешифратором 8 и под управлением сигнала с выхода Вызов первого дешифратора 8 в регистр 7 записывается номер требуемого формирователя 2 выходного группового потока с входа, а номер приемника 1 и номер канального интеразла - с вьг0

5

0

5

0

5

0

5

0

5

Этим же первый тригхода первого счетчика 19. сигналом устанавливается rep 4, сигнал с инверсного выхода которого запрещает работу первого счетчика 19. Кроме того, под управлением сигнала с выхода Вызов первого дешифратора 8 устанавливается триггер в первом блоке 2k, определяемый адресом на выходе шифратора 26, и блок 3 управления переходит в режим установления коммутации.

II. Режим установления коммутации.

Блок 3, располагая командой требования коммутации, сравнивает в блоке 11 номер формирователя 2, находящийся с регистре 7 с номером формирователя 2, на выходе второго счетчика 20. При сравнении номеров сигнал с выхода блока 11 поступает на первый вход элемента И 14, на вто-, рой вход которого приходит бит сво- бодности текущего канального интервала данного формирователя 2 выходного группового потока, сигнал с выхода элемента И 14 через элемент ИЛИ 15 устанавливает режим записи в блоке (б и по сигналу с выхода третьего дешифратора 10 в ячейку блока 13, соответствующую текущему канальному интервалу выбранного формирователя 2, записывается слово запроса на коммутацию, содержащее номер приемника 1, номер канального интервала, бит стирания и бит занятости канального интервала. Кроме того, сигналом с выхода элемента И 14 сбрасывается первый триггер 4, разрешая продолжение работы первого счетчика 19. Таким sобразом, запрос на коммутацию записывается в ближайший свободный канальный интервал выбранного формирователя 2,

III Режим обмена.

Блок 3 выделяет каждому формирователю 2 временной промежуток для приема информации в течение каждого канального интервала. Канальный интервал делится на М + 1 промежуток, где М - количество формирователей 2, М + 1-и интервал предназначен для работы блока 3 в режиме поиска команд в приемниках 1. Кроме того, для поиска команд блок 3 использует временные промежутки свободных в данном канальном интервале формирователей 2,

И- блока 16 в регистр 17 считывается слово запроса формирователя 2

по адресу текущего канального интервала. Номер приемника 1 дешифруется на втором дешифраторе 9, который формирует на соответствующем выходе запроса сигнал на чтение соответствующего приемника 1, через первый коммутатор 12 на адресный выход выставляется номер канального интервала приемника 1 и бит стирания, одновременно с этим блок 3 сигналом на выходе выбора подключает соответствующий формирователь 2 выходного группового потока к информационной шине, по которой последний принимает данные от приемника 1. Формирователь 2 считывает данные из приемника 1 только со стиранием. Кроме того, все данные, передаваемые по информационной шине, анализируются в блоке 3.

IV. Режим разрыва связи.

Если в процессе обмена по информационной шине первый дешифратор 8 блока 3 продешифрирует команду отбоя, на выходе Отбой первого дешифрато- ра 8 появляется сигнал, который переключает второй коммутатор 13 и, устанавливая режим записи в блоке 16, записывает на место слова запроса в текущем канальном интервале нули с шины логического нуля. Одновременно с этим под управлением сигнала Отбой, приходящего на вход разрешения сброса первого счетчика 19, сбрасывается триггер первого блока 24, номер которого приходит на адресный вход первого счетчика 19 с регистра 17. После этого данный канальный сигнал может быть занят для коммутации следующей связи. Синхронизация работы устройства осуществляется сигналами с выхода генератора 18. Сигнал начала каналоного интервала, подаваемый на формирователи 2, вырабатывается пторым триггером 5.

Первый счетчик 19 в режиме поиска команд блока 3 работает следующим образом. В соотьетствии с положением первого установленного триггера второго блока 25 шифратор 26 вырабатывает адрес незанятого канального интервала приемника 1. Если очередной промежуток времени в канальном интервале предоставлен для поиска команд или формирователю 2 свободному в данном канальном интервале, первый коммутатор 12 пропускает на выход адрес от первого счетчика 19. В конце этого промежутка под управлением

ю

20

25 сигнала на втором входе (управления сбросом) первого счетчика 19 сигналом с первого дешифратора 21 сбрасывается триггер второго блока 25. На выходе шифратора 26 устанавливается адрес, соответствующий следующему установленному триггеру второго блока 25, и процесс повторяется. В конце кадра, когда все триггера второго блока 25 оказываются сброшенными, под управлением сигнала, приходящего на вход управления записью первого счетчика 19f производится перепись 15 содержимого триггеров первого блока 2k в триггера второго блока 25, и работа первого счетчика 19 продолжается. При нахождении команды установления коммутации до записи адреса в блок 16 работа первого счетчика 19 блокируется сигналом на первом входе (разрешения выдачи).

фоомула изобретения

1. Устройство коммутации по авт. св. № , отличающее- с я тем, что, с целью повышения скорости коммутации, в блоке управления

первый и второй выходы первого дешифратора подключены соответственно к входу разрешения сброса и к входу разрешения установки первого счетчика , вход приоритета и адресный вход которого подключены соответственно к первому и второму выходам регистра управляющей памяти, а дополнительный выход третьего дешифратора подключен к входу управления записью

первого счетчика.

2. Устройство по п. отличающееся тем, что первый счетчик содержит первый дешифратор, выходы которого подключены к входам установки первого блока триггеров, второй дешифратор, выходы которого подключены к входам сброса первого блока триггеров, выходы которого

подключены к информационным входам второго блока триггеров, входы сброса которого подключены к выходам третьего дешифратора, входы которого объединены с первыми входами блока элементов И, входами первого дешифратора и подключены к выходам шифратора приоритетов, входы которого соединены с выходами второго блока триггеров и входами элемента ИЛИ, выход

которого подключен к первому входу первого элемента И,выход которого подключен к объединенным вторым входам блока элементов И, выходы которого являются выходом первого i счетчика, вторым входом и входом приоритета которого являются соответственно прямой и инверсный входы второго элемента И, выход которого соединен с управляющим входом третьего дешифратора, причем объединенные

тактовые вход второго блока триггеров являются входом управления записью первого сметчика, первым входом которого является второй вход первого элемента И, входами разрешения установки и разрешения сброса первого счетчика являются управляющие входы соответственно первого и второго дешифраторов, информационный вход последнего из которых является адресным входом первого счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с внешним устройством | 1986 |

|

SU1377864A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Адаптивный коммутатор | 1979 |

|

SU824264A1 |

| СИНХРОННЫЙ АДАПТИВНЫЙ МУЛЬТИПЛЕКСОР | 1993 |

|

RU2078401C1 |

| ВЕДОМСТВЕННАЯ СИСТЕМА ДВУХСТОРОННЕЙ ВЫСОКОСКОРОСТНОЙ РАДИОСВЯЗИ С ЭФФЕКТИВНЫМ ИСПОЛЬЗОВАНИЕМ РАДИОЧАСТОТНОГО СПЕКТРА | 2016 |

|

RU2650191C1 |

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

| СЕТЬ ДЛЯ МАРШРУТИЗАЦИИ СООБЩЕНИЙ | 1996 |

|

RU2115162C1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Устройство передачи и приема информации для интегрированной кольцевой сети связи | 1990 |

|

SU1734241A1 |

Изобретение относится к электросвязи и может быть использовано в системах цифровой коммутации. Цель изобретения - повышение скорости коммутации. Устройство содержит приемник 1 входного группового потока, формирователь 2 выходного группового потока и блок 3 управления. Блок 3 содержит триггеры 4 и 5, регистр 6 кода команды, регистр 7 адреса, три дешифратора 8 - 10, блок 11 сравнения, коммутаторы 12 и 13, элемент И 14, элемент ИЛИ 15, блок 16 управляющей памяти, регистр 17 управляющей памяти, генератор 18 тактовых импульсов и два счетчика 19 и 20. Устройство работает в четырех режимах: I - режим поиска команд, II - режим установления коммутации, III - режим обмена, IY - режим разрыва связи. 1 з.п. ф-лы, 2 ил.

Редактор Н.Рогулич

Составитель В.Шевцов

ТехредМ.Моргентал Корректор М.Самборска я

Заказ 342

Тираж 523

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Фие.2

Подписное

| Авторское свидетельство СССР N- , кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-03-23—Публикация

1987-10-05—Подача