ел СП ч

О

1

о

| название | год | авторы | номер документа |

|---|---|---|---|

| Система экстремального регулирования квадрупольного масс-спектрометра | 1989 |

|

SU1795419A1 |

| Устройство для задержки и формирования импульсов | 1988 |

|

SU1539979A1 |

| Устройство для подсчета числа импульсов | 1987 |

|

SU1497742A2 |

| Устройство для допускового контроля длительности временных интервалов | 1987 |

|

SU1442972A1 |

| Многофазный импульсный стабилизатор | 1984 |

|

SU1196830A1 |

| Устройство корректировки фазы для схем синхронизации | 1989 |

|

SU1706037A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265743A1 |

| Блок управления многофазным импульсным стабилизатором напряжения | 1987 |

|

SU1467704A1 |

| Устройство для допускового контроля длительности последовательности временных интервалов | 1988 |

|

SU1647508A1 |

| Устройство для выделения импульсов | 1987 |

|

SU1541759A1 |

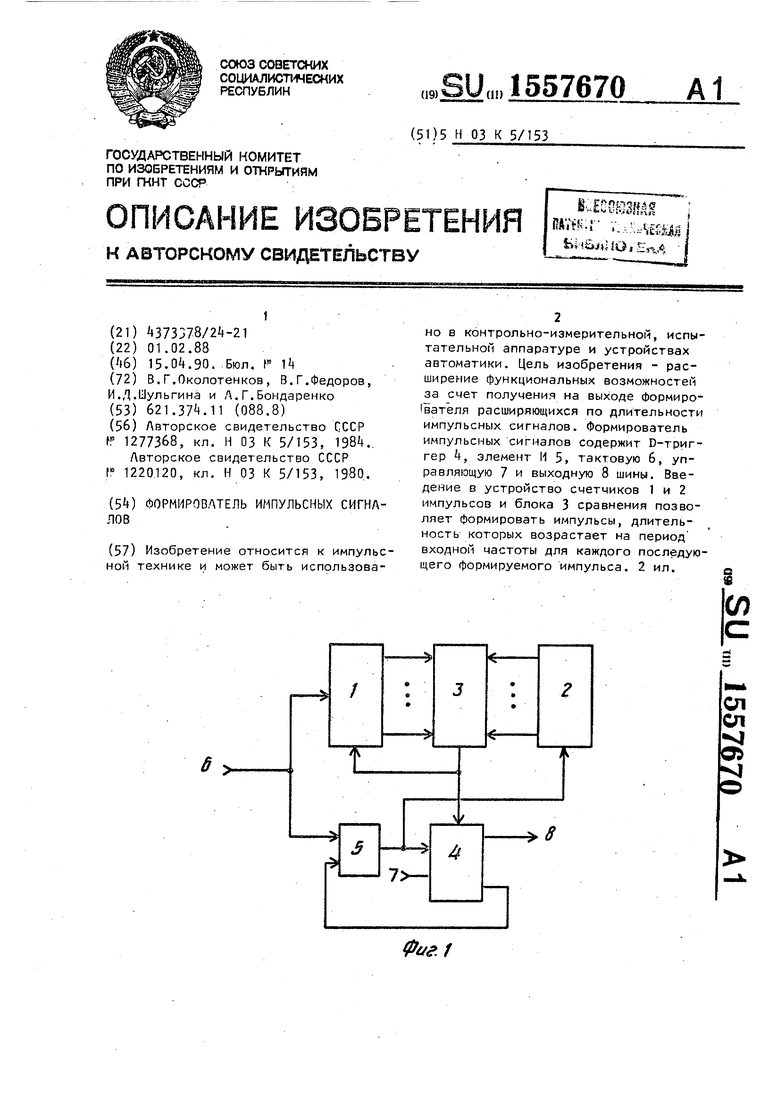

Изобретение относится к импульсной технике и может быть использовано в контрольно-измерительной, испытательной аппаратуре и устройствах автоматики. Цель изобретения - расширение функциональных возможностей за счет получения на выходе формирователя расширяющихся по длительности импульсных сигналов. Формирователь импульсных сигналов содержит D-триггер 4, элемент И 5, тактовую 6, управляющую 7 и выходную 8 шины. Введение в устройство счетчиков 1 и 2 импульсов и блока 3 сравнения позволяет формировать импульсы, длительность которых возрастает на период входной частоты для каждого последующего формируемого импульса. 2 ил.

Фие.1

Изобретение относится к импульсно технике и может быть использовано в автоматике, контрольно-измерительной и испытательной аппаратуре.

Целью изобретения является расширение функциональных возможностей устройства за счет получения на выходе формирователя расширяющихся по длительности импульсов.

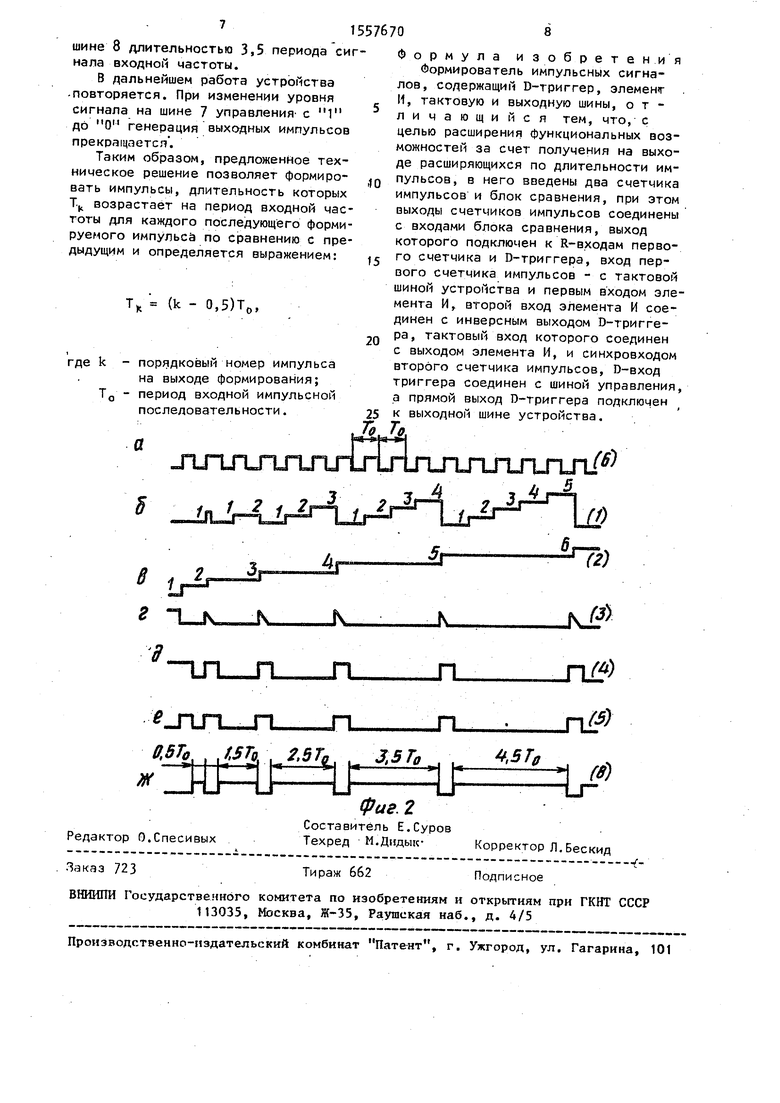

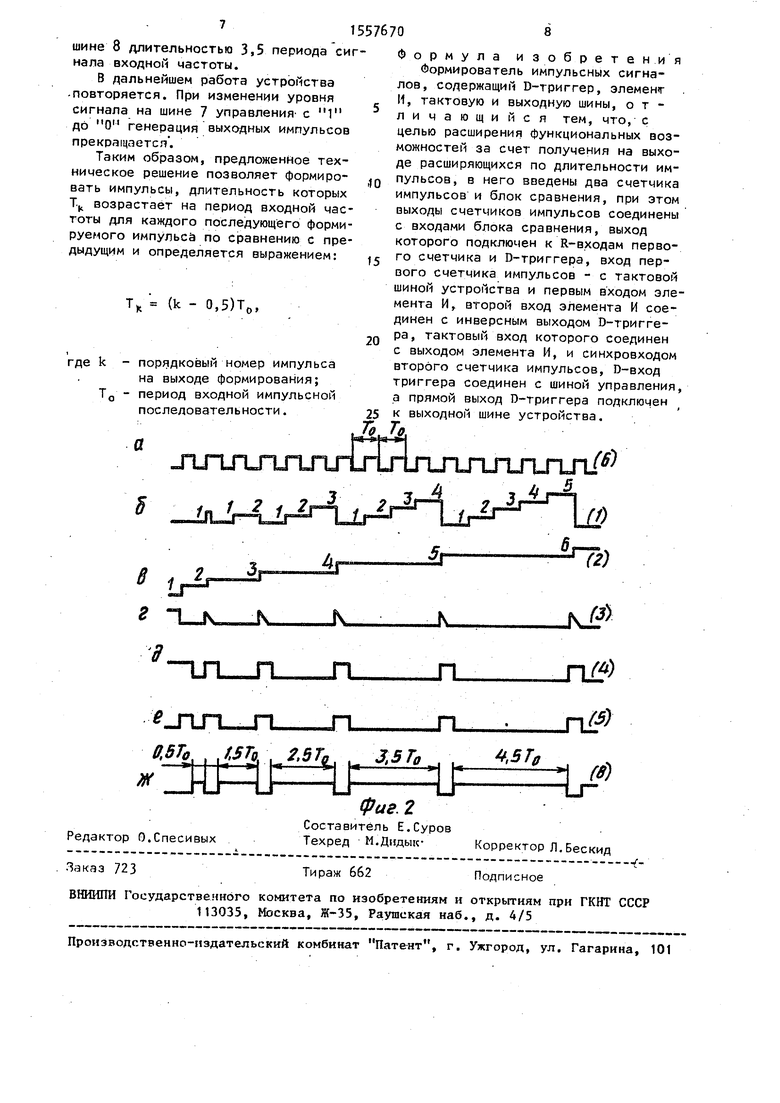

На фиг. 1 изображена структурная .схема формирователя импульсных сигналов; на фиг. 2 - эпюры напряжений, поясняющие работу формирователя.

Формирователь содержит счетчики 1 и 2 импульсов, выходы которых соединены соответственно с первой и второй группами входов блока 3 сравнения. Выход блока сравнения соедине с Н-входами D-триггера b и счетчика 1 импульсов, тактовый вход D-триггера 4 и синхровход счетчика 2 импульсов соединены с выходом элемента И 5, первый вход которого соединен с синхровходом счетчика 1 импульсов и тактовой шиной 6 устройства. Второй вход элемента И 5 соединен с инверсным выходом D-триггера 4, D-вход которого соединен с управляющей шиной 7, а прямой выход триггера подключен к выходной шине 8 устройства.

В качестве счетчиков 1, 2 импульсов могут быть использованы элементы соответствующих серий микросхем, на- |пример двоичные счетчики 155 ИЕ 5, 564 ИЕ 10. Блок 3 сравнения может быть реализован на элементах , 564ИП2 и других. Кроме того, в качестве блока сравнения может быть использована любая известная схема для сравнения двух n-разрядных чисел, на выходе которой при равенстве чисел присутствует высокий логический уровень, а при неравенстве - низкий.

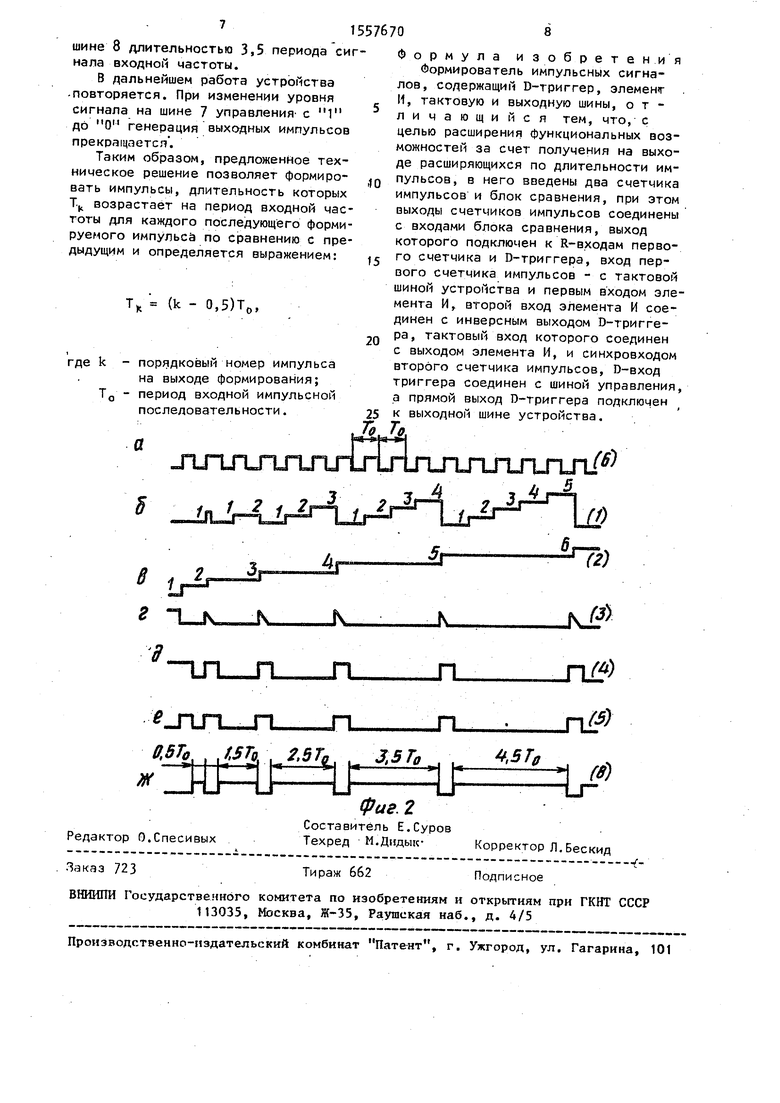

В приведенных эпюрах напряжений (фиг. 2) на выходах блоков и узлов формирователя буквенные обозначения эпюр соответствуют позиционным обозначениям элементов на его структурной схеме: «-6, 5-1, 8-2, г-3, $-Ь, е-5, ж-8. На эпюрах 6 и & индекса ми обозначено состояние счетчиков 1 и 2 импульсов, содержимое которых изменяется с каждым поступившим на их входы импульсом. Как видно из эпюр д. и х , на прямом и инверсном выходах триггера формируются две парафазные импульсные последовательности. Причем, если на выходной шине

0

5

0

5

0

5

0

5

0

5

8 устройства (см. , фиг. 2) длительность паузы между импульсами постоянна и длительность каждого последующего импульса больше длительности предыдущего на период входной частоты, то на инверсном выходе триггера 4 (см. у , фиг. 2) формируется импульсная последовательно, у которой длительность импульсов остается неизменной, а изменяется длительность паузы Между импульсами: после каждого очередного импульса она становится больше на период входной частоты Т0. Длительность импульсов в одной импульсной последовательности и пауз между импульсами другой импульсной последовательности кратна полученному числу периодов входной частоты (0,5Т0, , 2,5Т0 ... и т.д.).

Уст ройство работает -следующим образом.

В исходном состоянии D-триггер Ь, счетчики 1 и 2 импульсов обнулены (цепи начальной установки условно не показаны). На выходе блока 3 сравнения - уровень 1, так ка на обе группы его входов поступают одинаковые, (нулевые) кодовые комбинации. Элемент И 5 закрыт сигналом низкого уровня с тактовой шины 6 устройства. На управляющей шине 7 в исходном состоянии - низкий потенциал. Пусть счетчики 1 и 2 импульсов срабатывают по переднему, а триггер А - по заднему йронту тактовых импульсов. С изменением уровня сигнала на шине 7 управления от низкого до высокого логического уровня устройство подготавливается к работе. Пусть на тактовую шину 6 поступает импульсная последовательность типа меандр.

С приходом первого тактового им- пульса счетчик 2 переходит в состояние 1, состояние счетчика 1 при этом не изменяется, так как он остается в этот момент времени заблокирован по R-входу обнуляющим сигналом с выхода блока 3 сравнения. Изменение состояния счетчика 2 из нулевого в единичное приводит к изменению кодовой комбинации на второй группе входов блока 3 сравнения, в результате чего сигнал на его выходе становится равным О. С этого момента . времени счетчик 1 и триггер k оказываются разблокированы по обнуляющим входам. На информационном входе D10

15

20

25

5 155/670

триггера k - высокий логический уровень управляющей шины 7.

В результате этого после окончания действия первого входного импульса на тактовой шине 6 устройства происходит переключение в единичное состояние D-триггера h. Сигнал низкого логического уровня с инверсного выхода D-триггера 4 блокирует элемент И 5, а на выходной шине 8 устройства формируется единичный уровень выходного сигнала. После окончания паузы по переднему фронту второго импульса, поступившего на шину 6 устройства, изменяется состояние счетчика 1 импульсов, которое становится равным 1. На обеих группах входов блока 3 сравнения значения кодовых комбинаций становятся равными, в результате чего на выходе блока 3 сравнения сигнал изменяется с уровня О до 1, что вызывает обнуление счетчика 1 и переключение D-тоигге- ра 4 в нулевое состояние. В этот момент заканчивается формирование выходного сигнала на шине 8 устройства, длительность которого равна половине периода входной частоты. Переключение D-триггера 4 в нулевое состояние разблокирует элемент И 5, в результате чего по переднему фронту импульса на его выходе происходит изменение состояния счетчика 2, которое становится равным 2.

Изменение состояний счетчиков 1 и 2 импульсов приводит к изменению - сигнала на выходе блока 3 сравнения от уровня 1 до О, вследствие чего происходит разблокировка счетчика 1 и триггера Ц по обнуляющим входам. После окончания действия второго входного импульса по его заднему фронту происходит переключение триггера 4 в единичное состояние. На выходной шине 8 устройства начинается формирование единичного уровня второго выходного импульса. Одновременно с этим сигнал с инверсного выхода -триггера Ц блокирует элемент И 5, елая невозможным прохождение входных импульсов на вход счетчика 2. Третий и четвертый входные импульсы последовательно суммируются счетчиком 1. В момент равенства состояний счет- иков 1 и 2 импульсов (которое равно ) сигнал единичного уровня с выхода лока 3 сравнения обнуляет счетчик и возвращает в исходное состояние

30

35

40

1 с к в н с в п в т ч н е вы вы т йо пу вх ни на ли со ви

45

та им вх DвсИ но

«JQ пу с ся то не

,с си об эт ни

0

5

0

5

0

5

0

D-триггер 4, что приводит к окончанию формирования выходного импульса длительностью 1,5 периода входной частоты, элемент If 5 разблокируется и по переднему фронту сигнала на его выходе состояние счетчика 2 становится равном 3м. После обнуления счетчика 1 на первой группе входов блока 3 совпадения установятся низкие логические уровни, что приведет к изменению уровня сигнала на выходе с I до О и разблокировке по обнуляющим входам счетчика 1 импульсов и D-триггера k. После окончания действия четвертого импульса на тактовой шине 6 устройства переключается в единичное состояние D-триггер k. Это приводит к блокировке элемента И 5 и формированию переднего фронта третьего выходного импульса единичного уровня на шине 8 устройства. В дальнейшем состояние элементов не измене /я вплоть до поступления седьмого импульса на тактов ю шмну 6 устройства. По переднему фронту седьмого тактового импульсэ содержимое счетчика 1 импульсов становится равным 3. Равенство кодовых комбинаций на входах блока 3 сравнения вызыва-- ет появление на его выходе сигнала высокого логического уровня, что вызывает обнуление счетчика 1 и D- триггера k, при этом заканчивается йормирование третьего выходного импульса длительностью 2,5 периода входной частоты. Как только состояние счетчика 1 вновь станет нулевым, на выходе блока 3 сравнения устанавливается низкий логический уровень, состояние счетчика 2 импульсов становится равным 4, а счетчик 1 подго

тавливается к суммированию входных импульсов. Задним фронтом седьмой входной тактовый импульс переключает Dтриггер 4 в единичное состояние, вследствие чего блокируется элемент И 5 и начинается формирование единичного уровня четвертого выходного импульса. Последующие входные импульсы с восьмого по одиннадцатый суммируются счетчиком 1 и как только его состояние станет равным 4 (по переднему фронту одиннадцатого импульса),

сигнал с выхода блока 3 сравнения обнулит счетчик 1 и D-триггер 4. В этот момент заканчивается формирование четвертого импульса на выходной

S

/„ 12 1 -

| Устройство формирования одиночных импульсов | 1984 |

|

SU1277368A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для генерации одиночных импульсов | 1980 |

|

SU1220120A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-04-15—Публикация

1988-02-01—Подача