Изобретение относится к радиотехнике и может найти применение в многоканальных системах передачи инсЬор- мации с импульсно-кодовой модуляцией.

Целью изобретения является увеличение эффективной пропускной способности за счет обеспечения передачи дополнительной информации без увеличения частоты следования кодовых слов.

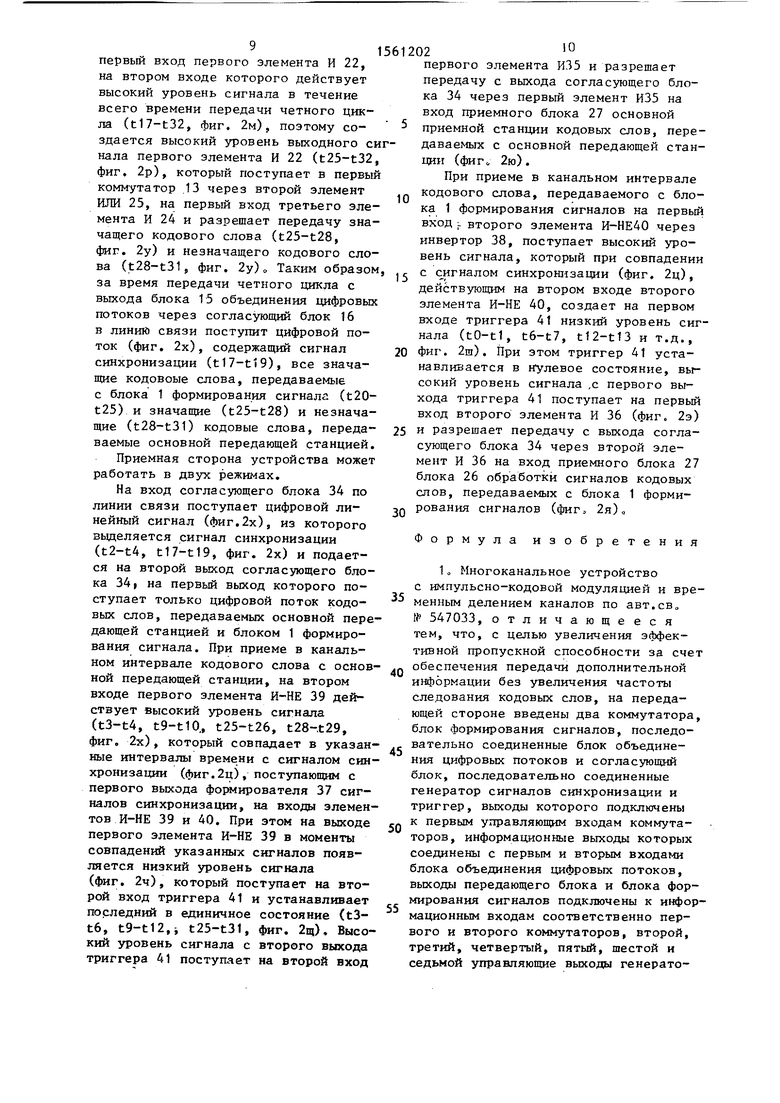

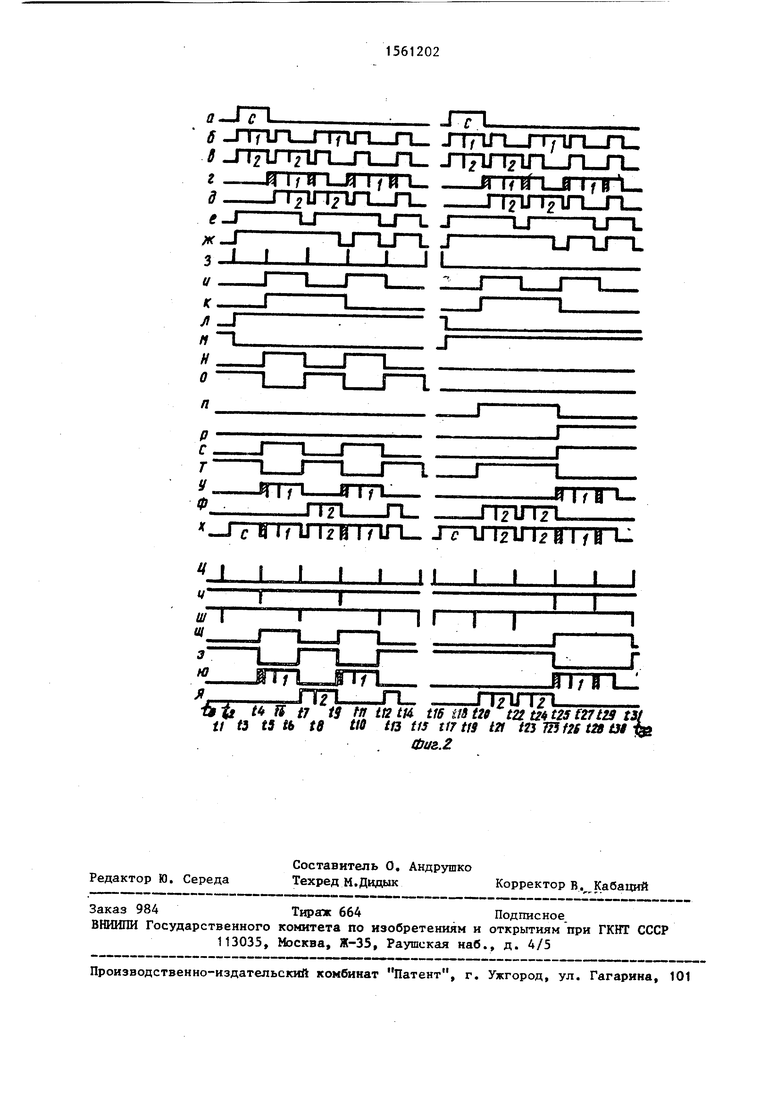

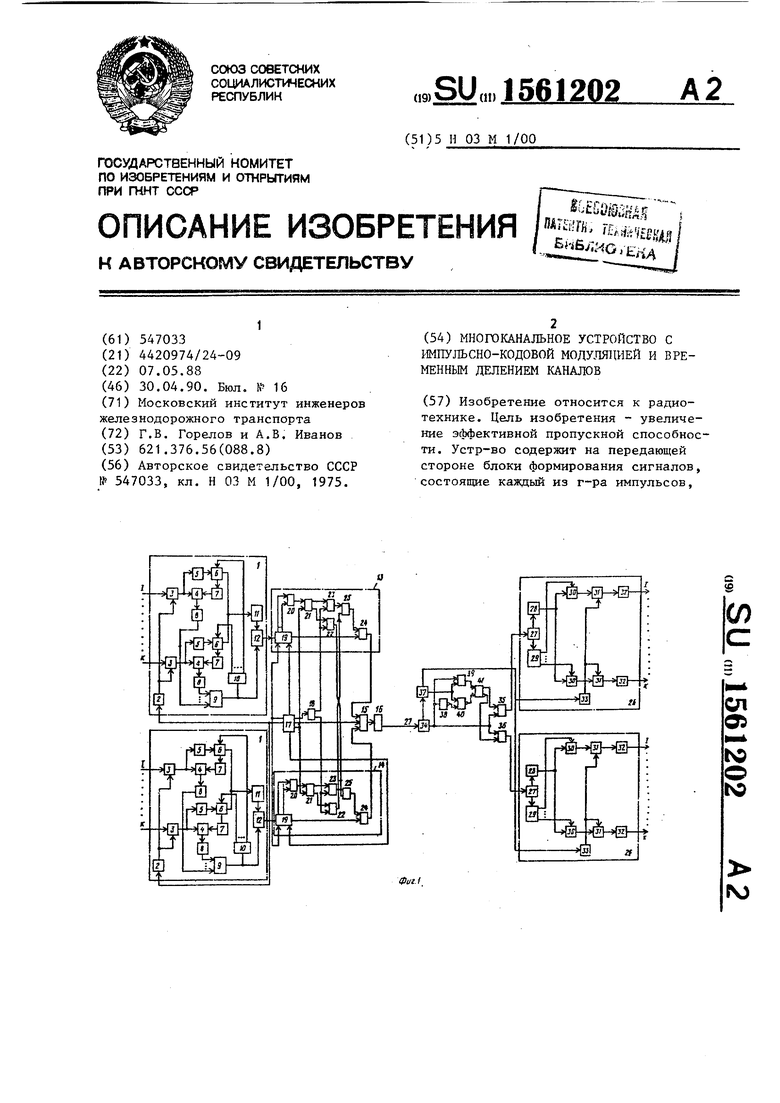

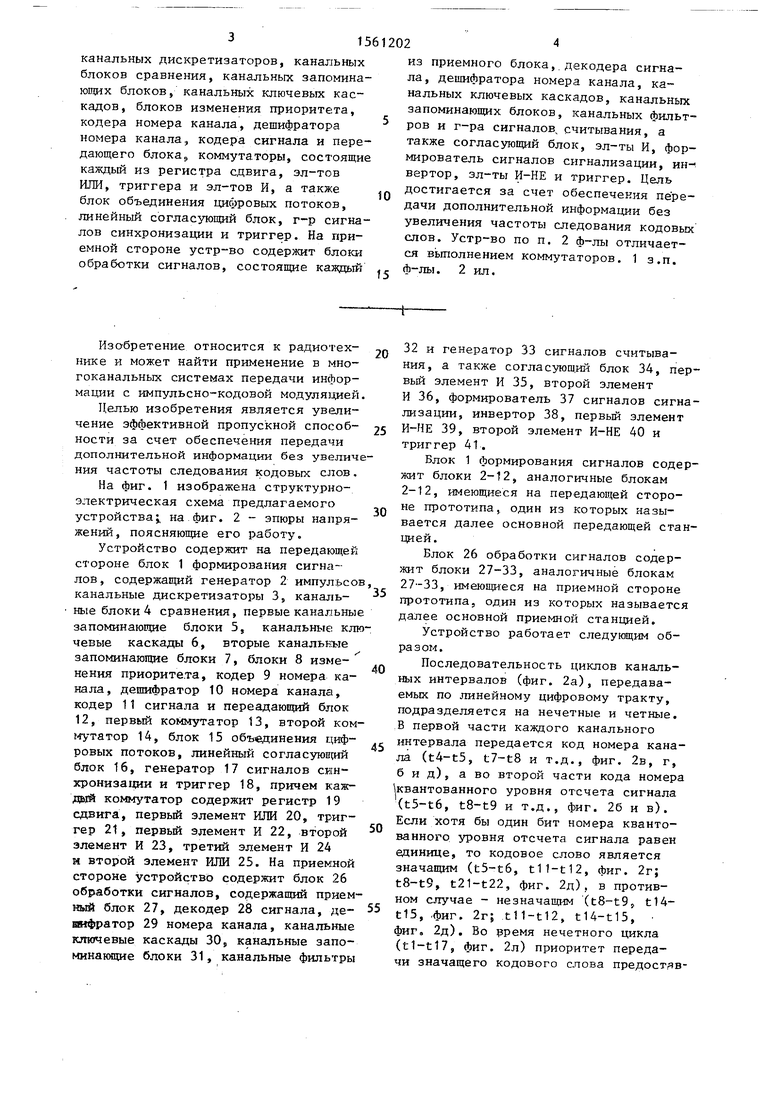

На фиг. 1 изображена структурно- электрическая схема предлагаемого устройства; на фиг. 2 - эпюры напряжений, поясняющие его работу.

Устройство содержит на передающей стороне блок 1 формирования сигналов, содержащий генератор 2 импульсов канальные дискретизаторы 3, канальные блоки 4 сравнения, первые канальные запоминающие блоки 5, канальные ключевые каскады 6, вторые канальмые запоминающие блоки 7, блоки 8 изменения приоритета, кодер 9 номера канала , дешифратор 10 номера канала, кодер 11 сигнала и переедающий блок 12, первый коммутатор 13, второй коммутатор 14, блок 15 объединения цифровых потоков, линейный согласующий блок 16, генератор 17 сигналов синхронизации и триггер 18, причем каждый коммутатор содержит регистр 19 сдвига, первый элемент ИЛИ 20, триггер 21, первый элемент И 22, второй элемент И 23, третий элемент И 24 м второй элемент ИЛИ 25. На приемной стороне устройство содержит блок 26 обработки сигналов, содержащий приемный блок 27, декодер 28 сигнала, де- дафратор 29 номера канала, канальные ключевые каскады 30, канальные запоминающие блоки 31, канальные фильтры

0

5

0

5

0

5

0

5

32 и генератор 33 сигналов считывания, а также согласуюший блок 34, первый элемент И 35, второй элемент И 36, формирователь 37 сигналов сигнализации, инвертор 38, первый элемент И-НЕ 39, второй элемент И-НЕ 40 и триггер 41.

Блок 1 формирования сигналов содержит блоки 2-12, аналогичные блокам 2-12, имеющиеся на передающей стороне прототипа, один из которых называется далее основной передающей станцией.

Блок 26 обработки сигналов содержит блоки 27-33, аналогичные блокам 27-33, имеющиеся на приемной стороне прототипа, один из которых называется далее основной приемной станцией.

Устройство работает следующим образом.

Последовательность циклов канальных интервалов (фиг. 2а), передаваемых по линейному цифровому тракту, подразделяется на нечетные и четные. В первой части каждого канального интервала передается код номера канала (t4-t5, t7-t8 и т.д., фиг. 2в, г, б и д), а во второй части кода номера квантованного уровня отсчета сигнала (t5-t6, t8-t9 и т.д., фиг. 26 и в). Если хотя бы один бит номера квантованного уровня отсчета сигнала равен единице, то кодовое слово является значащим (t5-t6, t11-t12, фиг. 2г; t8-t9, t21-t22, фиг. 2д). в противном случае - незначащим (t8-t9} t14- t15, фиг. 2г; t11-t12, t14-t15, фиг. 2д). Во время нечетного цикла (t1-t17, фиг. 2л) приоритет передачи значащего кодового слова предостявляется основной передающей станции, а на время передачи четного цикла (t17-t32, фиг. 2м) приоритет передачи значащего кодового слова предосталяется блоку 1 формирования сигналов При этом передающая сторона использует поочередно предоставляемый приоритет для передачи значащего кодового слова с данной передающей станции, либо передает право передачи блоку 1 формирования сигналов, если значащее кодовое слово на выходе данной передающей станции отсутствует. Таким образом, передающая сторона может работать в следующих режимах.

В нечетном цикле передачи (t1-t17 фиг. 2л) приоритет предоставляется основной передающей станции и с выхода передающего блока 12, которой в регистр 19 сдвига первого коммутатора 13 записано значащее кодовое слово (t1-t3, t7-t9, фиг. 26). При этом высокий уровень сигнала поступает через первый элемент ИЛИ 20 первого коммутатора 13 на первый вход триггера 21 (t1-t6, t7-t12, фиг. 2е), что обеспечивает установку триггера 21 в единичное состояние сигналом синхронизации (фиг. 2з), поступающим на второй вход триггера 21 в момент времени (t3, t9, фиг. 2и). Высокий уровень сигнала с второго выхода триггера 21 поступает на первый вход второго элемента И 23 и совпадает во времени с высоким уровнем управляющего сигнала, поступающим с первого управляющего входа первого коммутатора 13 на второй вход второго элемента И 23 (t2-t17, фиг. 2л). При этом высокий уровень выходного сигнала второго элемента И- 23 (t4-t6, t9-t12, фиг. 2н) через второй элемент ИЛИ 35 поступает на первый вход третьего элемента И 24 и разрешает передачу через третий элемент И 24 считываемых из регистра 19 сдвига значащих кодовых слов на первый вход блока 15 объединения цифровых потоков (t4-t6, t9-t12, фиг. 2у). При этом перед началом считывания каждого кодового слова из регистра 19 сдвига первого коммутатора 13 в первый считываемый разряд регистра 19 сдвига записывается единица (t3-t4, t9-t10, фиг. 2г). Запись единицы производится сигналом, поступающим с шестого выхода генератора 17 сигналов синхронизации на третий

гистра 19 сдвига первого коммутатора 13. В это же время низкий уровень сигнала с первого выхода триггера 21 первого коммутатора 13 создает на выходе первого элемента И 22 низкий уровень сигнала (t4-t6, t9-t12, фиг.2о), который поступает на второй вход второго элемента ИЛИ 25 второго коммутатора 14 и запрещает (t4-t6, фиг, 2ф) передачу значащего кодового слова, считываемого из регистра 19 сдвига второго коммутатора 14 через третий элемент И 24 на второй вход

с блока 15 объединения цифровых потоков.

В нечетном цикле передачи (t1-t17, фиг. 26) с выхода передающего блока 12 основной передающей станции в ре0 гистр 19 сдвига за время канального интервала записывается незначащее кодовое слово (t4-t6, фиг. 26). При этом низкие уровни сигналов со всех выходов регистра 19 сдвига поступают

5 на входы первого элемента ИЛИ 20

(t6-t7 фиг. 2е), что позволяет сигналу синхронизации (фиг. 2з), поступающему на первый вход триггера 21 первого коммутатора 13, установить триггер 21 в нулевое состояние (t6-t9, фиг. 2и). Низкий уровень сигнала с второго выхода триггера 21 поступает на первый вход второго элемента И 22. При этом низкий уровень выходного сигнала второго элемента И 22 (t6-t9, фиг. 2н) поступает на первый вход второго элемента ИЛИ 25 первого коммутатора 13, на втором входе которого действует низкий выходной уровень сигнала первого элемента И 22 второго коммутатора 14 (tO-t25, фиг. 2р), поэтому на выходе второго элемента ИЛИ 25 первого коммутатора 13 действует низкий уровень (t6-t9, фиг.2с), который поступает на первый вход третьего элемента И 24 и запрещает передачу кодового слова на информа- ционный выход коммутатора 13. В это же время высокий уровень сигнала с первого выхода триггера 21 первого коммутатора 13 поступает на первый вход первого элемента И 22, на втором входе которого действует высокий уровень сигнала в течение всего времени передачи нечетного цикла (t1- t17, фиг. 2л), поэтому создается высокий уровень выходного сигнала первого элемента И 22 (t6-t9, фиг.2о), который во втором коммутаторе 14 по0

5

0

5

0

5

ступает через второй элемент ИЛИ 25 на первый вход третьего элемента И 24 и разрешает передачу значащего кодового слова, считываемого из регистра 19 сдвига второго коммутатора 14, на второй вход блока 15 объединения цифровых потоков (t7-t9, фиг. 2ф). При этом перед началом считывания значащего кодового слова в первый считываемый разряд регистра 19 сдвига второго коммутатора 14 записывается нулевое значение элемента кодового слова (t6-t7, фиг. 2д). Запись нуля производится сигналом, поступающим с седьмого выхода генератора 17 сигналов синхронизации на третий вход регистра 19 сдвига второго коммутатора 14. Таким образом, за время передачи нечетного цикла с выхода блока 15 объединения цифровых потоков через согласующий блок 16 в линию связи поступит цифровой поток (фиг„2х), содержащий сигнал синхронизации (t l-t3) значащие кодовые слова, передаваемые с основной передающей станции (t3-t6, t9-t12) и значащие (t6-t9), а также незначащие кодовые слова (t13-t15 и т.д.), передаваемые с блока 1 формирования сигналов.

В четном цикле передачи (t17-t32, фиг. 2м) приоритет передачи значащих кодовых слов предоставляется блоку 1 формирования сигналов, с выхода передающего блока 12 которой в регистр 19 сдвига второго коммутатора 14 записано значащее кодовое слово (t17-t19, t20-t.22, фиг. 2в). При этом высокий уровень сигнала поступает через первый элемент ИЛИ 20 второго коммутатора 14 на второй вход триггера 21 (t17-t25, фиг, 2ж), что обеспечивает установку триггера 21 в единичное состояние сигналом синхронизации (фиг. 2з), наступающим на первый вход триггера 21, в моменты времени (t19, t22, фиг. 2к). Высокий уровень сигнала с второго выхода триггера 21 поступает на первый вход второго элемента И 23 и совпадает во времени с высоким уровнем управляющего сигнала, действующим на первом управляющем входе второго коммутатора 14 и втором входе второго элемента И 23 (t17-t32, фиг.2м). При этом высокий уровень выходного сигнала второго элемента И 2.3. (t 19- t25, фиг. 2п) через второй элемент ИЛИ 25 (t19-t25, фиг. 2т) поступает

0

5

0

5

0

5

0

5

на первый вход третьего элемента И 24 и разрешает передачу через третий элемент И 24 считываемых из регистра 19 сдвига значащих кодовых слов на второй вход блока 15 объединения цифровых потоков (t19-t25, фиг. 2ф). В это же время во втором коммутаторе 14 низкий уровень сигнала с первого выхода триггера 21 создает на выходе первого элемента И 22 низкий уровень сигнала (t19-t25, фиг„ 2р), который поступает на второй вход второго элемента ИЛИ 25 первого коммутатора 13 и запрещает (t19-t22, фиг. 2с) передачу значаше- го слова, считываемого из регистра 19 сдвига первого коммутатора 13, через третий элемент И 24 на первый вход блока 15 объединения цифровых потоков.

В четном цикле передачи (t17-t32, фиг. 2в) с выхода передающего блока 12 блока 1 формирования сигналов в регистр 19 сдвига за время канального интервала записывается незначащее кодовое слово (t22-t25, t25-t28, фиг. 2в). При этом низкие уровни сигнала со всех выходов регистра 19 сдвига поступают на входы первого элемента ИЛИ 20 второго коммутатора 14 и низкий уровень выходного сигнала первого элемента ИЛИ 20 (t25-t26, фиг. 2ж) позволяет сигналу синхронизации (фиг.2з), поступающему на первый вход триггера 21 второго коммутатора 14, установить триггер 21 в нулевое состояние (t25-t32, фиг. 2к). При этом низкий уровень сигнала с второго выхода триггера 21 поступает на первый вход второго элемента И 23 и низкий выходной уровень второго элемента И 23 (t25-t32, фиг. 2п) поступает на первый вход второго элемента ИЛИ 25 второго коммутатора 14, а на втором входе второго элемента ИЛИ 25 действует низкий выходной уровень сигнала первого элемента И 22 первого коммутатора 13 (t17-1:32, фиг.2о) поэтому на выходе второго элемента ИЛИ 35 второго коммутатора 14 действует низкий уровень (t25-t32, фиг. -2т), который поступает на первый вход третьего элемента И 24 и запрещает передачу кодового слова на выход второго коммутатора 14. В то же время высокий уровень сигнала с первого выхода триггера 21 второго коммутатора 14 поступает на

первый вход первого элемента И 22, на втором входе которого действует высокий уровень сигнала в течение всего времени передачи четного цикла (t17-t32, фиг. 2м), поэтому создается высокий уровень выходного синала первого элемента И 22 (t25-t32, фиг. 2р), который поступает в первый коммутатор 13 через второй элемент ИЛИ 25, на первый вход третьего элемента И 24 и разрешает передачу значащего кодового слова (t25-t28, фиг. 2у) и незначащего кодового слова (t28-t31, фиг. 2у)о Таким образом за время передачи четного цикла с выхода блока 15 объединения цифровых потоков через согласующий блок 16 в лини связи поступит цифровой поток (фиг. 2х), содержащий сигнал синхронизации (t17-t19), все значащие кодовоые слова, передаваемые с блока 1 формирования сигнала (t20- t25) и значащие (t25-t28) и незначащие (t28-t31) кодовые слова, передаваемые основной передающей станцией.

Приемная сторона устройства может работать в двух режимах.

На вход согласующего блока 34 по линии связи поступает цифровой линейный сигнал (фиг.2х), из которого выделяется сигнал синхронизации (t2-t4, t17-t19, фиг. 2х) и подается на второй выход согласующего блока 34 на первый выход которого поступает только цифровой поток кодовых слов, передаваемых основной передающей станцией и блоком 1 формирования сигнала. При приеме в канальном интервале кодового слова с основной передающей станции, на втором входе первого элемента И-НЕ 39 действует высокий уровень сигнала (t3-t4, t9-t10., t25-t26, t28-t29, фиг. 2х), который совпадает в указанные интервалы времени с сигналом синхронизации (фиг.2ц), поступающим с первого выхода формирователя 37 сигналов синхронизации, на входы элементов И-НЕ 39 и 40. При этом на выходе первого элемента И-НЕ 39 в моменты совпадений указанных сигналов появляется низкий уровень сигнала (фиг. 2ч), который поступает на второй вход триггера 41 и устанавливает последний в единичное состояние (t3- t6, t9-t12fi t25-t31, фиг. 2щ). Высокий уровень сигнала с второго выхода триггера 41 поступает на второй вход

г,

561202

10

10

20

25

первого элемента И35 и разрешает передачу с выхода согласующего блока 34 через первый элемент И35 на вход приемного блока 27 основной приемной станции кодовых слов, передаваемых с основной передающей станции (фиго 2ю).

При приеме в канальном интервале кодового слова, передаваемого с блока 1 формирования сигналов на первый вход г второго элемента И-НЕ40 через инвертор 38, поступает высокий уровень сигнала, который при совпадении .г с сигналом синхронизации (фиг. 2ц), действующим на втором входе второго элемента И-НЕ 40, создает на первом входе триггера 41 низкий уровень сигнала (tO-tl, t6-t7, t12-t13 и т.д., фиг. 2ш). При этом триггер 41 устанавливается в нулевое состояние, высокий уровень сигнала ,с первого выхода триггера 41 поступает на первый вход второго элемента И 36 (фиг. 2э) и разрешает передачу с выхода согласующего блока 34 через второй элемент И 36 на вход приемного блока 27 блока 26 обработки сигналов кодовых слов, передаваемых с блока 1 формирования сигналов (фиг3 2я)0

Формула изобретения

1 „ Многоканальное устройство с импульсно-кодовой модуляцией и временным делением каналов по авт.ев„ № 547033, отличающееся тем, что, с целью увеличения эффективной пропускной способности за счет обеспечения передачи дополнительной информации без увеличения частоты следования кодовых слов, на передающей стороне введены два коммутатора, блок формирования сигналов, последовательно соединенные блок объединения цифровых потоков и согласующий блок, последовательно соединенные генератор сигналов синхронизации и триггер, выходы которого подключены к первым управляющим входам коммутаторов, информационные выходы которых соединены с первым и вторым входами блока объединения цифровых потоков, выходы передающего блока и блока формирования сигналов подключены к информационным входам соответственно первого и второго коммутаторов, второй, третий, четвертый, пятый, шестой и седьмой управляющие выходы генерато30

35

40

45

50

55

11

pa сигналов синхронизации соединены соответственно с вторым входом блока объединения цифровых потоков, вкодом генератора импульсов, вторыми и третьими управляющими входами первого и второго коммутаторов, четвертым управляющим входом первого коммутатора и четвертым управляющим входом второго коммутатора, управляющий выход и пятый управляющий вход которого соединены соответственно с пятым управляющим входом и управляющим выходом первого коммутатора, третий выход генератора сигналов синхронизации подключен к входу блока формирования сигналов, а на приемной стороне введены последовательно соединенные согласующий блок и первый элемент И, последовательно соединенные формирователь сигналов синхронизации и первый элемент И-НЕ, последовательно соединенные инвертор, второй элемент И-НЕ, триггер, второй элемент И и блок обработки сигналов, второй вход которого соединен с входом генератора импульсов считывания и вторым .выходом формирователя сигналов синхронизации, первый выход и вход которого соединены соответственно с вторым входом второго элемента И-НЕ и вторым выходом согласующего блока, первый выход которого подключен к второму входу второго элемента И, входу инвертора и второму входу первого эле120212

мента И-НЕ, выход которого подключен к второму входу триггера, второй выход которого подключен к второму входу первого элемента И, выход которого подключен к входу приемного блока.

2. Устройство по п. 1,

о т л и

чающееся тем, что каждый

5

0

коммутатор содержит регистр сдвига, последовательно соединенные первый

элемент ИЛИ, триггер и первый элемент И, последовательно соединенные вто- рой элемент И, второй элемент ИЛИ и третий элемент И, причем второй выход триггера подключен к первому входу второго элемента И, второй вход которого соединен с вторым входом первого элемента И, один выход регистра сдвига подключен к второму входу третьего элемента И, а другие выходы - к входам первого элемента ИЛИ, выходы первого и треть- - его элементов И являются управляющим и информационными выходами коммутатора, информационным и первым, вторым, третьим, четвертым и пятым управляющими входами которого являются соответственно первый вход регистра сдвига, второй вход первого элемента И, второй вход регистра сдвига, второй вход триггера, третий вход регистра сдвига и второй вход второго элемента ИЛИ.

0

-J 11 u i-гт/ u i-i i j i / u ii i /

JTrFirrtirL-TL-TL- JlJlTTTLTll-rL-rL.

,N H И L-й I И ff pf

I

-J

1 Ц L-M i /Й L,

fU ifiTLJL, TJLJ L

ifBiL

I

J 11 J I

ц-ит

ff pf

ifBiL

ц-ит

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ИДЕНТИФИКАЦИИ ЧЕЛОВЕКА-ОПЕРАТОРА | 1994 |

|

RU2075777C1 |

| Устройство для передачи и приема информации | 1988 |

|

SU1520571A1 |

| Устройство для передачи и приема информации | 1990 |

|

SU1837348A1 |

| СИГНАЛИЗАТОР ОБЛЕДЕНЕНИЯ | 2022 |

|

RU2791724C1 |

| УСТРОЙСТВО ДЛЯ ВОССТАНОВЛЕНИЯ ЭЛЕКТРОКАРДИОСИГНАЛА | 1997 |

|

RU2122280C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1991 |

|

SU1832976A1 |

| Генератор псевдослучайных последовательностей | 1988 |

|

SU1626345A2 |

| ПРИЕМНИК РУЛОННОГО ТЕЛЕГРАФНОГО АППАРАТА | 1990 |

|

RU2017338C1 |

| БЛОК СДВИГОВОГО РЕГИСТРА, ВОЗБУЖДАЮЩАЯ СХЕМА ЗАТВОРА И УСТРОЙСТВО ОТОБРАЖЕНИЯ | 2019 |

|

RU2740162C1 |

| Устройство для деления двоичных чисел | 1985 |

|

SU1270758A1 |

Изобретение относится к радиотехнике. Цель изобретения - увеличение эффективной пропускной способности. Устройство содержит на передающей стороне блоки формирования 1 сигналов, состоящие каждый из генератора импульсов, канальных дискретизаторов, канальных блоков сравнения, канальных запоминающих блоков, канальных ключевых каскадов, блоков изменения приоритета, кодера номера канала, дешифратора номера канала, кодера сигнала и передающего блока, коммутаторы, состоящие каждый из регистра сдвига, элементов ИЛИ, триггера и элементов И, а также блок объединения цифровых потоков, линейный согласующий блок, генератор сигналов синхронизации и триггер. На приемной стороне устройство содержит блоки обработки сигналов, состоящие каждый из приемного блока, декодера сигнала, дешифратор номера канала, канальных ключевых каскадов, канальных запоминающих блоков, канальных фильтров и генератора сигналов считывания, а также согласующий блок, элементы И, формирователь сигналов сигнализации, инвертор, элементы И-НЕ и триггер. Цель достигается за счет обеспечения передачи дополнительной информации без увеличения частоты следования кодовых слов. Устройство по п.2 ф-лы отличается выполнением коммутаторов. 1 з.п. ф-лы, 2 ил.

.JTF PL, i izu ГП--

-Jf q ifij i2B 1/iTL. -ГТ ЛППТТТТ

ЛЛП,. l7uT7i

ЪЪ ft fS t7 13 Ht Ш ttt t1S iti t2t t22 Ш t25 /27/2 t3f

tits ts «6 ta tta tt3 tis ttrtfs tzi ютштш1&.

Фи&.2

I 11

I I I II

| Многоканальное устройство с импульснокодовой модуляцией и временным делением каналов | 1975 |

|

SU547033A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-04-30—Публикация

1988-05-07—Подача