26 и образования новых функциональных

связей. Генератор содержит также блоки 1 и 2 коррекции, блок 3 счета суммы, элементы задержки А, 5 и 12. блоки 6 и 7 смета симпоппп, регистры 8, 9 и 10, шину 11

Пуск, шину 13 тактовых импульсов, генератор 14 псевдослучайностей последовательности, элемент НЕ 15, элемент ИЛИ 16 и генератор 17 одиночных импульсов. 3 з.п ф-лы, 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ОШИБОК | 2008 |

|

RU2390943C1 |

| Устройство для формирования тестов | 1990 |

|

SU1795462A1 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ В СИСТЕМАХ С КОДОВЫМ РАЗДЕЛЕНИЕМ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2001 |

|

RU2234191C2 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Генератор псевдослучайной последовательности импульсов | 1989 |

|

SU1735846A1 |

| Устройство для формирования тестов | 1987 |

|

SU1429121A1 |

| Устройство для определения времени задержки последовательностей | 1987 |

|

SU1431044A1 |

| Устройство для задания тестовых воздействий | 1988 |

|

SU1541614A1 |

| Устройство для имитации информационных каналов | 1986 |

|

SU1386996A1 |

| Устройство для формирования тестов | 1985 |

|

SU1297059A1 |

Изобретение относится к импульсной технике. Цель изобретенил - расширение функциональных возможностей за счет генерации псевдослучайной последовательности кода Фибоначчи. Цель достигается введением а генератор псевдослучайных последовательностей двух регистров 18 и 20 сдвига, блоков 19, 22 и 24 коррекции, дешифратора 21, блока 23 счета, регистров 25,

Изобретение относится к импульсной технике, может быть использовано о информационно-измерительной технике и является усовершенствованием изобретения по авт. св. № 1378026

Цель изобретения расширение функциональных возможностей за счет генерации (км од , n liKi i поглг довател ног.ти кода

1 nf Of г. Ч

I, ч „и 1 представлена структурна i -MI ii4(( кпч гхема генератора псевдослу чайных тхледовглельностей нл фиг. 2 электричесше Функциональные Слемы при мероо конкретной реализации третьего четвертого и пятого блоков коррекции соответственно

Генератор псевдослучайных последова- темьноглей содержит первый блок 1 коррекции, первый вход которого соединен с выходом второю блока 2 коррекции и с первым блока 3 счета суммы первый -ломе.и :пдоржк1/ выход которого соеди- jii о г пдом второго элемента 5 зрдерккп, с первыми в/одами первого и второго блоков б и 7 счета символов, первый, второй и третий регистры 8, 9 и 10, входы которых соединены с шиной 1 1 Пуск, третий элемент 12 задержки, шину 13 тактовых импульсов, соединенную с входом синхронизации генератора 14 псевдослучайной последовательности выход которого соедино) с входом элемента НЕ 15, последовательно соединенные элемент ИЛИ 16 и юнератор 17 одиночных импульсов, последовательно соединенные первый регистр 18 сдвига, третий блок 19 коррекции, второй регистр 20 сдвига, дешифратор 21, четвертый блок 22 коррекции блок 23 счета и пятый блок 24 коррекции вторая и третья f руппы входов которого соединены с соответствующими выходами четвертого и пятого регистров 25 и 26, входы синхронизации которых соединены с шиной 13 тактовых импульсов, с входами первого элемента 4 задержки с входом синхронизации первого регистра 18 сдвига, с входом синхронизации третьего блока 19 коррекции, с входом синхронизации второго регистра 20 сдвига, с входами синфонизации четвертого и пятого блоков 22 и 24 коррекции и с третьим входом блока 23 счета, второй вход которого соединен с выходом пятого блока 24 оррекции, первый вход которого соединен с четвертым входом четвертого блока 22 коррекции и с третьим входом третьего блока 19 коррекции, выход которого соединен с

третьим входом четвертого блока 22 коррекции, выход которого соединен с вторым входом пятого блока 24 коррекции. Шина 11 Пуск соединена с входами четвертого и пятого регистров 25 и 26 с вторым входом

второго блока 7 счета символов, с вторым входом первого блока 6 счета символов, с вторым входом блока 3 счета суммы и с входом генератора 14 псевдослучайной последовательности, выход которого соединем с третьим входом второго блока 7 счета символов и с первым влодом второго блока 2 коррекции, второй вход которого соединен с третьим входом первого блока 6 счета символов с выходом второго блока 7 счета

символов и с первым входом элемента ИЛИ 16 второй вход которого соединен с четвертым входом второю блока 7 счета символов, с выходом первою б/,ока Ь счета символов и с третьим входом второго блока 2 коррекции четвертый вход которого соединен с третьим входом блока 3 счета суммы, с выходом второго элемента 5 задержки и с входом третьего элемента 12 задержки выход когорогосоединен с вторым входом первого

блока 1 коррекции третий к четвертый входы которого соединены с первым и вторым выходами блока 3 счета суммы группа входов которого соединена с выходами первого регистра 8

Выходы третьего регистра 10 соединены с группой входов второго блока 7 счета символов, пятый вход которого соединен с выходом генератора 17 одиночных импульсов и с четвертым входом первого блока 6

счета символов, пятый вход КОТОРОГО соединен с выходом элемента НЕ 15 Выходы второго регистра 9 соединены с группой входов первого блока 6 счета символов. Выход первого блока 1 коррекции соединен с информационным входом первого регистра 18 сдвига и с четвертым входом третьего блока 19 коррекции, второй вход которого соединен с вторым выходом первого регистра 18 сдвига.

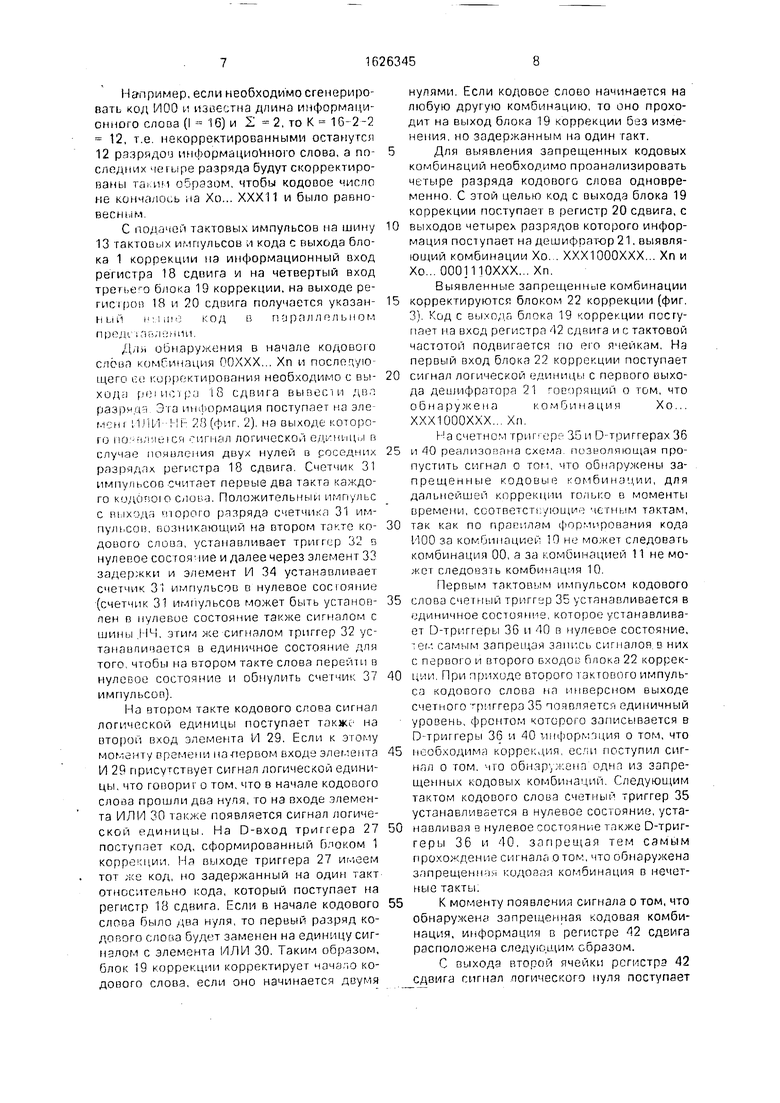

Третий блок 19 коррекции (фиг. 2) содержит D-триггер 27, последовательно соединенные элемент ИЛИ-НЕ 28. пероый

элемент и 29 и элемент ИЛИ 30, последовательно соединенные счетчик 31 импульсов, триггер 32, элемент 33 задержки и второй элемент И 34, выход которого соединен с установочным входом счетчика 31 импульсов, входсинхронизации которого соединен с входом синхронизации D-триггера 27 и является входом синхронизации третьего блока 19 коррекции, четвертый вход которого соединен с информационным входом D- триггера 27, выход которого соединен с вторым входом элемента ИЛИ 30, выход которого является выходом третьего блока 19 коррекции, первый и второй входы которого соединены с входами элемента ИЛИ-НЕ 28. Третий вход третьего блока 19 коррекции соединен с вторым входом второго элемента И 34 и с вторым входом триггера 32, первый вход которого соединен с вторым входом первого элемента И 29.

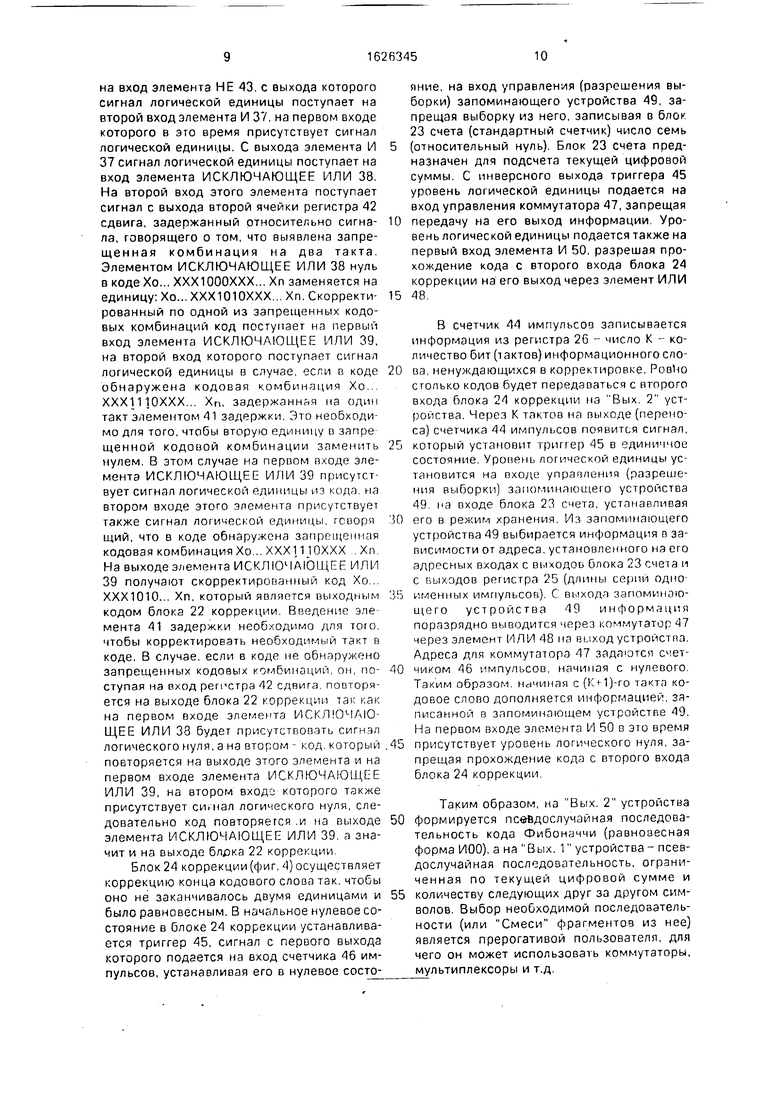

Четвертый блок 22 коррекции (фиг. 3) содержит последовательно соединенные счетный триггер 35, первый D-триггер 36. элемент И 37, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 38 и второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 39 последовательно соединенные второй D-триггер 40 и элемент 41 задержки, последовательно соединенные регистр 42 сдвига и элемент НЕ 43. выход которого соединен с вторым входом элемента И 37 Выход элемента 41 задержки соединен с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 39, выход которого является выходом четвертого блока 22 коррекции, первый вход которого соединен с информационным входом первого D-триггера 36, вход синхронизации которого соединен с входом синхронизации второго D-триггера 40 и с вторым выходом сметного триггера 35, вход синхронизации которого является входом синхронизации чет пергого блока 22 коррекции и соединен с входом синхронизации регистра 42 сдвига, информационный вход которого является третьим входом четвертого блока 22 коррекции, второй вход которого соединен с информационным входом второго D-триггера 40, вход установки которого соединен с первым выходом считного триггера 35, вход установки которого является четвертым входом четвертого блока 22 коррекции. Выход регистра 42 сдвига соединен с вторым входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 38.

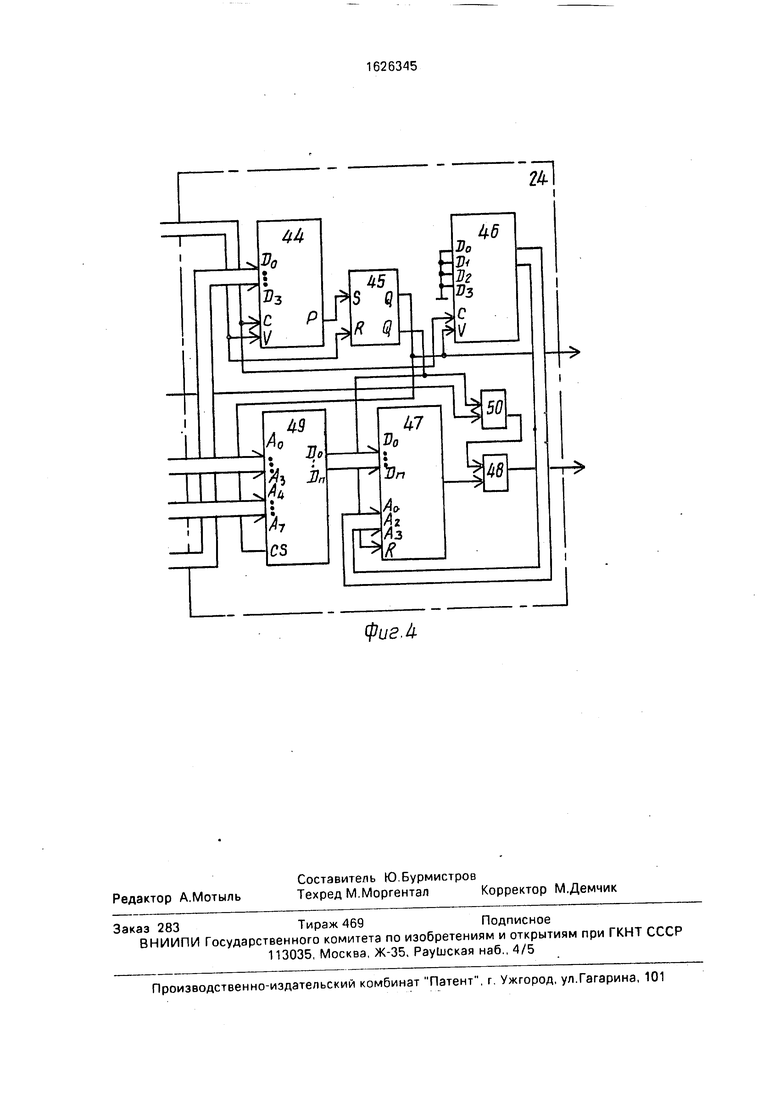

Пятый блок 24 коррекции (фиг. 4) содержит последовательно соединенные первый счетчик 44 импульсов, триггер 45, второй счетчик 46 импульсов, коммутатор 47 и элемент ИЛИ 48, запоминающее устройство 49

и элемент И 50, первый вход которого соединен с вторым выходом триггера 45 и с выходом управления коммутатора 47, информационные входы которого соединены с соответствующими выходами запоминающего устройства 49, вход управления которого соединен с выходом пятого блока 24 коррекции и с первым выходом триггера 45. второй вход которого соединен с входом

управления первого счетчика 44 импульсов и является первым входом пятого блока 24 коррекции, вход синхронизации которого соединен с входом синхронизации второго счетчика 46 импульсов и с входом синхронизации первого счетчика 44 импульсов, группа входов которого является третьей группой входов пятого блока 24 коррекции, первая и вторая группа входов которого соединена с соответствующими адресными

входами запоминающего устройства 24 Второй вход пятого блока 24 коррекции соединен с вторым входом элемента И 50, выход которого соединен с вторым входом элемента ИЛИ 48.

Генератор псевдослучайных последовательностей работает следующим образом

Для кода И 00. формируемого блоком 24 коррекции (см. Вых 2 на фиг .существуют следующие условия, кодовое слово не

может начинаться ООХХХ; кодовое слово не может начинаться ХХХ11; в любом информационном потоке не могуг встречаться комбинации Хо . ХХХЮООХХХ . Хп и Хо... 1110ХХХ... Хп (X - любое принимаемое значение О или 1, знаком - подчеркнуты четные разряды, Хо - младший разряд кодо-. вого слова, Хп - старший разряд кодового слова), для чего блок 2 коррекции производит коррекцию начала кодового слова, дешифратор 21 выявляет запрещенные кодовые комбинации, блок 22 коррекции корректирует выявленные запрещенные кодовые комбинации, а блок 24 коррекции корректирует конец кодового слова и делает

его равновесным. Перед началом работы все элементы и узлы устройства устанавливаются в заданное исходное состояние (цепи не показаны).

При подаче на шину 11- Пуск положительного импульса производится запись информации в первый 8 и второй 9 регистры. При этом в первый регистр 8 записывается длина серий одноименных импульсов, а во

второй регистр 9 записывается величина К I -2-2, где К-число бит информационного слова, не нуждающихся в корректировке; I - длина информационного слова; 2 - текущая цифровая сумма для заданного кода.

Например, если необходимо сгенерировать код ИОО и известна длина информационного слова (I 16) и 2 2, то К 16-2-2 12, те некорректированными останутся

12разрядов информационною слова, а последних четыре разряда будут скорректированы таг им образом, чтобы кодовое чигпо не кончалось на Хо . ХХХ11 и было равно- вегш IM

С подачей тактовых импульсов на шину

13тактовых импульсов и кода с выхода блока 1 коррекции на информационный вход регистра 18 сдвига и на четвертый вход треп-е о блока 19 коррекции, на выходе ре- гисфов 18 и 20 сдвига получается указанный I MI- год ь параллельном

ПРРД . , if-,l 1ЧИ

обнаружения в начале кодового слоьа комгинация ПОХХХ Хп и поелоч/ю щего го корректирования необходимо с выход 1 ptMiioipa 18 сдвига вывеет дв : i Oia информация поступает на эле f.nfliHl1 U 2В (фиг 2) на выходекоторо- ru no i 4jiC4 сигнал логической е/уницы в случае появления двух нулей в соседних разрядах регистра 18 сдвига Счетчик 31 импульсов считает первые два такта каждого кодовою слоь-з Положительным с FU ix vi t торою разряда счетчика 31 им- nyju сов возникающий на втором кодового слоит устанавливает триггер 32 п нулевое состоя те и далее через элемент 33 задержки и элемент И 34 устанавливает счетчик 3 импульсов в нулевое сосюяние (счетчик 31 импульсов может быть установлен в нулевое состояние также сигналом с шины И Ч этим же сигналом триггер 32 устанавливается в единичное состояние для того чтобы на втором такте слова перейти в нулевое состояние и обнулить счетчик 37 импульсов)

На втором такте кодового слова сигнал логической единицы поступает такии на второй вход элемента И 29. Если к этому моменту времени на первом входе элеменга И 2Р присутствует сигнал логической единицы что говори о том что в начале кодового слова прошли два нупя, го на входе элемента ИЛИ 30 также появляется сигнал логической единицы На D-вход триггера 27 поступает код, сформированный бгюком 1 коррекции На выходе триггера 27 имеем тот код, но задержанный на один такт относительно кода, который поступает на регистр 18 сдвига Если в начале кодового слова было два нуля то первый разряд кодового слова будет заменен на единицу сигналом с элемента ИЛИ 30 Таким образом, блок 19 коррекции корректирует чача .о кодового слова, если оно начинается двумя

нулями Если кодовое слово начинается на любую другую комбинацию, то оно проходит на выход блока 19 коррекции без изменения но задержанным на один такт.

Для выявления запрещенных кодовых

комбинаций необходимо проанализировать четыре разряда кодового слова одновременно С этой целью код с выхода блока 19 коррекции поступав в регистр 20 сдвига, с

0 выходов четырех разрядов которого информация поступает на дешифратор 21. выявляющий комбинации Хо ХХХ1000ХХХ Хпи Хо 0001110ХХХ. Хп

Выявленные запрещенные комбинации

5 корректируются блоком 22 коррекции (фиг 3) Код с вывода блпка 19 коррекции поступает на вход регистра 12 сдвига и с тактовой частотой подвигается по PIO ячейкам На первый вход блока 22 коррекции поступает

0 сигнал логической единицы с первого выхода дешифратора 21 горорящии о том, что обнаруженакомбинацияX о

ХХХ1000ХХХ Хп

На счетном грпг ер 35 и D триггерах 36

5 и 40 реализо 1Гша схема позволяющая пропустить сигнал о топ что обнаружены запрещенные кодовые омбинэции, для дальнейшей коррекции только в моменты времени, ссответст) лощи четным тактам,

0 так как по правилам формирования кода 1100 за комбинацией 10 н мо кет следовать комбинация 00 а за юмбинацией 11 не может следовать комбинация 10

Первым тактовь м импульсом кодового

5 слова СЧРТНЫИ триггер 35 устанавливается в единичное состояние которое устанавливает D-трнггеры 36 и 40 в нулевое состояние, -ег самым запрещая зашть сигналов в них с nepooi о и второго входов блока 22 коррек0 ции При приходе втооого тактового импульса кодового слова на инверсном выходе счетного грчггерз 35 почвпяетсл единичный уровень фронтом которого записывается в D триггеры 36 и 40 гыформтция о том, что

5 пгсбчодима коррекция ес .и поступил сигнал о том ire обнчр; ант однт из запрещенных кодовых комбинаций Следующим тактом кодового слова счетный триггер 35 устанавливается в нулевое сосюяние, уста0 навливая в нулевое состояние т ткже D-триг- г е р ы 36 и 40, запрещая тем самым прохождение cm нала о том, что обнаружена запрещенн н кодовая комбинация в нечетные такты.

5К моменту появления сигнала о том, что

обнаружена запрещенная кодовая комбинация, информация в регистре Л2 сдвига расположена следующим образом.

С выхода второй ячейки регистра 42 сдвига сигнал логического нуля поступает

на вход элемента НЕ 43, с выхода которого сигнал логической единицы поступает на второй вход элемента И 37, на первом входе которого в это время присутствует сигнал логической единицы. С выхода элемента И 37 сигнал логической единицы поступает на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 38. На второй вход этого элемента поступает сигнал с выхода второй ячейки регистра 42 сдвига, задержанный относительно сигнала, говорящего о том, что выявлена запрещенная комбинация на два такта. Элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 38 нуль в коде Хо... ХХХ1000ХХХ... Хп заменяется на единицу: Хо... ХХХ1010ХХХ... Хп. Скорректированный по одной из запрещенных кодовых комбинаций код поступает на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 39, на второй вход которого поступает сигнал логической единицы в случае, если в коде обнаружена кодовая комбинация Хо.. ХХХ1110ХХХ... Хп, задержанная на один такт элементом 41 задержки. Это необходимо для того, чтобы вторую единицу в запре щенной кодовой комбинации заменить нулем. В этом случае на первом входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 39 присутствует сигнал логической единицы из кода на втором входе этого элемента присутствует также сигнал логической единицы, говоря щий, что в коде обнаружена запрещенная кодовая комбинация Хо .. XXX1110ХХХ Хп На выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 39 получают скорректированный код Хо.. ХХХ1010... Хп, который является выходным кодом блока 22 коррекции. Введение элемента 41 задержки необходимо для тою, чтобы корректировать необходимый такт в коде. В случае, если в коде не обнаружено запрещенных кодовых комбинаций, он, поступая на вход регистра 42 сдвига, повторяется на выходе блока 22 коррекции так как на первом входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 38 будет присутствовать сигнал логического нуля, а на втором - код который повторяется на выходе этого элемента и на первом входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 39, на втором входо которого также присутствует сигнал логического нуля, следовательно код повторяется .и на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 39, а значит и на выходе блрка 22 коррекции

Блок 24 коррекции (фиг. 4) осуществляет коррекцию конца кодового слова так. чтобы оно не заканчивалось двумя единицами и было равновесным. В начальное нулевое состояние в блоке 24 коррекции устанавливается триггер 45, сигнал с первого выхода которого подается на вход счетчика 46 импульсов, устанавливая его в нулевое состояние, на вход управления (разрешения выборки) запоминающего устройства 49, запрещая выборку из него, записывая в блок 23 счета (стандартный счетчик) число семь

(относительный нуль). Блок 23 счета предназначен для подсчета текущей цифровой суммы. С инверсного выхода триггера 45 уровень логической единицы подается на вход управления коммутатора 47, запрещая

передачу на его выход информации. Уровень логической единицы подается также на первый вход элемента И 50, разрешая прохождение кода с второго входа блока 24 коррекции на его выход через элемент ИЛИ

В счетчик 44 импульсов записывается информация из регистра 26 - число К - количество бит (тактов) информационного слова, ненуждающихся в корректировке. Ровно столько кодов будет передаваться с второго входа блока 24 коррекции на Вых. 2 устройства. Через К тактов на выходе (переноса) счетчика 44 импульсов появится сигнал,

который установит триггер 45 в единичное состояние. Уровень логической единицы установится на входе управления (разрешения выборки) запоминающего устройства 49 на входе блока 23 счета, устанавливая

его в режим хранения. Из запоминающего устройства 49 выбирается информация в зависимости от адреса, установленного на его адресных входах с выходов блока 23 счета и с выходов регистра 25 (длины серии одноименных импульсов). С выхода запоминающего устройства 49 информация поразрядно выводится через коммутатор 47 через элемент ИЛИ 48 на выход устройства. Адреса для коммутатора 47 задаются счетчиком 46 импульсов, начиная с нулевого. Таким образом, начиная с (КН)-го такта кодовое слово дополняется информацией, записанной в запоминающем устройстве 49. На первом входе элемента И 50 в это время

присутствует уровень логического нуля, запрещая прохождение кода с второго входа блока 24 коррекции

Таким образом, на Вых. 2 устройства формируется псевдослучайная последовательность кода Фибоначчи (равновесная форма ИОО), а на Вых. 1 устройства - псевдослучайная последовательность, ограниченная по текущей цифровой сумме и количеству следующих друг за другом символов. Выбор необходимой последовательности (или Смеси фрагментов из нее) является прерогативой пользователя, для чего он может использовать коммутаторы, мультиплексоры и т.д.

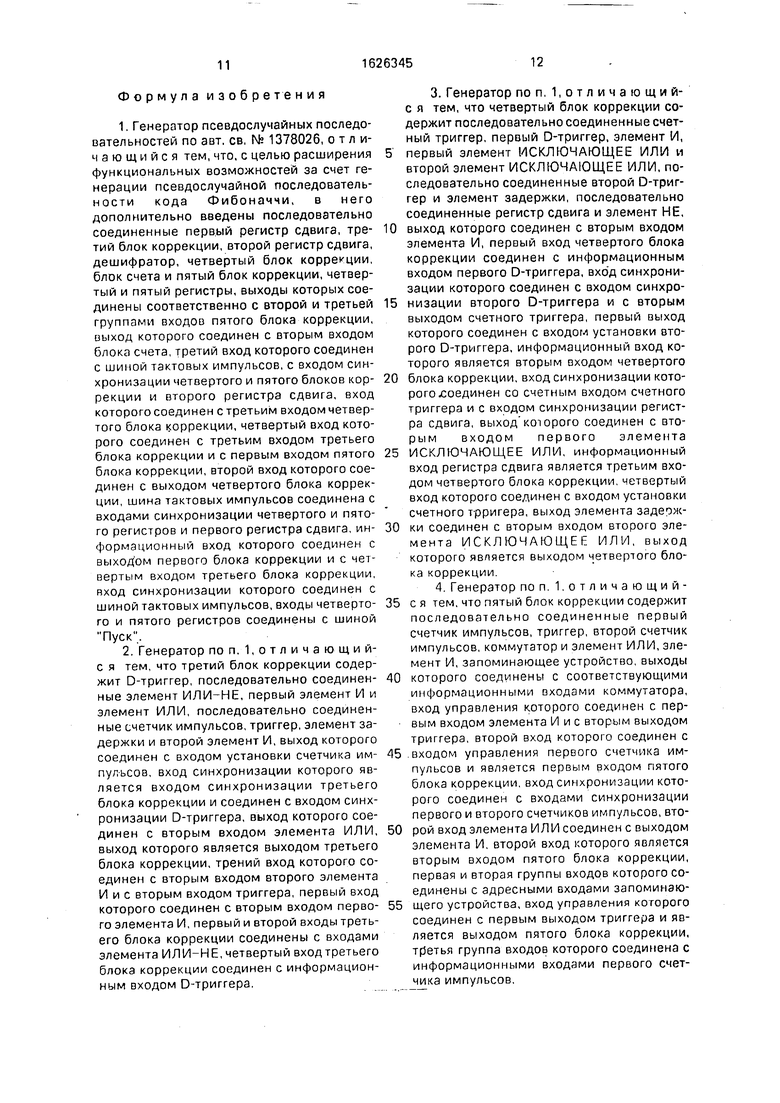

Формула изобретения

первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, последовательно соединенные второй D-триггер и элемент задержки, последовательно соединенные регистр сдвига и элемент НЕ,

0 выход которого соединен с вторым входом элемента И, первый вход четвертого блока коррекции соединен с информационным входом первого D-триггера, вход синхронизации которого соединен с входом синхро5 низации второго D-триггера и с вторым выходом счетного триггера, первый выход которого соединен с входом установки второго D-триггера, информационный вход которого является вторым входом четвертого

0 блока коррекции,вход синхронизации которого .соединен со счетным входом счетного триггера и с входом синхронизации регистра сдвига, выход которого соединен с вторым входом первого элемента

5 ИСКЛЮЧАЮЩЕЕ ИЛИ, информационный вход регистра сдвига является третьим входом четвертого блока коррекции, четвертый вход которого соединен с входом установки счетного т-рригера, выход элемента задеож0 ки соединен с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является выходом четвертого блока коррекции

последовательно соединенные первый счетчик импульсов, триггер, второй счетчик импульсов, коммутатор и элемент ИЛИ, элемент И, запоминающее устройство, выходы

0 которого соединены с соответствующими информационными входами коммутатора, вход управления которого соединен с первым входом элемента И и с вторым выходом триггера, второй вход которого соединен с

5 входом управления первого счетчика импульсов и является первым входом пятого блока коррекции, вход синхронизации которого соединен с входами синхронизации первого и второго счетчиков импульсов, вто0 рой вход элемента ИЛИ соединен с выходом элемента И, второй вход которого является вторым входом пятого блока коррекции, первая и вторая группы входов которого соединены с адресными входами запоминэю5 щего устройства, вход управления которого соединен с первым выходом триггера и является выходом пятого блока коррекции, третья группа входов которого соединена с информационными входами первого счетчика импульсов.

v

Фиг. 2

-Ј

м

39

-

Фиг.Ъ

фиг Л

| Генератор псевдослучайных последовательностей | 1986 |

|

SU1378026A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-02-07—Публикация

1988-10-20—Подача