ьо о ел

00

Изобретение относится к вьгаислительной технике и может быть использовано в специализированных вычислительных машинах.

Цель изобретения - повышение быстродействия.

На фиг. 1 изображена структурная схема предлагаемого устройства для деления двоичных чисел,на фиг .2-функ циональная схема блока управления.

Устройство для деления двоичных чисел (фиг. 1) содержит вход 1 кода делимого, вход 2 кода делителя, вход 3 кода точности деления, вход 4 сигнала сопровождения, блок 5 определения значащей части, делимого, состоящий из узла вьщеления приоритета 5, и шифратора 5, , блок 6 оп2

ределения значащей части делителя, состоящий из узла выделения приоритета 6 и шифратора 6j,сумматор 7, дополнительный сумматор-вычитатель 8 коммутатор 9 делимого, коммутатор 10 делителя, блок 11 управления, дополнительный блок 12 сравнения кодов, регистр 13 делимого, регистр Т4 делителя, сумматор-вычитатель 15, блок 16 сравнения кодов, регистр Т7 частного, выход частного 18, выход 19 окончания деления устройства.

Блок управления (фиг. 2) содержит триггер 20, вычитающий счетчик 21 циклов, первый элемент НЕ 22, первый элемент И 23, генератор 24 импульсов, регистр 25 сдвига5 D-триггер 26, второй элемент НЕ 27, второй элемент И 28, элемент ИЛИ 29, третий элемент И 30.

Тстройство работает следующим образом.

На входы 1, 2 и 4 устройства (фиг. 1) поступают п и

п разрядftbie коды делимого А, делителя В вместе с сигналом сопровождения. В блоках 5 и 6 определения значащей части делимого и делителя определяется число значащих разрядов кодов делимого., и делителя, и результат кодируется т., m разрядньм кодом. При этом число значащих разрядов каждого кода определяется как разность между разрядностью соответствующего кода (п , п) и числом старших нулевых разрядов, следующих в нем подряд Если, например, на входы 1 и 2 устройства поступили 8-разрядные коды А и В, которые равны 10010010 и 00010101 соответственно, то на выходах прямого кода блоков 5 и 6 определения значащей ,части делимого и делителя формируются 4-разрядные коды 1000, 0101, а на выходы обратного кода блока 6 определения значащей части делителя поступает код 1010.

Выходные коды блоков 5 и 6 определения значащей части делимого и

делителя управляют процессом коммутации соответствующих входных кодов в коммутаторах 9 и 10 делимого и делителя так, что первый разряд их выходного кода соответствует первому значащему разряду (1) входного кода, второй разряд выходного кода второму, следующему за значащим, разряду входного кода и т.д. Поэтому для рассмотренных значений кодов А 10010010 и В 00010101 на выходы коммутаторов 9 и 10 делимого и делителя поступают соответственно коды А 10010010 и В 10101000, которые записываются в регистры 13

5 и 14 делимого и делителя по сигналам разрешения записи делимого и делителя формируемым на выходах блока 11 управления.

После записи делимого и делителя в соответствзтощие регистры 13 и 14 начинается процесс деления, который заключается в следующем. Содержимое регистров 13 и 14 делимого и делителя сравнивается в блоке 16 сравнения кодов и одновременно на выходе сумматрра-вьмитателя 15 формируется разность регистров 13 и 14 делимого и делителя, которая записьшается в коммутатор 9 делимого по сигналу синхронизации (сигнал ТV) с первого выхода регистра 25 сдвига блока 11 управления. В том случае, если содержимое регистра 13 делимого не меньше содержимого регистра делителя, т.е. А / В, то разность делимого и делителя с выхода коммутатора 9 делимого переписывается затем по сигналу, разрешение записи -делимого в регистр 13 делимого со сдвигом - за счет коммутации на один разряд влево. Одновременно с записью разницы (А-В) в коммутатор 9 делимого производится сдвиг в регистре 17 частного и запись в младший разряд его единицы, так как А В. В том случае, .если

содержимое регистра 13 делимого

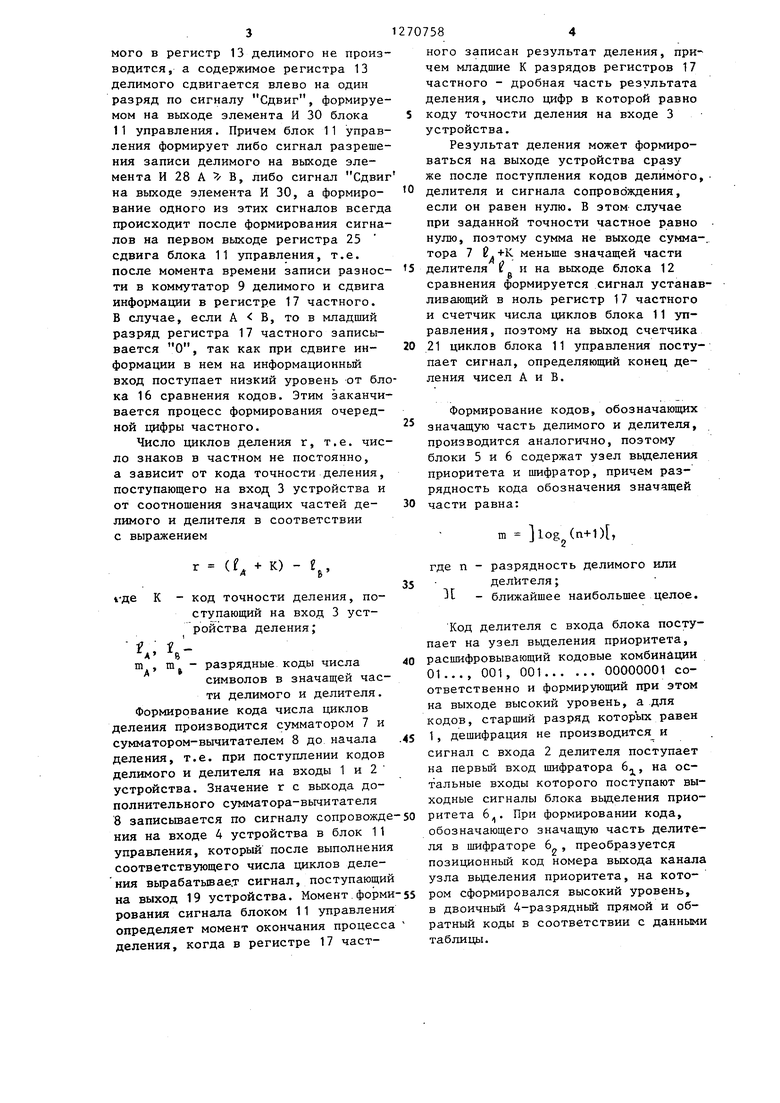

меньше содержимого регистра 14 делителя, т.е. А i В, тогда перезапись разности А-В из коммутатора 9 дели3мого в регистр 13 делимого не производится, а содержимое регистра 13 делимого сдвигается влево на один разряд по сигналу Сдвиг, формируемом на выходе элемента И 30 блока 11 управления. Причем блок 11 управления формирует либо сигнал разрешения записи делимого на выходе элемента И 28 А / В, либо сигнал Сдвиг на выходе элемента И 30, а формирование одного из этих сигналов всегда происходит после формирования сигналов на первом выходе регистра 25 сдвига блока 11 управления, т.е. после момента времени записи разности в коммутатор 9 делимого и сдвига информации в регистре 17 частного. В случае, если А В, то в младший разряд регистра 17 частного записы 0вается , так как при сдвиге информации в нем на информационньй вход поступает низкий уровень от бло ка 16 сравнения кодов. Этим заканчивается процесс формирования очередной цифры частного. Число циклов деления г, т.е. число знаков в частном не постоянно, а зависит от кода точности деления, поступающего на вход 3 устройства и от соотношения значащих частей делимого и делителя в соответствии с выражением г (f, ч- К) - t К - код точности деления, поступающий на вход 3 устройства деления; т - разрядные коды числа символов в значащей час ти делимого и делителя. Формирование кода числа циклов деления производится сумматором 7 и сумматором-вычитателем 8 до начала деления, т.е. при поступлении кодов делимого и делителя на входы 1 и 2 устройства. Значение г с выхода дополнительного сумматора-вычитателя 8 записьюается по сигналу сопровожд ния на входе 4 устройства в блок 11 управления, который после выполнения соответствующего числа циклов деления вырабатьшае.т сигнал, поступающий на выход 19 устройства. Момент.форми-55 рования сигнала блоком 11 управления определяет момент окончания процесса деления, когда в регистре 17 част758ного записан результат деления, причем младшие К разрядов регистров 17 частного - дробная часть результата деления, число цифр в которой равно коду точности деления на входе 3 устройства. Результат деления может формироваться на выходе устройства сразу же после поступления кодов делимого, делителя и сигнала сопровождения, если он равен нулю. В этом случае при заданной точности частное равно нулю, поэтому сумма не выходе сумма-, тора 7 и.+К меньше значащей части и на выходе блока 12 делителя - . сравнения формируется сигнал устанавливающий в ноль регистр 17 частного и счетчик числа циклов блока 11 управления, поэтому на выход счетчика 21 циклов блока 11 управления поступает сигнал, определяющий конец деления чисел А и В. Формирование кодов, обозначающих значащую часть делимого и делителя, производится аналогично, поэтому блоки 5 и 6 содержат узел выделения приоритета и шифратор, причем разрядность кода обозначения значащей части равна: log(n+1), где п - разрядность делимого или делителя; ближайшее наибольшее целое. Код делителя с входа блока поступает на узел выделения приоритета, расшифровывающий кодовые комбинации 01..., 001, 00100000001 соответственно и формирующий при этом на выходе высокий уровень, а для кодов, старший разряд которых равен 1, дешифрация не производится и сигнал с входа 2 делителя поступает на первый вход шифратора 6, на остальные входы которого поступают выходные сигналы блока вьщеления приоритета 6. При формировании кода. обозначающего значащую часть делителя в шифраторе 6 , преобразуется позиционный код номера выхода канала узла вьщеления приоритета, на котором сформировался высокий уровень, в двоичный 4-разрядный прямой и обратный коды в соответствии с данными таблицы. 001 0001 00001... 000001.. 0000001. 00000001 Вследствие того, что в блоке 6 определения значащей части делителя используется обратный код делителя то в названном блоке содержатся эле менты НЕ. Управление процессом деления в устройстве осуществляется блоком 1 управления (фиг. 2), работающем в ждущем режиме, причем запуск его осуществляется при поступлении сигнала сопровождения на вход S-триггера 20. В исходном состоянии триггер 20 и D-триггер 26 установлены в ноль, на входе Сброс счетчика21 - высокий уровень, поэтому он не считает импульсы, а на всех выходах блока 11 управления - низкий уровень. При поступлении сигнала сопровожде ния на вход триггера 20 устанавливается низкий уровень на входе Сброс вычитающего счетчика 21 цик лов. Сигнал с прямого выхода триггера 20 разрешает запись единицы в регистр 25 сдвига по сигналу от генератора 24 импульсов. После появле ния высокого уровня на первом выходе регистра 25 сдвига по следующему сигналу генератора 24 на первом выходе регистра 25 сдвига появляется низкий уровень, а на втором выходе высокий уровень. В результате синхронно с сигналом сопровождения запускается регистр 25 сдвига,, формируя при этом на выходах два импульса Т. и Т„, которые, не совпадая

Л лво времени, следуют друг за другом. Сигнал Т, L. поступает на первьй выход 11 управления, синхронизируя блока процесс записи информации в коммутатор 10 делителя и осуществляя сдвиг информации в регистре 17 частного. Первый сигнал Т, сформированный после поступления сигнала сопровождения , через элемент И 28 поступает на выход блока управления, а по заднему фронту устанавливает в единицу D-триггер 26, высокий уровень с прямого выхода которого поступает на выход блока 11 управления, управляя коммутацией информации, а по переднему фронту вводя в регистр 14 делителя код делителя. Сигнал Т поступает на выход элемента И 28, если он первый по счету с момента начала деления, или если на вход анализа элемента ИЛИ 29 поступает высокий уровень, т.е. если делимое не меньше делителя. В первом случае входной код делимого, а во втором - код разности делимого и делителя записывается в регистр 13 делимого. Если fe некотором цикле деления делимое меньше делителя, то на вход анализа поступает низкий уровень, который запрещает прохождение сигнала Т на второй выход блока управления и разрещает его прохождение на выход элемента И 30, т.е. на выход блока управления, при этом производится один сдвиг влево в регистре 13 делимого. Управление количеством циклов деления производится счетчиком 21, перед началом деления, в который низким уровнем с вькода D-триггера 26 (до момента его включения) осуществляется ввод кода числа циклов деления с входа устройства управления. Каждый цикл деления включает два такта (сигналы Т и Т), причем в первом цикле в регистре делимого и делителя 13 и 14 записьшаются делимое и делитель, а во всех последующих - происходит непосредственно деление чисел. После окончания очередного цикла деления по сигналу ТТ из содержимого счетчика 2 вычитается единица. После выполнения числа циклов деления на единицу большего кода числ циклов деления на инфор71

мационном счетчике 21 входе на выходе Заем счетчика формируется сигнал, определяющий момент окончания деления. Этот сигнал поступает на выход 19 устройства, причем в блоке управления сигнал на выходе счетчика циклов устанавливает в исходное (нулевое) состояние триггер 20 и D-триг гер 26.

В том случае, если деление данных чисел производить не надо (результат равен нулю), то на вход сброса счетчика 21 вычитающего циклов поступает высокий уровень, который устанавливает в ноль счетчик и по первому сигналу Т, регистра 25 сдвига а счет чике формируется сигнал Заем, определяющий окончание процесса деления.

В предлагаемом устройстве процесс деления начинается сразу после поступления делимого, делителя и сигнала сопровождения на входы 1, 2 и А устройства, а результат деления частное формируется одновременно с моментом окончания деления (по переднему фронту синхросигнала).

Формула изобретения

Устройство для деления двоичных чисел, содержащее регистры делимого, делителя, частного, сумматор-вычитатель, блок сравнения кодов и блок управления, содержащий регистр сдвига, вычитающий счетчик циклов, триггер, генератор импульсов, три элемента И, причем выход регистра делимого соединен с первыми входами сумматора-вычитателя и блока сравнения кодов, второй вход сумматора-вычитателя соединен с выходом обратного кода регистра делителя, выход прямого кода которого соединен с вторым входом блока сравнения кодов, выход которого соединен с входом анализа блока управления, выход разрешения записи делимого которого соединен с входом разрешения записи регистра делимого, вход.разрешения сдвига которого соединен с выходом разрешения сдвига блока управления, выход разрешения записи делителя которого соединен с входом разрешения записи регистра делителя, выход регистра частного является выходом результата устройства, отличающееся тем, что, с целью повыше707588

ния быстродействия, в него ввеУ1ены блок определения значающей части делимого, содержащий узел выделения приоритета и шифратор, блок опреде5 ления значащей части делителя,содержащий узел выделения приоритета и шифратор, коммутаторы делимого и делителя, сумматор, дополнительные сумматор-вычитатель и блок сравнения

0 кодов, причем вход блока определения значащей части делимого является входом делимого устройства и соединен с входом узла вьщеления приоритета блока определения значащей час-15 ти делимого и с первым информационным входом коммутатора делимого, вто рой информационный вход которого соединен с выходом сумматора-вычитателя, вькод коммутатора делимого

20 соединен с информационным входом регистра делимого, вход блока опреде-ления значащей части делителя является входом делителя устройства и соединен с входом узла выделения

приоритета блока определения значащей части делителя и с информационным входом коммутатора делителя, выход Которого соединен с информационным входом регистра делителя, выход

30 узла выделения,приоритета блока определения значащей части делимого соединен с входом шифратора блока определения значащей части делимого, выход которого соединен с первым уп35 .равляющим входом коммутатора делимого и с первым входом сумматора, вто:рой вход которого является входом кода точности деления устройства, прямой выход узла вьщеления приори40 тета блока определения значащей части делителя соединен с входом шифратора блока вьщеления значащей части делителя, прямой выход которого соединен с управляющим входом комму татора делителя и первым информационным входом дополнительного блока сравнения кодов, второй информационньй вход которого соединен с выходом сумматора и с первым входом допол ° нительного сумматора-вычитателя, второй вход которого соединен с инверсным выходом шифратора блока определения значащей части делителя, выход блока сравнения кодов соединен

с информационным входом регистра частного, вход разрешения сброса которого соединен с выходом дополнительного блока сравнения кодов и с

первым входом разрешения сброса вычитающего счетчика циклов блока уп)авления, информационньй вход которого соединен с выходом дополнительного сумматора-вычитателя, вход синхронизации дополнительного блока сравнения кодов является входом сигнала сопровождения устройства и соединен с единичным входом триггера блока управления, в который дополнительно введены D-триггер и два элемента НЕ, элемент ИЛИ, причем прямой выход триггера Соединен с первым входом первого элемента И, выход которого соединен с информационным входом регистра сдвига, тактирующий вход которого соединен с выходном генератора импульсов, выход старшего разряда регистра сдвига соединен с. входом разрешения сдвига регистра частного и входом синхронизации коммутатора делимого устройства и с входом первого элемента НЕ, выход которого соединен с вторым входом первого элемента И, выход младшего разряда регистра сдвига соединен с первыми входами второго и третьего ,элементов И, с тактирующим входом D-триггера и входом заема вьгаитающего счетчика циклов, второй вход -30

разрешения сброса которого t с инверсным -выходом триггера, вход разрешения сброса которого соединен с входом разрешения сброса D-триггера и с выходом заема вычитающего счетчика 1щклЪв и является выходом окончания деления устройства, инормационный вход D-триггера соединен с входом логической единицы,

прямой выход D-триггера - с инверсным входом разрешения записи вычитающего счетчика циклов и с вторым входом третьего элемента-И, третий вход которого соединен с выходом

второго элемента НЕ, вход которого соединен с вторым входом второго элемента И и с выходом элемента ИЛИ, первый вход которого соединен с инверсным выходом D-триггера, второй

вход элемента ИЛИ является входом анализа блока управления, выход второго элемента И является выходом разрешения записи делимого блока управления, прямой выход D-триггера

является выходом разрешения записи делителя блока управления и соединен с вторым управляющим входом коммутатора делимого, выход третьего элемента И является вькодом разрешения сдвига блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для деления | 1989 |

|

SU1709301A1 |

| Устройство для деления чисел | 1987 |

|

SU1441388A1 |

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Устройство для деления | 1989 |

|

SU1667060A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Устройство для деления | 1988 |

|

SU1541596A1 |

Изобретение относится к вычислительной технике и может быть использовано для создания специализированных вычислительных машин. Цель изобретения - повьшение быстродействия за счет исключения потерь времени на сдвиг делителя до начала деления и частного после его окончания, а также за счет минимизации числа циклов деления при заданной точности получения результата. Устройство содержит блоки определения значащей части делимого и делителя, коммутаторы делимого и делителя, регистры делимого, делителя и частного, два блока сравнения, сумматор, два сумматора-вычитателя и блок управления. 2 ил., 1 табл.

фиг. 2.

1

| Устройство для деления двоичных чисел | 1975 |

|

SU646331A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления двоичных чисел | 1982 |

|

SU1103224A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-15—Публикация

1985-05-15—Подача