СЛ

о оэ

4 3 СП

| название | год | авторы | номер документа |

|---|---|---|---|

| Таймер | 1981 |

|

SU974581A1 |

| Устройство для измерения коэффициента нелинейности пилообразного напряжения | 1985 |

|

SU1270728A1 |

| Устройство для оптимизации фотосинтеза растений | 1989 |

|

SU1690611A1 |

| ИМПУЛЬСНЫЙ СТАБИЛИЗАТОР ПОСТОЯННОГО НАПРЯЖЕНИЯ ПОНИЖАЮЩЕГО ТИПА | 1991 |

|

RU2006062C1 |

| JK-триггер | 1989 |

|

SU1713091A1 |

| Формирователь центра тяжести импульсов | 1983 |

|

SU1129581A1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| Стабилизированный преобразователь напряжения постоянного тока | 2024 |

|

RU2822294C1 |

| Ограничитель пускового тока инвертора | 1985 |

|

SU1356144A1 |

| УСТРОЙСТВО ТОКОВОЙ ЗАЩИТЫ ЭЛЕКТРОУСТАНОВКИ | 1993 |

|

RU2114496C1 |

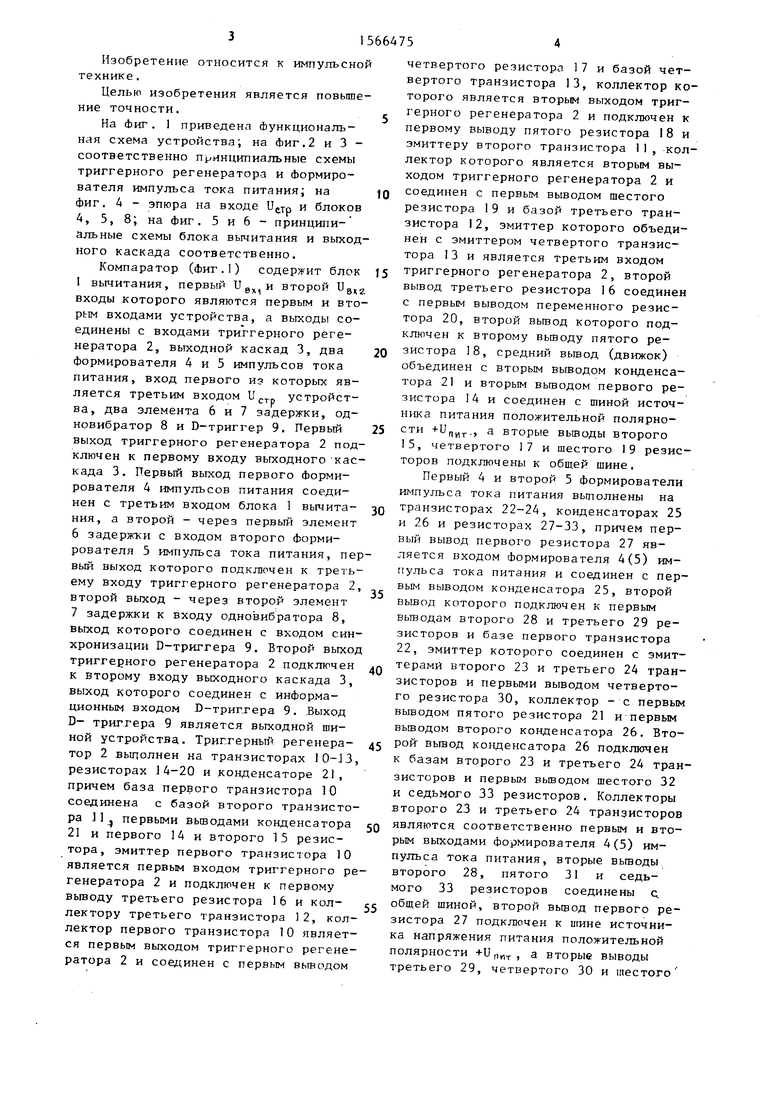

Изобретение относится к импульсной технике и может быть использовано в устройствах сравнения электрических параметров сигналов. Целью изобретения является повышение точности. Для этого компаратор содержит блок 1 вычитания, первый и второй входы которого являются входами устройства, триггерный регенератор 2, входной каскад 3, первый и второй формирователи 4 и 5 импульсов тока питания, элементы 6 и 7 задержки, одновибратор 8 и D-триггер 9. 2 з.п.ф-лы. 6 ил.

фиг.1

Изобретение относится к импульсной технике.

Целью изобретения является повышение точности.

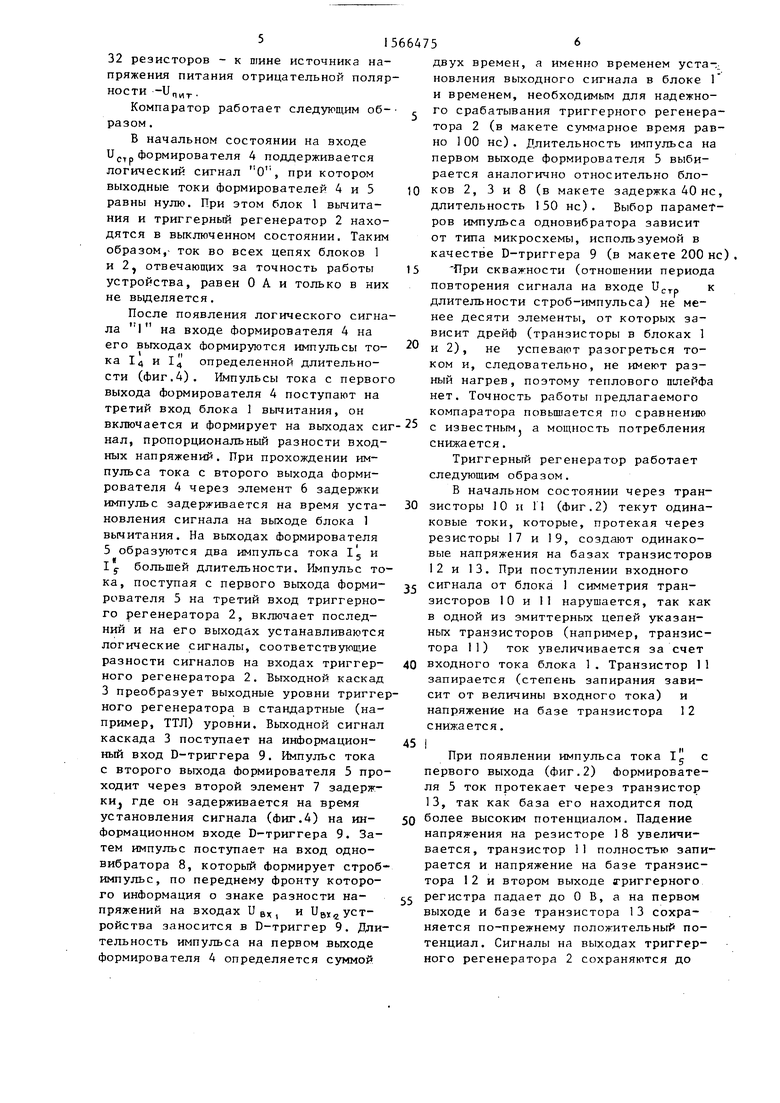

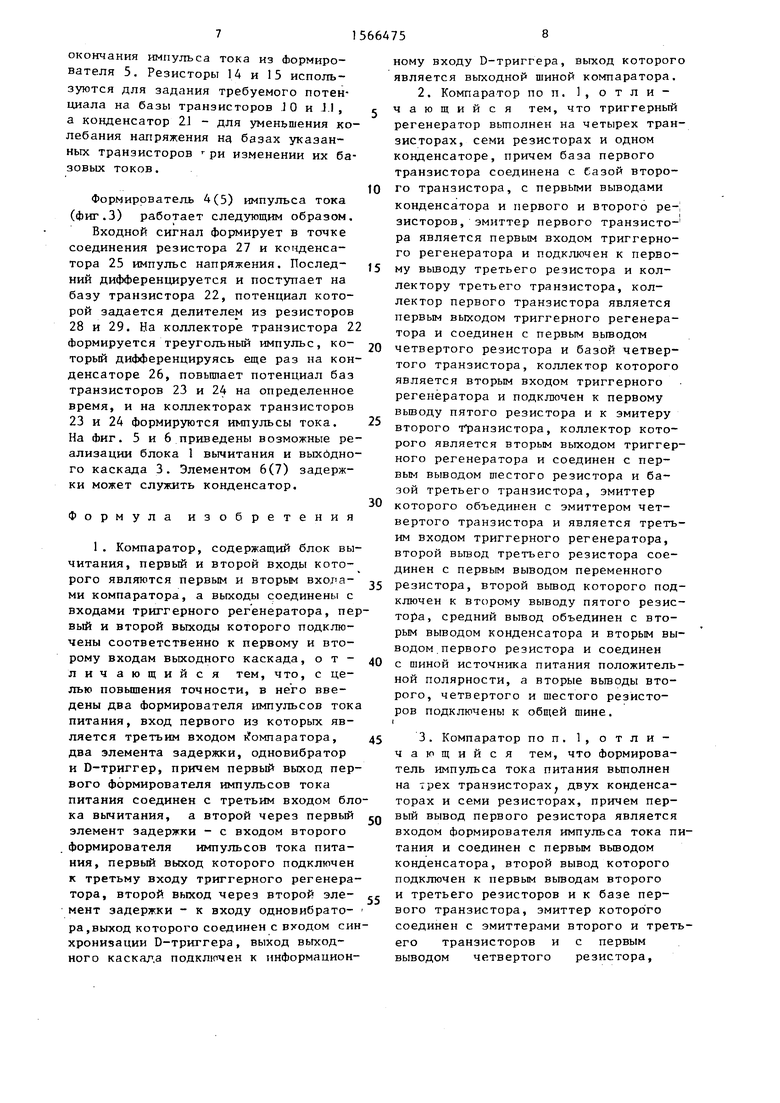

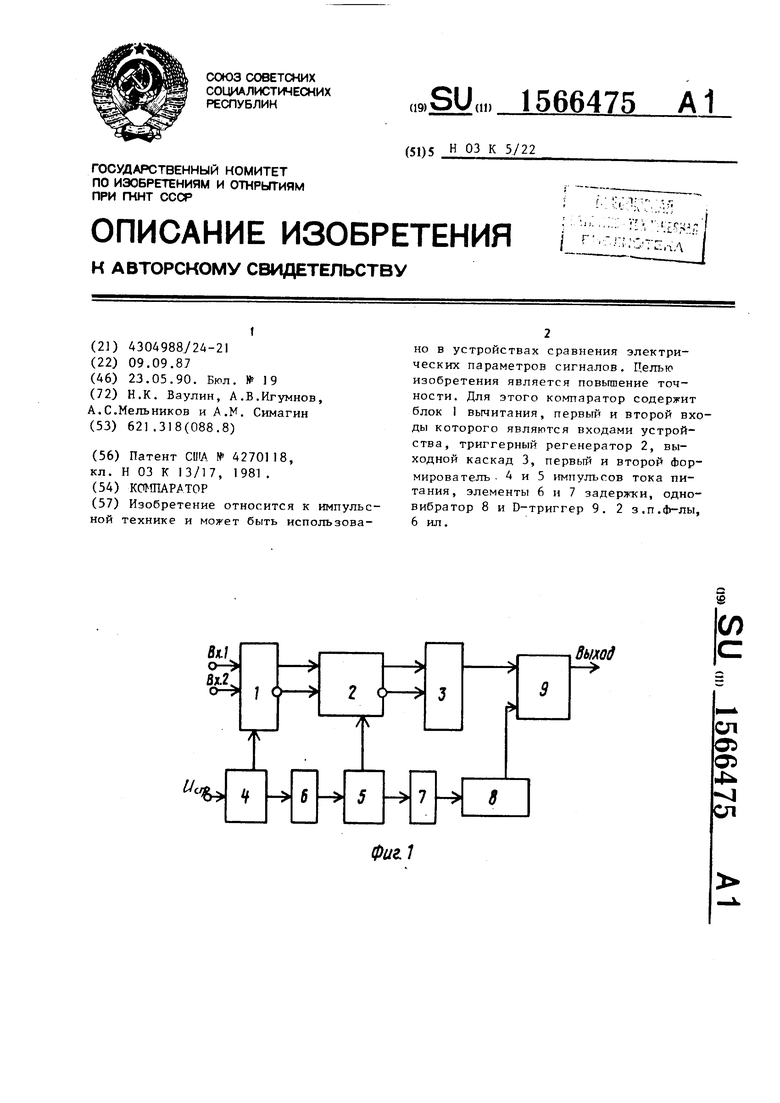

На Фиг. 1 приведена функциональная схема устройства; на фиг.2 и 3 - соответственно принципиальные схемы триггерного регенератора и формирователя импульса тока питания; на фиг. 4 - эпюра на входе UtTp и блоков 4, 5, 8; на фиг. 5 и 6 - принципиальные схемы блока вычитания и выходного каскада соответственно.

Компаратор (Фиг.1) содержит блок 1 вычитания, первый Uем и второй иВц2 входы которого являются первым и вторым входами устройства, а выходы соединены с входами триггерного регенератора 2, выходной каскад 3, два формирователя 4 и 5 импульсов тока питания, вход первого из которых является третьим входом Ucrp устройства, два элемента 6 и 7 задержки, од- новибратор 8 и D-триггер 9. Первый выход триггерного регенератора 2 подключен к первому входу выходного каскада 3. Первый выход первого Формирователя 4 импульсов питания соединен с третьим входом блока 1 вычита- ния, а второй - через первый элемент

6задержки с входом второго формирователя 5 импульса тока питания, первый выход которого подключен к третьему входу триггерного регенератора 2, второй выход - через второй элемент

7задержки к входу одновибратора 8, выход которого соединен с входом синхронизации D-триггера 9. Второй выход триггерного регенератора 2 подключен к второму входу выходного каскада 3, выход которого соединен с информационным входом 1 -триг:гера 9. Выход

D- триггера 9 является выходной шиной устройства. Триггерный регенера- тор 2 выполнен на транзисторах 10-J3, резисторах J4-20 и конденсаторе 21, причем база первого транзистора 10 соединена с базой второго транзистора J1 первыми выводами конденсатора 21 и первого 14 и второго 15 резистора, эмиттер первого транзистора 10 является первым входом триггерного регенератора 2 и подключен к первому выводу третьего резистора 16 и кол- лектору третьего транзистора 12, коллектор первого транзистора 10 является первым выходом триггерного регенератора 2 и соединен с первым выводом

5 0 5 0

0

5 O с

5

четвертого резистора 17 и базой четвертого транзистора 13, коллектор которого является вторым выходом триггерного регенератора 2 и подключен к первому выводу пятого резистора 18 и эмиттеру второго транзистора 11, коллектор которого является вторым выходом триггерного регенератора 2 и соединен с первым выводом шестого резистора 19 и базой третьего транзистора 12, эмиттер которого объединен с эмиттером четвертого транзистора 13 и является третьим входом триггерного регенератора 2, второй вывод третьего резистора 16 соединен с первым выводом переменного резистора 20, второй вывод которого подключен к второму выводу пятого резистора 18, средний вывод (движок) объединен с вторым выводом конденсатора 21 и вторым выводом первого резистора 14 и соединен с шиной источника питания положительной полярности +ипит., а вторые выводы второго 15, четвертого 17 и шестого 19 резисторов подключены к общей шине.

Первый 4 и второй 5 формирователи импульса тока питания выполнены на транзисторах 22-24, конденсаторах 25 и 26 и резисторах 27-33, причем первый вывод первого резистора 27 является входом формирователя 4(5) импульса тока питания и соединен с первым выводом конденсатора 25, второй вывод которого подключен к первым выводам второго 28 и третьего 29 резисторов и базе первого транзистора 22, эмиттер которого соединен с эмиттерами второго 23 и третьего 24 транзисторов и первыми выводом четвертого резистора 30, коллектор - с первым выводом пятого резистора 21 и первым выводом второго конденсатора 26. Второй вывод конденсатора 26 подключен к базам второго 23 и третьего 24 транзисторов и первым выводом шестого 32 и седьмого 33 резисторов. Коллекторы второго 23 и третьего 24 транзисторов являются соответственно первым и вторым выходами формирователя 4(5) импульса тока питания, вторые выводы второго 28, пятого 31 и седьмого 33 резисторов соединены с, общей шиной, второй вывод первого резистора 27 подключен к шине источника напряжения питания положительной полярности +ипит, а вторые выводы третьего 29, четвертого 30 и шестого

51566475

32 резисторов - к шине источника напряжения питания отрицательной полярности -ипит.

Компаратор работает следующим об- разом.

В начальном состоянии на входе U формирователя 4 поддерживается

логический сигнал О, при котором выходные токи формирователей 4 и 5 равны нулю. При этом блок 1 вычитания и триггерный регенератор 2 находятся в выключенном состоянии. Таким образом,- ток во всех цепях блоков 1 и 2 отвечающих за точность работы устройства, равен О А и только в них не выделяется.

После появления логического сигнала на входе формирователя 4 на его выходах формируются импульсы тока 14 и 14 определенной длительности (фиг.4). Импульсы тока с первого выхода формирователя 4 поступают на третий вход блока 1 вычитания, он

10

15

20

двух времен, а именно временем уста новления выходного сигнала в блоке и временем, необходимым для надежно го срабатывания триггерного регенер тора 2 (в макете суммарное время ра но 100 не). Длительность импульса н первом выходе формирователя 5 выбирается аналогично относительно блоков 2, 3 и 8 (в макете задержка 40 н длительность 150 не). Выбор параме ров импульса одновибратора зависит от типа микросхемы, используемой в качестве D-триггера 9 (в макете 200 При скважности (отношении период

повторения сигнала на входе UЈ

ГР

длительности строб-импульса) не менее десяти элементы, от которых зависит дрейф (транзисторы в блоках 1 и 2), не успевают разогреться током и, следовательно, не имеют разный нагрев, поэтому теплового шлейф нет. Точность работы предлагаемого компаратора повышается по сравнению

включается и формирует на выходах сиг-25 с известным, а мощность потребления

) снижается.

нал, пропорциональный разности входных напряжений. При прохождении импульса тока с второго выхода формирователя 4 через элемент 6 задержки импульс задерживается на время уста- новления сигнала на выходе блока 1 вычитания. На выходах формирователя 5 образуются два импульса тока 15 и I j. большей длительности. Импульс тока, поступая с первого выхода форми- рователя 5 на третий вход триггерного регенератора 2, включает последний и на его выходах устанавливаются логические сигналы, соответствующие разности сигналов на входах триггер- ного регенератора 2. Выходной каскад 3 преобразует выходные уровни триггеного регенератора в стандартные (например, ТТЛ) уровни. Выходной сигнал каскада 3 поступает на информацион- ный вход D-триггера 9. Импульс тока с второго выхода формирователя 5 проходит через второй элемент 7 задерж

где он задерживается на время установления сигнала (фиг.4) на информационном входе D-триггера 9. Затем импульс поступает на вход одно- вибратора 8, который формирует строб- импульс, по переднему фронту которого информация о знаке разности напряжений на входах U вх ( и UBXc устройства заносится в D-триггер 9. Длительность импульса на первом выходе формирователя 4 определяется суммой

0

5

двух времен, а именно временем уста-:: новления выходного сигнала в блоке 1 и временем, необходимым для надежного срабатывания триггерного регенератора 2 (в макете суммарное время равно 100 не). Длительность импульса на первом выходе формирователя 5 выбирается аналогично относительно блоков 2, 3 и 8 (в макете задержка 40 не, длительность 150 не). Выбор параметров импульса одновибратора зависит от типа микросхемы, используемой в качестве D-триггера 9 (в макете 200 не). При скважности (отношении периода

повторения сигнала на входе UЈ

ГР

длительности строб-импульса) не менее десяти элементы, от которых зависит дрейф (транзисторы в блоках 1 и 2), не успевают разогреться током и, следовательно, не имеют разный нагрев, поэтому теплового шлейфа нет. Точность работы предлагаемого компаратора повышается по сравнению

с известным, а мощность потребления

|

) снижается.

Триггерный регенератор работает следующим образом.

В начальном состоянии через транзисторы 10 и 11 (фиг.2) текут одинаковые токи, которые, протекая через резисторы 17 и 19, создают одинаковые напряжения на базах транзисторов 12 и 13. При поступлении входного сигнала от блока 1 симметрия транзисторов 10 и 11 нарушается, так как в одной из эмиттерных цепей указанных транзисторов (например, транзистора 11) ток увеличивается за счет входного тока блока 1. Транзистор 11 запирается (степень запирания зависит от величины входного тока) и напряжение на базе транзистора 12 с нижа е тс я .

|

При появлении импульса тока 1 с первого выхода (фиг.2) Формирователя 5 ток протекает через транзистор 13, так как база его находится под

более высоким потенциалом. Падение напряжения на резисторе 18 увеличивается, транзистор 11 полностью запирается и напряжение на базе транзистора 1 2 и втором выходе я-риггерного

регистра падает до ОБ, а на первом выходе и базе транзистора 13 сохраняется по-прежнему положительный потенциал. Сигналы на выходах триггерного регенератора 2 сохраняются до

окончания импульса тока из Формирователя 5. Резисторы 14 и 15 используются для задания требуемого потенциала на базы транзисторов JO и J1, а конденсатор 2J - для уменьшения колебания напряжения на базах указанных транзисторов г ри изменении их базовых токов.

Формирователь 4(5) импульса тока

(фиг.З) работает следующим образом. Входной сигнал формирует в точке соединения резистора 27 и конденсатора 25 импульс напряжения. Послед- ний дифференцируется и поступает на базу транзистора 22, потенциал которой задается делителем из резисторов 28 и 29. На коллекторе транзистора 22 Формируется треугольный импульс, ко- торый дифференцируясь еще раз на конденсаторе 26, повышает потенциал баз транзисторов 23 и 24 на определенное время, и на коллекторах транзисторов 23 и 24 формируются импульсы тока. На Фиг. 5 и 6 приведены возможные реализации блока 1 вычитания и выхбдно- го каскада 3. Элементом 6(7) задержки может служить конденсатор.

Формула изобретения

с шиной источника питания положительной полярности, а вторые выводы второго, четвертого и шестого резисторов подключены к общей шине. i

и третьего резисторов и к базе первого транзистора, эмиттер которого соединен с эмиттерами второго и третего транзисторов и с первым выводом четвертого резистора,

коллектор - с первым выводом пятого резистора и первым выводом второго конденсатора, второй вывод которого подключен к базам второго и третьего транзисторов, и первым выводам шестого и седьмого резисторов, коллекторы второго и третьего транзисторов являются соответственно первым и вторым выходами формирователя импульса

Г

-L

О

н н

/7 I,Г J

Г

тока питания, вторые выводы второго пятого и седьмого резисторов соединены с общей шиной, второй вывод первого резистора подключен к шине источника напряжения питания положительной полярности, а вторые выводы третьего, четвертого и шестого резисторов подключены к шине источника напряжения питания отрицательной полярности.

ъ

11

WiS

КЗ V

Фиг. 2

Фиг. 3

n,

П

U8x(

&/г.4 K блоку 2

f

I ОтИлока.1 Фиг.5

I

| Патент США № 4270118, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-05-23—Публикация

1987-09-09—Подача