Изобретение относится к импульсной технике и может быть использовано в соста ве БИС-систем сбора и обработки информации, в качестве функционального элемента последовательностНых устройств.

Известен интегральный 1К-триггер, содержащий 22 п-р-п и шесть многоэмитгерных транзисторов, устройство производит запись информации по фронту тактового импульса.

Недостатком устройства являются большие аппаратурные затрг|ты, требуемые для реализации узстройства, и низкое быстродействие.(

Меньшие аппаратурные затраты требу ются для реализации тактируемого 1К-триггера, содержащего 10 п-р-п и четыре многоэмиттерных транзисторов, схема со держит меньшее число межзлементных связей. Ж-триггер построен с использованием статно-динамического принципа. На входе RS-триггера находятся два управляемых 1-й К-сигнала и разнос1 ные элементы.

Недостатком устройства являются жесткие требования, предьявляемые к фронтам тактового импульса. ПриГф г(где г-длительность импульса, формируемого на выходе разностного элемента) на выходе разностного элемента управляющ,ий импульс не формируется и схема перестает работать. Следовательно, на входе триггера необхо,пимо дополнительно устанавливать формирователь тактовых импульсов, так как стандартная максимальная для ТТЛ и ТТЛ Ш серий длительность 1ф (100--150) не, но в данном случае недопустима.Наиболее близким к изобретению является 1К-триггер, состоящий из основного и

дополнительного триггеров, между крторыми находятся ключи, разрешающие по тактовому сигналу перезапись информации.

Дополнительный триггер представляет собой RS-триггер. Основной триггер содержит 11 транзисторов и 10 резисторов, схема имеет достаточно большое число межсоединений.

Недостатком устройства являются большие аппаратурные затраты требуемые для реализации основного триггера.

Целью изобретения является повышение надежности устройства и уменьшение потребляемой им мощности.

Поставленная цель достигается тем, что в I К-триггер, содержащий основной триггер, входы которого соединены соответственно с прямым и инверсными выходами дополнительного триггера, который содержит шесть транзисторов и девять резисторов, первые выводы первого и второго резисторов соединены с шиной питания, базы первого и второго транзисторов соответственно через третий и четвертый резисторы соединены с общей шиной и их змиттерами, а коллекторы подключены соответственно к инверсному и прямому входам дополнительного триггера и к первым выводам соответственно пятого и шестого резисторов, вторые выводы которых соединены с первыми выводами седьмого и восьмого резисторов, змиттеры третьего и четвертого транзисторов объединены, коллектор пятого транзистора соединен с первым выводом , девятого резистора, введены десять диодов Шоттки, второй вывод девятого резистора соединен с прямым выходом основного триггера, база шестого транзистора соединена с тактовым входом, коллектор - с шиной питания, а змиттер - с первым выводом седьмого резистора, второй вывод которого соединен с базой пятого транзистора и через десятый резистор - с его эмиттером и базой первого транзистора, второй вывод восьмого резистора соединен с базой второго транзистора, вторые выводы первого и второго резисторов соединены соответственно с базами третьего и, четвертого транзисторов, коллекторы KOTOpiJx соединены с катодами соответственно первого и второго диодов Шоттки, катоды которых соединены соответственно с базами первого и второго транзисторов, коллектор первого транзисто|эа соединен с катодами третьего и четвертого диодов, аноды цоторых соединены с базами соответственна второго и третьего транзисторов, коллектор второго транзистора соединен с катодами пятого и шестого диодов Шоттки, аноды которых соединены

с базами соответственно первого и четвертого транзисторов, база третьего транзистора соединена с анодами седьмого и восьмого диодов Шоттки, катоды которых соединены соответствбнно с прямь1м выходом основного триггера и К-входом, база четвертого транзистора соединена с анодами девятого и десятого диодов Шоттки, катоды которых соединены соответственно с инверсным выходом основного триггера и -входом.

Выходная функция предлагаемого устройства имеет следующий вид:.,,,

Qt 1 - CQt-1 + GQt-1 KQt-1 - CQt-1 IQt-i, где (+), {-) - арифметические операции суммированияи вычитания соответственно. В режиме хранения С-0 все транзисторы, кроме четвертого и шестого (могут быть закрыты или открыты в зависимости от значений входных сигналов IQt-1 и KQt-i), закрыты. При I К О и по переднему фронту G импульса первь1й и второй транзисторы, которые образуют между собой триггер компаратор (схему сравнения), устройство реализует режим хранения Qt Qt-i; Qt-i 0 или 1. Под логической 1 будем понимать заданный уровень постоянного входного тока второго транзистора И, а под О - уровень входного тОка первого транзистора 12. Информационный сигнал обратной связи Qt-i будет задавать третий уровень тока 1з. Причем li l2, И l2 + 1з. Отметим, что ток 1з управляемый и появляется лишь в том случае, если Qt-i 1. Следовательно, если входные емкости перового и второготранзисторов равны (). пороговые напряжения идентичны (Unppi Unop2) то быстрее откроется тот транзистор триггера, базовый ток (1б) которого больше (torn Unop X

хСвх/1б}.Следовательн6, в режиме хранения на транзисторах и триггер работает как компаратор входных токов.

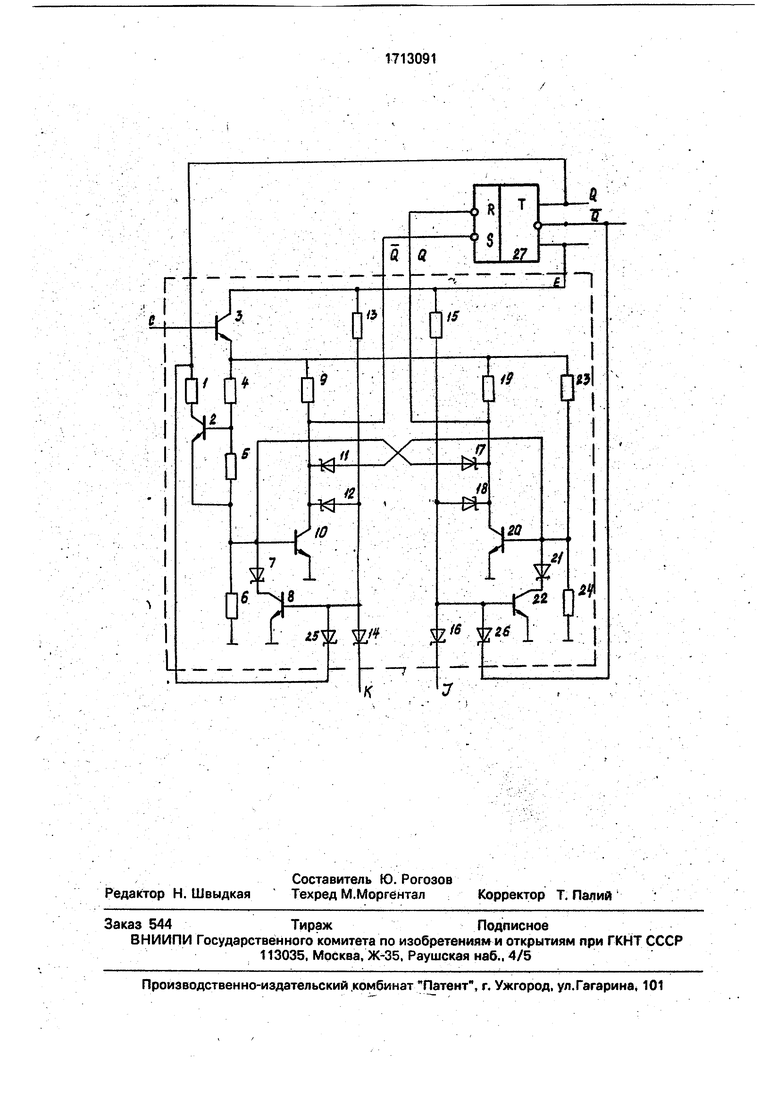

На чертеже приведена принципиальная схема 1К-триггера.

1К Триггер содержит основной и дополнительный триггеры, причем дополнительный триггер содержит десять резисторов, шесть П--Р-П транзисторов, десять диодов Шоттки, основной триггер.

Сигнал обратной связи с прямого выхода основного триггера 1 через девятый резистор 2 соединен с коллектором пятого транзистрраЗ, тактовый вход устройства соединен с базой шестого транзистора 4, эмиттер которого через седьмой резистор 5 объединен с базой транзистора 3 и первым выводом десятого резистора 6, второй вывод которого Объединен с эмиттером транзистора 3, первым выводом третьего резистора 7.. и анодом первого диода Шоттки 8, катод которого соединен с коллектором третьего транзистора 9, эмиттер транзистора 4 через пятый резистор 10 соединен с 5 инверсным выходом дополнительного триггер, прямым входом основного триггера 1, катодами третьего и четвертого диодов Шоттки 11 и 12 и коллектором первого транзистора 13, база транзистора 9 соединена с 10 анодом седьмого диода Шоттки 14, вторым выводом первого резистора 15 и через восьмой диод Шоттки 16 с К-входом устройства, коллектор транзистора 4 соединен с шиной питания и первыми выводами первого 15 и второго резисторов 15 и 17, второй вывод последнего через десятый диод Шоттки 18 соединен с 1-входом устройства, база транзистора 13 соединена с анодами диодов Шоттки 8 и 19, анод диода 18 соединен 20 с анодом шестого диода 20, катод которого объединен с инверсным входом основного триггера 1, катодом диода 19, вторь м выводом шестого резистора 21, коллектором второго транзистора 22, инверсный выход 25 устройства соединен с инверсным выходом основного триггера 1 и катодом девятого диода Шоттки 23, анод которого V соединен с анодом диода 18, анод диода 11 соединен с базой транзистора 22 через 30. второй диод Шоттки 24 с коллектором четвертого транзистора 25, вторым выводом восьмого резистора 26 и первым выводом четвертого резистора 27, первые выводы резисторов 21 и 26 объединены с эмиттером 35 транзистора 4, база транзистора 25 соединена с анодом диода 23, прямой выход основного триггера соединен с прямым выходом основного триггера 1 и катодом диода 14, вторые выводы резисторов 7 и 27 40 и эмиттеры транзисторов 9,13,22 и 25 объединены с общей шиной.

Рассмотрим, каким образом задаются , различные входные токи транзисторов 13 и 22, которые образуют триггер-компаратор 45 (при KQt-1 IQt-1 О транзисторы 9 и 25 закрыты). Причем необходимо получить неравенства li l2 или li la + 1з. Указанные неравенства обеспечиваются подбором резисторов. Резисторы 26 и 27 задают 50 ток ii, резисторы 5 и 6 - ток г и, наконец, резистор 2 и транзистор 3 обеспечивают ток 1з при высоком логическом уровне сигнала обратной связи {Qt-i Т); если 01- 0, то1з р.55

Устройство работает следующим образом.

Если С О, то 1К-триггер находится в режиме хранения, так как в этом случае транзисторы 13 и 22 закрыты, что не влияет

на состояние основного триггера. Причем изменение уровней сигналов на I- и К-входах приводит к изменению состояния лишь транзисторов 9 и 25. Отметим, что в режиме хранения дополнительный триггер не потребляет мощность (не считая мич нимальных токов, протекающих через резистора 15 и 17).

Если С 1, то по переднему фронту (переход от О к 1) транзистор 4 открывается и триггер начинает устанавливаться в состояние, определяемое входными сигналами l5t-i и KQt-1. При I К 1 (счетный режим), транзисторы 9 и 25 закрыты, поэтому транзисторы 13 и 22 на 11инают открываться своими входами токами. Предположим, что Qt-1 1, тогда входной ток транзистора 13(12 + 1з) больше входного тока транзистора 22. Поэтому транзистор 13 открывается быстрее и через свой открытый коллектор отбирает входной ток транзисторов 22 и 9. По окончании переходного процесса на прямом выходе дополнительного триггера формируется сигнал высокого, а на инверсном выходе - низкого логического уровня, что не приводит к изменению состояния основного триггера. По окончании, переходного процесса образуются триггерные связи не только между транзисторами 13 и 22, но и между транзисторами 9, 13 и 25, 22 (имеем три триггера), что не дает возможности изменить состояние триггера при изменении как входных сигналов (I и К), так и сигнала обратной связи, т.е. триггер устанавливается по переднему фронту тактового импульса. По окончании тактового импульса (С ) транзистор 4 закрывается и, как следствие, закрываются транзисторы 13 и 22, что не приводит к изменению состояния основного триггера.

Если С приходом очередного тактового импульса (С ) KQt-i О, IQt-i 1 (еще до прихода С 1 транзистор 4 закрыт, транзистор 25 насыщен), то отпирание транзистора 4 привода1т к появлению входных токов транзисторов 13 и 22. Так как транзистор 25 насыщен, то входной транзистор 22 отбирается через коллектор транзистора 25, а так как транзистор 9 закрыт, то открывается транзистор 13 и через свой коллектор и диоды Шоттки 11 и 12 обеспечивает запирание транзисторов 9 и 22. По окончании переходного процесса изменение уровней входных сигналов не вызывает изменение состояния триггера.

При KQt-1 1, IQt-1 О по переднему фронту очередного тактового импульса открывается транзистор 22, который закрывает транзисторы 13 и 25. На выходе

основного триггера формируется сигнал низкого уровня.

Отметим, что в режиме хранения при низком уровне на входе тактирования дополнительный триггер тока не потребляет. Поэтому при скважности тактового сигнала, равной двум, дополнительный триггер потребляет в два раза меньшую мощность, чем в схеме прототипа, при увеличении скважности рассеиваемая мощность уменьшается. Схема имеет в 1,5 раза большее быстродействие, так как в отличие от схемы прототипа дополнительный триггер данной схемы имеет время переключения, равное 4 ts (в схеме прототипа дополнительный триггер имеет Gta). Кроме того, схема дополнительного триггера не содержит многоэмиттерные транзисторы (т.е. исключены 4 многоэмиттерных транзистора), что позволяет сократить площадь, занимаемую на кристалле. В 1,5 раза сокращено число межсоединений (38 в предлагаемой схеме, 51 в схеме прототипа).

Таким образом, предлагаемое устройство реализует функции К-триггера с наименьшими затратами аппаратуры, мощности, занимает меньшую площадь на кристалле, не уступает аналогам по быстродействию и не накладывает нестандартные требования на параметры (длительность фронта) входных сигналов.

Формула изобрете.ния 1К-триггер, содержащий основной триггер, входы которого соединены соответственно с прямым и инверсным выходами дополнительного триггера, который содержит шесть транзисторов и десять резисторов, первые выводы первого и второго резисторов соединены с шиной питания, базы первого и второго транзисторов соответственно через третий и четвертый резисторы соединены с общей шиной и их эмиттерами, а коллекторы подключены соответственно к инверсному и прямому входам дополнительного триггера и первым

выводам соответственно пятого и шестого резисторов, вторые выводы которых соединены с первыми выводами седьмого и восьмого резисторов, эмиттеры третьего и

метвертого транзисторов объединены, коллектор пятого TpaH3VicTopa соединен с первым выводом девятого резистора, отличающийся тем, что, с целью увеличения надежности и уменьшения потребляемой мощности, в него введены десять диодов Шоттки, второй вывод девятого резистора соединен с прямым выходом основного триггера, база шестого транзистора соединена с тактовым входом,

коллектор -с шиной питания, а эмиттер - с первым выводом седьмого резистора, второй вывод которого соединен с базой пятого транзистора и через десятый резистор - с его эмиттером и базой первого транзистора,

второй вывод восьмого резистора соединен с базой второго транзистора, вторые вьтоды первого и второго резисторов соединены соответственно с базами третьего и четвертого транзисторов, коллекторы которых соединены с катодами соответственно первого и второго диодов Шоттки, катоды которых соединены соответственно с базами первого и второго транзисторов, коллектор первого транзистора

соединен с катодами третьего и четвертого диодов, аноды которых соединены с базами соответственно второго и третьего транзисторов, коллектор второго транзистора соединен с катодами пятого и шестого диодов Шоттки, аноды которых соэдинены с базами соответственно первого и четвертого транзисторов, база третьего транзистора соединена с анодами седьмого и восьмого диодов Шоттки, катоды которых

соединены соответственно с прямым выходом основного триггера и К-входом, база четвертого транзистора соединена с анодами девятого и десятого диодов Шоттки, катоды которых соединены соответственно с инверсным выходом основного триггера и f-входом.

| название | год | авторы | номер документа |

|---|---|---|---|

| D-триггер | 1985 |

|

SU1332380A1 |

| Д-триггер | 1984 |

|

SU1221714A1 |

| Триггер | 1983 |

|

SU1150734A1 |

| @ -Триггер | 1984 |

|

SU1174987A1 |

| Триггер | 1986 |

|

SU1325669A1 |

| Мажоритарное устройство | 1981 |

|

SU970701A1 |

| Устройство для выделения тактовой частоты при воспроизведении цифрового сигнала | 1991 |

|

SU1770985A1 |

| Триггер | 1983 |

|

SU1132343A1 |

| Двойной инвертор с минимальной асимметрией | 1987 |

|

SU1499484A1 |

| Устройство для трехпозиционного управления (его варианты) | 1983 |

|

SU1185586A1 |

| Слравецйик по полупроводниковым приборам ftpAJpeA | |||

| Горюнова Н.Н | |||

| М.: Энергия, 1976, cJ 515-516.Але1ссеенк:о А.Г | |||

| и Шагурин П.И | |||

| Микро- схемотехнмка | |||

| М.: Радио и связь, 1982, с | |||

| Индукционная катушка | 1920 |

|

SU187A1 |

Авторы

Даты

1992-02-15—Публикация

1989-12-19—Подача