-Г

1

СП

0 СО

со &

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для частотного разделения многоканального цифрового сигнала | 1984 |

|

SU1226609A1 |

| СПОСОБ СПЕКТРАЛЬНОГО АНАЛИЗА СИГНАЛОВ | 1993 |

|

RU2127888C1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО СИГНАЛА ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2004 |

|

RU2287909C2 |

| ЦИФРОВОЙ ПРИЕМНИК СПУТНИКОВЫХ РАДИОНАВИГАЦИОННЫХ СИСТЕМ | 2007 |

|

RU2361232C2 |

| Устройство компенсации сигнала дефектов киноленты | 1985 |

|

SU1322503A2 |

| Устройство для вычисления двумерного дискретного преобразования Фурье | 1988 |

|

SU1589289A1 |

| Адаптивный фильтр | 1983 |

|

SU1116537A1 |

| Устройство для адаптивной обработки сигналов | 1981 |

|

SU1014127A1 |

| СПОСОБ МНОГОКАНАЛЬНОГО АДАПТИВНОГО ПРИЕМА РАДИОСИГНАЛОВ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 2011 |

|

RU2477551C1 |

| Способ многоканальной передачи и приема сигналов | 1989 |

|

SU1693731A1 |

Изобретение относится к цифровой многоканальной связи и предназначено для выделения канальных сигналов из группового сигнала с частотным разделением каналов. Цель изобретения - упрощение устройства за счет уменьшения количества умножителей. Устройство содержит N элементов задержки, группы умножителей 2 и 4, группу сумматоров 3,5 и 6. Поставленная цель достигается введением третьей группы сумматоров 6. Устройство для частотного разделения многоканального цифрового сигнала эквивалентно набору цифровых полосовых фильтров, сформированных на основе одного цифрового фильтра нижних частот (ЦФНЧ). Частотное разделение многоканального цифрового сигнала осуществляется так: отсчеты многоканального цифрового сигнала поступают в элементы 1 задержки, далее, поступая на умножители 2, умножаются на коэффициенты базового ЦФНЧ. Сумматоры 3 формируют результаты суммы

группа сумматоров 6 реализует умножение вектора LN, образованного из отсчетов выходных сигналов сумматоров 3, на матрицу Qс @ , умножители 4 выполняют умножение на диагональную матрицу Dс, сумматоры 5 - на матрицу выходных сложений Sс. Количество сумматоров 5 и 6 определяется структурой матрицы Sс и Qс @ . 3 ил.

m m...m

ГТ J

Фа.1

Изобретение относится к цифровой многоканальной связи и предназначено для выделения канальных сигналов из группового Сигнала с частотным разделением каналов.

Цель изобретения - упрощение устройства за счет уменьшения количества умножителей.

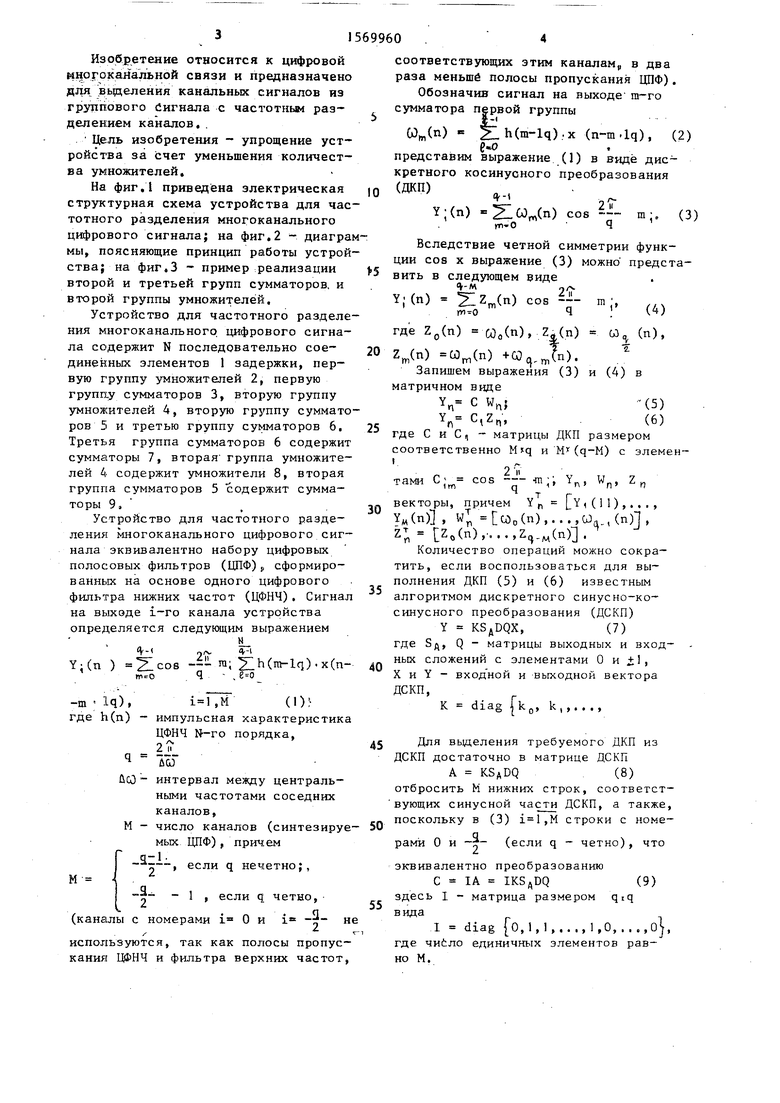

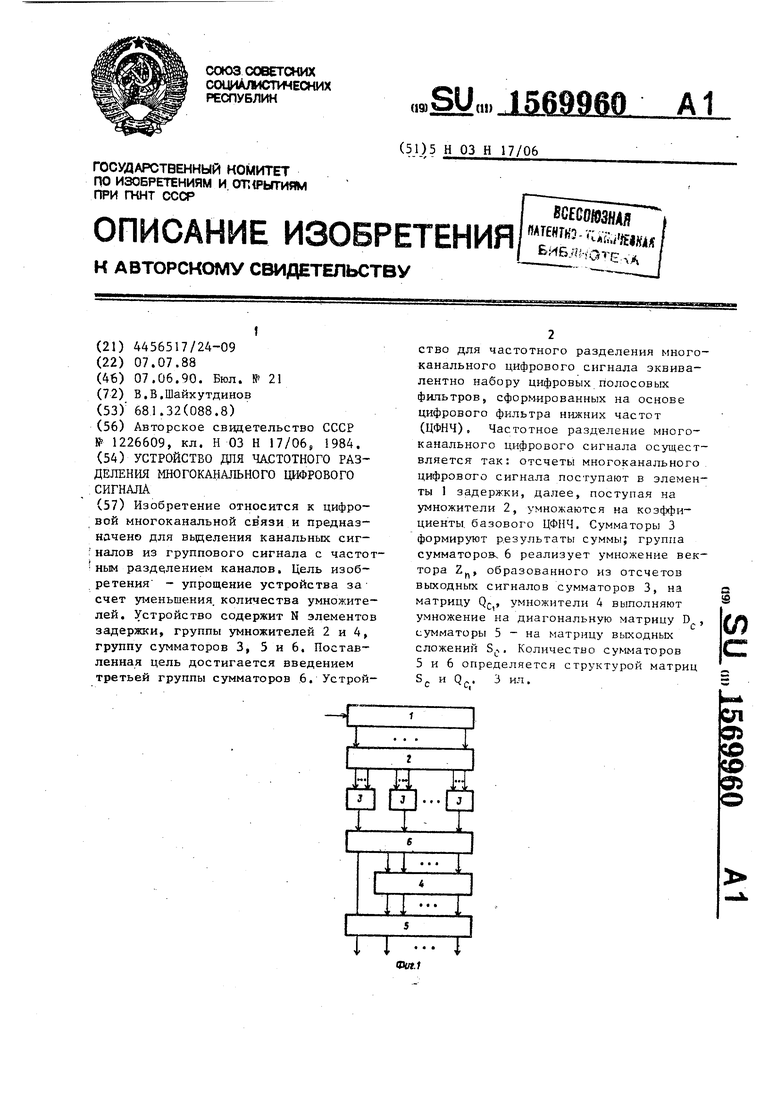

На фиг.1 приведена электрическая структурная схема устройства для частотного разделения многоканального цифрового сигнала; на фиг.2 - диаграммы, поясняющие принцип работы устройства; на фиг.З - пример реализации второй и третьей групп сумматоров, и второй группы умножителей.

Устройство для частотного разделения многоканального цифрового сигнала содержит N последовательно сое- диненных элементов 1 задержки, первую группу умножителей 2, первую группу сумматоров 3, вторую группу умножителей 4, вторую группу сумматоров 5 и третью группу сумматоров 6. Третья группа сумматоров 6 содержит сумматоры 7, вторая группа умножителей 4 содержит умножители 8, вторая группа сумматоров 5 содержит сумматоры 9.,

Устройство для частотного разделения многоканального цифрового сигнала эквивалентно набору цифровых полосовых фильтров (ЦПФ) сформированных на основе одного цифрового фильтра нижних частот (ЦФНЧ). Сигнал на выходе 1-го канала устройства

определяется следующим выражением

н

Y:(n ) -Xcos --- га; Th(m-ln,).x(n- 1.nQ

lq), i-l,M (1) h(n) - импульсная характеристика ЦФНЧ N-ro порядка, 2 fr45

q 1 И

UCO - интервал между центральными частотами соседних каналов,

М - число каналов (синтезируе- 50 мых ЦПФ), причем

-, если q нечетно;,

- 1 , если q четно,

1-Jналы с номерами i- 0 и

55

не

используются, так как полосы пропускания и фильтра верхних частот,

соответствующих этим каналам, в два раза меньше полосы пропускания ЦПФ).

Обозначив сигнал на выходе т-го сумматора первой группы

JQfs

202530

ДО

35

45

50

55

Wjn) - Г h(m-lq).x (п-ш-lq), (2)

е-о

представим выражение (1) в виде дискретного косинусного преобразования

(ДКП)

Yj(n) -21COm(n) cos ± ш;. (3) m-0 Ч

Вследствие четной симметрии функции сое х выражение (3) можно представить в следующем виде

V; (п) - Г Z.O « - -|. (4)

где ZQ(n) C00(n), гЛп) W (п),

zr «m(n) +a,,mTn).

Запишем выражения (3) и (4) в матричном виде

V с wnJ Y

45)

П (6)

где С и С, - матрицы ДКП размером соответственно и М(q-M) с элемен2 п тами C;m cos -т;; Yn, Wn, Zn

т г векторы, причем Yn (1 I) ,. . . ,

M(n) , (n)Ц.,(п),

Z; ЈZ0(n),...,ZVM(n).

Количество операций можно сократить, если воспользоваться для выполнения ДКП (5) и (6) известным алгоритмом дискретного синусно-ко- синусного преобразования (ДСКП)

Y KSADQX, (7) где Sft, Q - матрицы выходных и вход- - ных сложений с элементами 0 и + 1, X и Y - входной и выходной вектора ДСКП,

К diag k0 k,,...,

Для выделения требуемого ДКП из ДСКП достаточно в матрице ДСКП А (8)

отбросить h нижних строк, соответствующих синусной части ДСКП, а также, поскольку в (3) ,M строки с номерами 0 и -г- (если q - четно), что

эквивалентно преобразованию

С « IA IKSftDQ(9)

здесь I - матрица размером qtq вида

I - diag 0,1,11,0,.. .,,

где число единичных элементов равно М.

Поскольку при усечении строк с номерами 0 и матрица К вырождается в скалярный множитель 4, который можно опустить, (так как в (3) используется ненормированное ДКП), то

С - SCDQ,

где

IS,

(Ю)

(11)

с J«

Матрицы S д и D связаны с матрицами и Т в алгоритме Виноградова дискретного преобразования Фурье (ДПФ) YF - STQ,(12)

следующими соотношениями Т I2D

SA- ЕеП, здесь Re{ - операция взятия действительной части 1 и i - матрица

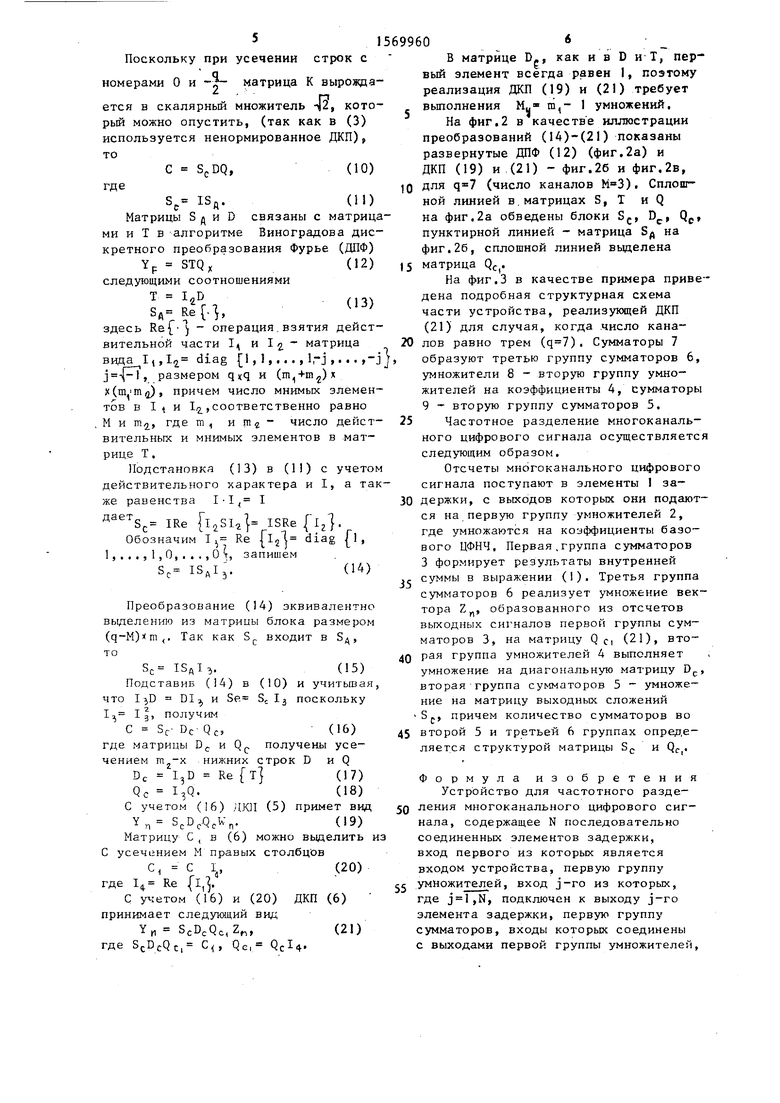

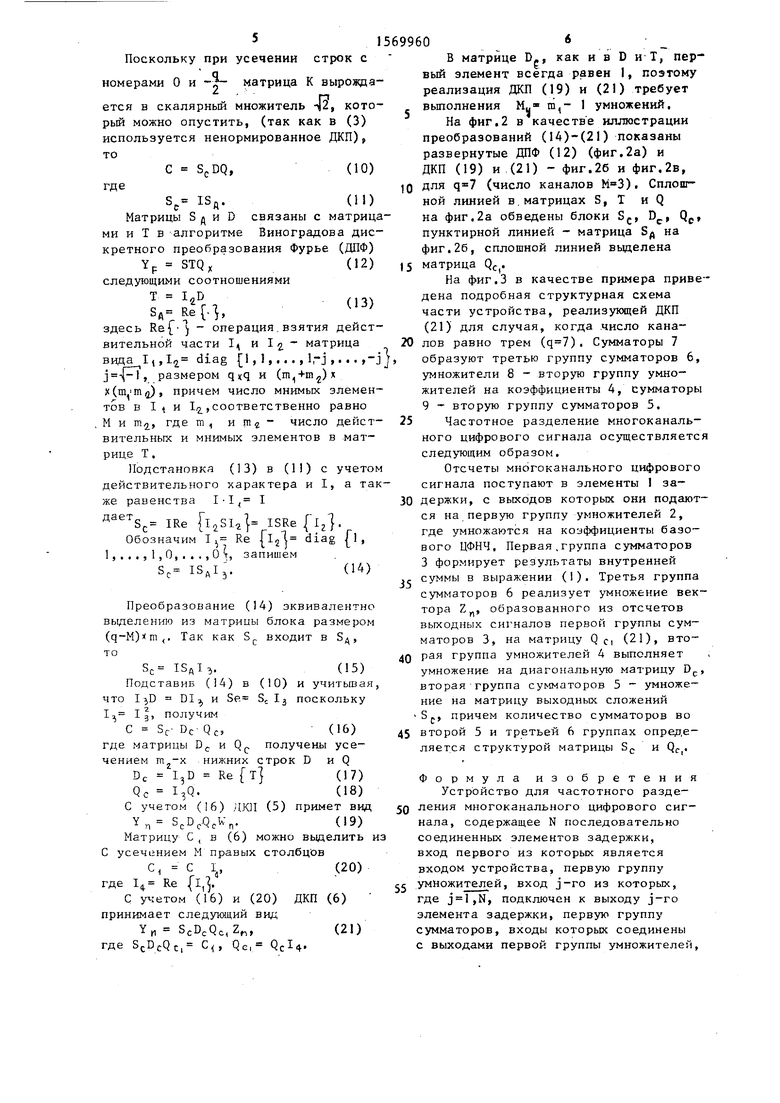

На фиг.2 в качестве иллюстрации преобразований (14)-(21) показаны развернутые ДПФ (12) (фиг.2а) и ДКП (19) и (21) - фиг.26 и фиг.2в, Ю для q-7 (число каналов М-3). Сплошной линией в матрицах S, Т и Q на фиг.2а обведены блоки S., D , Q

е

(13)

пунктирной линией - матрица 8Л на фиг.26, сплошной линией выделена

15 матрица QCi.

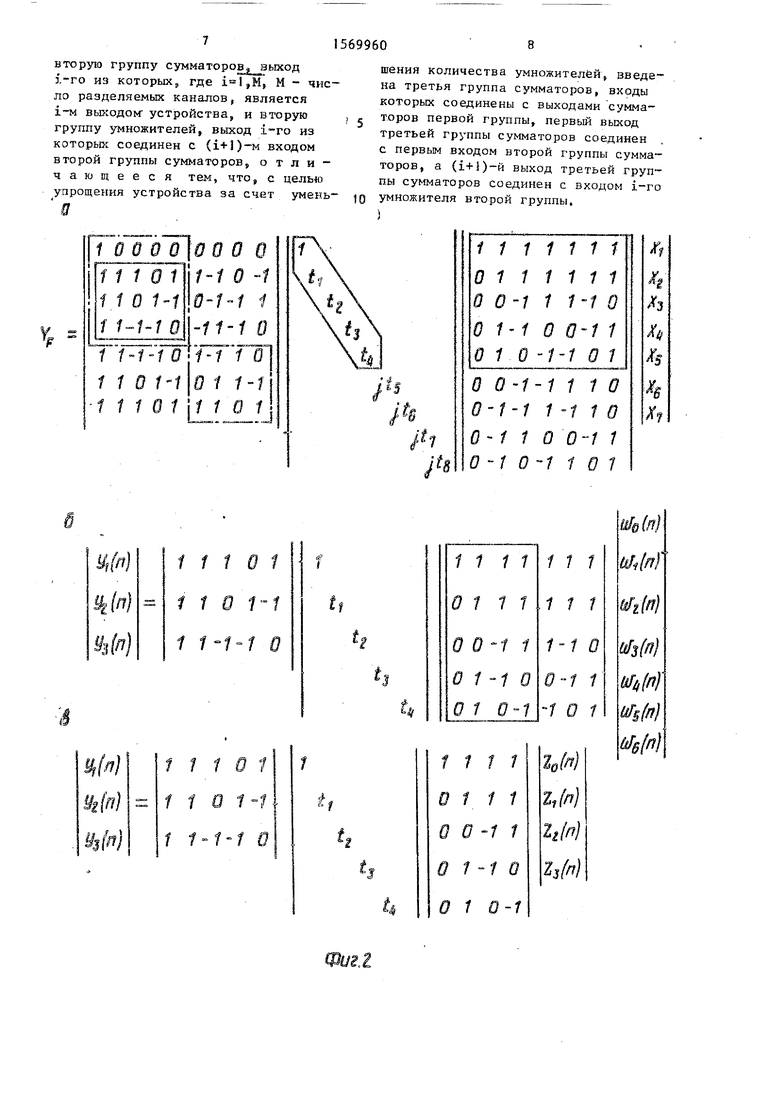

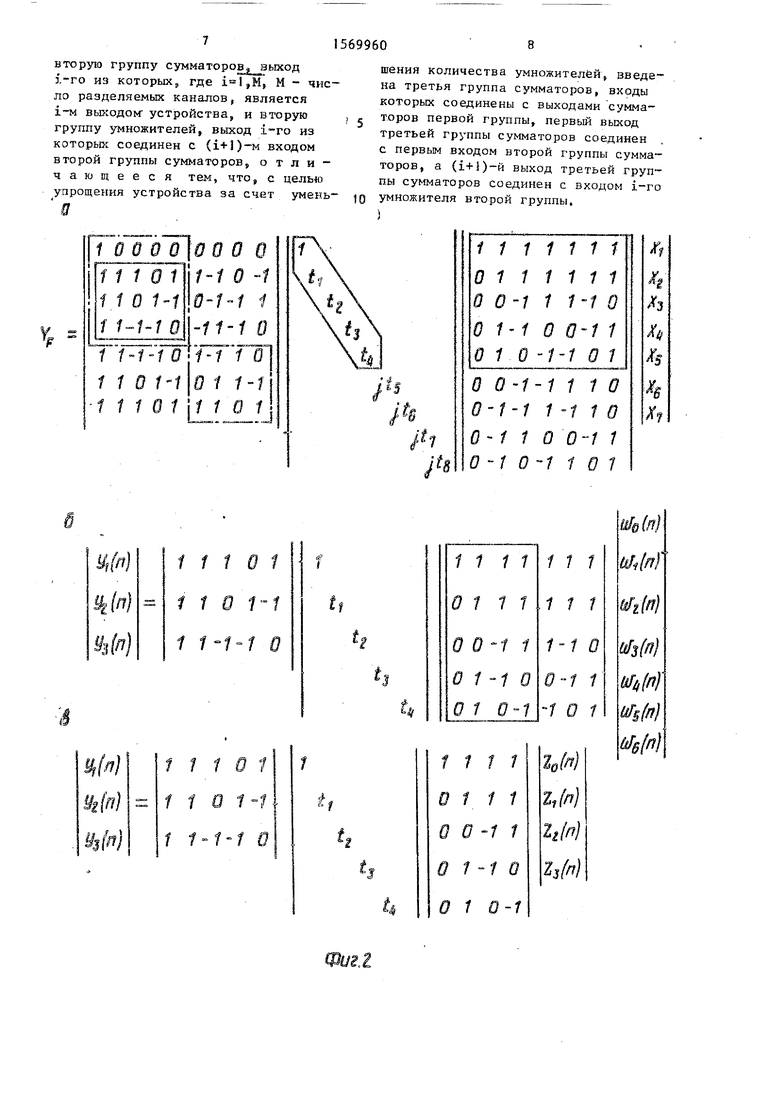

На фиг.З в качестве примера приве дена подробная структурная схема части устройства, реализующей ДКП (21) для случая, когда число кана20 лов равно трем () . Сумматоры 7

вида 1), diag Ј1 , 1,,.. , 1,-j ,.. . ,-j j, образуют третью группу сумматоров 6,

, размером и () x(m. m), причем число мнимых элементов в 1 и 1г соответственно равно М и т2, где m , и m4 - число действительных и мнимых элементов в матрице Т.

Подстановка (13) в (11) с учетом действительного характера и I, а также равенства I

ДЗеТ8с IRe l2SI2j ISRe (lz.

Обозначим I Re diag fl, 1, . . . , 1,0, . . . , 0 , запишем

Sf ISAI5.(14)

Преобразование (14) эквивалентно выделению из матрицы блока размером (q-M)m,. Так как Sc входит в SA, то

Sc ISftI ,.(15)

Подставив (14) в (10) и учитывая, что I D DI и Se Sc I5 поскольку I I, получим

С Sr- Dc Qc,(16)

где матрицы Dc и Qc получены усечением нижних строк D и Q Dc I,D Re (17)

Qc I,Q.(18)

С учетом (16) ДКП (5) примет вид

Yn ScDcQeWn.(19)

Матрицу С, в (6) можно выделить из С усечением М правых столбцов

С, С ld,(20)

где I4 Re l,.

С учетом (16) и (20) ДКП (6) принимает следующий вид

Ґ„ ScDcQc,Zr, (21) где SCDCQC, C, QCl- Qc умножители 8 - вторую группу умножителей на коэффициенты 4, сумматоры 9 - вторую группу сумматоров 5.

25 Частотное разделение многоканального цифрового сигнала осуществляетс следующим образом.

Отсчеты многоканального цифрового сигнала поступают в элементы 1 за-

30 держки, с выходов которых они подают ся на первую группу умножителей 2, где умножаются на коэффициенты базового ЦФНЧ. Первая,группа сумматоров 3 формирует результаты внутренней

,, суммы в выражении (1). Третья группа сумматоров 6 реализует умножение вектора Zn, образованного из отсчетов выходных сигналов первой группы сумматоров 3, на матрицу Q Cl (21), вто40 рая группа умножителей 4 выполняет умножение на диагональную матрицу Dc, вторая группа сумматоров 5 - умножение на матрицу выходных сложений -Sp, причем количество сумматоров во

45 второй 5 и третьей 6 группах определяется структурой матрицы Sc и QC|.

Формула изобретения Устройство для частотного разде-

50 ления многоканального цифрового сигнала, содержащее N последовательно соединенных элементов задержки, вход первого из которых является входом устройства, первую группу

55 умножителей, вход j-ro из которых, где ,N, подключен к выходу j-ro элемента задержки, первую группу сумматоров, входы которых соединены с выходами первой группы умножителей,

1569960«

В матрице D., как и в D и Т, первый элемент всегда равен I, поэтому реализация ДКП (19) и (21) требует

выполнения М т,- 1 умножений.

На фиг.2 в качестве иллюстрации преобразований (14)-(21) показаны развернутые ДПФ (12) (фиг.2а) и ДКП (19) и (21) - фиг.26 и фиг.2в, для q-7 (число каналов М-3). Сплошной линией в матрицах S, Т и Q на фиг.2а обведены блоки S., D , Q

е

пунктирной линией - матрица 8Л на фиг.26, сплошной линией выделена

матрица QCi.

На фиг.З в качестве примера приведена подробная структурная схема части устройства, реализующей ДКП (21) для случая, когда число каналов равно трем () . Сумматоры 7

образуют третью группу сумматоров 6,

умножители 8 - вторую группу умножителей на коэффициенты 4, сумматоры 9 - вторую группу сумматоров 5.

25 Частотное разделение многоканального цифрового сигнала осуществляется следующим образом.

Отсчеты многоканального цифрового сигнала поступают в элементы 1 за-

30 держки, с выходов которых они подаются на первую группу умножителей 2, где умножаются на коэффициенты базового ЦФНЧ. Первая,группа сумматоров 3 формирует результаты внутренней

,, суммы в выражении (1). Третья группа сумматоров 6 реализует умножение вектора Zn, образованного из отсчетов выходных сигналов первой группы сумматоров 3, на матрицу Q Cl (21), вто0 рая группа умножителей 4 выполняет умножение на диагональную матрицу Dc, вторая группа сумматоров 5 - умножение на матрицу выходных сложений -Sp, причем количество сумматоров во

5 второй 5 и третьей 6 группах определяется структурой матрицы Sc и QC|.

Формула изобретения Устройство для частотного разде-

0 ления многоканального цифрового сигнала, содержащее N последовательно соединенных элементов задержки, вход первого из которых является входом устройства, первую группу

умножителей, вход j-ro из которых, где ,N, подключен к выходу j-ro элемента задержки, первую группу сумматоров, входы которых соединены с выходами первой группы умножителей,

вторую группу сумматоров, выход j-ro из которых, где ,M, M - число разделяемых каналов, является i-м выходом устройства, и вторую группу умножителей, выход 1-го из которых соединен с (1+1)-м входом второй группы сумматоров, отличающееся тем, что, с целью упрощения устройства за счет умень U

1 о о ооо

1-1 0 -1 0-1-1 i 0

о

11101 1101-1

1-1-1 0 -11-1 1 ГТ-ТТ;

1101-1

О 1 1-1

1 1 1 0 1 1

Фиг. Z

шения количества умножителей, введена третья группа сумматоров, входы которых соединены с выходами сумма- , торов первой группы, первый выход

третьей группы сумматоров соединен . с первым входом второй группы сумматоров, а (1+1)-й выход третьей группы сумматоров соединен с входом 1-го 10 умножителя второй группы.

z,//;;

Г

Третья группа

гг(п)

ZjM

сунматороб

™i

j

Уг() У31) Фиг.З

| Устройство для частотного разделения многоканального цифрового сигнала | 1984 |

|

SU1226609A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-06-07—Публикация

1988-07-07—Подача