Изобретение относится к области электронных часов и может быть использовано в качестве счетчика (делителя) секунд и минут по модулю 60.

Цель изобретения - упрощение счетчика .

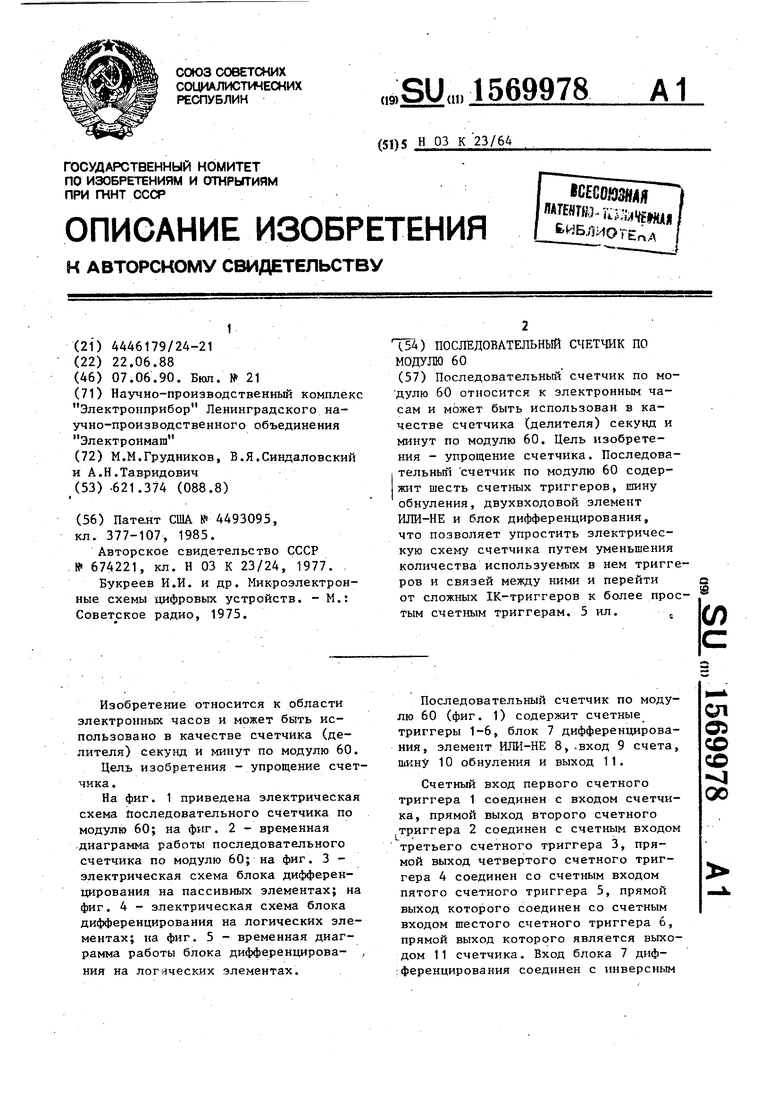

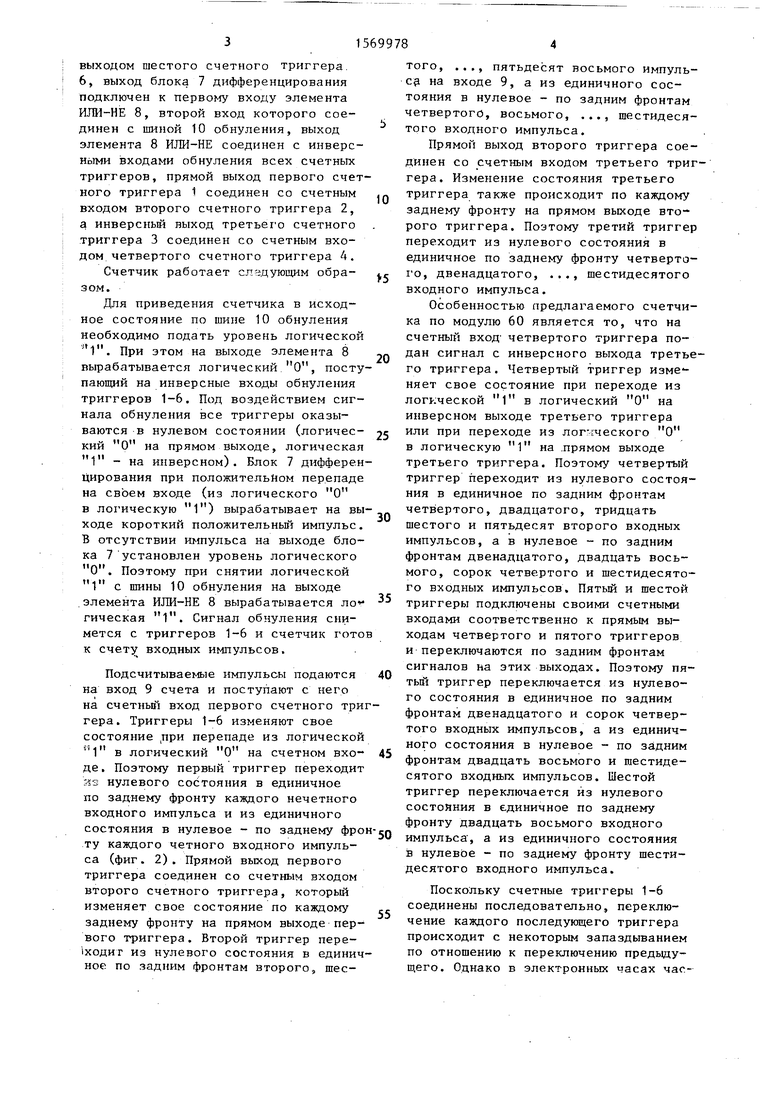

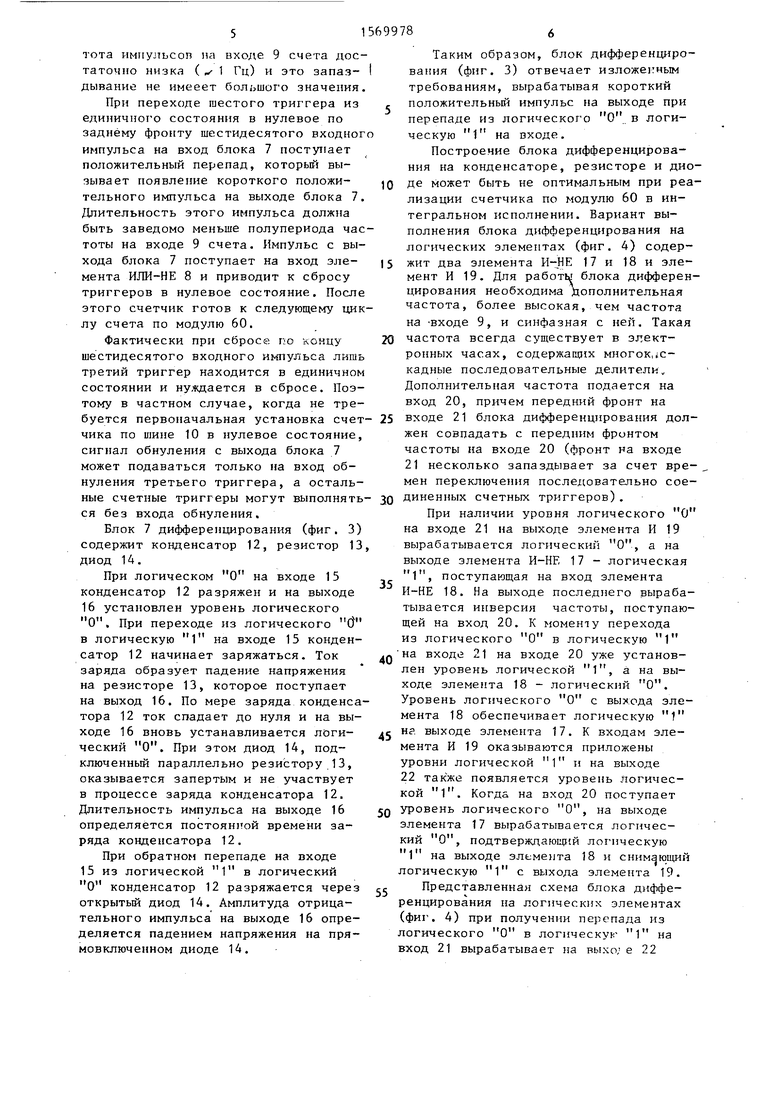

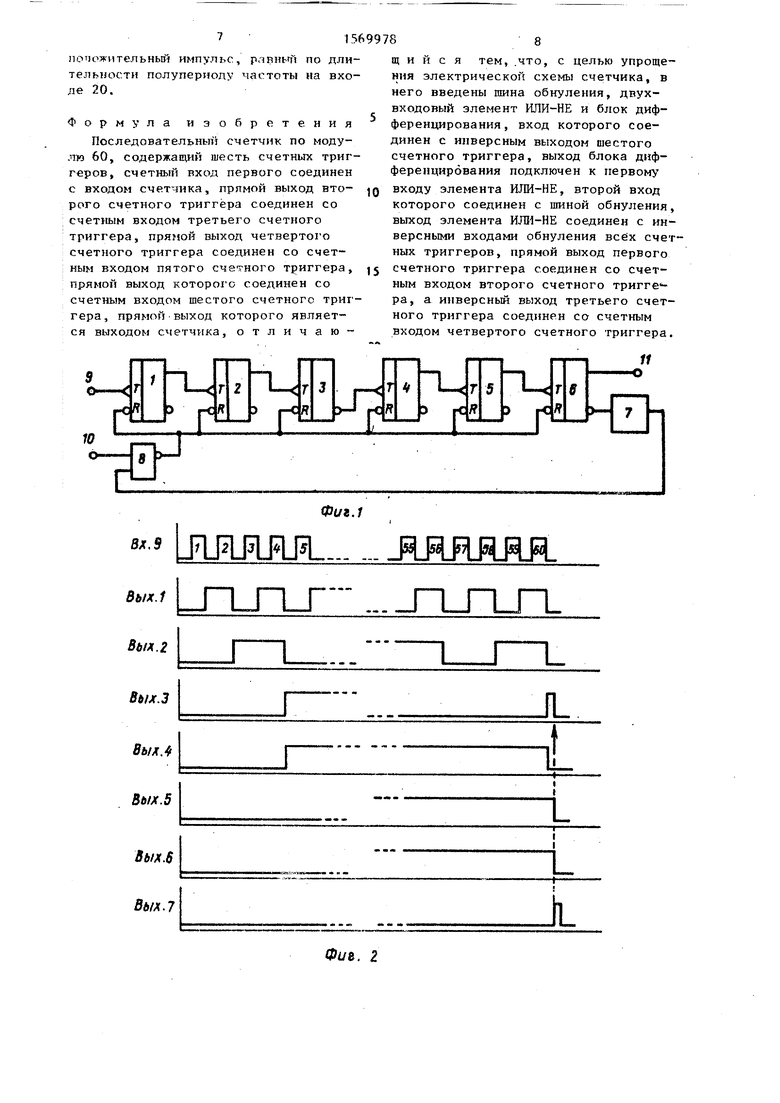

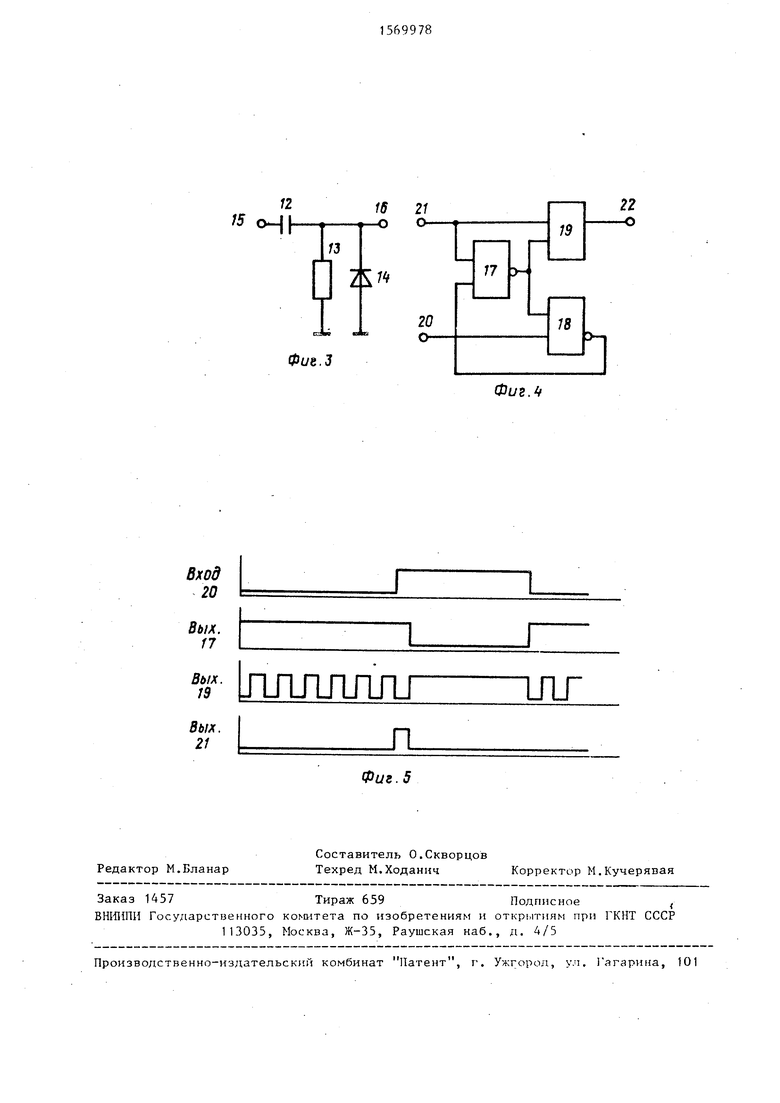

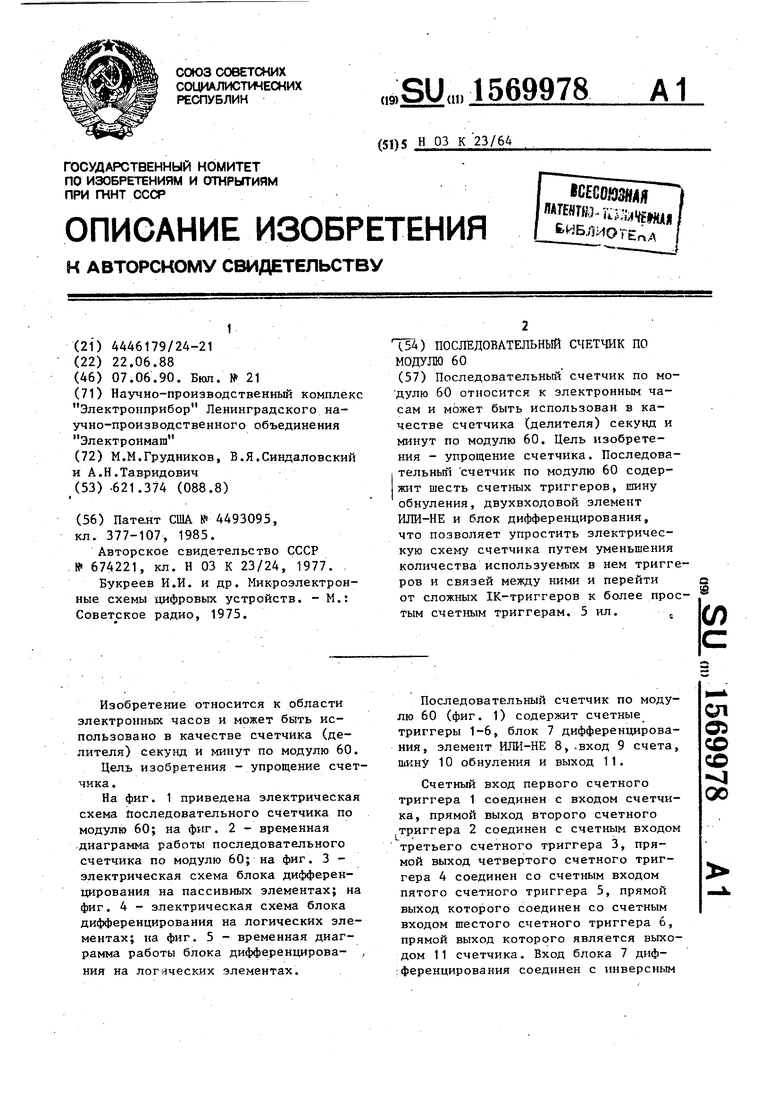

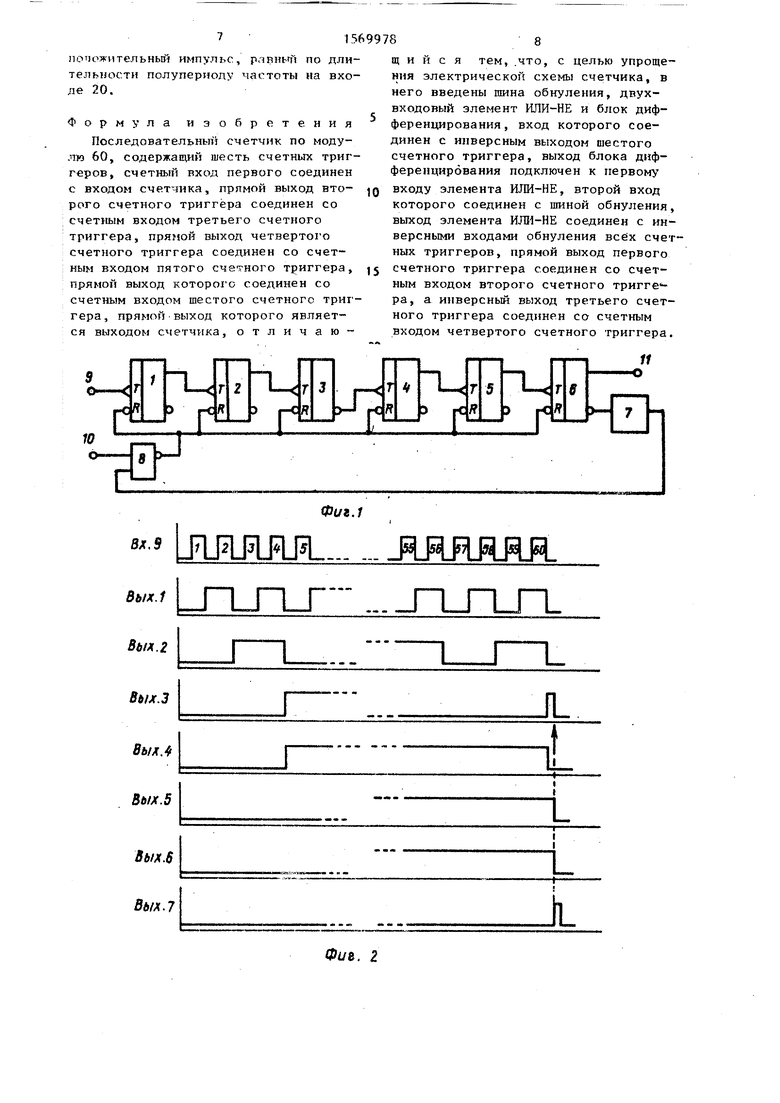

На фиг. 1 приведена электрическая схема последовательного счетчика по модулю 60; на фиг. 2 - временная диаграмма работы последовательного счетчика по модулю 60; на фиг. 3 - электрическая схема блока дифференцирования на пассивных элементах; на фиг. 4 - электрическая схема блока дифференцирования на логических элементах; на фиг. 5 - временная диаграмма работы блока дифференцирова- , ния на логических элементах.

Последовательный счетчик по модулю 60 (фиг. 1) содержит счетные триггеры 1-6, блок 7 дифференцирования, элемент ИЛИ-НЕ 8, -вход 9 счета, шину 10 обнуления и выход 11.

Счетный вход первого счетного триггера 1 соединен с входом счетчика, прямой выход второго счетного триггера 2 соединен с счетным входом третьего счетного триггера 3, прямой выход четвертого счетного триггера 4 соединен со счетным входом пятого счетного триггера 5, прямой выход которого соединен со счетным входом шестого счетного триггера 6, прямой выход которого является выходом 11 счетчика. Вход блока 7 дифференцирования соединен с инверсным

сл

& со со

vl

00

выходом шестого счетного триггера 6, выход блока 7 дифференцирования подключен к первому входу элемента ИЛИ-НЕ 8, второй вход которого соединен с шиной 10 обнуления, выход элемента 8 ИЛИ-НЕ соединен с инверсными входами обнуления всех счетных триггеров, прямой выход первого счетного триггера 1 соединен со счетным входом второго счетного триггера 2, а инверсный выход третьего счетного триггера 3 соединен со счетным входом четвертого счетного триггера 4.

Счетчик работает следующим обра- зом.

Для приведения счетчика в исходное состояние по шине 10 обнуления необходимо подать уровень логической 1. При этом на выходе элемента 8 вырабатывается логический О, поступающий на инверсные входы обнуления триггеров 1-6. Под воздействием сигнала обнуления все триггеры оказываются в нулевом состоянии (логичес- кий О на прямом выходе, логическая 1 - на инверсном). Блок 7 дифференцирования при положительном перепаде на своем входе (из логического О в логическую 1) вырабатывает на выходе короткий положительный импульс. В отсутствии импульса на выходе блока 7 установлен уровень логического О. Поэтому при снятии логической 1 с шины 10 обнуления на выходе элемента ИЛИ-НЕ 8 вырабатывается гическая 1. Сигнал обнуления снимется с триггеров 1-6 и счетчик гото к счету входных импульсов.

Подсчитываемые импульсы подаются на вход 9 счета и поступают с него на счетный вход первого счетного тригера. Триггеры 1-6 изменяют свое состояние ,при перепаде из логической 1 в логический О на счетном вхо- де. Поэтому первый триггер переходит нулевого состояния в единичное по заднему фронту каждого нечетного входного импульса и из единичного состояния в нулевое - по заднему фро ту каждого четного входного импульса (фиг. 2). Прямой выход первого триггера соединен со счетным входом второго счетного триггера, который изменяет свое состояние по каждому заднему фронту на прямом выходе первого триггера. Второй триггер пере- 1ходиг из нулевого состояния в единичное по задним фронтам второго, шес

Q

п 5

0 45зд ,-,

0

того, ..., пятьдесят восьмого импуль- сэ на входе 9, а из единичного состояния в нулевое - по задним фронтам четвертого, восьмого, ..., шестидесятого входного импульса.

Прямой выход второго триггера соединен со счетным входом третьего триггера. Изменение состояния третьего триггера также происходит по каждому заднему фронту на прямом выходе второго триггера. Поэтому третий триггер переходит из нулевого состояния в единичное по заднему фронту четвертого, двенадцатого, ..., шестидесятого входного импульса.

Особенностью предлагаемого счетчика по модулю 60 является то, что на счетный вход1 четвертого триггера подан сигнал с инверсного выхода третьего триггера. Четвертый триггер изменяет свое состояние при переходе из логической 1 в логический О на инверсном выходе третьего триггера или при переходе из логического О в логическую 1 на прямом выходе третьего триггера. Поэтому четвертый триггер переходит из нулевого состояния в единичное по задним фронтам четвертого, двадцатого, тридцать шестого и пятьдесят второго входных импульсов, а в нулевое - по задним фронтам двенадцатого, двадцать восьмого, сорок четвертого и шестидесятого входных импульсов. Пятый и шестой триггеры подключены своими счетными входами соответственно к прямым выходам четвертого и пятого триггеров и переключаются по задним фронтам сигналов на этих выходах. Поэтому пятый триггер переключается из нулевого состояния в единичное по задним фронтам двенадцатого и сорок четвертого входных импульсов, а из единичного состояния в нулевое - по задним фронтам двадцать восьмого и шестидесятого входных импульсов. Шестой триггер переключается из нулевого состояния в единичное по заднему фронту двадцать восьмого входного импульса, а из единичного состояния в нулевое - по заднему фронту шестидесятого входного импульса.

Поскольку счетные триггеры 1-6 соединены последовательно, переключение каждого последующего триггера происходит с некоторым запаздыванием по отношению к переключению предыдущего. Однако в электронных иасах частота импульсов па входе. 9 счета достаточно низка ( 1 Гц) и это запаз- I дывание не имееет большого значения.

При переходе шестого триггера из единичного состояния в нулевое по заднему фронту шестидесятого входного импульса на вход блока 7 поступает положительный перепад, который вызывает появление короткого положительного импульса на выходе блока 7. Длительность этого импульса должна быть заведомо меньше полупериода частоты на входе 9 счета. Импульс с выхода блока 7 поступает на вход элемента ИЛИ-НЕ 8 и приводит к сбросу триггеров в нулевое состояние. После этого счетчик готов к следующему циклу счета по модулю 60.

Фактически при сбросе по концу шестидесятого входного импульса лишь третий триггер находится в единичном состоянии и нуждается в сбросе. Поэтому в частном случае, когда не треТаким образом, блок дифференцирования (фиг. 3) отвечает изложенным требованиям, вырабатывая короткий положительный импульс на выходе при перепаде из логического О в логическую 1 на входе.

Построение блока дифференцирования на конденсаторе, резисторе и диоJQ де может быть не оптимальным при реализации счетчика по модулю 60 в интегральном исполнении. Вариант выполнения блока дифференцирования на логических элементах (фиг. 4) содер15 жит два элемента И-НЕ 17 и 18 и элемент И 19. Для работы блока дифференцирования необходима дополнительная частота, более высокая, чем частота на входе 9, и синфазная с ней. Такая

20 частота всегда существует в электронных часах, содержащих многокаскадные последовательные делители„ Дополнительная частота подается на вход 20, причем передний фронт на

буется первоначальная установка счет- 25 входе 21 блока дифференцирования долТаким образом, блок дифференцирования (фиг. 3) отвечает изложенным требованиям, вырабатывая короткий положительный импульс на выходе при перепаде из логического О в логическую 1 на входе.

Построение блока дифференцирования на конденсаторе, резисторе и диоде может быть не оптимальным при реализации счетчика по модулю 60 в интегральном исполнении. Вариант выполнения блока дифференцирования на логических элементах (фиг. 4) содержит два элемента И-НЕ 17 и 18 и элемент И 19. Для работы блока дифференцирования необходима дополнительная частота, более высокая, чем частота на входе 9, и синфазная с ней. Такая

частота всегда существует в электронных часах, содержащих многокаскадные последовательные делители„ Дополнительная частота подается на вход 20, причем передний фронт на

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для допускового контроля длительности последовательности временных интервалов | 1988 |

|

SU1647508A1 |

| Измеритель временных параметров случайных импульсных потоков | 1988 |

|

SU1575135A1 |

| Устройство для обработки сообщений | 1990 |

|

SU1803919A1 |

| Устройство генерации импульсов управления шаговым двигателем с электронной коррекцией | 1991 |

|

SU1829022A1 |

| Цифровой частотомер | 1981 |

|

SU1068834A1 |

| Устройство для передачи информации | 1989 |

|

SU1700571A1 |

| Сигнатурный анализатор | 1986 |

|

SU1357961A1 |

| Часовое устройство с полуавтоматической коррекцией | 1988 |

|

SU1670673A1 |

| Устройство для контроля цифровых сигналов | 1981 |

|

SU1032428A1 |

| Устройство для подключения источника информации к общей магистрали ЭВМ | 1990 |

|

SU1835547A1 |

Последовательный счетчик по модулю 60 относится к электронным часам и может быть использован в качестве счетчика (делителя) секунд и минут по модулю 60. Цель изобретения - упрощение счетчика. Последовательный счетчик по модулю 60 содержит шесть счетных триггеров, шину обнуления, двухвходовой элемент ИЛИ-НЕ и блок дифференцирования, что позволяет упростить электрическую схему счетчика путем уменьшения количества используемых в нем триггеров и связей между ними и перейти от сложных JK-триггеров к более простым счетным триггерам. 5 ил.

чика по шине 10 в нулевое состояние, сигнал обнуления с выхода блока 7 может подаваться только на вход обнуления третьего триггера, а остальные счетные триггеры могут выполняться без входа обнуления.

Блок 7 дифференцирования (фиг. 3) содержит конденсатор 12, резистор 13 диод 14.

При логическом О на входе 15 конденсатор 12 разряжен и на выходе 16 установлен уровень логического О. При переходе из логического О4 в логическую 1 на входе 15 конденсатор 12 начинает заряжаться. Ток заряда образует падение напряжения на резисторе 13, которое поступает на выход 16. По мере заряда конденсатора 12 ток спадает до нуля и на выходе 16 вновь устанавливается логический О. При этом диод 14, подключенный параллельно резистору 13, оказывается запертым и не участвует в процессе заряда конденсатора 12. Длительность импульса на выходе 16 определяется постоянной времени заряда конденсатора 12.

При обратном перепаде на входе 15 из логической 1 в логический О конденсатор 12 разряжается через открытый диод 14. Амплитуда отрицательного импульса на выходе 16 определяется падением напряжения на пря- мовключенном диоде 14.

0

5

0

5

0

5

жен совпадать с передним фронтом частоты на входе 20 (фронт на входе 21 несколько запаздывает за счет времен переключения последовательно соединенных счетных триггеров).

При наличии уровня логического О на входе 21 на выходе элемента И 19 вырабатывается логический О, а на выходе элемента И-НЕ 17 - логическая 1, поступающая на вход элемента И-НЕ 18. На выходе последнего вырабатывается инверсия частоты, поступающей на вход 20. К моменту перехода из логического О в логическую 1 на входе 21 на входе 20 уже установлен уровень логической 1, а на выходе элемента 18 - логический О. Уровень логического О с выхода элемента 18 обеспечивает логическую 1 н выходе элемента 17. К входам элемента И 19 оказываются приложены уровни логической 1 и на выходе 22 также появляется уровень логической 1. Когда на вход 20 поступает уровень логического О, на выходе элемента 17 вырабатывается логический О, подтверждающий логическую

1 на выходе элемента 18 и снимающий логическую 1 с выхода элемента 19. Представленная схема блока дифференцирования на логических элементах (фиг. 4) при получении перепада из логического О в логическую 1 на вход 21 вырабатывает на выхо; е 22

почожитепьныи импупьс, p.iBHbii по длительности полупериолу частоты на входе 20.

Формула изобретения Последовательный счетчик по модули 60, содержащий шесть счетных триггеров, счетный вход первого соединен с входом счетчика, прямой выход второго счетного триггера соединен со счетным входом третьего счетного триггера, пряной выход четвертого счетного триггера соединен со счетным входом пятого счетного триггера, прямой выход которого соединен со счетным входом шестого счетного триггера, прямой выход которого является выходом счетчика, отличаю70

на

г

ыП

г-1

Фиг.1

в -3 LFLRELRJL RAFIRRR.

Вых. 1

игТ-П-Г ... -TLTLTL

Фиг. I

5

щ и и с я тем, что, с целью упрощения электрической схемы счетчика, в него введены шина обнуления, двух- входовый элемент ИЛИ-НЕ и блок дифференцирования, вход которого соединен с инверсным выходом шестого счетного триггера, выход блока дифференцирования подключен к первому

входу элемента ИЛИ-НЕ, второй вход которого соединен с шиной обнуления, выход элемента ИЛИ-НЕ соединен с инверсными входами обнуления всех счетных триггеров, прямой выход первого счетного триггера соединен со счетным входом второго счетного тригге - ра, а инверсный выход третьего счетного триггера соединен со счетным входом четвертого счетного триггера.

U

г

8

11

ФиъЛ

| Патент США № 4493095, кл | |||

| Устройство для получения водяного пара и подведения его в толщу горящего топлива | 1921 |

|

SU377A1 |

| Счетчик с регулируемым коэффициентом пересчета | 1977 |

|

SU674221A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Букреев И.И | |||

| и др | |||

| Микроэлектронные схемы цифровых устройств | |||

| - М.: Советское радио, 1975. | |||

Авторы

Даты

1990-06-07—Публикация

1988-06-22—Подача