Изобретение относится к вычислительной технике и может быть использовано при контроле и диагностировании неисправностей цифровых; узлов и блоков устройств автоматики и вычис- лительной техники.

Цель изобретения - повышение диагностической точности анализатора за счет обеспечения локализации искаженных разрядов параллельного вход ного потока контролируе1 1х сигналов.

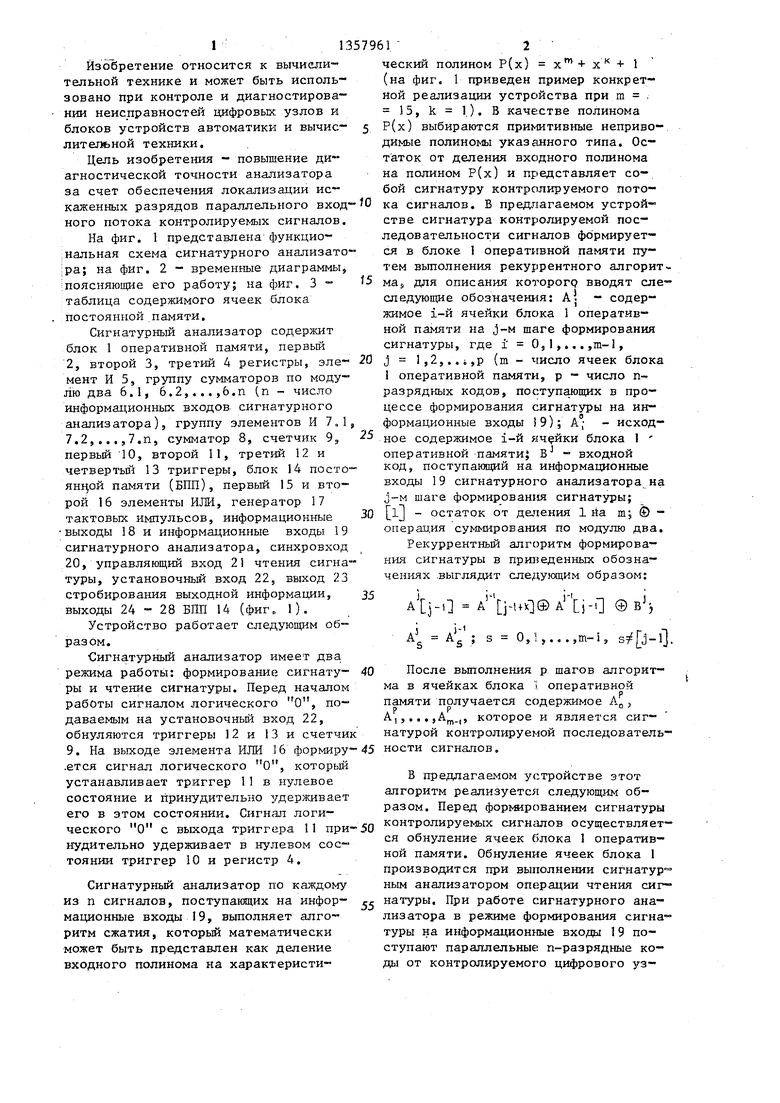

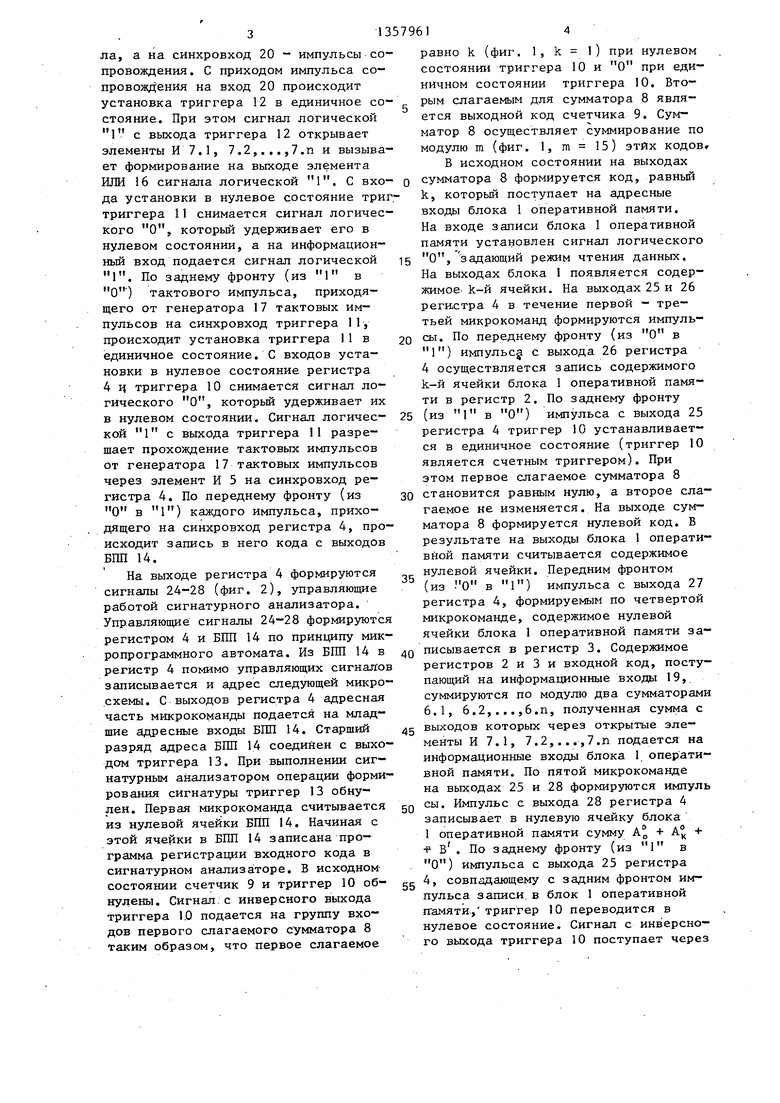

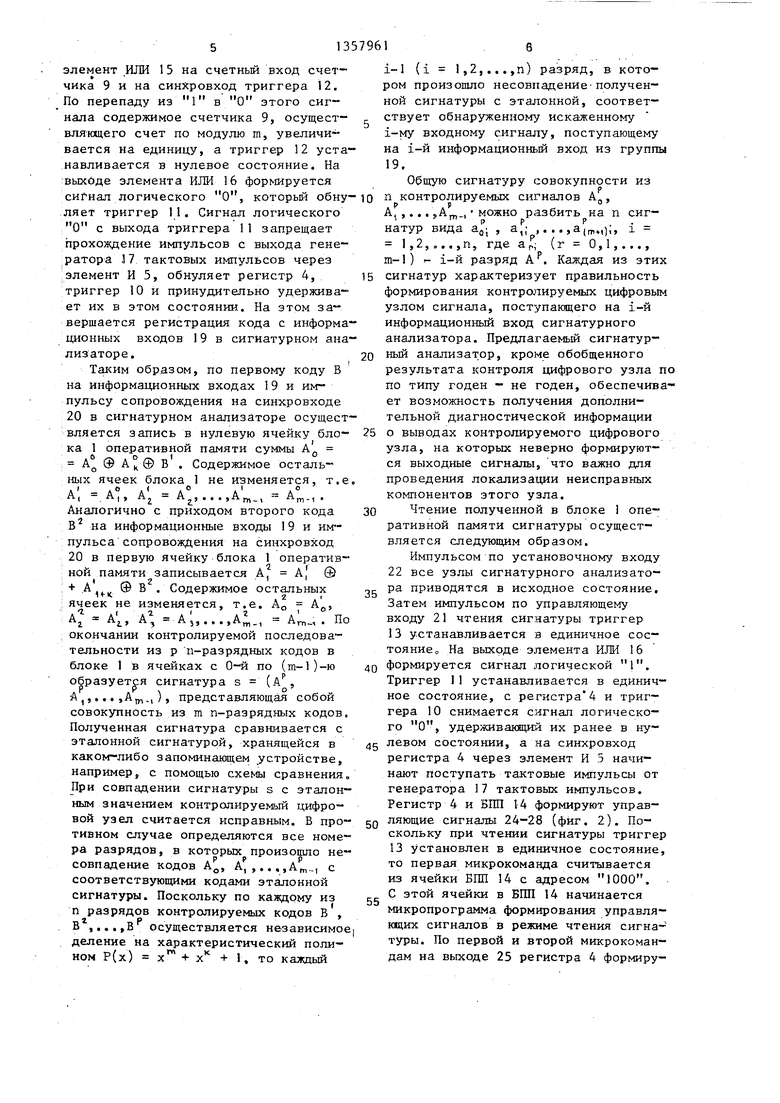

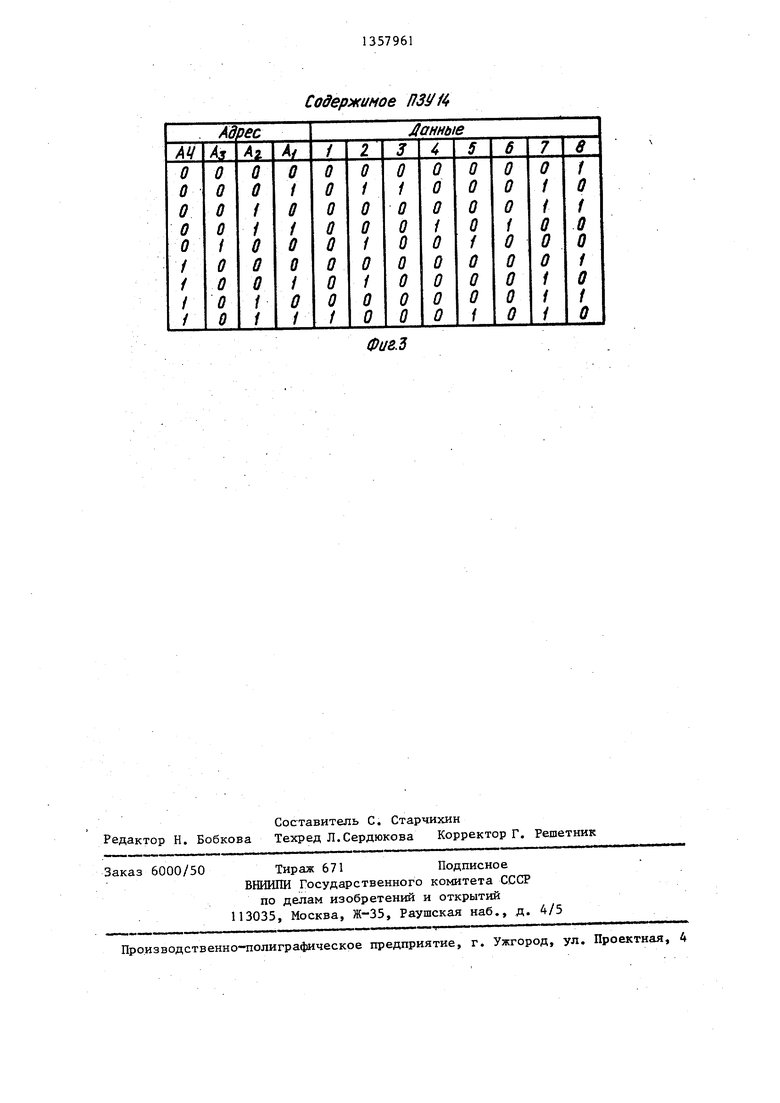

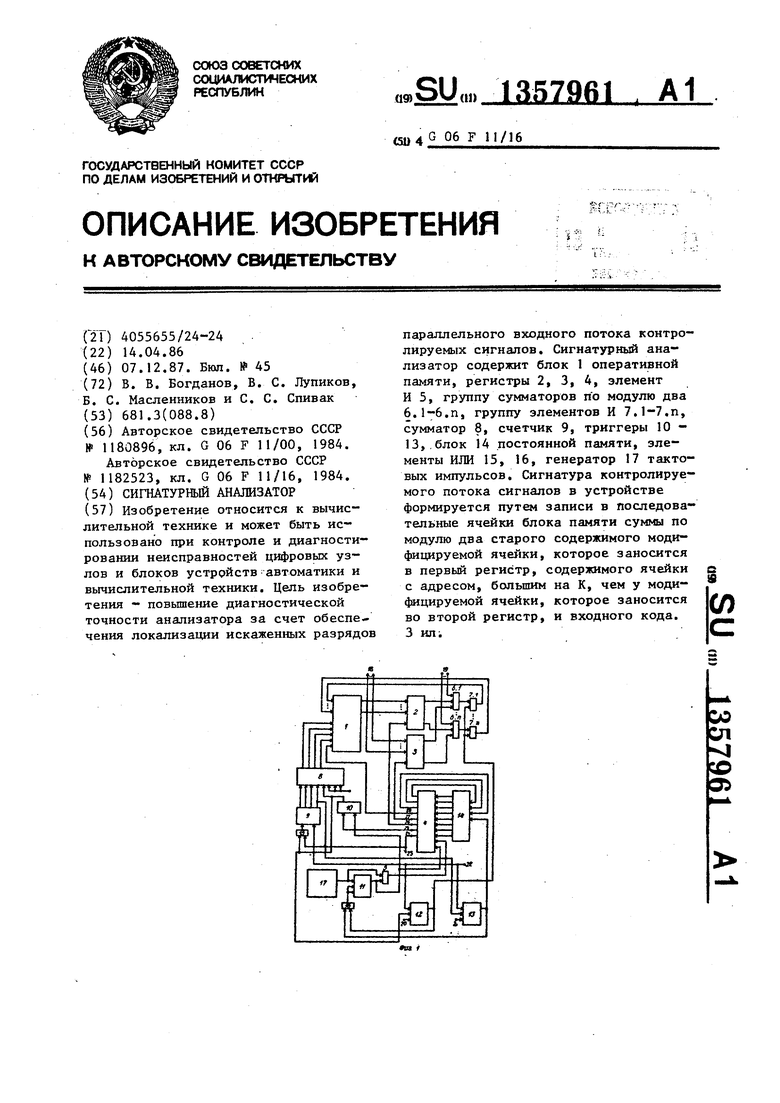

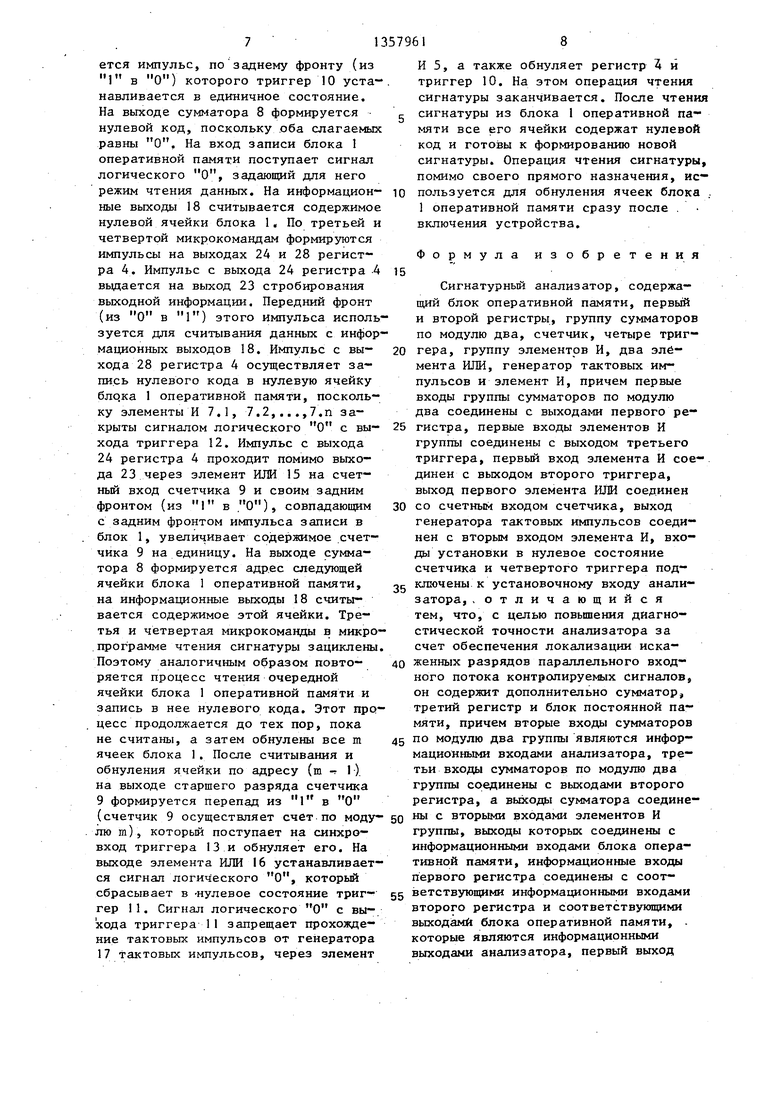

На фиг. 1 представлена функцио- :нальная схема сигнатурного анализато :ра; на фиг. 2 - временные диаграммы, ;поясняющие его работу; на фиг. 3 таблица содержимого ячеек блока постоянной памяти.

Сигнатурньш анализатор содержит блок 1 оперативной памяти, первый 2, второй 3, третий 4 регистры, эле мент И 5, группу сумматоров по модулю два 6.1, 6.2,4..,6.п (п - число информационных входов сигнатурного анализатора), группу элементов И 7.2,...,7.п, сумматор 8, счетчик 9, первьй 10, второй 11, третий 12 и четвертьй 13 триггеры, блок 14 посто янцой памяти (БПП), первый 15 и второй 16 элементы ИЛИ, генератор 17

тактовых импульсов, информационные

выходы 18 и информационные входы 19 сигнатурного анализатора, синхровход 20, управляющий вход 21 чтения сигна туры, установочньй вход 22, ввкод 23 стробирования выходной информации, выходы 24 - 28 БПП 14 (фиг. 1).

Устройство работает следующим образом.

Сигнатурный анализатор имеет два режима работы: формирование сигнату- ры и чтение сигнатуры. Перед началом работы сигналом логического О, подаваемым на установочньй вход 22, обнуляются триггеры 12 и 13 и счетчик 9. На выходе элемента ИЛИ 16 формиру.ется сигнал логического О, которьй устанавливает триггер 11 в нулевое состояние и принудительно удерживает его в этом состоянии. Сигнал логического О с выхода триггера 11 принудительно удерживает в нулевом состоянии триггер 10 и регистр 4.

Сигнатурный анализатор по каждому из п сигналов, поступакнцих на инфор- мационные входы 19, выполняет алгоритм сжатия, который математически может быть представлен как деление входного полинома на характеристи

0 5

0

5

0 5 0

ческий полином Р(х) (на фиг. 1 приведен пример конкретной реализации устройства при m . 15, k 1). В качестве полинома Р(х) выбираются примитивные неприводимые полиномы указанного типа. Остаток от деления входного полинома на полином Р(х) и представляет со-, бой сигнатуру контролируемого потока сигналов. В предлагаемом устройстве сигнатура контролируемой последовательности сигналов формируется в блоке 1 оперативной памяти путем вьшолнения рекуррентного алгоритма., для описания которогр вводят еле- следующие обозначения: А. - содержимое i-й ячейки блока 1 оперативной памяти на j-м шаге формирования сигнатуры, где i 0,1,... ,m-1, j l,2,..i,p (m - число ячеек блока 1 оперативной памяти, р - число п- разрядных кодов, поступающих в процессе формирования сигнатуры на информационные входы 9); А - исходное содержимое i-й ячейки блока 1 оперативной памяти} Б - входной код, поступанлций на информационные входы 19 сигнатурнох о анализатора на J-M шаге формирования сигнатуры; l - остаток от деления 1 На т; © - операция сумьшрования по модулю два. Рекуррентньй алгоритм формирования сигнатуры в приведенных обозначениях .выглядит следующим образом:

Atj-t А j-UiQ® А j-i ® A g s О,,...,m-i, .

После выполнения р шагов алгоритма в ячейках блока 1 оперативной памяти получается содержимое А j А,,..,,А„,, которое и является сигнатурой контролируемой последовательности сигналов.

В предлагаемом устройстве этот алгоритм реализуется следующим образом. Перед фор№1рованием сигнатуры контролируемых сигналов осуществляется обнуление ячеек блока 1 оперативной памяти. Обнуление ячеек блока 1 производится при выполнении сигнатур- ньм анализатором операции чтения сигнатуры. При работе сигнатурного анализатора в режиме формирования сигнатуры на информационные входы 19 поступают параллельные п-разрядные коды от контролируемого цифрового уз3135796 4

, а на синхровход 20 - импульсы со- равно k (фиг. 1, k 1) при нулевом

ла

провождения. С приходом импульса со провождения на вход 20 происходит установка триггера 12 в единичное состояние. При этом сигнал логической 1 с выхода триггера 12 открывает элементы И7.1, 7.2,...,7.п и вызывает формирование на выходе элемента ИЛИ 16 сигнала логической 1. С входа установки в нулевое с.остояние триг- триггера 11 снимается сигнал логического О, которьш удерживает его в нулевом состоянии, а на информационный вход подается сигнал логической 1. По заднему фронту (из 1 в ) тактового импульса, приходящего от генератора 17 тактовых импульсов на синхровход триггера 11, происходит установка триггера I1 в единичное состояние. С входов установки в нулевое состояние регистра 4 ц триггера 10 снимается сигнал логического О, которьй удерживает их в нулевом состоянии. Сигнал логической 1 с выхода триггера 11 разрешает прохождение тактовых импульсов от генератора 17 тактовых импульсов через элемент И 5 на синхровход регистра 4. По переднему фронту (из О в 1) каждого импульса, приходящего на синхровход регистра 4, происходит запись в него кода с выходов БШ1 14.

На выходе регистра 4 формируются сигналы 24-28 (фиг. 2), управляющие работой сигнатурного анализатора. Управляющие сигналы 24-28 формируются регистром 4 и БПП 14 по принципу микропрограммного автомата. Из БПП 14 в регистр 4 помимо управляющих сигналов записывается и адрес следующей микросхемы. С выходов регистра 4 адресная часть микрокоманды подается на младшие адресные входы БПП 14. Старший разряд адреса БПП 14 соедийен с выходом триггера 13. При выполнении сигнатурным анализатором операции формирования сигнатуры триггер 13 обнулен. Первая микрокоманда считывается из нулевой ячейки БПП 14. Начиная с этой ячейки в БПП 14 записана программа регистрации входного кода в сигнатурном анализаторе. В исходном

состоянии триггера 10 и О при единичном состоянии триггера 10. Вторым слагаемым для сумматора 8 является выходной код счетчика 9. Сумматор 8 осуществляет суммирование по модулю m (фиг. 1, m 15) этих кодов

В исходном состоянии на выходах О сумматора 8 формируется код, равньй k, который поступает на адресные входы блока 1 оперативной памяти. На входе записи блока 1 оперативной

15

памяти установлен сигнал логического О,

20

задающий режим чтения данных. На выходах блока I появляется содержимое k-й ячейки. На выходах 25 и 26 регистра 4 в течение первой - третьей микрокоманд формируются импульсы. По переднему фронту (из О в 1) импульсу с выхода 26 регистра 4 осуществляется запись содержимого k-й ячейки блока 1 оперативной памяти в регистр 2. По заднему фронту

25 (из 1 в О) импульса с выхода 25 регистра 4 триггер 10 устанавливается в единичное состояние (триггер 10 является счетным триггером). При этом первое слагаемое сумматора 8

30 становится равным нулю, а второе слагаемое не изменяется. На выходе сумматора 8 формируется нулевой код. В результате на выходы блока 1 оперативной памяти считывается содержимое нулевой ячейки. Передним фронтом (из в 1) импульса с выхода 27 регистра 4, формируемым по четвертой микрокоманде, содержимое нулевой ячейки блока 1 оперативной памяти записывается в регистр 3. Содержимое регистров 2 и 3 и входной код, поступающий на информационные входы 19,. суммируются по модулю два сумматорами 6.1, 6.2,...,6.п, полученная сумма с

jg выходов которых через открытые элементы И 7.1, 7.2,...,7.п подается на информационные входы блока 1 оперативной памяти. По пятой микрокоманде на выходах 25 и 28 формируются импуль сы. Импульс с выхода 28 регистра 4 записывает в нулевую ячейку блока 1 оперативной памяти сумму А° + А + 4 в . По заднему фронту (из 1 в О) импульса с выхода 25 регистра

35

40

50

состоянии счетчик 9 и триггер 10 об- gg 4, совпадающему с задним фронтом импульса записи, в блок 1 оперативной памяти, триггер 10 Переводится в нулевое состояние. Сигнал с инверсного выхода триггера 10 поступает через

нулены. Сигнал.с инверсного выхода триггера 1.0 подается на группу входов первого слагаемого сумматора 8 таким образом, что первое слагаемое

состоянии триггера 10 и О при единичном состоянии триггера 10. Вторым слагаемым для сумматора 8 является выходной код счетчика 9. Сумматор 8 осуществляет суммирование по модулю m (фиг. 1, m 15) этих кодов

В исходном состоянии на выходах сумматора 8 формируется код, равньй k, который поступает на адресные входы блока 1 оперативной памяти. На входе записи блока 1 оперативной

памяти установлен сигнал логического О,

задающий режим чтения данных. На выходах блока I появляется содержимое k-й ячейки. На выходах 25 и 26 регистра 4 в течение первой - третьей микрокоманд формируются импульсы. По переднему фронту (из О в 1) импульсу с выхода 26 регистра 4 осуществляется запись содержимого k-й ячейки блока 1 оперативной памяти в регистр 2. По заднему фронту

(из 1 в О) импульса с выхода 25 регистра 4 триггер 10 устанавливается в единичное состояние (триггер 10 является счетным триггером). При этом первое слагаемое сумматора 8

становится равным нулю, а второе слагаемое не изменяется. На выходе сумматора 8 формируется нулевой код. В результате на выходы блока 1 оперативной памяти считывается содержимое нулевой ячейки. Передним фронтом (из в 1) импульса с выхода 27 регистра 4, формируемым по четвертой микрокоманде, содержимое нулевой ячейки блока 1 оперативной памяти записывается в регистр 3. Содержимое регистров 2 и 3 и входной код, поступающий на информационные входы 19,. суммируются по модулю два сумматорами 6.1, 6.2,...,6.п, полученная сумма с

выходов которых через открытые элементы И 7.1, 7.2,...,7.п подается на информационные входы блока 1 оперативной памяти. По пятой микрокоманде на выходах 25 и 28 формируются импуль сы. Импульс с выхода 28 регистра 4 записывает в нулевую ячейку блока 1 оперативной памяти сумму А° + А + 4 в . По заднему фронту (из 1 в О) импульса с выхода 25 регистра

4, совпадающему с задним фронтом импульса записи, в блок 1 оперативной памяти, триггер 10 Переводится в нулевое состояние. Сигнал с инверсного выхода триггера 10 поступает через

элемент .ИЛИ 15 на счетньй вход счет чика 9 и на синХровход триггера 12. По перепаду из 1 в О этого сигнала содержимое счетчика 9, осуществляющего счет по модулю т, увеличи- вается на единицу, а триггер 12 устанавливается в нулевое состояние. На выходе элемента ИЛИ 16 фop иpyeтcя

13579616

1-1 (i - 1,2,...,п) разряд.

ром произошло несовпадениеной сигнатуры с эталонной, ствует обнаруженному искаже i-му входному сигналу, пост на i-й информационный вход 19.

Общую сигнатуру совокупн

р

сигнал логического О, который обну-ю п контролируемых сигналов А,

А, ,... 5 А, можно разбить на п натур вида , af.,

15

ляет триггер 11. Сигнал логического О с выхода триггера 11 запрещает прохождение импульсов с выхода генератора 37 тактовых импульсов через :элемент И 5, обнуляет регистр 4, триггер 10 и принудительно удерживает их в этом состоянии. На этом завершается регистрация кода с информационных входов 19 в сигнатурном анализаторе.20

Тшсим образом, по первому коду В на информационных входах 19 и импульсу сопровождения на синхровходе 20 в сигнатурном анализаторе осуществляется запись в нулевую ячейку блока 1 оперативной памяти суммы А А ® В . Содержимое остальных ячеек блока 1 не изменяется, т.е

J 11 J (ГГ«0

1 ,2, ..,, п, где а р, m-l) - i-й разряд А,

(г 0,1, Каждая и

д - А ( .)

А;

не изменяется, А А - А

.,

Аналогично с приходом второго кода В на информационные входы 19 и импульса сопровождения на синхровход 20 в первую ячейку блока 1 оперативной памяти записывается А

30

.., А; ®

Содержимое остальных

.2 .1

ячеек не изменяется, т.е. An

А .... ® в

-

35

АА,

гл с I Ч-л . - л5

I 91

А Д ТТп

Ч l. 7 5

окончании контролируемой последовательности из р п-разрядных кодов в блоке 1 в ячейках с О-и по (т-1)-ю

сигнатур характеризует правиль формирования контролируемых циф узлом сигнала, поступакщего на информационный вход сигнатурно анализатора. Предлагаемый сигн ный анализатор, кроме обобщенн результата контроля цифрового по типу годен - не годен, обес ет возможность получения допол тельной диагностической информ

25 о выводах контролируемого цифр узла, на которых неверно форми ся выходные сигналы, что важно проведения локализации неиспра компонентов этого узла.

Чтение полученной в блоке 1 ративной памяти сигнатуры осущ вляется следующим образом.

Импульсом по установочному 22 все узлы сигнатурного анали ра приводятся в исходное состо Затем импульсом по управляющем входу 21 чтения сигнатуры триг 13 устанавливается в единичное тояние На выходе элемента ИЛИ

4Q формируется сигнал логической Триггер 11 устанавливается в е ное состояние, с регистра 4 и гера 10 снимается сигнал логич го О, удерживакщий их ранее

об

(А

бразуется сигнатура s А ,,... ,А,, ), представляющая собой совокупность из m п-разрядных кодов. Полученная сигнатура сравнивается с эталонной сигнатурой, хранящейся в каком-либо запоминакнцем устройстве, например, с помощью схемы сравнения/ При совпадении сигнатуры s с эталонным значением контролируемый цифровой узел считается исправным. В противном случае определяются все номера разрядов, в которых произошло несовпадение кодов А, А ,...,.., с соответствующими кодами эталонной сигнатуры. Поскольку по каждому из п разрядов контролируемых кодов В , В ,...,В осуществляется независимое деление на характеристический полином Р(х) х + х + 1. то каждый

1-1 (i - 1,2,...,п) разряд.

в котором произошло несовпадениеполученной сигнатуры с эталонной, соответствует обнаруженному искаженному i-му входному сигналу, поступающему на i-й информационный вход из группы 19.

Общую сигнатуру совокупности из

р

п контролируемых сигналов А,

А, ,... 5 А, можно разбить на п натур вида , af.,

сиг-

J 11 J (ГГ«0 -

1 ,2, ..,, п, где а р, m-l) - i-й разряд А,

(г 0,1,.... Каждая из этих

0

5

сигнатур характеризует правильность формирования контролируемых цифровым узлом сигнала, поступакщего на i-й информационный вход сигнатурного анализатора. Предлагаемый сигнатурный анализатор, кроме обобщенного результата контроля цифрового узла по по типу годен - не годен, обеспечивает возможность получения дополнительной диагностической информации

5 о выводах контролируемого цифрового узла, на которых неверно формируются выходные сигналы, что важно для проведения локализации неисправных компонентов этого узла.

Чтение полученной в блоке 1 оперативной памяти сигнатуры осуществляется следующим образом.

Импульсом по установочному входу 22 все узлы сигнатурного анализатора приводятся в исходное состояние. Затем импульсом по управляющему входу 21 чтения сигнатуры триггер 13 устанавливается в единичное состояние На выходе элемента ИЛИ 16

Q формируется сигнал логической 1. Триггер 11 устанавливается в единичное состояние, с регистра 4 и триггера 10 снимается сигнал логического О, удерживакщий их ранее в ну-

g левом состоянии, а на синхровход регистра 4 через элемент И 5 начинают поступать тактовые импульсы от генератора 17 тактовых импульсов. Регистр 4 и ВПП 14 формируют управляющие сигналы 24-28 (фиг. 2). Поскольку при чтении сигнатуры триггер 13 установлен в единичное состояние, то первая микрокоманда считывается из ячейки БПП 14 с адресом 1000. С этой ячейки в БШ1 14 начинается микропрограмма формирования управляющих сигналов в режиме чтения сигнатуры. По первой и второй микрокомандам на выходе 25 регистра 4 формиру50

55

ется импульс, по заднему фронту (из 1 в О) которого триггер 10 уста-, навливается в единичное состояние. На выходе сумматора 8 формируется нулевой код, поскольку оба слагаемых равны О, На вход записи блока 1 оперативной памяти поступает сигнал логического О, задающий для него режим чтения данных. На информационные выходы 18 считывается содержимое нулевой ячейки блока 1, По третьей и четвертой микрокомандам формируются импульсы на выходах 24 и 28 регистра 4. Импульс с выхода 24 регистра 4 выдается на выход 23 стробирования выходной информации. Передний фронт (из О в 1) этого импульса используется для считывания данных с информационных выходов 18. Импульс с выхода 28 регистра 4 осуществляет запись нулевого кода в нулевую ячейку блдка 1 оперативной памяти, поскольку элементы И 7.1, 7.2,...,7.п за- крыты сигналом логического О с выхода триггера 12. Импульс с выхода 24 регистра 4 проходит помимо выхода 23 через элемент ИЛИ 15 на счетный вход счетчика 9 и своим задним фронтом (из I в О), совпадающим с задним фронтом импульса записи в блок 1, увеличивает содержимое счетчика 9 на единицу. На выходе сумматора 8 формируется адр.ес следующей ячейки блока 1 оперативной памяти, на информационные выходы 18 считывается содержимое этой ячейки. Третья и четвертая микрокоманды в микро- .программе чтения сигнатуры зациклены. Поэтому аналогичным образом повторяется процесс чтения очередной ячейки блока 1 оперативной памяти и запись в нее нулевого кода. Этот процесс продолжается до тех пор, пока не считаны, а затем обнулены все m ячеек блока 1. После считывания и обнуления ячейки по адресу (т - Г), на выходе старшего разряда счетчика 9 формируется перепад из 1 в О

10

15

20

25

30

35

И 5, а также обнуляет регистр -4 и триггер 10. На этом операция чтения сигнатуры заканчивается. После чтени сигнатуры из блока 1 оперативной памяти все его ячейки содержат нулевой код и готовы к формированию новой сигнатуры. Операция чтения сигнатуры помимо своего прямого назначения, ис пользуется для обнуления ячеек блока 1 оперативной памяти сразу после , включения устройства.

Формула изобретения

Сигнатурньй анализатор, содержащий блок оперативной памяти, первый и второй регистры, группу сумматоров по модулю два, счетчик, четыре триггера, группу элементов И, два элемента ИЛИ, генератор тактовых импульсов и элемент И, причем первые входы группы сумматоров по модулю два соединены с выходами первого регистра, первые входы элементов И группы соединены с выходом третьего триггера, первый вход элемента И сое динен с выходом второго триггера, выход первого элемента ИЛИ соединен со счетным входом счетчика, выход генератора тактовых импульсов соединен с вторым входом элемента И, входы установки в нулевое состояние счетчика и четвертого триггера подключены к установочному входу анализатора,

отличающийся

тем, что, с целью повьппения диагностической точности анализатора за счет обеспечения локализации иска40 женных разрядов параллельного входного потока контролируемых сигналов, он содержит дополнительно сумматор, третий регистр и блок постоянной памяти, причем вторые входы сумматоров

45 по модулю два группы являются информационными входами анализатора, третьи входы сумматоров по модулю два группы соединены с выходами второго регистра, а выходы сумматора соедине-

(счетчик 9

лю т), которьй поступает на синхро- вход триггера 13 и обнуляет его. На выходе элемента ИЛИ 16 устанавливаетосуществляет счет по моду- 50 ™ - вторыми входами элементов И

группы, выходы которых соединены с информационными входами блока оперативной памяти, информационные входы первого регистра соединены с соот- 55 ветствующими информационными входами второго регистра и соответствующими выходами блока оперативной памяти, . которые являются информационными выходами анализатора, первый выход

ся сигнал логического О , который сбрасывает в -нулевое состояние триг-

хода триггера 1I запрещает прохождение тактовых импульсов от генератора 17 тактовых импульсов, через элемент

5

0

5

0

5

И 5, а также обнуляет регистр -4 и триггер 10. На этом операция чтения сигнатуры заканчивается. После чтения сигнатуры из блока 1 оперативной памяти все его ячейки содержат нулевой код и готовы к формированию новой сигнатуры. Операция чтения сигнатуры, помимо своего прямого назначения, используется для обнуления ячеек блока .. 1 оперативной памяти сразу после , включения устройства.

Формула изобретения

Сигнатурньй анализатор, содержащий блок оперативной памяти, первый и второй регистры, группу сумматоров по модулю два, счетчик, четыре триггера, группу элементов И, два элемента ИЛИ, генератор тактовых импульсов и элемент И, причем первые входы группы сумматоров по модулю два соединены с выходами первого регистра, первые входы элементов И группы соединены с выходом третьего триггера, первый вход элемента И соединен с выходом второго триггера, выход первого элемента ИЛИ соединен со счетным входом счетчика, выход генератора тактовых импульсов соединен с вторым входом элемента И, входы установки в нулевое состояние счетчика и четвертого триггера подключены к установочному входу анализатора,

отличающийся

тем, что, с целью повьппения диагностической точности анализатора за счет обеспечения локализации иска40 женных разрядов параллельного входного потока контролируемых сигналов, он содержит дополнительно сумматор, третий регистр и блок постоянной памяти, причем вторые входы сумматоров

45 по модулю два группы являются информационными входами анализатора, третьи входы сумматоров по модулю два группы соединены с выходами второго регистра, а выходы сумматора соедине-

9

третьего регистра соединен с первым входом первого элемента ИЛИ и являет ся выходом стробирования выходной информации анализатора, второй, третий, уетвертый и пятый разрядные выходы третьего регистра соединены соответственно со счетным входом первого триггера, синхровходами первого и второго регистров и входом записи блока оперативной памяти, группа выходов третьего регистра соединена с группой младших адресных входов блока постоянной памяти,.выходы которого соединены с информационными вхо- ;дами третьего регистра, синхровход второго триггера соединен с выходом генератогра тактовых импульсов, вход установки в нулевое состояние второ-

го триггера соединен с выходом второ- 20 группа входов первого слагаемого

го элемента ИЛИ, а выход второго триггера соединен с входами установки в нулевое состояние третьего регистра и первого триггера, вход установки в единичное состояние третьего триггера является синхровходом анализатора, синхровход третьегоФормиробание сигнатуры

Фиг. 2

61

10

триггера соединен с вторым входом первого элемента ИЛИ, с инверсным выходом первого триггера и первой группой входов первого слагаемого сумматора, вход установки в нулевое состояние третьего триггера соединен с установо.чным входом анализатора, выход третьего триггера соединен с первым входом второго элемента ИЛИ, второй вход которого соединен со старшим адресным входом блока постоянной памяти и выходом четвертого триггера, вход установки в единичное состояние четвертого триггера является управляющим входом чтения сигнатуры анализатора, синхровход четвертого триггера соединен с выходом старшего разряда счетчика, вторая

сумматора соединена с шиной логического нуля, входы второго слагаемого соединены с выходами счетчика, а выходы сумматора соединены с адресными входами блока оперативной памяти, выход третьего элемента И соединен с синхровходом третьего регистра.

Чтение сигиат1/ры

Содержимое ПЗУ1

Составитель С. Старчихин Редактор Н. Бобкова Техред Л.Сердюкова Корректор Г. Решетник

6000/50

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-ттолиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг.д

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1262500A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЦИФРОВЫХ БЛОКОВ | 1991 |

|

RU2065202C1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1564693A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Многоканальный сигнатурный анализатор | 1987 |

|

SU1430956A1 |

| Параллельный сигнатурный анализатор | 1984 |

|

SU1182523A1 |

| Многовходовой сигнатурный анализатор | 1987 |

|

SU1478220A1 |

| Устройство для контроля цифровых блоков | 1986 |

|

SU1343417A1 |

Изобретение относится к вычислительной технике и может быть использовано при контроле и диагностировании неисправностей цифровых узлов и блоков устройств-автоматики и вычислительной техники. Цель изобретения - повышение диагностической точности анализатора за счет обеспечения локализации искаженных разрядов параллельного входного потока контролируемых сигналов. Сигнатурный анализатор содержит блок 1 оперативной памяти, регистры 2, 3, 4, элемент И 5, группу сумматоров по модулю два 6.1-6.П, группу элементов И 7.1-7.П, сумматор 8, счетчик 9, триггеры 10 - 13,,блок 14 постоянной памяти, элементы ИЛИ 15, 16, генератор 17 тактовых импульсов. Сигнатура контролируемого потока сигналов в устройстве формируется путем записи в последовательные ячейки блока памяти суммы по модулю два старого содержимого модифицируемой ячейки, которое заносится в первый регистр, содержимого ячейки с адресом, большим на К, чем у модифицируемой ячейки, которое заносится во второй регистр, и входного кода. 3 кп. i (Л со СП со а:

| Сигнатурный анализатор | 1983 |

|

SU1180896A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Параллельный сигнатурный анализатор | 1984 |

|

SU1182523A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-07—Публикация

1986-04-14—Подача