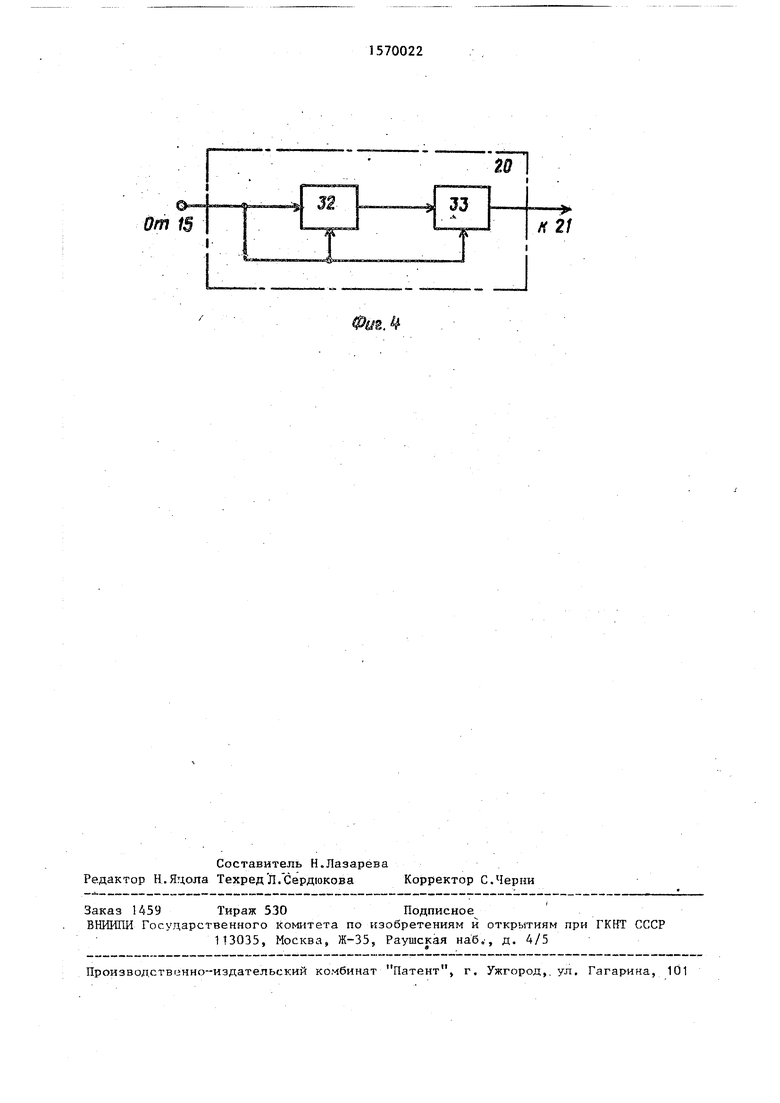

тальных компараторов будет напряжение сп ной ССП M (t) в блоке 6, но и дня по- URni, соответствующее логическому О. давления возможных спектральных сос- Набор логических О и логической тавляющих нелинейных искажений N(t),

возникающих при данном частотноизби- рательном ограничении ССП M(t). На

1, поступает на m входов блока 24, причем каждое напряжение U цп строго на определенный вход. Если ССП M(t) отсутствует, то на всех га входах блог ка 24 устанавливается напряжение логического О, при этом на выходе данного блока 24 будет также напря55

сигнальный вход режекторного фильтра 5 подается сигнал V2(t) с выхода блока 6. Поскольку полосы локализации нелинейных компонент N(t) определяются полосой df ; KK 25, то и полоса

сигнальный вход режекторного фильтра 5 подается сигнал V2(t) с выхода блока 6. Поскольку полосы локализации нелинейных компонент N(t) определяются полосой df ; KK 25, то и полоса

режекторного фильтра 5 dfp должна быть выбрана равной полосе данного КК 25 блока 6. После такого подавления линейного и нелинейного влияния ССП M(t) режекторного фильтра 5 очищенный сигнал

V3(t)

) + n(t),

(4)

где S(t) - зто S(t) с вырезным

участком спектра, который поражен линейным и локализованным в блоке б Нелинейным влиянием ССП M(t),

поступает на второй сигнальный вход коммутатора 4 и далее с его выхода на вход частотного детектора.

Перестраиваемый фильтр 7 выделяет полосу частот, занятую ССП M(t). При этом в полосу попадает и часть полезного, сигнала ). Ширина полосы прозрачности uf.n перестраиваемого фильтра и положение этой полосы на частотной оси f выбирается таким образом, чтобы максимизировать отношение помеха/сигнал 1/ Ьг в этой полосе частот 3fn. Центральная частота настройки Ј0 данного фильтра совпада- ет с частотой ССП M(t) и подстраивается под эту помеху под воздействием приложенного напряжения U упг -с первого управляющего выхода блока 6 на,управляющий вход перестраиваемого филь- тра 7.

Сигнал на входе адаптивного фильтра 8 можно представить в виде

VO

S,(t) + M/t) + n(t), (5)

где S,(t)

- часть полезного сигнала S(t), попавшая в полосу пропускания ff, перестраиваемого фильтра 7. Выходной сигнал адаптивного фильтра 8 имеет вид

Z,(t) W,(t). V«,(t)

(6)

где

Wf(t)

- изменяемая во времени импульсная характеристика адаптивного фильтра 8.

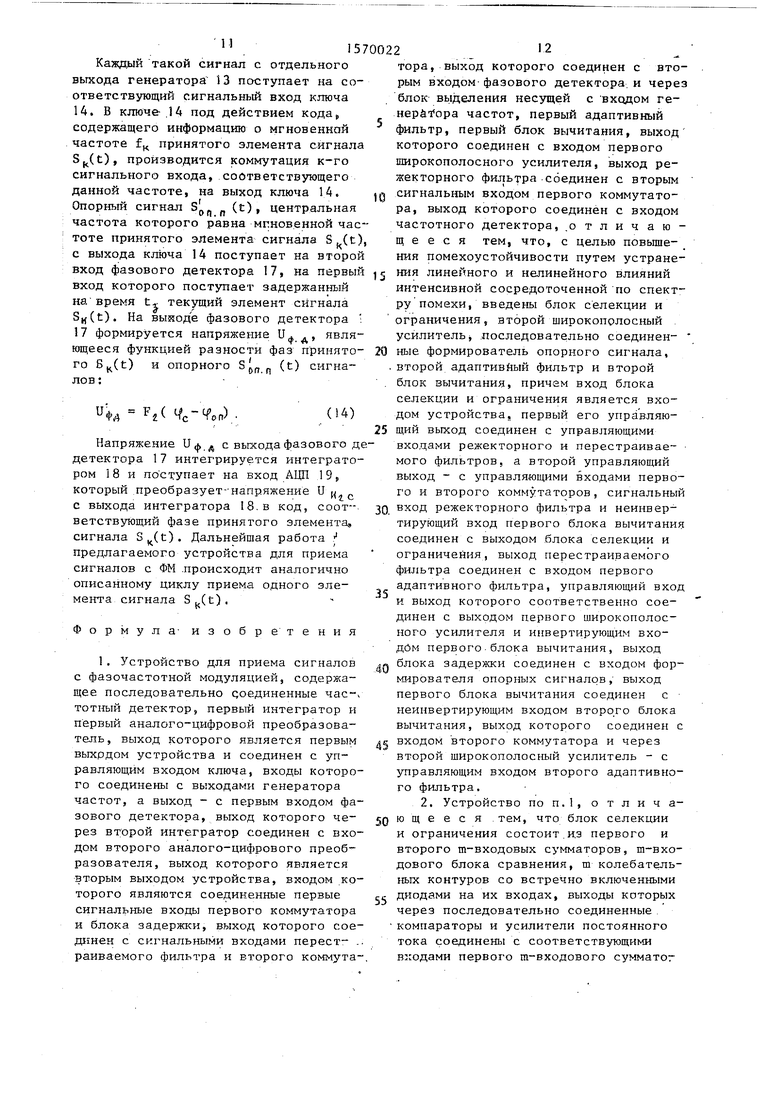

При воздействии сигнала ошибки Vj(t) с выхода широкополосного усилителя 16 на управляющий вход адаптивного фильтра 8 передаточной функции W,f(t) последнего изменяется таким об

00228

разом, что в блоке 9 обеспечивается оптимальное (по критерию минимума среднекрадратической ошибк и) лодавле- ние CCn.tytt) во входном воздействии V2(t). Действительно, совокупность из последовательно соединенных перемножителя 29 и интегратора 30 адаптивного фильтра 8 образуется корректор, выходной отклик которого Z (t) характеризует степень линейной «. стохастической взаимосвязи между воздей

10

о

0

5

0

5

0

5

ствием V,j(t) на сигнальном (т.е. с выхода перестраиваемого фильтра 7) и управляющем V5(t) (т.е. с выхода широкополосного усилителя 16) входах адаптивного фильтра 8. Этим и обеспечивается формирование выходного сигнала Z(t) адаптивного фильтра 8 в максимальной степени похожего на подаваемую ССП M(t) (а значит и ее подавление в блоке 9).

Таким образом адаптивный фильтр 8 учитывает и устраняет до блока 9 возможные различия характеристики при прохождении ССП M(t) от входа устройства через блок 6 до неинвертирующего входа блока 9 и от входа устройства через блок 15, перестраиваемый и адаптивный фильтры 7 и 8 до инвертирующего входа блока 9. Кроме того, необходимо отследить и возможные изменения собственно ССП M(t), претер- певшую частотно-селективные искажения в блоке 15 с практически неизбежной дисперсионностью ее характеристик. Адаптивный фильтр 8 также позволяет устранить влияние изменения характеристик ССП M(t) во времени (поскольку параметры ССП M(t) изменяются значительно медленнее, чем параметры полезного информационного сигнала S(t), который при высокоскоростной передаче сообщений является существенно более широкополосным по сравнению с подавляемой ССП M(t).

На неинвертирующий вход блока 9 поступает сигнал V4(t) с сигнального выхода блока 6, а на инвертирующий выход - сигнал с выхода адаптивного фильтра 8 Z, (t) . Выход сигнал блока 9 Vt(t) можно представить в виде

VO v4(t) - Z,(L) s(t) +

+ M,(t) + N(t) + n(t) - ). (7)

Для минимизации искажений сигнала S(t) необходимо повышать отношение сигнал/шум h1:

19

S(t)

(8)

i MjCty+nU)

на инвертирующем -входе блока 9 и уменьшать отношение сигнал/шум

S,(t)

M,Tt)+n(t)

10

на сигнальном входе адаптивного фильтра 8,

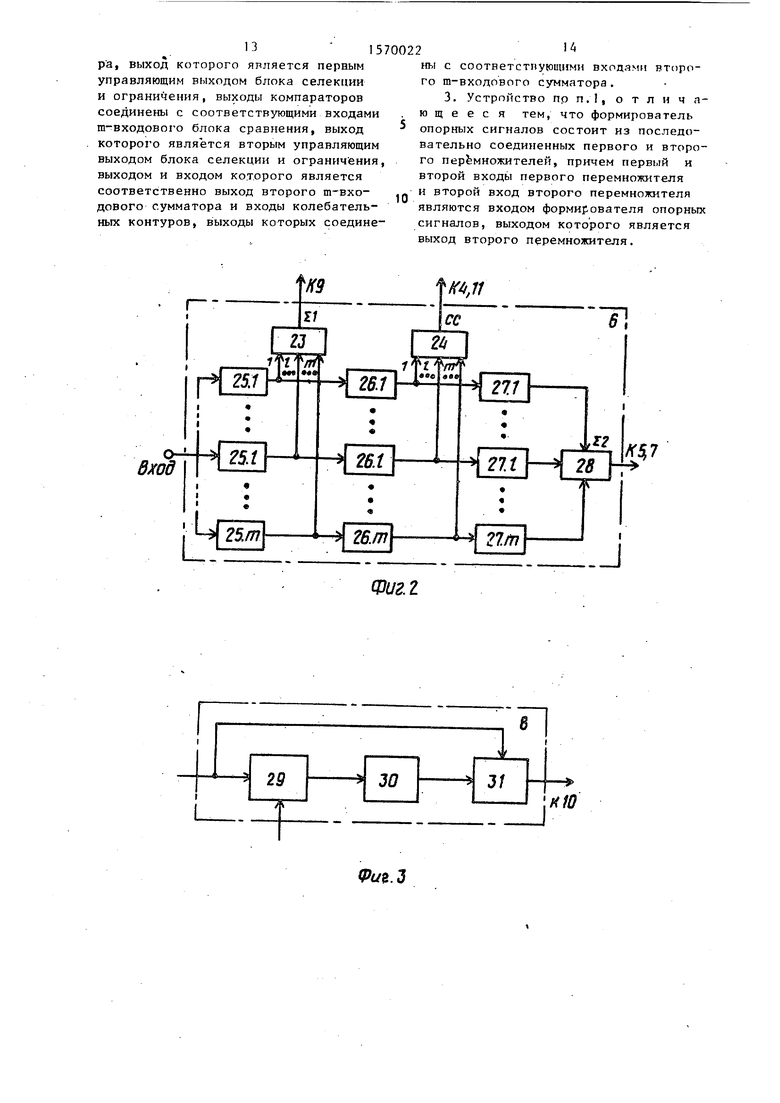

С выхода блока 15 входно е воздействие Vf(t) поступает также на вход формирователя 20 (устройство возведения в третью степень - кубатор), Входное воздействие V(t) поступает одновременно на оба входа первого перемножителя 32 и одновременно, на второй вход второго перемножителя 33.

Сигнал V(t) с выхода первого перемножителя 32 умножается во втором перемножителе 33 еще раз на сигнал Vt(t), чем обеспечивается воздействие в третью степень входного воздействия Vf(t) в блоке 20. Сигнал V(t) поступает на вход адаптивног9 фильтра 21. Формирование сигнала V(t) на выходе формирователя 20 связано с тем, что нелинейные искажения N(t) в блоке 5 обусловлены в основном нелинейными эффектами третьего порядка. На выходе адаптивного фильтра 21, принцип действия которого идентичен принципу дейтвия адаптивного фильтра 8, формируется сигнал Z4(t), в максимальной степени похожий на подавляемые (и ло- 35 кализованные в блоке 6) нелинейные компоненты N(t) сигнала S(t), поступающие на неинвертирующий вход блока 10 с выхода блока 9, причем

15

20

2S

30

Z4(t) Wt(t). V(t),

где W(t) -изменяемая во времени импульсная характеристика адаптивного фильтра 21.

При воздействии сигнала ошибки V.(t) с выхода широкополосного усили--. теля 22 Ни управляющий вход адаптивного фильтра 21 передаточная функция W(t) последнего изменяется таким образом, что в блоке 10 обеспечивается- оптимальное (по критерию минимума среднеквадратической ошибки) подавление нелинейных компонент N(t), возникших при часто.тноизбирательном or-- раничении, в полезном сигнале S(t). Выходной сигнал Z(t) адаптивного фильтра 21 поступает на инвертирующий

.1570022

10

10

35

вход блока 10. На выходе блока 10 формируется сигнал V. (t),:

Vg(t) - Vt(t) - Z7(t) - S(t)+M,,(t) + + N(t) + n(t) - Z,(t) - Z2(t), (11)

в котором скомпенсированы ограниченная в блок 6 собственно ССП ) и нелинейные искажения N(t), возникшие при ее ограничении.

На выходе частотного детектора 1 по результатам приема элемента сигна- 15 ла S№(t) за тактовый инвервал времени формируется напряжение иуд, которое является функцией отклонения значения мгновенной частоты принятого элемента сигнала f к от частоты наст20 ройки частотного детектора 1 frt:

U

УА

F,(fK- Ј„).

(12)

Данное напряжение иудинтегрируется за время тактового интервала интегратора 2, выходное напряжение которого равно

ииЛ и,. (13)

о

где Т- постоянная времени интегратора 2. .

Напряжение UH (t) с выхода интегратора 2 поступает на вход АЦП 3, который преобразует данное напряжение U,. (t,) в код, соответствующий мгновенной частоте f K принятого текущего элемента сигнала SK(t), который и выдается на первый выход предлагаемого

35

40

устройства.

Блок 15 производит задержку входного воздействия V(t) на время t«, равное длительности обработки одного элемента сигнала SK(t) с момента пос- ,с тупления его на вход устройства до момента выдачи решения о частоте данного элемента сигнала SK(t) в виде кода с выхода АЦП 3.

В блоке 12 центральная частота 50 tfn n опорного сигнала SR(t) изменяется (переключается) под мгновенную частоту fk сигнала SK(t) лишь в моменты поступления элементов сигнала SK(t) с частотой fKeffon.ni.

Опорный сигнал S „(t) с частотой f с выхода блока112 поступает на

00 - Л

вход генератора 13, который преобразует данный сигнал Sn(t) во множество опорных сигналов S onn(t).

Каждый такой сигнал с отдельного выхода генератора 13 поступает на соответствующий сигнальный вход ключа 14. В ключе 14 под действием кода, содержащего информацию о мгновенной частоте Јк принятого элемента сигнала S«(t), производится коммутация к-го сигнального входа, соответствующего данной частоте, на выход ключа 14. Опорный сигнал s n (t), центральная частота которого равна мгновенной частоте принятого элемента сигнала S (t),

тора, выход которого соединен с вторым входом фазового детектора и через блок выделения несущей с входом генератора частот, первый адаптивный фильтр, первый блок вычитания, выход которого соединен с входом первого широкополосного усилителя, выход ре- жекторного фильтра соединен с вторым сигнальным входом первого коммутатора, выход которого соединен с входом частотного детектора, отличающееся тем, что, с целью повышения помехоустойчивости путем устранес выхода ключа 14 поступает на второй вход фазового детектора 17, на первый ния линейного и нелинейного влияний вход которого поступает задержанный интенсивной сосредоточенной по спектру помехи, введены блок селекции и ограничения, второй широкополосный

на время t, текущий элемент сигнала

Зй(1:). На выяод е фазового детектора

17 формируется напряжение , явля- усилитель, последовательно соединенющееся функцией разности фаз принято- 20 ные формирователь опорного сигнала,

го лов:

6K(t)

и опорного S nn (t) сигнавп п

второй адаптивный фильтр и второй блок вычитания, причгм вход блока селекции и ограничения является входом устройства, первый его управляющий выход соединен с управляющими входами режекторного и перестраиваемого фильтров, а второй управляющий выход - с управляющими входами первого и второго коммутаторов, сигнальный

V fc-Yon)

(14)

Напряжение U д с выхода фазового де детектора 17 интегрируется интегратором 18 и поступает на вход АЦП 19, который преобразует напряжение U с с выхода интегратора 18 в код, соответствующий фазе принятого элемента, сигнала S(t). Дальнейшая работа -1

ts.,i

предлагаемого устройства для приема сигналов с ФМ происходит аналогично описанному циклу приема одного элемента сигнала S.,(t). t

Формула изобретения

1. Устройство для приема сигналов с фазочастотной модуляцией, содержащее последовательно соединенные час- тотный детектор, первый интегратор и первый аналого-цифровой преобразователь, выход которого является первым выхрдом устройства и соединен с управляющим входом ключа, входы которого соединены с выходами генератора частот, а выход - с первым входом фазового детектора, выход которого через второй интегратор соединен с входом второго аналого-цифрового преобразователя, выход которого является вторым выходом устройства, входом которого являются соединенные первые сигнальные входы первого коммутатора и блока задержки, выход которого соединен с сигнальными входами перестраиваемого фильтра и второго коммутатора, выход которого соединен с вторым входом фазового детектора и через блок выделения несущей с входом генератора частот, первый адаптивный фильтр, первый блок вычитания, выход которого соединен с входом первого широкополосного усилителя, выход ре- жекторного фильтра соединен с вторым сигнальным входом первого коммутатора, выход которого соединен с входом частотного детектора, отличающееся тем, что, с целью повышения помехоустойчивости путем устранения линейного и нелинейного влияний интенсивной сосредоточенной по спектру помехи, введены блок селекции и ограничения, второй широкополосный

5

второй адаптивный фильтр и второй блок вычитания, причгм вход блока селекции и ограничения является входом устройства, первый его управляющий выход соединен с управляющими входами режекторного и перестраиваемого фильтров, а второй управляющий выход - с управляющими входами первого и второго коммутаторов, сигнальный

0 вход режекторного фильтра и неинвертирующий вход первого блока вычитания соединен с выходом блока селекции и ограничения, выход перестраиваемого фильтра соединен с входом первого адаптивного фильтра, управляющий вход и выход которого соответственно соединен с выходом первого широкополосного усилителя и инвертирующим входим первого блока вычитания, выход

п, блока задержки соединен с входом формирователя опорных сигналов, выход первого блока вычитания соединен с неинвертирующим входом второго блока вычитания, выход которого соединен с

S входом второго коммутатора и через второй широкополосный усилитель - с управляющим входом второго адаптивного фильтра.

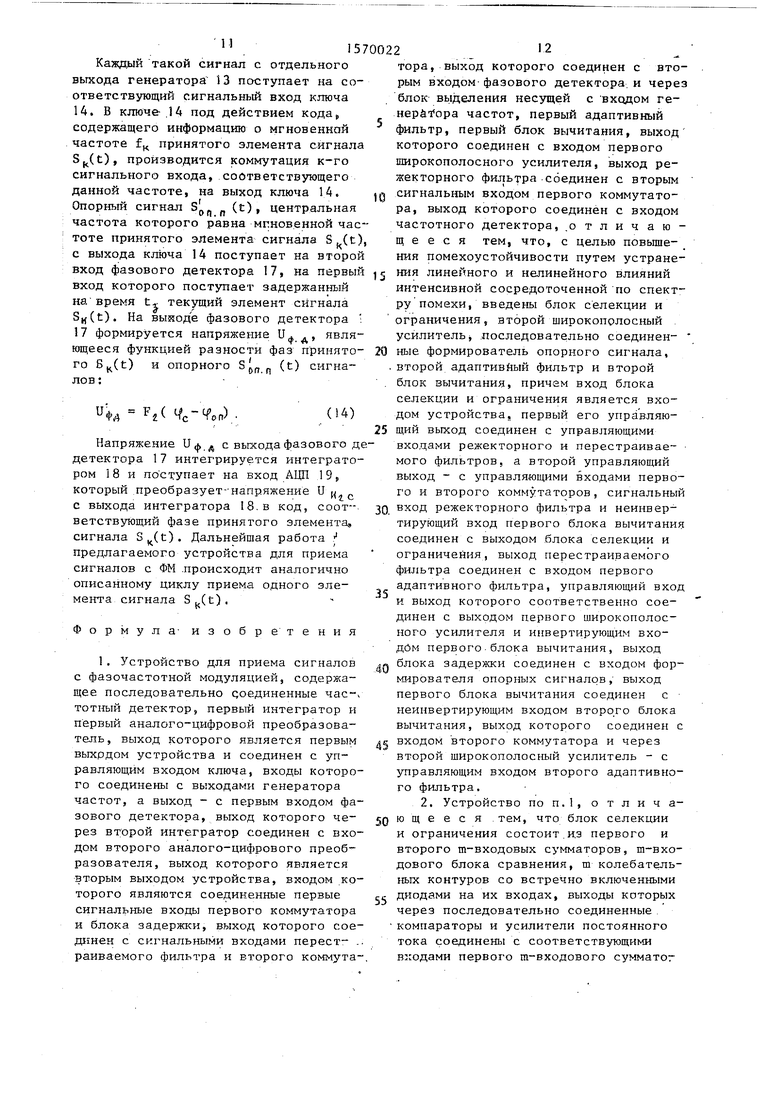

2. Устройство по п.1, о т л и ч а0 ю щ е е с я тем, что блок селекции и ограничения состоит из первого и второго m-входовых сумматоров, ш-вхо- дового блока сравнения, m колебательных контуров со встречно включенными

е диодами на их входах, выходы которых через последовательно соединенные компараторы и усилители постоянного тока соединены с соответствующими входами первого m-входового сумматог

pa, выход которого является первым управляющим выходом блока селекции и ограничения, выходы компараторов соединены с соответствующими входами m-входового блока сравнения, выход которого является вторым управляющим выходом блока селекции и ограничения, выходом и входом которого является соответственно выход второго т-вхо- дового сумматора и входы колебательных контуров, выходы которых соедине

ны с соответствующими входами второго m-входового сумматора.

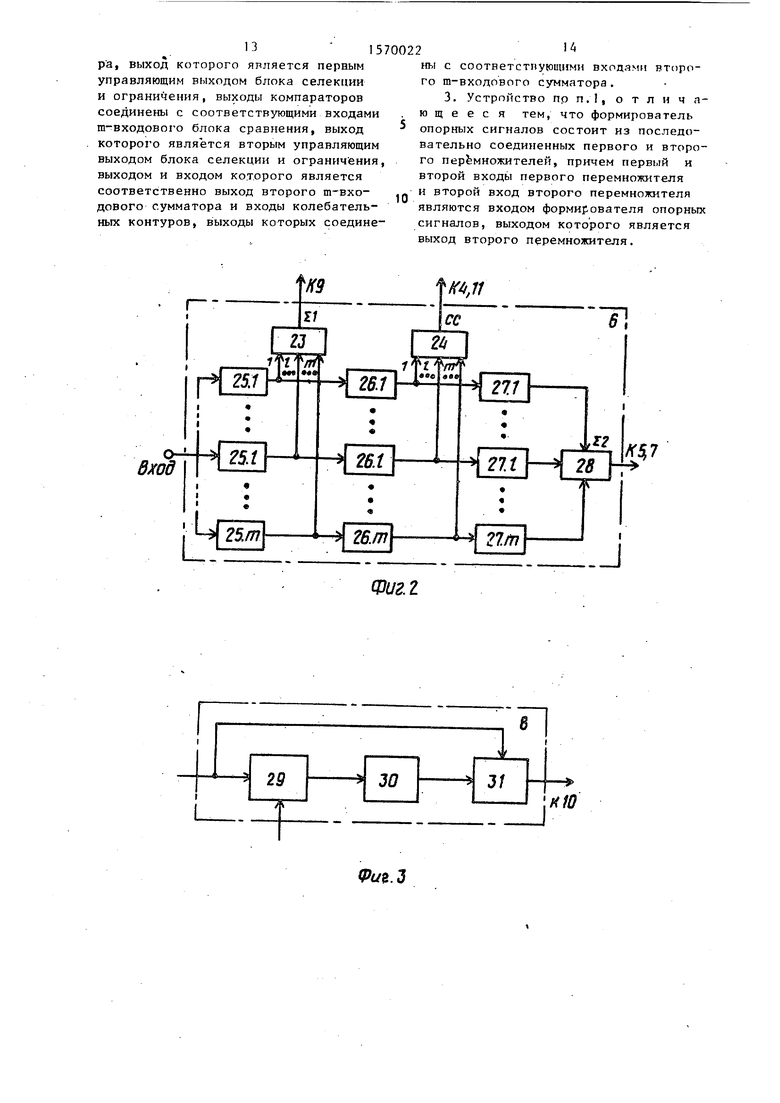

3. Устройство пр п.1, отличающееся тем, что формирователь опорных сигналов состоит из последовательно соединенных первого и второго перёмножителей, причем первый и второй входы первого перемножителя и второй вход второго перемножителя являются входом формирователя опорных сигналов, выходом которого является выход второго перемножителя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема сигналов с частотно-фазовой модуляцией | 1988 |

|

SU1518915A2 |

| Устройство для приема сигналов с частотно-фазовой модуляцией | 1987 |

|

SU1499523A2 |

| Устройство приема сигналов с частотным разделением каналов | 1988 |

|

SU1626410A1 |

| Устройство для приема сигналов с частотно-фазовой модуляцией | 1989 |

|

SU1600000A1 |

| АДАПТИВНЫЙ ЭКСПРЕСС-АНАЛИЗАТОР ПАРАМЕТРОВ ШИРОКОПОЛОСНЫХ ЧАСТОТНО-МОДУЛИРОВАННЫХ СИГНАЛОВ | 2006 |

|

RU2316774C1 |

| Адаптивная антенная решетка для систем связи с псевдослучайной перестройкой рабочей частоты | 1990 |

|

SU1786456A1 |

| КОРРЕЛЯЦИОННО-ФИЛЬТРОВОЕ УСТРОЙСТВО СЕЛЕКЦИИ ДВИЖУЩИХСЯ ЦЕЛЕЙ | 2003 |

|

RU2254594C1 |

| УСТРОЙСТВО ПОДАВЛЕНИЯ ПОМЕХ | 2002 |

|

RU2205507C1 |

| Линия связи | 1988 |

|

SU1628206A1 |

| КОРРЕЛЯЦИОННЫЙ ИЗМЕРИТЕЛЬ ФЛУКТУАЦИЙ | 2006 |

|

RU2339959C2 |

Изобретение относится к радиотехнике. Цель изобретения - повышение помехоустойчивости. Устройство содержит частотный детектор 1, интеграторы 2 и 18, АЦП 3 и 19, коммутаторы 4 и 11, режекторный фильтр 5, блок 6 селекции и ограничения, перестраиваемый фильтр 7, адаптивные фильтры 8 и 21, блоки 9 и 10 вычитания, блок 12 выделения несущей, г-р 13 частот, ключ 14, блок 15 задержки, широкополосные усилители 16 и 22, фазовый детектор 17 и формирователь 20 опорных сигналов. Цель достигается путем устранения линейного и нелинейного влияний интенсивной сосредоточенной по спектру помехи. Устройство по п.п. 2 и 3 ф-лы отличается выполнением блока 6 селекции и ограничения и формирователя 20. 2 з.п. ф-лы, 4 ил.

Фиг. г

Фиг.З

J

| Устройство для приема сигналов с частотно-фазовой модуляцией | 1987 |

|

SU1499523A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-06-07—Публикация

1988-09-14—Подача