ел

ОЭ

о

Јь

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

| Устройство для сопряжения электронных вычислительных машин | 1985 |

|

SU1285485A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1575193A2 |

| Устройство для сопряжения магистрали приборного интерфейса с магистралью микро-ЭВМ | 1986 |

|

SU1368885A1 |

| Устройство межмодульной связи для системы коммутации сообщений | 1986 |

|

SU1388883A1 |

| Устройство для сопряжения электронной вычислительной машины с общей шиной | 1983 |

|

SU1144112A1 |

| Устройство для подключения источников информации к общей магистрали | 1989 |

|

SU1679498A1 |

| Устройство для сопряжения ЭВМ в вычислительной системе с децентрализованным арбитром магистрали | 1984 |

|

SU1291997A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО СОПРЯЖЕНИЯ С ИНТЕРФЕЙСОМ ПОСЛЕДОВАТЕЛЬНОГО КОДА | 2000 |

|

RU2201617C2 |

| Устройство для сопряжения вычислительной машины с магистралью | 1981 |

|

SU980088A2 |

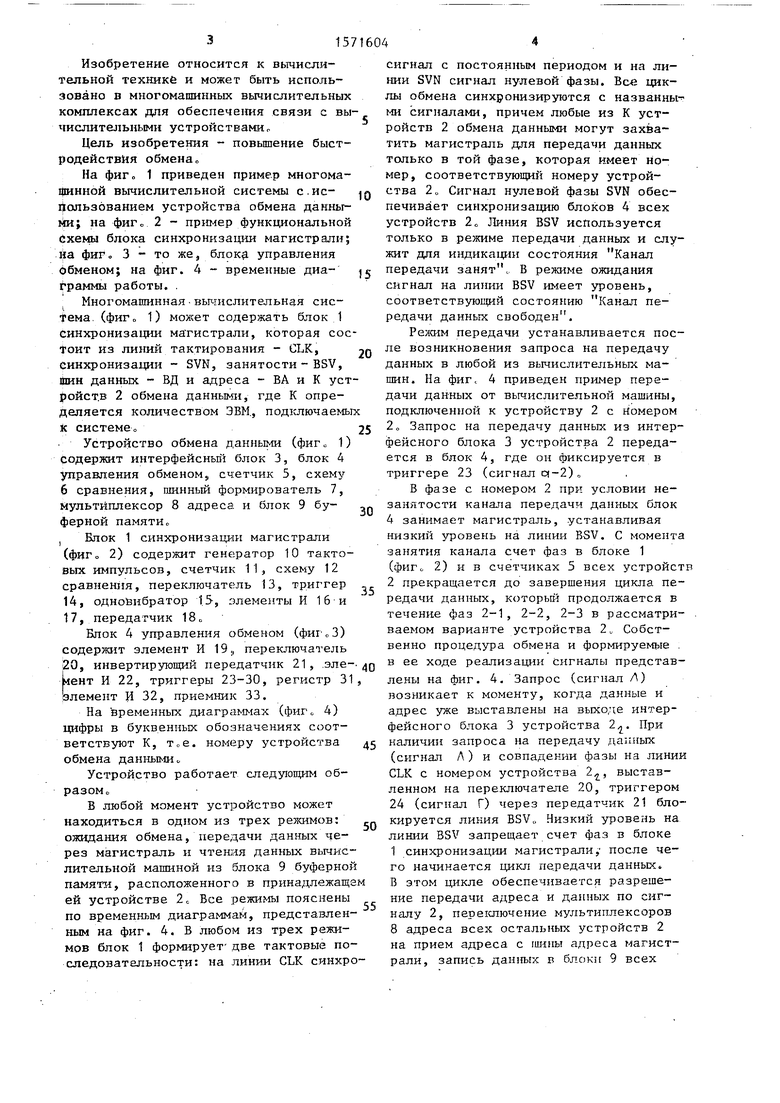

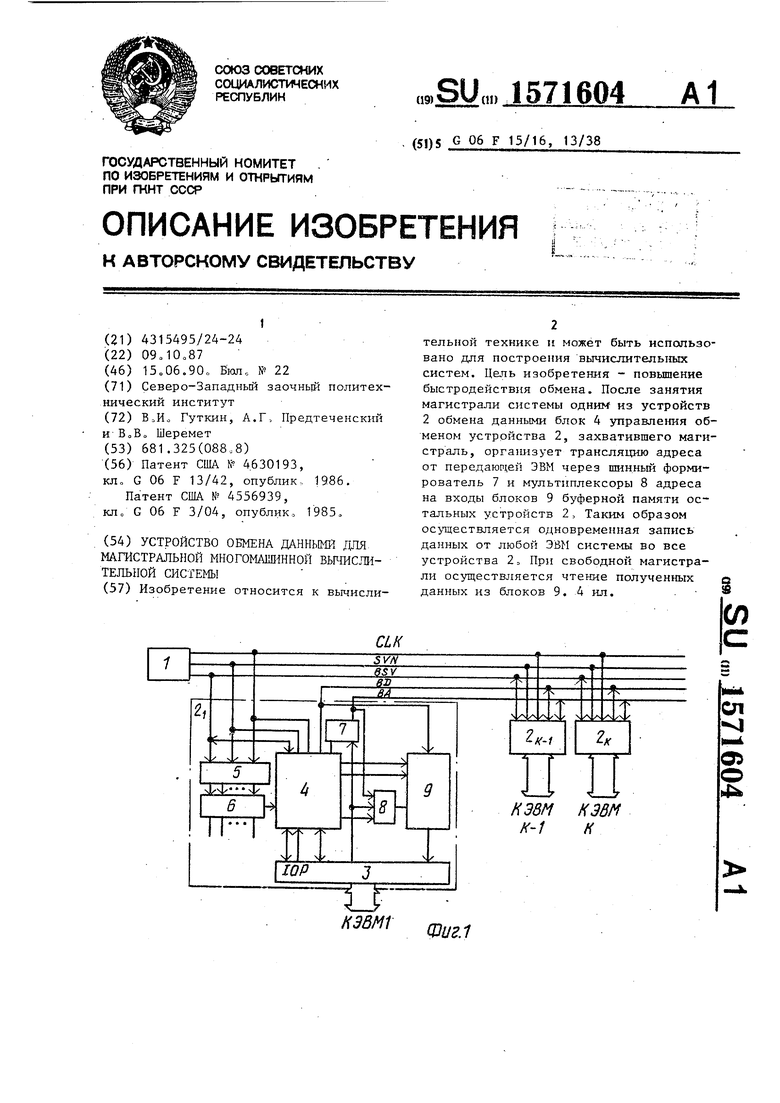

Изобретение относится к вычислительной технике и может быть использовано для построения вычислительных систем. Цель изобретения - повышение быстродействия обмена. После занятия магистрали системы одним из устройств 2 обмена данными блок 4 управления обменом устройства 2, захватившего магистраль, организует трансляцию адреса от передающей ЭВМ через шинный формирователь 7 и мультиплексоры 8 адреса на входы блоков 9 буферной памяти остальных устройств 2. Таким образом осуществляется одновременная запись данных от любой ЭВМ системы во все устройства 2. При свободной магистрали осуществляется чтение полученных данных из блоков 9. 4 ил.

К ЭВМ

Шиг.1

10

315716

Изобретение относится к вычислительной технике и может быть использовано в многомашинных вычислительных комплексах для обеспечения связи с вычислительными устройствамио

Цель изобретения - повышение быстродействия обменас

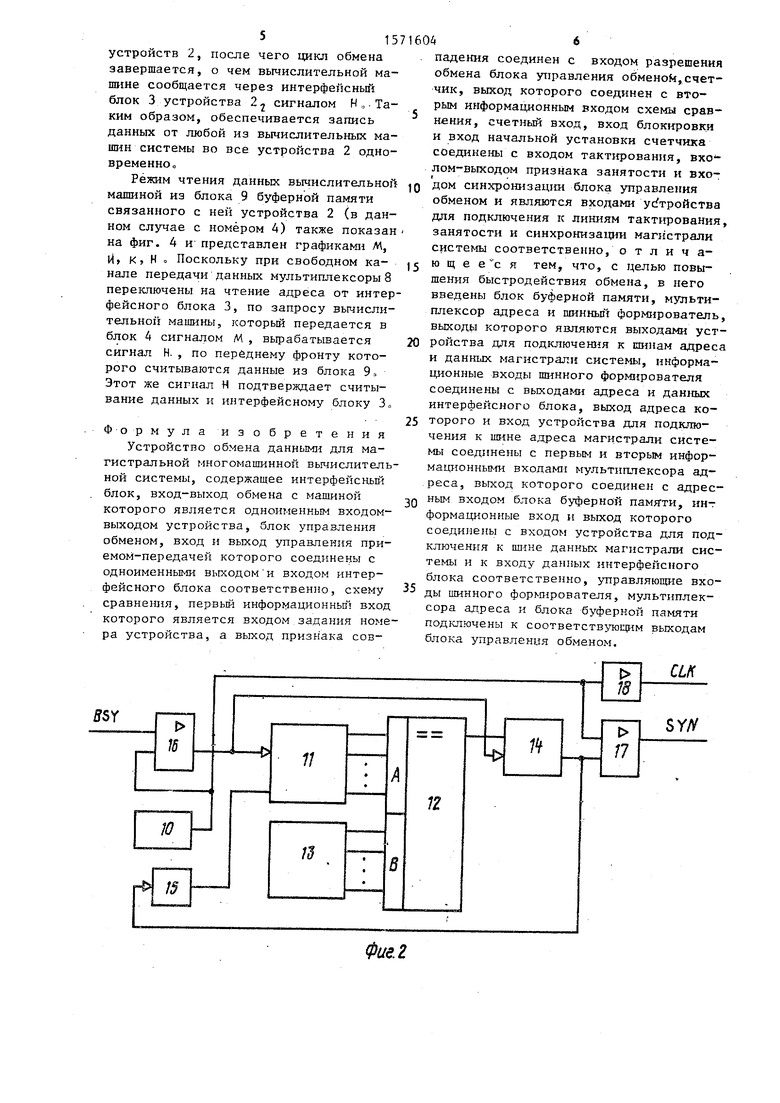

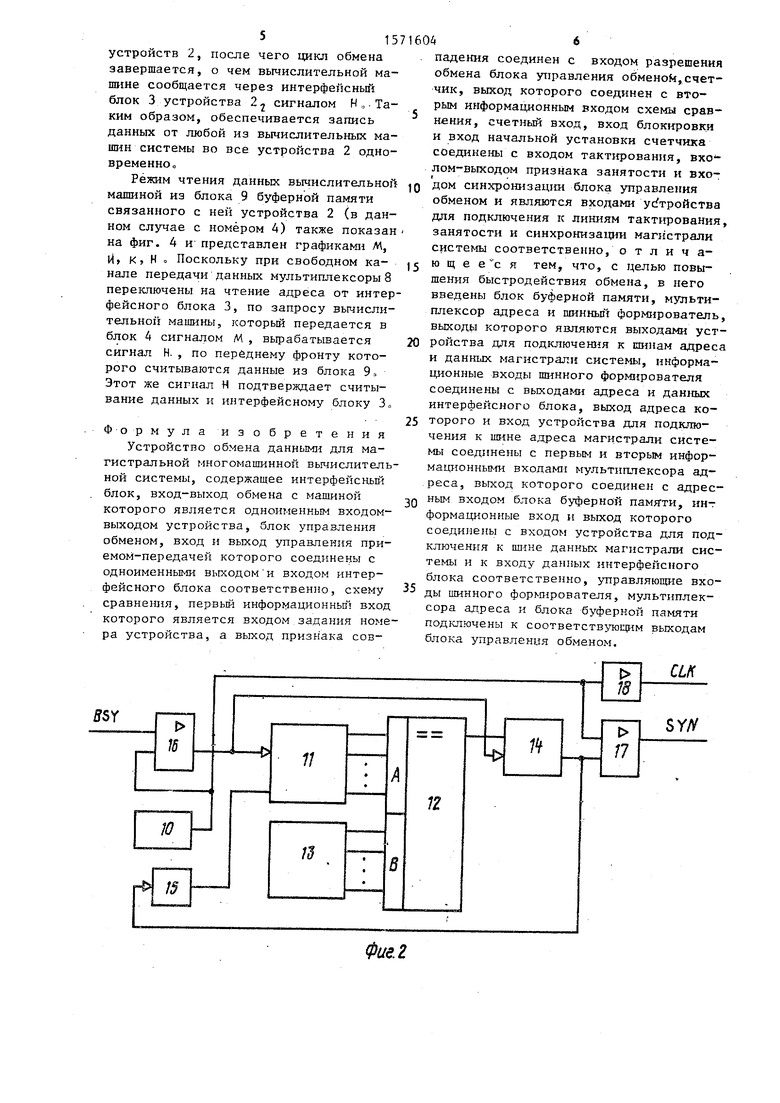

На фиг 1 приведен пример многомашинной вычислительной системы с использованием устройства обмена данными; на фиг о 2 - пример функциональной Схемы блока синхронизации магистрали; на фиг о 3 - то же, блокЈ управления Обменом; на фиг. 4 - временные диаграммы работы.

Многомашинная вычислительная система (фиг о 1) может содержать блок 1 Синхронизации магистрали, которая состоит из линий тактирования - CLK, 20 Синхронизации - SVN, занятости - BSV, (оин данных - ВД и адреса - ВА и К устройств 2 обмена данными, где К определяется количеством ЭВМ, подключаемых к системе 25

Устройство обмена данными (фиг. 1) содержит интерфейсный блок 3, блок 4

15

управления обменом, счетчик 5, схему 6 сравнения, шинный формирователь 7, мультиплексор 8 адреса и блок 9 буферной памятио

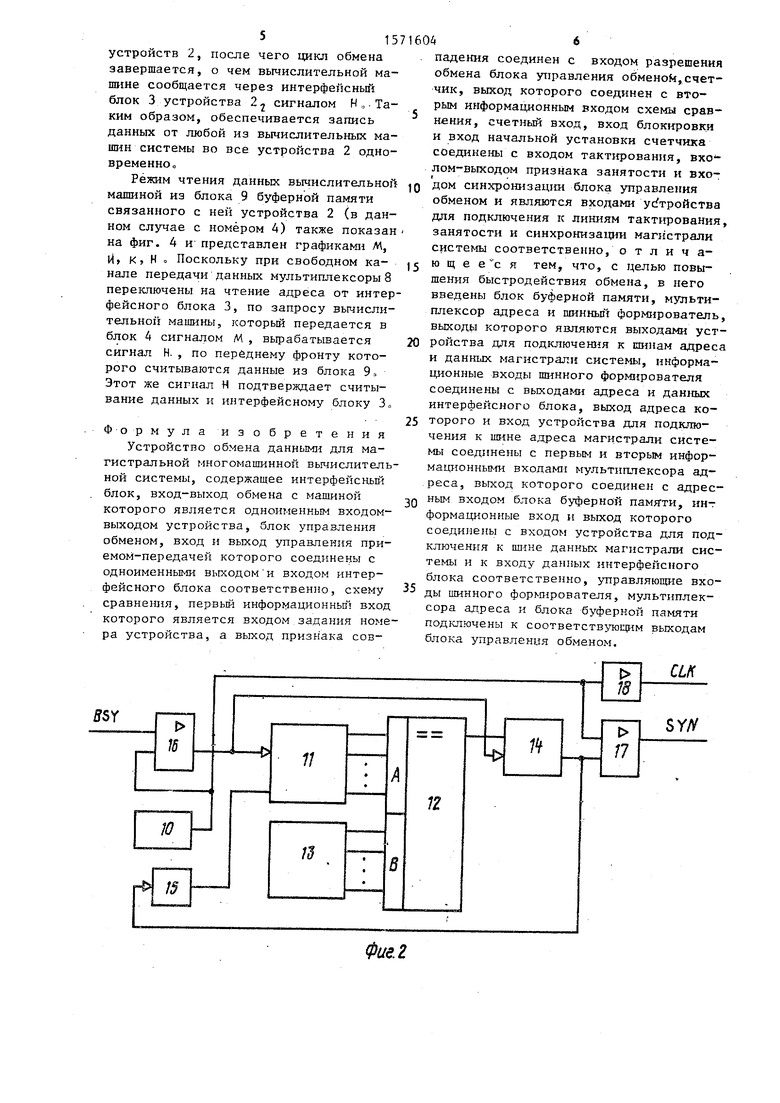

, Блок 1 синхронизации магистрали (фиго 2) содержит генератор 10 тактовых импульсов, счетчик 1lj схему 12 сравнения, переключатель 13, триггер 14, одновибратор 15, элементы И 16 и 17, передатчик 18„

Блок 4 управления обменом (фиг„3) содержит элемент И 19,, переключатель 20, инвертирующий передатчик 21, эле- Ьент И 22, триггеры 23-30, регистр 31 элемент И 32, приемник 33.

На временных диаграммах (фиг., 4) цифры в буквенных обозначениях соответствуют К, т„е. номеру устройства обмена данными„

Устройство работает следующим образом

В любой момент устройство может находиться в одном из трех режимов: ожидания обмена, передачи данных через магистраль и чтения данных вычислительной машиной из блока 9 буферной памяти, расположенного в принадлежаще

ей устройстве 2« Все режимы пояснены

5

по временным диаграммам, представленным на фиг. 4. В любом из трех режимов блок 1 формирует две тактовые последовательности: на линии CLK синхро0

0 5

5

0

5

о

5

0

5

сигнал с постоянным периодом и на линии SVN сигнал нулевой фазы. Все циклы обмена синхронизируются с названными сигналами, причем любые из К устройств 2 обмена данными могут захватить магистраль для передачи данных только в той фазе, которая имеет номер, соответствующий номеру устройства 2„ Сигнал нулевой фазы SVN обеспечивает синхронизацию блоков 4 всех устройств 2о Линия BSV используется только в режиме передачи данных и служит для индикации состояния Канал передачи занят, В режиме ожидания сигнал на линии BSV имеет уровень, соответствующий состоянию Канал передачи данных свободен.

Режим передачи устанавливается после возникновения запроса на передачу данных в любой из вычислительных машин. На фиг, 4 приведен пример передачи данных от вычислительной машины, подключенной к устройству 2 с номером 2 о Запрос на передачу данных из интерфейсного блока 3 устройства 2 передается в блок 4, где он фиксируется в триггере 23 (сигнал сц-2) „

В фазе с номером 2 при условии незанятости канала передачи данных блок 4 занимает магистраль, устанавливая низкий уровень на линии BSV. С момента занятия канала счет фаз в блоке 1 (фиго 2) и в счетчиках 5 всех устройств 2 прекращается до завершения цикла передачи данных, который продолжается в течение фаз 2-1, 2-2, 2-3 в рассматриваемом варианте устройства 2„ Собственно процедура обмена и формируемые в ее ходе реализации сигналы представлены на фиг. 4. Запрос (сигнал Л) возникает к моменту, когда данные и адрес уже выставлены на выходе интерфейсного блока 3 устройства 2. При наличии запроса на передачу данных (сигнал Л) и совпадении фазы на линии CLK с номером устройства 2t, выставленном на переключателе 20, триггером 24 (сигнал Г) через передатчик 21 блокируется линия BSV0 Низкий уровень на линии BSV запрещает счет фаз в блоке 1 синхронизации магистрали, после чего начинается цикл передачи данных. В этом цикле обеспечивается разрешение передачи адреса и данных по сигналу 2, переключение мультиплексоров 8 адреса всех остальных устройств 2 на прием адреса с шины адреса магистрали, запись данных в блоки 9 всех

55Г

CLK

Фиг. 2

| Патент США № 4630193, юл G 06 F 13/42, опублик 1986 | |||

| Патент США № 4556939, кл„ G 06 F 3/04, опублико 1985, |

Авторы

Даты

1990-06-15—Публикация

1987-10-09—Подача