:

00 00 00 00

z

Изобретение относится к вычислительной технике и может быть испоо1ь- зовано при построении низкоскоростных линий связи повышенной отказ о- устойчивости.

Целью изобретения является упро- П1ение устройства и повышение быстродействия за счет реализации режима прямого доступа к памяти о

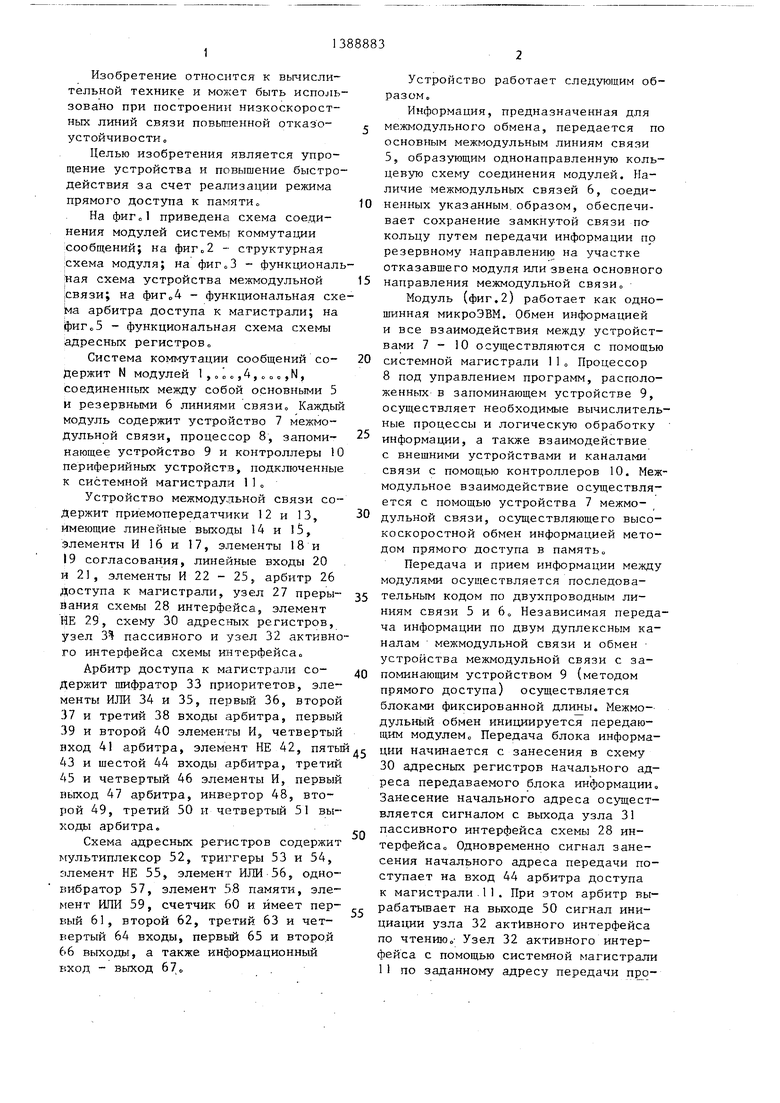

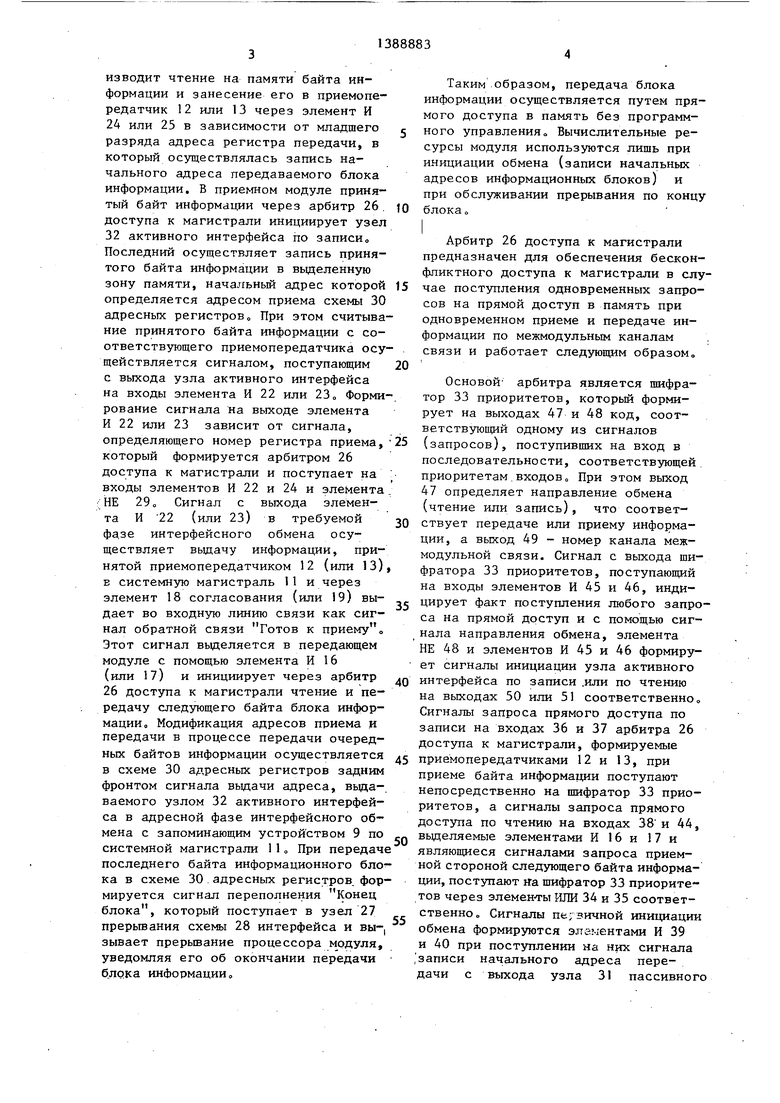

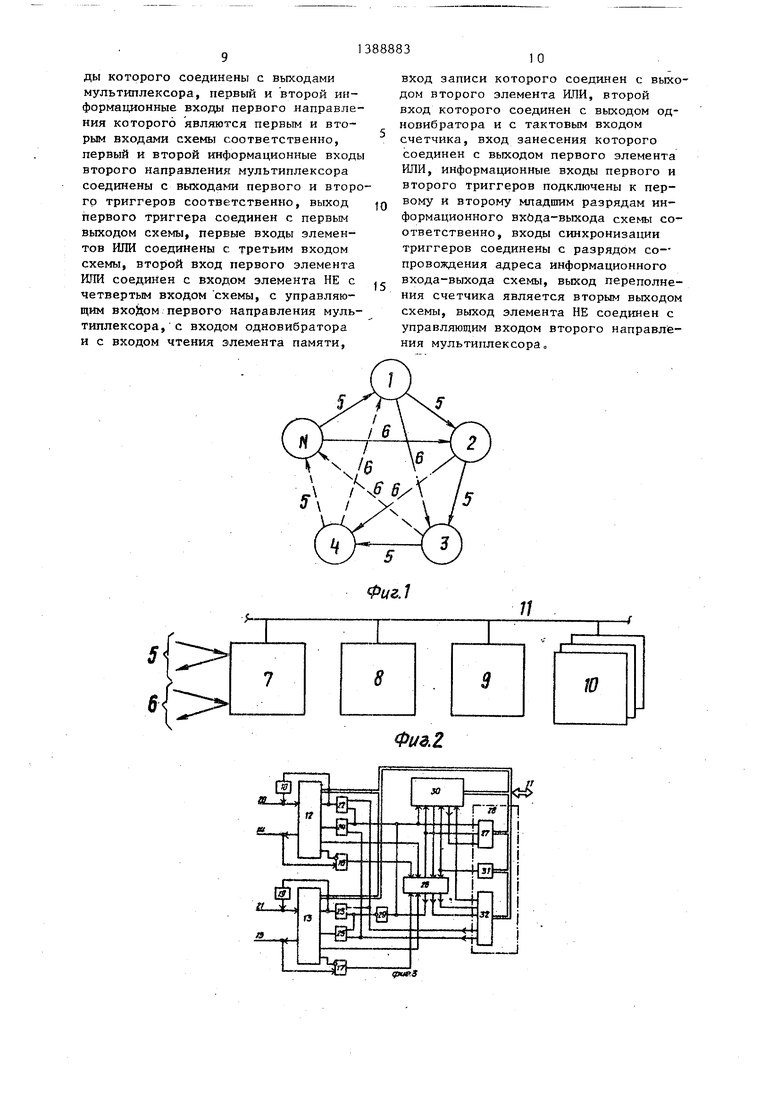

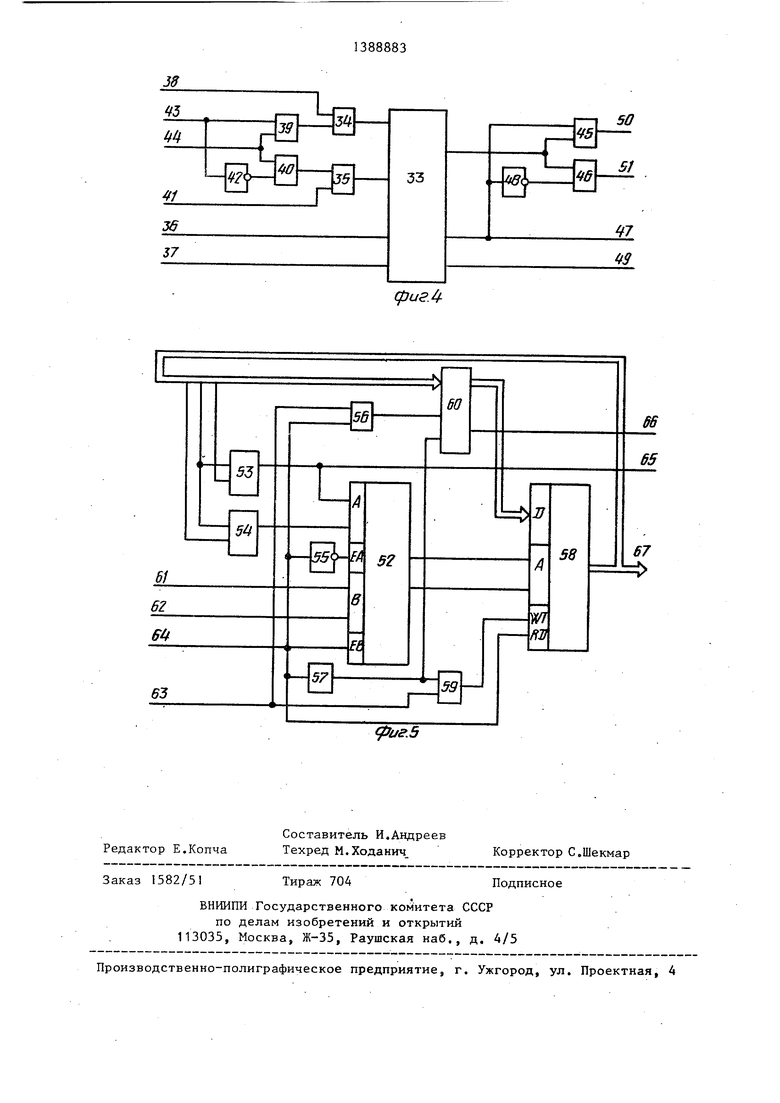

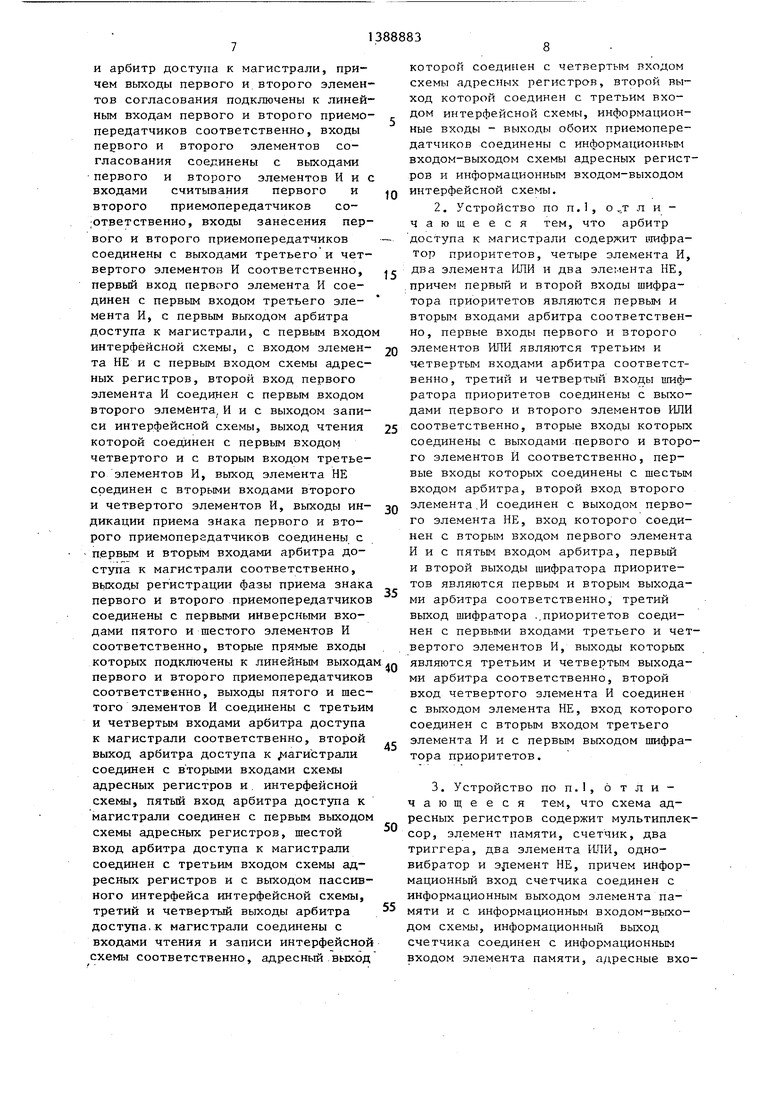

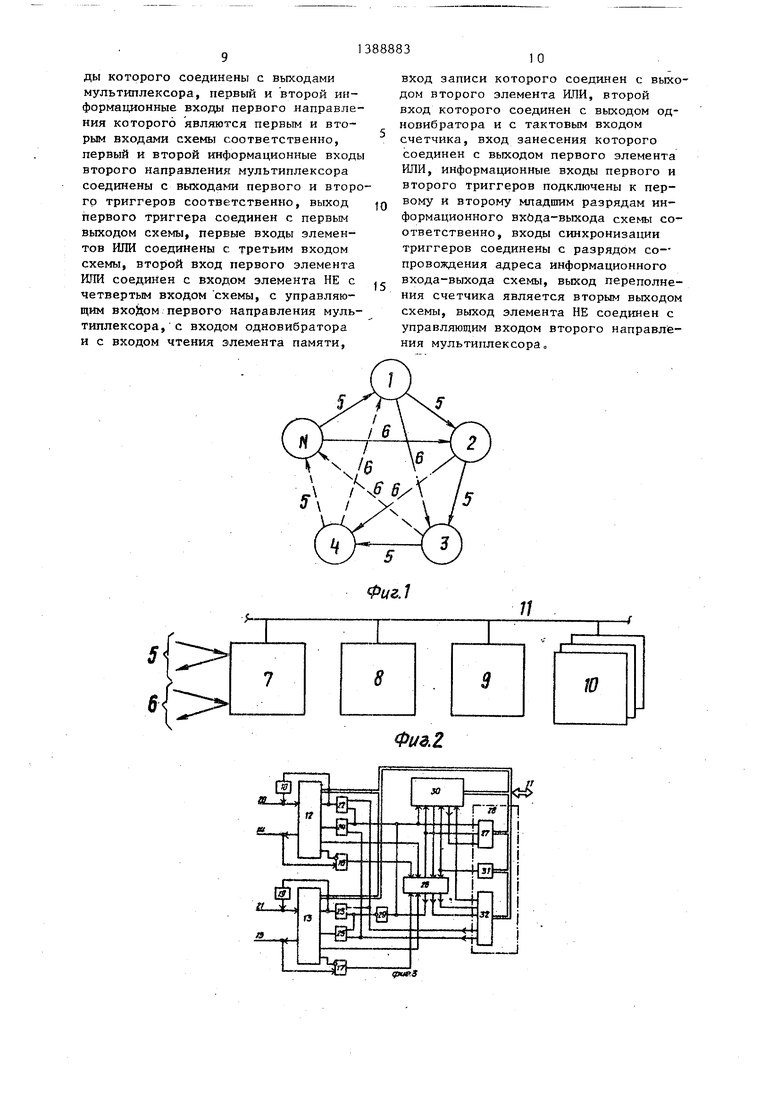

На фиГо1 приведена схема соединения модулей системь коммутации сообщений; на - структурная схема модуля; на фиг„3 - функциональная схема устройства межмодульной ;связи; на фиГо4 - функциональная схе йа арбитра доступа к магистрали; на фиг о 5 - функциональная схема схемы адресных регистров

Система коммутации сообщений со- Держит N модулей l,oo,,4,ooo,N, соединенных между собой основными 5 и резервными 6 линиями связи Каждый модуль содержит устройство 7 межмодульной связи, процессор 8, запоми- нающее устройство 9 и контроллеры 10 периферийных устройств, подключенные к системной магистрали 11

Устройство межмодульной связи содержит приемопередатчики 12 и 13, имеющие линейные выходы 14 и 5, элементы И 16 и 17, элементы 18 и 19 согласования, линейные входы 20 и 21, элементы И 22 - 25,, арбитр 26 доступа к магистрали, узел 27 преры- йания схемы 28 интерфейса, элемент НЕ 29, схему 30 адресзл1Х регистров, узел 3 пассивного и узел 32 активного интерфейса схемы интерфейса

Арбитр доступа к магистрали со- Держит шифратор 33 приоритетов, элементы ИЛИ 34 и 35, первый 36, второй 37 и третий 38 входы арбитра, первый 39 и второй 40 элементы И, четвертый нход 41 арбитра, элемент НЕ 42, пяты 43 и шестой 44 входы арбитра, третий 45 и четвертый 46 элементы И, первый ныход 47 арбитра, инвертор 48, второй 49, третий 50 и четвертый 51 выходы арбитра,,

Схема адресных регистров содержит мультиплексор 52, триггеры 53 и 54, :1лемент НЕ 55, элемент ИЛИ 56, одно- вибратор 57, элемент 5.8 памяти, элемент ИЛИ 59, счетчик 60 и имеет пер- вый 61, второй 62, третий 63 и чет- 1 ертый 64 входы, первьй 65 и второй 66 выходы, а также информационный вход - выход 67„

г

0

5

0 5

0 5

Q

0

Устройство работает следующим образом

Информация, предназначенная для мeж юдyльнoгo обмена, передается по основным межмодульным линиям связи 5, образующим однонаправленную кольцевую схему соединения модулей. Наличие межмодульных связей 6, соединенных указанным.образом, обеспечивает сохранение замкнутой связи по- кольцу путем передачи информации по резервному направлению на участке отказавшего модуля или звена основного направления межмодульной связи

Модуль (фиг.2) работает как одно- шинная микроэвм. Обмен информацией и все взаимодействия между устройствами 7-10 осуществляются с помощью системной магистрали 11 Процессор 8 под управлением программ, расположенных в запоминающем устройстве 9, осуществляет необходимые вычислительные процессы и логическую обработку информации, а также взаимодействие с внешними устройствами и каналами связи с помощью контроллеров 10. Межмодульное взаимодействие осуществляется с помощью устройства 7 межмодульной связи, осуществляющего высокоскоростной обмен информацией методом прямого доступа в память

Передача и прием информации между модулями осуществляется последовательным кодом по двухпроводным линиям связи 5 и 6 Независимая передача информации по двум дуплексным каналам межмодульной связи и обмен устройства межмодульной связи с запоминающим устройством 9 (методом прямого доступа) осуществляется блоками фиксированной дли21ы. Межмодульный обмен инициируется передающим модулем Передача блока информации начинается с занесения в схему 30 адресных регистров начального адреса передаваемого блока информации Занесение начального адреса осуществляется сигналом с выхода узла 31 пассивного интерфейса схемы 28 интерфейса Одновременно сигнал занесения начального адреса передачи поступает на вход 44 арбитра доступа к магистрали .11. При этом арбитр вырабатывает на вьжоде 50 сигнал инициации узла 32 активного интерфейса по чтению - Узел 32 активного интерфейса с помощью системной магистрали 11 по заданному адресу передачи производит чтение на памяти байта информации и занесение его в приемопередатчик 12 или 13 через элемент И 24 или 25 в зависимости от младшего разряда адреса регистра передачи, в который осуществлялась запись начального адреса передаваемого блока информации, В приемном модуле принятый байт информации через арбитр 26. доступа к магистрали инициирует узел 32 активного интерфейса по записи Последний осуществляет запись принятого байта информации в вьщеленную зону памяти, начальный адрес которой определяется адресом приема схемы 30 адресньгх регистров При этом считывание принятого байта информации с соответствующего приемопередатчика осу- щействляется сигналом, поступающим с выхода узла активного интерфейса на входы элемента И 22 или 23„ Формирование сигнала на выходе элемента И 22 или 23 зависит от сигнала, определяющего номер регистра приема, который формируется арбитром 26 доступа к магистрали и поступает на входы элементов И 22 и 24 и элемента : НЕ 29 о Сигнал с выхода элемента И 22 (или 23) в требуемой Фазе интерфейсного обмена осуществляет выдачу информации, принятой приемопередатчиком 12 (или 13) в системную магистраль 11 и через элемент 18 согласования (или 19) вы- дает во входную линию связи как сигнал обратной связи Готов к приему,, Этот сигнал вьщеляется в передающем модуле с помощью элемента И 16 (или 17) и инициирует через арбитр 26 доступа к магистрали чтение и передачу следующего байта блока информации. Модификация адресов приема и передачи в процессе передачи очередных байтов информации осуществляется в схеме 30 адресных регистров задним фронтом сигнала вьздачи адреса, вьщаваемого узлом 32 активного интерфейса в адресной фазе интерфейсного обмена с запоминающим устройством 9 по системной магистрали 11 При передач последнего байта информационного бло ка в схеме 30 . адресньгх регистров, формируется сигнал переполнения Конец блока, который поступает в узел 27 прерьгеания схемы 28 интерфейса и вызывает прерьшание процессора м одуля, уведомляя его об окончании передачи блока информациио

. 0 5 O Q

0

5

Таким образом, передача блока информации осуществляется путем прямого доступа в память без программного управленияо Вычислительные ресурсы модуля используются лишь при инициации обмена (записи начальных адресов информационных блоков) и при обслуживании прерывания по концу блока о

Арбитр 26 доступа к магистрали предназначен для обеспечения бесконфликтного доступа к магистрали в случае поступления одновременных запросов на прямой доступ в память при одновременном приеме и передаче информации по межмодульным каналам связи и работает следующим образомо

Основой арбитра является шифратор 33 приоритетов, который формирует на выходах 47 и 48 код, соответствующий одному из сигналов (запросов), поступивших на вход в последовательности, соответствующей приоритетам.входов о При этом выход 47 определяет направление обмена (чтение или запись), что соответствует передаче или приему информации, а выход 49 - номер канала межмодульной связи. Сигнал с выхода щи- фратора 33 приоритетов, поступаюш 1й на входы элементов И 45 и 46, индицирует факт поступления любого запроса на прямой доступ и с помощью сигнала направления обмена, элемента НЕ 48 и элементов И 45 и 46 формирует сигналы инициации узла активного интерфейса по записи .или по чтению на выходах 50 или 51 соответственно о Сигналы запроса прямого доступа по записи на входах 36 и 37 арбитра 26 доступа к магистрали, формируемые приемопередатчиками 12 и 13, при приеме байта информации поступают непосредственно на шифратор 33 приоритетов, а сигналы запроса прямого доступа по чтению на входах 38 и 44, выделяемые элементами И 16 и 17 и являющиеся сигналами запроса приемной стороной следующего байта информации, поступают яа шифратор 33 приоритетов через элемен-ты ИШ 34 и 35 соответственно Сигналы пегзнчной инициации обмена формируются элементами И 39 и 40 при поступлении на них сигнала , записи начального адреса передачи с выхода узла 31 пассивного

интерфейсао При этом формирование сигнала запроса прямого доступа по чтению для соответствующего направления передачи - основного (элемент И 39) или резервного (элемент 40} определяется состоянием сигнала на входе A3 арбитра 26,, зависящего от адреса регистра адреса передачи, в .который осуществлялась запись началь ного адреса передаваемого блока информации

Схема адресных рсггистров предназначена для хранения и модификации текущих адресов передаваемой и при- нимаемой информации по основному; и резервному направлениям и работает следующим образом.,

Для хранения адресов по приему и передаче для двух направле- НИИ требуются четыре регистра, которые организуются в-элементе 58 памятио Занесение начального и текущего адресов в элемент 58 памяти осуществляется из системной магистра ли 11 через счетчик 60,Выбор одного из четырех регистров текущего адреса определяется сигналами на адресных входах элемента 58 памяти, по ступающими с вьгхода мультиплексора 52 о В исходном состоянии мультиплексор 52 обеспечивает прохождение на свои вькоды значения адреса с входов второго (верхнего по схеме на фиг„5) направления,.соединенных с выходами триггеров 53 и 54,, в которые, в свою очередь, значение адресных разрядов, определяющих номер регистра адреса в элементе 5В памяти, заносится из системной магистрсши 11 сигналом сопровождения адреса, поступающим на синхровходы триггеров 53 и 54 , Занесение информации (начального адреса приема или передачи блока информации) в элемент 58 памяти по адресу, определенному состоянием триггеров 53 и 54., осуществляется сигналом записи, поступаюащм с вых:о- да узла 31 пассивного интерфейса через элемент ИЛИ 59 на вход записи элемента 58 памяти Одновременно тот же сигнал записи через элемент ИЛИ 56 разрещает занесение записываемой в элемент 58 памяти информации в счетчик 60, обеспечивая тем самым ее прохождение на информационные входы элемента 58 памяти В релси- ме прямого доступа (в процессе передачи блока информации; мультиплек

сор 52 осуществляет коммутацию адреса требуемого регистра с первого (нижнего по схеме на фиг о 5) направления, куда он, в свою очередь, поступает с выхода арбитра 26 доступа к магистрали. Коммутация адреса на выход мультиплексора 52 с второго направления осуществляется сигналом выдачи адреса на. входе 64 схемы 30 адресных регистров, поступающим с выхода узла 3.2 активного интерфейс а, который также с помощью элемента НЕ 55 осуществляет блокировку первого направления мультиплексора 52, обесг печивает с помощью элемента ИЛИ 59 выдачу текущего значения адреса требуемого регистра в магистраль и с помощью элемента ИЛИ 56 прохождение выданного значения адреса на вход элемента 58 памяти через счетчик 60 Задним фронтом сигнала выдачи адреса запускается одновибратор 57, сигнал с выхода которого осуществляет модификацию (увеличение на единицу) адреса, записанного в счетчике 60, и запись с помощью элемента ИЛИ 59 нового значения адреса в элемент 58 памяти

Приемопередатчики 12 и 13, используемые в устройстве межмодульного обмена, представляют, собой параллельно- последовательные преобразователи, предназначенные для побайтовой последовательной передачи информации со стартстопной синхронизациейо

Формула

изобретения

1«Устройство межмодульной связи для системы коммутации сообщений, содержащее два приемопередатчика и интерфейсную схему, причем линейные входы первого и второго приемопередатчиков являются первым и,вторым входами линии связи узла соответственно, линейные выходы первого и второго приемопередатчиков являются первым и вторым выходами линии связи узла соответственно, информационный вход-выход интерфейсной схемы является информационным входом-выходом узла, отличающееся тем, что, с целью .упрощения устройства и повьщ1ения быстродействия за счет реа ЛИЗации режима йряМого доступа к памяти, в него введены щесть элементов И, два элемента согласования, элемент НЕ, схема адресных регистров

и арбитр доступа к магистрали, причем выходы первого и второго элементов согласования подключены к линейным входам первого и второго приемопередатчиков соответственно, входы первого и второго элементов согласования соединены с выходами первого и второго элементов И и с входами считывания первого и второго приемопередатчиков со- ;ответственно, входы занесения первого и второго приемопередатчиков соединены с выходами третьего и четвертого элементов И соответственно, первый вход первого элемента И соединен с первым входом третьего элемента И, с первым выходом арбитра доступа к магистрали, с первым входо интерфейсной схемы, с входом элемента НЕ и с первым входом схемы адресных регистров, второй вход первого элемента И соединен с первым входом второго элемента, И и с выходом записи интерфейсной схемы, выход чтения которой соединен с первым входом четвертого и с вторым входом третьего элементов И, выход элемента НЕ соединен с вторыми входами второго и четвертого элементов И, выходы индикации приема знака первого и второго приемопередатчиков соединены с первым и вторым входами арбитра доступа к магистрали соответственно, вьгходы регистрации фазы приема знака первого и второго приемопередатчиков соединены с первыми инверсными входами пятого и шестого элементов И соответственно, вторые прямые входы которых подключены к линейным выхода первого и второго приемопередатчиков соответственно, вьгходы пятого и шестого элементов И соединены с третьим и четвертым входами арбитра доступа к магистрали соответственно, второй выход арбитра доступа к 1агистрали соединен с в торыми входами схемы адресных регистров и. интерфейсной схемы, пятый вход арбитра доступа к

магистрали соединен с первым выходом схемы адресных регистров, шестой вход арбитра доступа к магистрали соединен с третьим входом схемы адресных регистров и с выходом пассивного интерфейса интерфейсной схемы, третий и четвертый выходы арбитра доступа,к магистрали соединены с входами чтения и записи интерфейсной схемы соответственно, адресный выход

0

5

0

Q

5

0

5

5

0

5

которой соединен с четвертым входом схемы адресных регистров, второй выход которой соединен с третьим входом интерфейсной схемы, информационные входы - выходы обоих приемопередатчиков соединены с информационным входом-выходом схемы адресных регистров и информационным входом-выходом интерфейсной схемы,

2,Устройство по п., л и - чающееся тем, что арбитр доступа к магистрали содержит 1чифра- тор приоритетов, четыре элемента И, два элемента liHH и два элемента НЕ, причем первый и второй входы шифратора приоритетов являются первым и вторым входами арбитра соответственно, первые входы первого и второго элементов ИЛИ являются третьим и четвертым входами арбитра соответственно, третий и четвертый входы шифратора приоритетов соединены с выходами первого и второго элементов ИЛИ соответственно, вторые входы которых соединены с выходами первого и второго элементов И соответственно, первые входы которых соединены с шестым входом арбитра, второй вход второго элемента.И соединен с выходом первого элемента НЕ, вход которого соединен с вторым входом первого элемента И и с пятым входом арбитра, первый

и второй выходы шифратора приоритетов являются первым и вторым выходами арбитра соответственно, третий выход шифратора ..приоритетов соединен с первыми входами третьего и четвертого элементов И, выходы которых являются третьим и четвертым выходами арбитра соответственно, второй вход четвертого элемента И соединен с выходом элемента НЕ, вход которого соединен с вторым входом третьего элемента И и с первым вьгходом шифратора приоритетов.

3.Устройство по п., отличающееся тем, что схема адресных регистров содержит мультиплексор, элемент памяти, счетчик, два триггера, два элемента Ш1И, одно- вибратор и э темент НЕ, причем информационный вход счетчика соединен с информационным выходом элемента памяти и с информационным входом-выходом схемы, информационный выход счетчика соединен с информационным входом элемента памяти, адресные входы которого соединены с выходами мультиплексора, первый и второй информационные входы первого направления которого являются первым и вторым входами схемы соответственно, первый и второй информационные входы второго направления мультиплексора соединены с выходами первого и второго триггеров соответственно, выход первого триггера соединен с первым выходом схемы, первые входы элементов ИЛИ соединены с третьим входом схемы, второй вход первого элемента ИЛИ соединен с входом элемента НЕ с четвертым входом схемы, с управляющим BXoftoM первого направления мультиплексора, с входом одновибратора и с входом чтения элемента памяти.

5

вход записи которого соединен с выходом второго элемента ИЛИ, второй вход которого соединен с выходом одновибратора и с тактовым входом счетчика, вход занесения которого соединен с выходом первого элемента ИЛИ, информационные входы первого и второго триггеров подключены к первому и второму младшим разрядам информационного входа-выхода схемы соответственно, входы синхронизации триггеров соединены с разрядом со- провождения адреса информационного входа-выхода схемы, выход переполнения счетчика является вторым выходом схемы, выход элемента НЕ соединен с управляющим входом второго направления мультиплексора о

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения системной и локальной магистралей. | 1988 |

|

SU1672460A1 |

| Мультиплексное устройство для обмена информацией | 1983 |

|

SU1157546A1 |

| Адаптер магистрального последовательного интерфейса мультиплексного канала информационного обмена | 2016 |

|

RU2639959C2 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

| Система сбора и обработки информации | 1987 |

|

SU1424024A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении низкоскоростных отказоустойчивых линий связи. Целью изобретения является упрощение устройства и увеличение быстродействия за счет реализации режима прямого доступа к памяти. Реализация прямого доступа к памяти достигается путем изменения схемы устройства -межмодульной связи и позволяет экономить вычислительные ресурсы процессора управления модулем. Устройство рассчитано на использование внутримашинной магистрали по ОСТ 11,305-903-80. 2 з,п,ф-лы, 5 ил.

Фиг.

П

Фиг2

фие.З

Редактор Е.Копча

Составитель И.Андреев Техред М.Ходанич.

Заказ 1582/51

Тираж 704

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д, 4/5

сригЛ

.Э

Корректор С.Шекмар

Подписное

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Насадок к приемнику воздушного давления датчика скорости самолета | 1956 |

|

SU110569A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-15—Публикация

1986-07-04—Подача