Изобретение относится к вычислительной технике и может быть использовано в многомашинных и многопроцессорных вычислительных системах.

Целью изобретения является увеличение быстродействия.

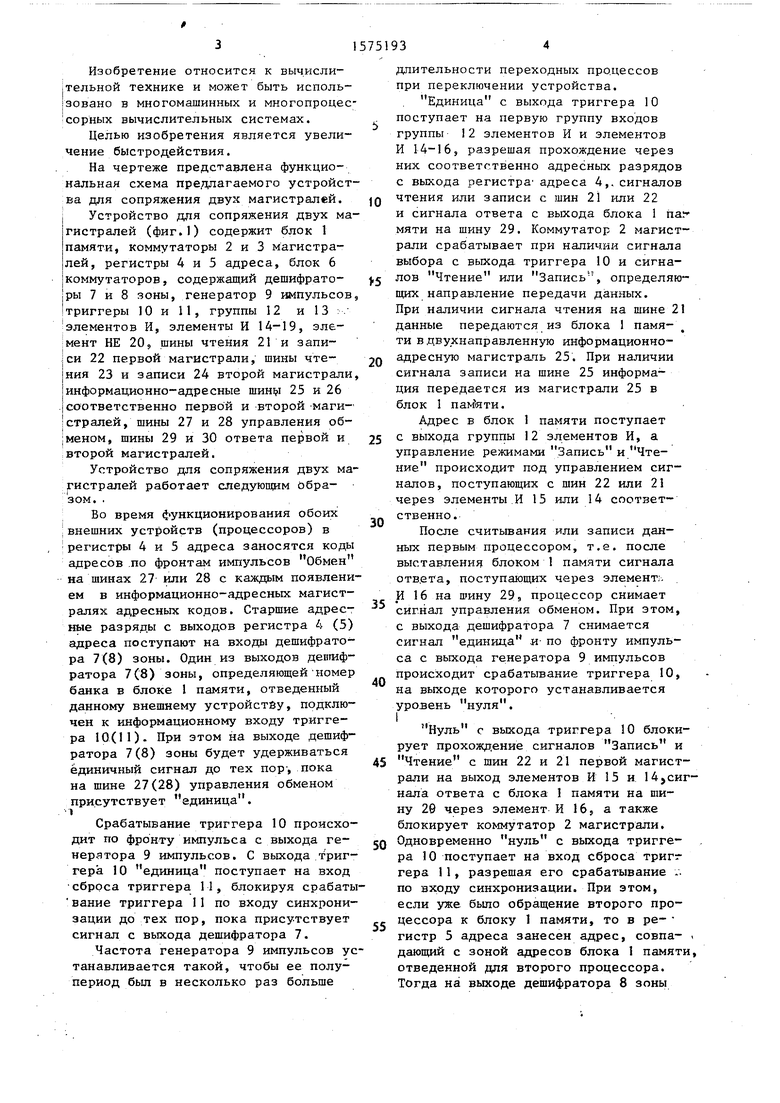

На чертеже представлена функциональная схема предлагаемого устройства для сопряжения двух магистралей.

Устройство для сопряжения двух магистралей (фиг.1) содержит блок 1 памяти, коммутаторы 2 и 3 магистралей, регистры 4 и 5 адреса, блок 6 коммутаторов, содержащий дешифраторы 7 и 8 зоны, генератор 9 импульсов триггеры 10 и 11, группы 12 и 13 элементов И, элементы И 14-19, элемент НЕ 209 шины чтения 21 и запищи 22 первой магистрали, шины чте- JHHH 23 и записи 24 второй магистрали информационно-адресные шины 25 и 26 соответственно первой и второй маги- стралей, шины 27 и 28 управления обменом, шины 29 и 30 ответа первой и второй магистралей.

Устройство для сопряжения двух магистралей работает следующим образом. .

Во время Функционирования обоих внешних устройств (процессоров) в регистры 4 и 5 адреса заносятся коды адресов по фронтам импульсов Обмен на шинах 27 или 28 с каждым появлением в информационно-адресных магистралях адресных коцов. Старшие адресные разряды с выходов регистра 4 (5) адреса поступают на входы дешифратора 7(8) зоны. Один из выходов дешифратора 7(8) зоны, определяющей номер банка в блоке 1 памяти, отведенный данному внешнему устройству, подключен к информационному входу триггера 10(11). При этом на выходе дешифратора 7(8) зоны будет удерживаться единичный сигнал до тех пор, пока на шине 27(28) управления обменом присутствует

единица

Срабатывание триггера 10 происходит по фронту импульса с выхода генератора 9 импульсов. С выхода триггера 10 единица поступает на вход сброса триггера 11, блокируя срабаты- вание триггера 11 по входу синхронизации до тех пор, пока присутствует сигнал с выхода дешифратора 7.

Частота генератора 9 импульсов устанавливается такой, чтобы ее полу- период был в несколько раз больше

5

0

5

0

5

0

5

0

5

длительности переходных процессов при переключении устройства.

Единица с выхода триггера 10 поступает на первую группу входов группы 12 элементов И и элементов И 14-16, разрешая прохождение через них соответственно адресных разрядов с выхода регистра адреса 4,, сигналов чтения или записи с шин 21 или 22 и сигнала ответа с выхода блока 1 паг мяти на шину 29. Коммутатор 2 магистрали срабатывает при наличии сигнала выбора с выхода триггера 10 и сигналов Чтение или Запись , определяющих направление передачи данных. При наличии сигнала чтения на шине 21 данные передаются из блока 1 памяти вдвухнаправленную информационно- адресную магистраль 25. При наличии сигнала записи на шине 25 информация передается из магистрали 25 в блок 1 памяти.

Адрес в блок 1 памяти поступает с выхода группы 12 элементов И, а управление режимами Запись и Чтение происходит под управлением сигналов, поступающих с шин 22 или 21 через элементы И 15 или 14 соответственно.

После считывания или записи данных первым процессором, т.е. после выставления блоком 1 памяти сигнала ответа, поступающих через элемент И 16 на шину 29 s процессор снимает сигнал управления обменом. При этом, с выхода дешифратора 7 снимается сигнал единица и по фронту импульса с выхода генератора 9 импульсов происходит срабатывание триггера 10, на выходе которого устанавливается

уровень нуля. I

Нуль г выхода триггера 10 блокирует прохождение сигналов Запись и Чтение с шин 22 и 21 первой магистрали на выход элементов И 15 и 14jCHr- нала ответа с блока 1 памяти на шину 29 через элемент И 16, а также блокирует коммутатор 2 магистрали. Одновременно нуль с выхода триггера 10 поступает на вход сброса тригг гера 11, разрешая его срабатывание . по входу синхронизации. При этом, если уже было обращение второго процессора к блоку 1 памяти, то в ре- гистр 5 адреса занесен адрес, совпа- дающий с зоной адресов блока 1 памяти, отведенной для второго процессора. Тогда на выходе дешифратора 8 зоны

5

находится уровень единицы. По

фронту импульса с выхода элемента

НЕ 20 срабатывает триггер 11 и на

вход оброса триггера 10 поступает

сигнал блокирующего сброса, запрещая

срабатывание триггера 10 по синхровходу.

Далее работа устройства происходит аналогично, как и при работе с первым процессором. При этом единица с выхода триггера 11 поступает на первую группу входов элементов И 13,17,18 и 19, разрешая прохождение через них соответственно адрес- ных разрядов с регистра 5 адреса на адресные входы блока 1 памяти, сигналов Чтение с шины 23 или Запись с шины 24 на входы блока 1 памяти и сигнала ответа с выхода бло ка 1 памяти на шину 30. Коммутатор 3 магистрали производит передачу данных из блока 1 памяти на шину 26 при наличии сигнала Чтение или в блок 1 памяти при наличии сигнала Запись.

Если в это время происходит запрос обращения к блоку 1 ,памяти от

,

1575193

первого процессора, то срабатывание триггера 10 не произойдет до тех пор, пока не будет снят сигнал управ- .. ления обменом с шины 28.

, После появления сигнала ответа от блока 1 памяти на шине 30 и снятия сигнала управления обменом с шины 28 возможно новое обращение к блоку 1 памяти.

Одновременное срабатывание триггера 10 и 11 исключено, так как на их синхровходах сигналы от генератора 9 инверсии, т.е. приоритет при одновременном обращении обоих внешних устройств случаен.

Формула изобретения

Устройство -для сопряжения двух магистралей по авт.св. № 1283781, отличающееся тем, что, с целью увеличения быстродействия, входы управления обменом первой и второй магистралей соединены соответственно с входами стробирования первого и второго дешифраторов зоны.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения магистралей | 1990 |

|

SU1737460A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1550523A1 |

| Устройство для сопряжения двух магистралей | 1985 |

|

SU1283781A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1619285A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1522224A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1524061A1 |

| Устройство сопряжения двух магистралей | 1988 |

|

SU1675894A1 |

| Устройство для обмена информацией | 1979 |

|

SU842773A1 |

| Устройство для сопряжения двух магистралей | 1990 |

|

SU1778760A1 |

| Специализированный процессор | 1990 |

|

SU1705834A1 |

Изобретение относится к вычислительной технике и может быть использовано в многомашинных и многопроцессорных вычислительных системах. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что устройство для сопряжения двух магистралей содержит блок 1 памяти, первой и второй коммутаторы 2 и 3 магистралей, первый и второй регистры 4, 5 адреса, блок 6 коммутаторов, содержащий первый и второй дешифраторы 7, 8 зоны, генератор 9 импульсов, первый и второй триггеры 10 и 11, первую и вторую группы 12 и 13 элементов И, с первого по шестой 14-19 элементы И и элемент НЕ 20, шины чтения 21, и записи 22 первой магистрали, шины чтения 23 и записи 24 второй магистрали, информационно-адресные шины 25, 26 первой и второй магистралей, шины 27, 28 управления обменом, шины 29, 30 ответа первой и второй магистралей. 1 ил.

| Устройство для сопряжения двух магистралей | 1985 |

|

SU1283781A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

Авторы

Даты

1990-06-30—Публикация

1988-05-06—Подача