Изобретение относится к вычислительной технике и может быть использовано при построении многопроцессорных и многомашинных вычислительных систем.

Цель изобретения - упрощение устройства, за счет обмена через один приемный и передающий блок буферной памяти со всеми ЭВМ, подключаемыми к общей межмашинной магистрали.

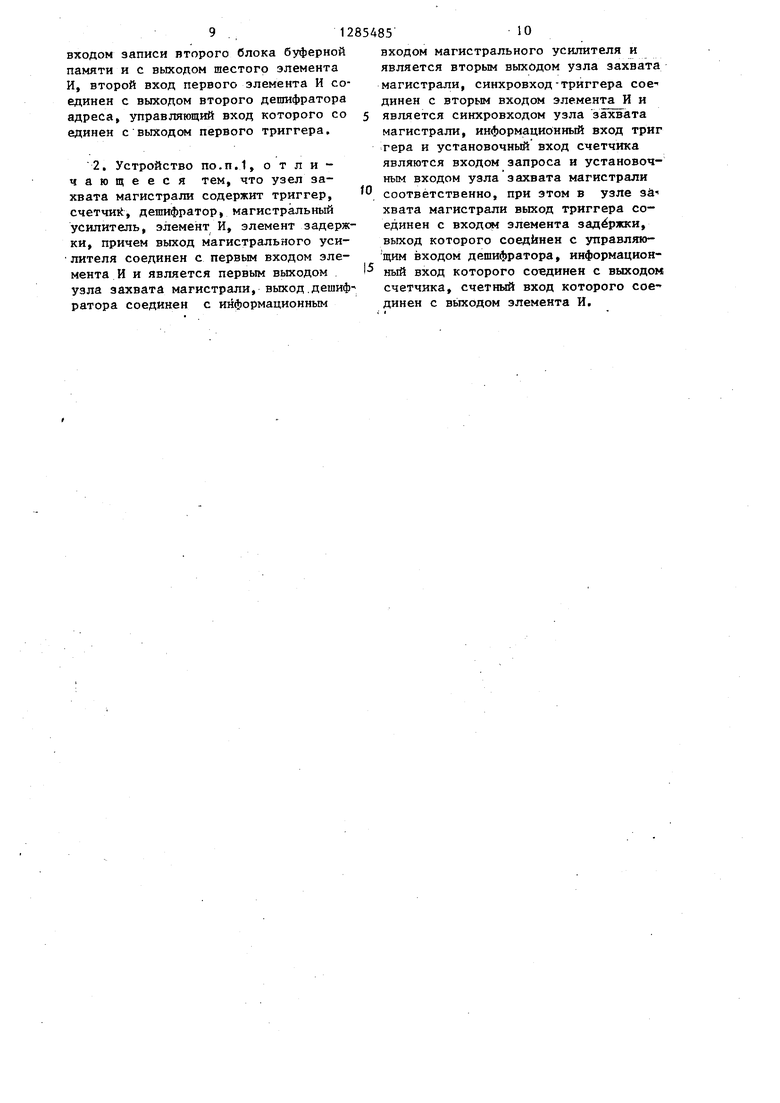

На фиг.1 представлена структурная схема устройства; на фиг.2 - пример реализации узла захвата магистрали, на фиг.З - схема первого дешифратора адреса; на фиг.4 - пример объединения ЭВМ с помощью предлагаемого устройства в многомашинную систему .

Устройство (фиг.1) содержит два дешифратора 1 и 2 адреса, два блока 3 и 4 буферной памяти, два счетчика 5 и 6, регистр 7, триггеры 8-10, магистральные усилители 11-13, генератор 14 импульсов, элемент ИЛИ 15, элементы И 16-21, узел 22 захвата магистрали, одновибраторы 23 и 24.

На фиг.1 обозначены также внутренняя шина-25 ЭВМ, входы 26-28 устройства, общая информационная шина 29,

20 блок 4 буферной памяти - только по .чтению. Соответственно на магистрал 25 выделено два адреса устройства первый адрес - адрес регистра 7; второй адрес - адрес блоков 3 и 4 буферной памяти. Первый и второй ад реса устройства 51 воспринимаются фазе адреса магистрали 25 первым д шифратором 1 адреса. При эт ом в фа данных магистрали 25 на первом или

вход 30 устройства, вход 31 узла 22, общие шины 33 и 34 управления, первая-30 втором выходе дешифратора 1 адреса общая шина 35 синхронизации, выход поддерживается высокий уровень. 36 запроса прерывания устройства, третий установочный вход 38 устройства.

Запись в регистр 7 и блок 3 буф ной памяти сопровождается в фазе данных сигналом на линии 28, а -чте

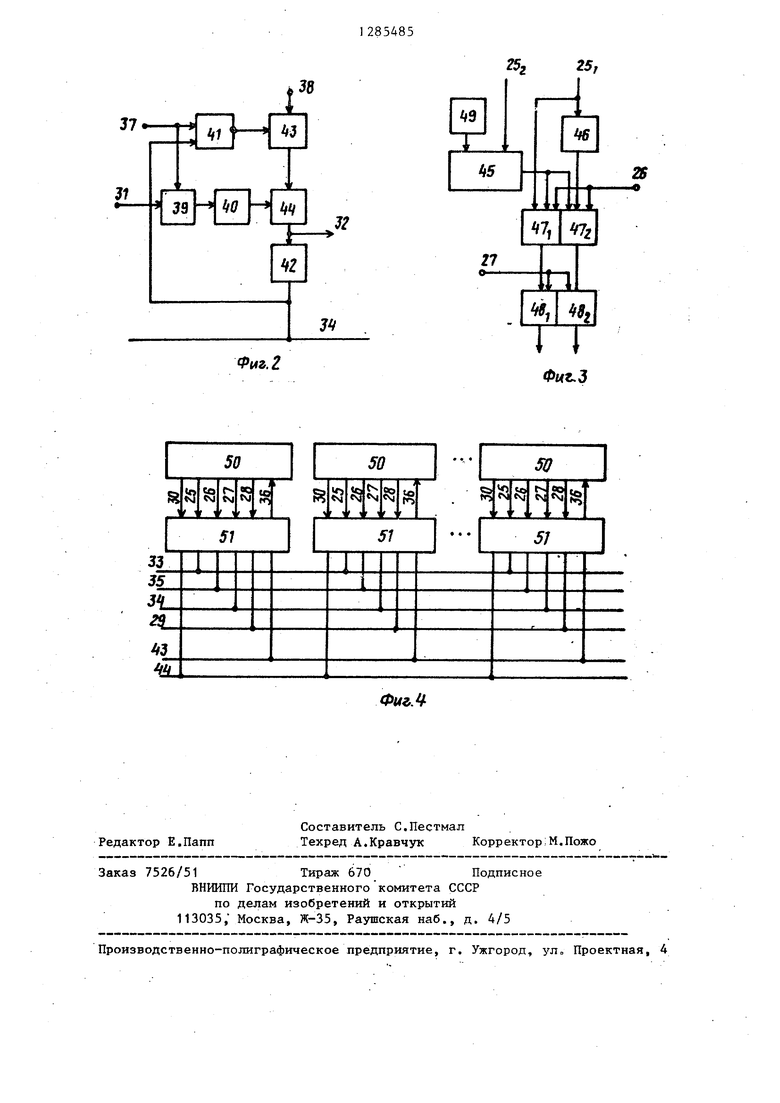

Э зел 22 захвата магистрали (фиг.2) 35 из регистра 7 или блока 4 буферной

содержит триггер 39, элемент 40 задержки, элемент И 41 и магистральный усилитель 42, счетчик 43, дешифратор 44.

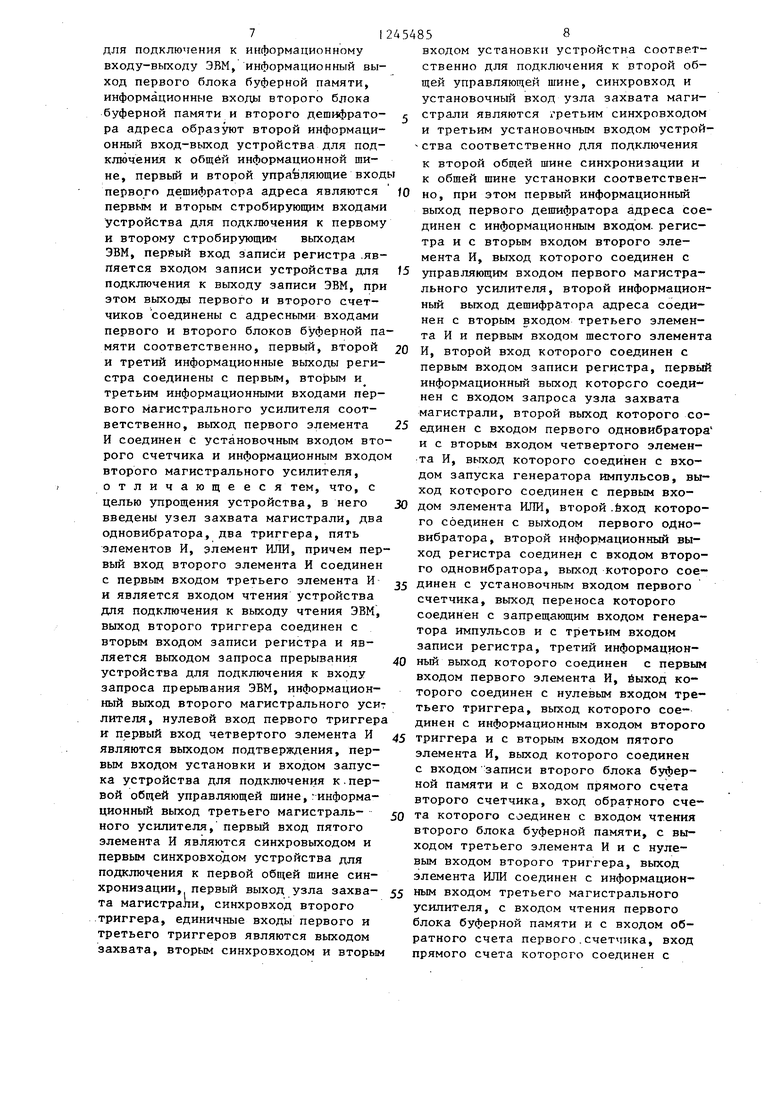

Первый дешифратор адреса (фиг.З) содержит элемент 45 сравнения, элемент НЕ 4Ь, элементы И 47, й 47, триггеры 48 и 482 регистр 49.

Многомашинная система с использованием устройства представлена на фиг.4 и содержит ЭВМ 50 и предлагаемое устройство 51 для сопряжения.

Устройство работает следующим образом.

Обмен между парой ЭВМ 50; и 50j через устройства 51; и 51; и межмашинную магистраль 29 включает следу- кщие этапы: проверка машиной-инициатором 50, обмена занятости своего устройства 51; и при необходимости ожидание его освобождения, занесение пакета данных по магистрали 25 из ЭВК 5П. в блок 3 буферной памят устпамяти - сигналом на линии 30. Чтение с регистра 7 проводится через ма магистральный усилитель 11 при возбуждении выхода элемента И 17. Запис 40 в блок 3 буферной памяти проводится при возбуждении,выхода элемента И

18,а чтение из блока 4 памяти - при возбуждении выхода элемента И

19.По заднему фронту сигнала с эле- 45 мента И 18 (19) происходит увеличени

(уменьшение) на 1 содержимого счет чика 5 (6). С блока 3 буферной памяти на магистраль 29 межмашинного обмена осуществляется только чт ение, а

50 в блок 4 памяти - только запись дан- ньк. . -

Межмашинный обмен начинается с проверки машиной-инициАтором 50 j обмена готовности своего устройства

55 51j. Для этого ЭВМ 50i по своей магистрали 25 считьшает содержимое регистра 7. Если первый, разряд регистра 7 содержит О, то устройство 51;

ройства 51; , захват устройством 51} межмашинной магистрали 29, проверка занятости блока буферной памяти устройства 51: ив случае необходимости ожидание его освобождения; передача пакета данных из блока 3 буферной памяти устройства 51; в блок 4 буферной памяти устройства 51j, передача пакета из блока буферной памяти устройства 51: по магистрали 25 в ЭВМ 50j.

На первом и втором этапах управление происходит от ЭВМ 50;, на последнем этапе от ЭВМ 50j , а на ос5 тальных этапах от устройства 51 .

В устройстве 51 регистр 7 доступен с магистрали 25 как по записи, так и по чтению. Блок 3 буферной памяти доступен только по записи, а

0 блок 4 буферной памяти - только по .чтению. Соответственно на магистрали 25 выделено два адреса устройства 51j первый адрес - адрес регистра 7; второй адрес - адрес блоков 3 и 4 буферной памяти. Первый и второй адреса устройства 51 воспринимаются в фазе адреса магистрали 25 первым дешифратором 1 адреса. При эт ом в фазе данных магистрали 25 на первом или

0 втором выходе дешифратора 1 адреса поддерживается высокий уровень.

втором выходе дешифратора 1 адреса поддерживается высокий уровень.

Запись в регистр 7 и блок 3 буферной памяти сопровождается в фазе данных сигналом на линии 28, а -чтение

памяти - сигналом на линии 30. Чтение с регистра 7 проводится через ма- магистральный усилитель 11 при возбуждении выхода элемента И 17. Запись в блок 3 буферной памяти проводится при возбуждении,выхода элемента И

18,а чтение из блока 4 памяти - при возбуждении выхода элемента И

19.По заднему фронту сигнала с эле- мента И 18 (19) происходит увеличение

(уменьшение) на 1 содержимого счетчика 5 (6). С блока 3 буферной памяти на магистраль 29 межмашинного обмена осуществляется только чт ение, а

в блок 4 памяти - только запись дан- ньк. . -.

Межмашинный обмен начинается с проверки машиной-инициАтором 50 j обмена готовности своего устройства

51j. Для этого ЭВМ 50i по своей магистрали 25 считьшает содержимое регистра 7. Если первый, разряд регистра 7 содержит О, то устройство 51;

31285

готово для обмена данными (не занято) . Если в первом разряде регистра 7 находится М, то устройство 51 занято и ЭВМ 50;периодически опрашивает регистр 7 до момента готовности

устройства 51;. После установления

тывается сигнал, по которому обнуляется счетчик 6 и триггер 9 и, кроме того, через магисфральный усилитель 13 на линию 33 вьщается сигнал подтверждения. По сигналу на линии 33 производите обнуление триггеров 8 всех устройств 51 и через элемент И 20 запуск генератора 14 импульсов

готовности устройства ЗТц ЭВМ 50{ заносит в первый разряд регистра 7 1. По фронту сигнала на вьпсоде первого разряда регистра 7 вьфабатьгеает- tO активного устройства 51 . ся импульс на выходе одновибратора Синхроимпульсы с генератора 14, 23 и происходит обнуление счетчика 5. проходя через элемент ИЛИ 15 актив- После этого начинается занесение пакета данных ,из ЭВМ 50; в блок 3 буного устройства 51, производят выдачу на магистраль 29 очередного сло

ферной памяти устройства 51 (. Для за- 15 ва пакета с блока 3 буферной памяти

писи пакета в блок 3 памяти в фазе адреса на магистрали 25 уЬтанавлива- ется второй адрес устройства 51, а в фазе данных передаются слова пакета. После записи каждого слова.в блок 3 памяти по сигналу с выхода элемейта И 18 происходит автоматическое наращивание содержимого счетчика 5, задапроходя через магистральный усили- . тель 12, линию 35 синхронизации и элемент И 21 пассивного устройства 51. (в триггере 9 которого записан

ющего адрес блока 3 памя ти. После завершения передачи пакета ё блок 3 О ) - осуществляют запись слова с ферной памяти ЭВМ 50 записывает 1 магистрали 29 в блок 4 буферной па- во второй разряд регистра 7, при этом вырабатывается запрос на захват межмашинной магистрали 29, поступающий на вход 31 узла захвата магистрали 22. После разрешения возможных конфликтов по захвату межмашинной магистрали от различных устройст 51 и

30

п

мяти по адресу, определяемому счетчиком 6. По заднему фронту синхроимпульсов содержимое счетчика 6 увеличивается на 1. Таким образом.

весь пакет данных из блока 3 ной памяти устройства 51j через магистраль 29 переписывается в блок 4 буферной памяти пассивно-го устройпредоставления магистрали 29 устройству 51; на выходе 32 узла 22 выраба- 35 ства 51: . При передаче последнего

тьгоается сигнал, кроме этого узел 22 устройства 51 ( выставляет уровень на линию 34, по переднему фронту кото- рог о триггеры 8 и 9 всех устройств 51 устанавливаются в единичное положение. По сигналу с выхода 32 узла захвата магистрали 22 через одновиб- ратор 24 по переднему фронту и элемент ИЛИ 15 производится выдача да

слова пакета на сигнальном выходе счетчика 5 формируется сигнал перен са (обнуления счетчика 5), по которому останавливается генератор 14 40 импульсов и в первый и второй разряды регистра 7 записывается О. В результате этого устройство готово для передачи следующего пакета и ег узел захвата магистрали 22 освобож-

магистраль 29 последнего слова паке- 45 дает магистраль 29 для обмена меяоду

другими ЭВМ, снимая уровень с линии 34.

По заднему фронту сигнала занятости на линии 34 осуществляется зата, соответствующего адресу устройства 51; (адрес этого слова содер- ;жит ся в счетчике 5) пассивной ЭВМ 50 J. Адрес на магист рали 29 при единичном состоянии триггеров 8 воспри- 50 нимается всеми устройствами 51, но только в адресуемом устройстве 51j на входе дешифратора 2 адреса формируется сигнал. По сигналу с выхода дешифратора 2 при О на третьем выходе регистра 7 (выхс(д третьего разряда регистра 7), в котором находитпись 1 в -триггер 10 постоянного : устройства 51 из триггера 9, в котором находится О (инверсйый выход триггера 9 подключен к D-входу триг- гера 1U, его С-вход подключен к ли- 55 НИИ 34). При переброске триггера 10 происходит запись 1 в третий разряд регистра 7. При единичном состоянии триггера 10 на сигнальном выходе

ся 1 при незанятости блока 4 памя-

ти, на выходе элемента И 16 вырабатывается сигнал, по которому обнуляется счетчик 6 и триггер 9 и, кроме того, через магисфральный усилитель 13 на линию 33 вьщается сигнал подтверждения. По сигналу на линии 33 производите обнуление триггеров 8 всех устройств 51 и через элемент И 20 запуск генератора 14 импульсов

активного устройства 51 . Синхроимпульсы с генератора 14, проходя через элемент ИЛИ 15 актив-

активного устройства 51 . Синхроимпульсы с генератора 14, проходя через элемент ИЛИ 15 актив-

ного устройства 51, производят выдачу на магистраль 29 очередного слопо адресу, определенному счетчиком 5. Содержимое счетчика 5 зт еньшается по заднему фронту импульса с генератора 14. Синхроимпульсы с генера- тора 14 активного устройства 51;,

проходя через магистральный усили- тель 12, линию 35 синхронизации и элемент И 21 пассивного устройства 51. (в триггере 9 которого записан

О ) - осуществляют запись слова с агистрали 29 в блок 4 буферной па-

п

-5 О ) - осуществляют запись слова с магистрали 29 в блок 4 буферной па-

30

мяти по адресу, определяемому счетчиком 6. По заднему фронту синхроимпульсов содержимое счетчика 6 увеличивается на 1. Таким образом.

О ) - осуществляют запись слова с магистрали 29 в блок 4 буферной па-

весь пакет данных из блока 3 ной памяти устройства 51j через магистраль 29 переписывается в блок 4 буферной памяти пассивно-го устройслова пакета на сигнальном выходе счетчика 5 формируется сигнал переноса (обнуления счетчика 5), по которому останавливается генератор 14 импульсов и в первый и второй разряды регистра 7 записывается О. В результате этого устройство готово для передачи следующего пакета и его узел захвата магистрали 22 освобож-

пись 1 в -триггер 10 постоянного устройства 51 из триггера 9, в котором находится О (инверсйый выход триггера 9 подключен к D-входу триг- гера 1U, его С-вход подключен к ли- НИИ 34). При переброске триггера 10 происходит запись 1 в третий разряд регистра 7. При единичном состоянии триггера 10 на сигнальном выходе

36 устройства 51: формируется сигнал запроса в ЭВМ 50., которая начинает чтение пакета данных из блока А буферной памяти (возможна инициация njJHeMa -пакета ЭВМ 50 не только по прерыванию, но и при ее периодической проверке третьего разряда регистра состояния 7, доступного по чтению с магистрали 25), При чтении первого слова с блока 4 памяти сигналом с выхода элемента И 19 триггер 10 обнуляется. Информация о количестве слов в пакете ЭВМ 50: получает из первых слов пакета, занесенного в блок 4 памяти. .

Если требуется осуществить передачу пакета из пассивной ЭВМ 50: в активную ЭВМ 50J-, то, как было рассмотрено вьше, ЭВМ 50; передает в пакет

ЭВМ

50: пакет, содержащий информацию о необходимости чтения пакета из ЭВМ 50 заголовок пакета (либо начальный адрес пакета и при необходимости число передаваемых слов), а также адрес ЭВМ-приемника пакета. Заметим, что приемником пакета может быть как ЭВМ- инициатор 50; обмена, так и некоторая третья ЭВМ 50,

Рассмотрим работу узла 22 захвата магистрали (фиг,2), о

Запросы на захват магистрали 29 межмашинного обмена поступают на вход 31 и по синхровходу 37 заносятся в триггер 39, При незанятости магист- 29 наVлинии ЗА нет сигнала и блокировки поступления синхроимпульсов с входа 37 через элемент И 41 на вход счетчика 43 не происходит, При этом осуществляется увеличение содержимого счетчика 43 и последовательная проверка (при поступлении каждого синхроимпульса с входа 37) 1,2,3,,,,,Ктго устройства 51 на наличие запроса С в триггере 39), В результате того, что в первом устройстве 51 к входу усилителя 42 подключен первый выход дешифратора 44, во втором - второй и т,д,, в каждый момент времени происходит проверка наличия запроса т.олько в одном устройстве 51, Если оно запрашивает захват магистрали, то на выходе 43 формируется сигнал и на линию 34 через усилитель 42 выставляется сигнал занятости, по которому блокируется прохозкдение синхроимпульсов с входа 37 на счетный вход счетчиков 43, чем фиксируется захват общей магистрали

одним 1-м устройством (номер i которого определяется содержимым счетчика 43). Если i-e устройство 51 не требует обмена через общую магистраль то при следующем син:хроимпульсе содержимое счетчиков 43 увеличивается

и происходит проверка следующего (i+1)-ro устройства и т,д, (наращивание содержимого счетчиков происходит, если на линии 34 Hei- сигнала занятости), При завершении процедуры обмена в устройстве 51 снимается за-i прос с входа 31 узла 22 и по синхроимпульсу с входа 37 триггер 39 обнуляется и сигнал занятости с магистра ли 34 и выхода 32 снимается, в результате чего общая магистраль может быть представлена для обмена между другими машинами 50, Задержка на элементе 40 определяется временем срабатывания счетчика 43,

Рассмотрим работу дешифратора 1 адреса. Предварительно в регистре 49 (фиг,3) задается адрес устройства 51 на магистрали 25, На элементе 45 сравнения происходит сравнения кода с регистра 49 и кода на линиях магистрали 25, начиная с второй. Если на выходе элемента 45 сравнения формируется сигнал, то на элементах И 47 и НЕ 46 по первой линии магистрали 25 идентифицируется первьй или второй адрес устройства 51, При идентификации первого адреса сигналом- с элемента И 47, в фазе адреса (1 на линии 25) в триггер 48j заносится единица, а при идентификации второго адреса единица заносится в триггер 48,

Обнуление триггеров 48 происходит по заднему фронту сигнала сопровождения данных на линии 27,

Формула изобре т.е н и я

,

1, Устройство для сопряжения электронных вычислительных машин, содержащее два блока буферной памяти, два дешифратора адреса, два счетчика, регистр, три магистральных усилителя, генератор импульсов, первый триггер, первый элемент И, причем информационные входы первого дешифратора адреса, первого блока буферной памяти,

информационные выходы первого магистрального усилителя, второго блока буферной памяти образуют первый информационный вход-выход устройства

для подключения к информадионному входу-выходу ЭВМ, информадионный выход первого блока буферной памяти, информадионные входы второго блока буферной памяти и второго дешифрато- ра адреса образуют второй информационный вход-выход устройства для дод- ключения к общей информационной шине, первый и второй управляющие вход первого дешифратора адреса являются первым и вторым стробирующим входами устройства для подключения к первому и второму стробирующим выходам ЭВМ, первый вход записи регистра .является входом записи устройства для подключения к выходу записи ЭВМ, при этом выходы первого и второго счетчиков соединены с адресными входами первого и второго блоков буферной памяти соответственно, первый, второй и третий информационные вьпсоды регистра соединены с первым, вторым и третьим информационными входами первого магистрального усилителя соответственно, выход первого элемента И соединен с установочным входом второго счетчика и информационным входо второго магистрального усилителя, отличающееся тем, что, с целью упрощения устройства, в него введены узел захвата магистрали, два одновибратора, два триггера, пять элементов И, элемент ИЛИ, причем первый вход второго элемента И соединен с первым входом третьего элемента И и является входом чтения устройства для подключения к выходу чтения ЭВМ, выход второго триггера соединен с вторым входом записи регистра и является выходом запроса прерывания устройства для подключения к входу запроса прерьгаания ЭВМ, информационный выход второго магистрального усит лителя, нулевой вход первого триггера и первый вход четвертого элемента И являются выходом подтверждения, первым входом установки и входом задус- ка устройства для подключения к.первой общей управляющей шине,г информационный выход третьего магистраль- ного усилителя, первый вход пятого элемента И являются синхровыходом и первым синхровходом устройства для подключения к первой общей шине синхронизации, первый выход узла захва- та магистрали, синхровход второго .триггера, единичные входы первого и третьего триггеров являются выходом захвата, вторым синхровходом и вторым

входом установки устройстна соответственно для подключения к второй общей управляющей шине, синхровход и установочный вход узла захвата магистрали являются третьим синхровходом и третьим установочным входом устрой ства соответственно для подключения к второй общей шине синхронизации и к обшей шине установки соответственно, при этом первый информационный выход первого дешифратора адреса соединен с информационным входом, регистра и с вторым входом второго элемента И, выход которого соединен с управляющим входом первого магистрального усилителя, второй информационный выход дешифратора адреса соединен с вторым входом третьего элемента И и первым входом шестого элемент И, второй вход которого соединен с первым входом записи регистра, первы информационный выход которого соединен с входом запроса узла захвата магистрали, второй выход которого соединен с входом первого одновибратора и с вторым входом четвертого элемента И, выход которого соединен с входом запуска генератора импульсов, выход которого соединен с первым входом элемента ИЛИ, второй .&ход которого соединен с выходом первого одно- вибратора, второй информационный выход регистра соединен с входом второго одновибратора, выход которого соединен с установочным входом первого счетчика, выход переноса которого соединен с запрещающим входом генератора импульсов и с третыгм входом записи регистра, третий информационный выход которого соединен с первым входом первого элемента И, йыход которого соединен с нулевым входом третьего триггера, выход которого соединен с информационным входом второго триггера и с вторым входом пятого элемента И, выход которого соединен с входом эаписи второго блока буферной памяти и с входом прямого счета второго счетчика, вход обратного счета которого соединен с входом чтения второго блока буферной памяти, с выходом третьего элемента И и с нулевым входом второго триггера, выход элемента ИЛИ соединен с информационным входом третьего магистрального усилителя, с входом чтения первого блока буферной памяти и с входом обратного счета первого.счетчика, вход прямого счета которого соединен с

входом записи второго блока буферной памяти и с выходом шестого элемента И, второй вход первого элемента И соединен с выходом второго дешифратора адреса, управляющий вход которого со единен с выходом первого триггера,

2. Устройство ПО.П.1, о т л и - чающееся тем, что узел захвата магистрали содержит триггер, счетчий, дешифратор, магистральный усилитель, элемент И, элемент задержки, причем выход магистрального усилителя соединен с первым входом элемента И и является первым выходом узла захвата магистрали, выход,дешиф ратора соединен с информационным

входом магистрального усилителя и является вторым выходом узла захвата магистрали, синхровход-триггера сое динен с вторым входом элемента И и является синхровходом узла магистрали, информационный вход триг гера и установочный вход счетчика являются входом запроса и установочным входом узла захвата магистрали соответственно, при этом в узле за хвата магистрали выход триггера соединен с входом элемента задержки, вьпсод которого соединен с управляющим входом дешифратора, информационный вход которого соединен с выходом счетчика, счетный вход которого соединен с вьпсодом элемента И.

25,

25,

J7

Фиг. 2

Фиг.3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ | 1986 |

|

SU1381534A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1987 |

|

SU1462336A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с магистралью | 1984 |

|

SU1246107A1 |

| Устройство для сопряжения электронных вычислительных машин | 1987 |

|

SU1443001A1 |

| Устройство для сопряжения ЭВМ с общей магистралью | 1988 |

|

SU1532939A1 |

| Устройство для сопряжения ЭВМ | 1987 |

|

SU1418729A1 |

| Устройство для сопряжения вычислительной машины с общей магистралью | 1986 |

|

SU1354199A1 |

| Устройство для сопряжения ЭВМ | 1986 |

|

SU1376095A1 |

| Устройство для сопряжения ЭВМ | 1987 |

|

SU1460724A1 |

| Устройство для сопряжения цифровых вычислительных машин | 1988 |

|

SU1571603A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении многопроцессорных и многомашинных вычислительных систем. Целью изобретения является упрощение устройства за счет обмена через один приемный и передающий блок буферной памяти со всеми ЭВМ, подключаемыми к общей межмашинной магистрали. Устройство содержит два дешифратора 1, 2 адреса, два блока 3, 4 буферной памяти, два счетчика 5, 6, регистр 7, три триггера 8-10, три магистральных усилителя 11-13-, генератор 14 импульсов, Элемент ИЛИ 15, шесть элементов И 16-21, узел 22 захвата магистрали, два одновибратора 23, 24. 1 з.п. ф-лы, 4 ил. 25

Редактор Е.Папп

Составитель С.Пестмал

Техред А.Кравчук Корректор;М.Пожо

Заказ 7526/51Тираж 670 Подписное

ВНИШТИ Государственного комитета СССР

по делам изобретений и открытий 113035; Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул Проектная, 4

Фиг.

| Устройство для отбора проб | 1979 |

|

SU990088A3 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения электронных вычислительных машин | 1980 |

|

SU962905A1 |

Авторы

Даты

1987-01-23—Публикация

1985-09-11—Подача