Изобретение относится ,к технике контроля и автоматизации управления производственными процессами и преимущественно может быть использовано в системах автоматизированного управления технической эксплуатацией радиоэлектронных комплексов, а также в научных исследованиях.

Целью изобретения является повыше-jg ние точности определения времени проведения технического обслуживания системы путем учета информации о состоянии системы в момент времени, предшествующий техническому обслужи- $ ванию.

Уменьшение погрешности определения времени проведения технического обслуживания возможно при переходе к модели технического обслуживания сложных систем по фактическому техническому состоянию. При этом в качестве параметра, характеризующего состояние системы, выбирается параметр потока отказов, область его воз-25 можных состояний разбивается на W уровней и в дискретные моменты вреW

20

мени ,2,..., Т, где окончания эксплуатации ределяется состоянием уровень параметра пото где ,1,...,W, и при ние о проведении одног ных видов технического где ,1,...,К.

Каждый вид техничес ния характеризуется за проведение CYo(K). Кро ты на техническую эксп теризуются затратами н тояния системы Ck, зат становление отказов С ными затратами, связан нением системой требов

ности С

Для определения опт критерию минимума затр ведения технического обходимо решить функци нение динамического пр для марковского процес системой

. 1 pii si(t+1)b

s (т)о,

ч

мени ,2,..., Т, где Т - время окончания эксплуатации системы, определяется состоянием системы как уровень параметра потока отказов и/,- , где ,1,...,W, и принимается решение о проведении одного из К возможных видов технического обслуживания, где ,1,...,К.

Каждый вид технического обслуживания характеризуется затратами на его проведение CYo(K). Кроме того, затраты на техническую эксплуатацию характеризуются затратами на контроль состояния системы Ck, затратами на восстановление отказов С6 и дополнительными затратами, связанными с невыполнением системой требований по надежности С

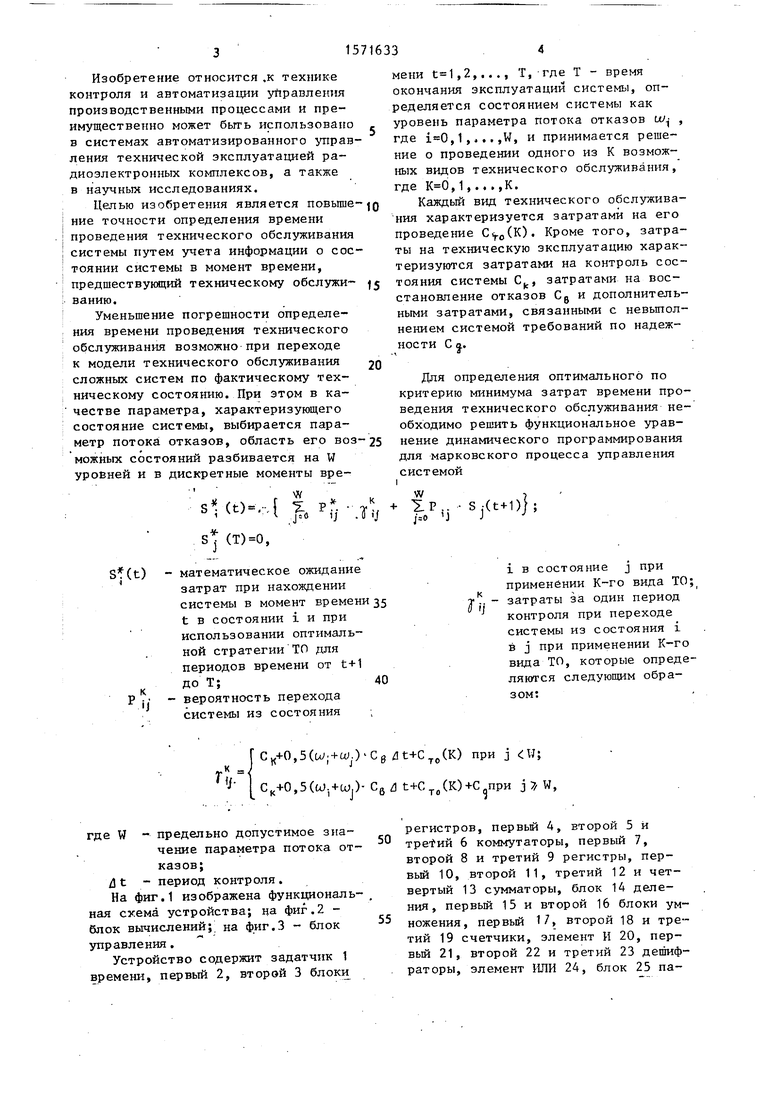

Для определения оптимального по критерию минимума затрат времени проведения технического обслуживания необходимо решить функциональное уравнение динамического программирования для марковского процесса управления системой

ii

ч

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления матрицы направляющих косинусов | 1983 |

|

SU1233142A1 |

| Устройство для вывода информации на экран электронно-лучевой трубки | 1977 |

|

SU1029177A1 |

| Арифметико-логическое устройство | 1983 |

|

SU1176321A1 |

| Устройство для считывания графической информации | 1981 |

|

SU983731A1 |

| Вероятностный коррелометр | 1981 |

|

SU1049921A1 |

| Устройство для вычисления полинома | 1980 |

|

SU885997A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Цифровой коррелятор | 1983 |

|

SU1129621A1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Устройство для умножения | 1980 |

|

SU960805A1 |

Изобретение относится к контролю и автоматизации управления производственными процессами и может быть использовано в системах автоматизированного управления технической эксплуатацией радиоэлектронных комплексов. Целью изобретения является повышение точности определения времени проведения технического обслуживания системы путем учета информации о состоянии системы в момент времени, предшествующий техническому обслуживанию. Устройство содержит датчик 1 времени, первый и второй блоки 2 и 3 регистров, первый, второй и третий коммутаторы 4, 5 и 6, первый, второй и третий регистры 7, 8 и 9, первый, второй, третий и четвертый сумматоры 10, 11, 12 и 13, блок 14 деления, первый и второй блоки 15 и 16 умножения, первый, второй и третий счетчики 17, 18 и 19, элемент И 20, первый, второй и третий дешифраторы 21, 22 и 23, элемент ИЛИ 24, блок 25 памяти, блок 26 вычислений, блок 27 управления и регистратор 28. 2 з.п. ф-лы, 3 ил.

(t)

математическое ожидание затрат при нахождении системы в момент времени 35 t в состоянии i и при использовании оптимальной стратегии ТО для периодов времени от t+1 до Т;40

вероятность перехода системы из состояния

& г /

Г у.

Ск+0,5(ы;+.) С8 4t+CTO(K) при j U; CK+0,5(w,+w.)- С6 и t+CTO(K)+C при j 7/ W,

где W - предельно допустимое значение параметра потока отказов;

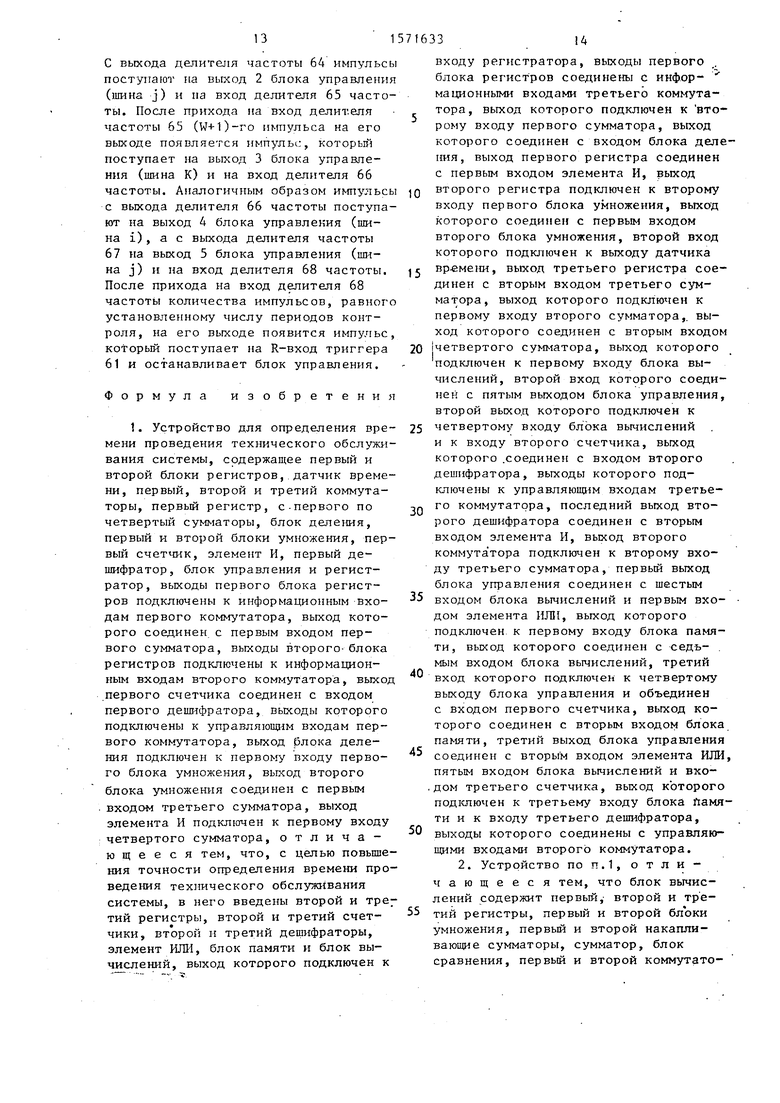

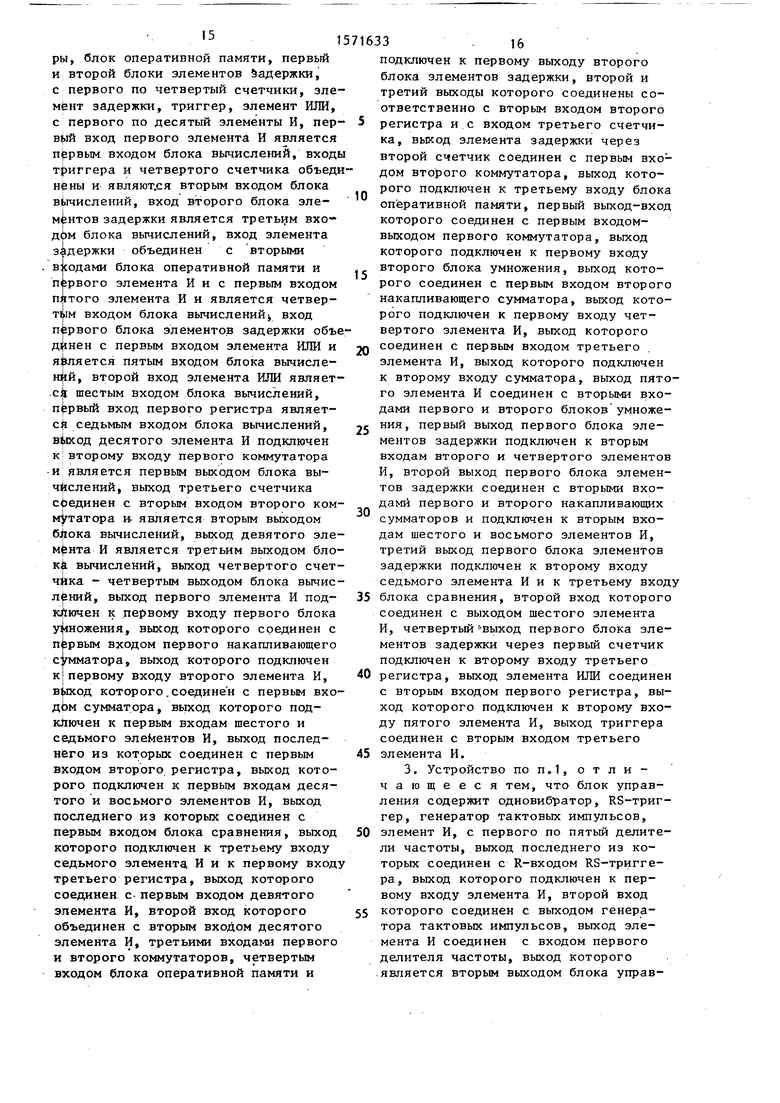

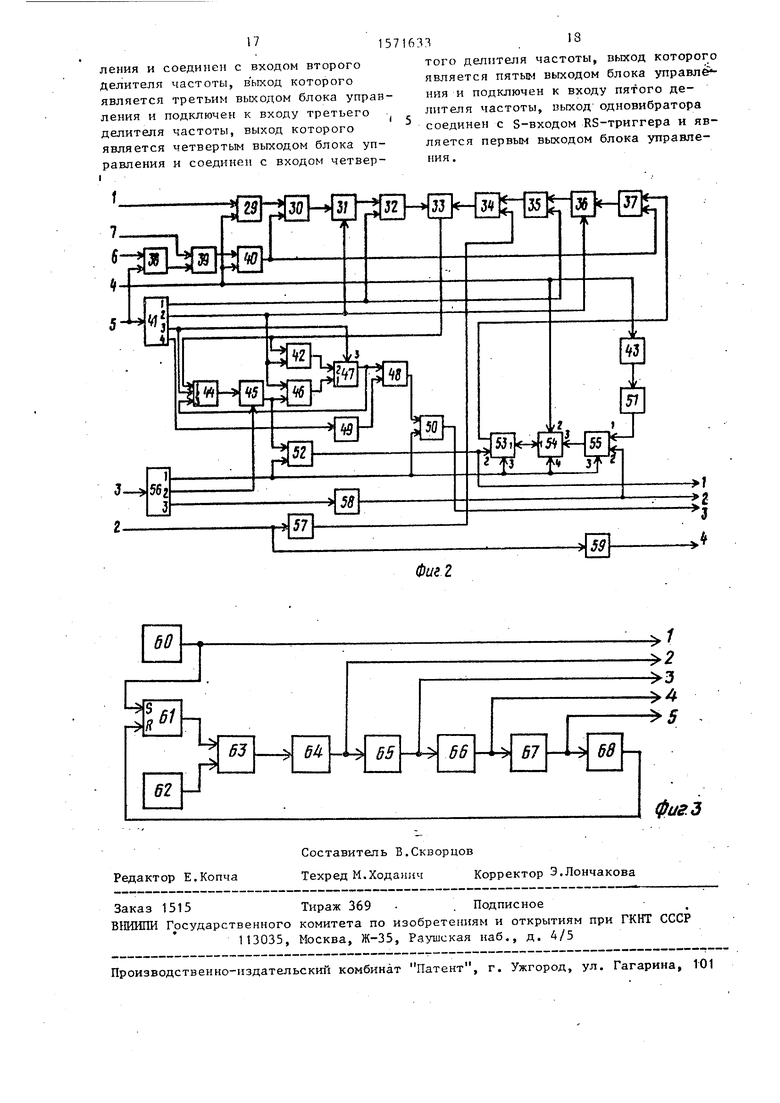

иt - период контроля. На фиг.1 изображена функциональная схема устройства; на фиг.2 - блок вычислений; на фиг.З - блок управления.

Устройство содержит задатчик 1 времени, первый 2, второй 3 блоки

к

ч

i в состояние j при применении К-го вида ТО затраты за один период контроля при переходе системы из состояния i в j при применении К-го вида ТО, которые определяются следующим образом:

регистров, первый 4, второй 5 и третий 6 коммутаторы, первый 7,

второй 8 и третий 9 регистры, первый 10, второй 11, третий 12 и четвертый 13 сумматоры, блок 14 деления, первый 15 и второй 16 блоки умножения, первый 17, второй 18 и третий 19 счетчики, элемент И 20, первый 21, второй 22 и третий 23 дешифраторы, элемент ИЛИ 24, блок 25 па

5

мяти, блок 26 вычислений, блок 27 управления и регистратор 28.

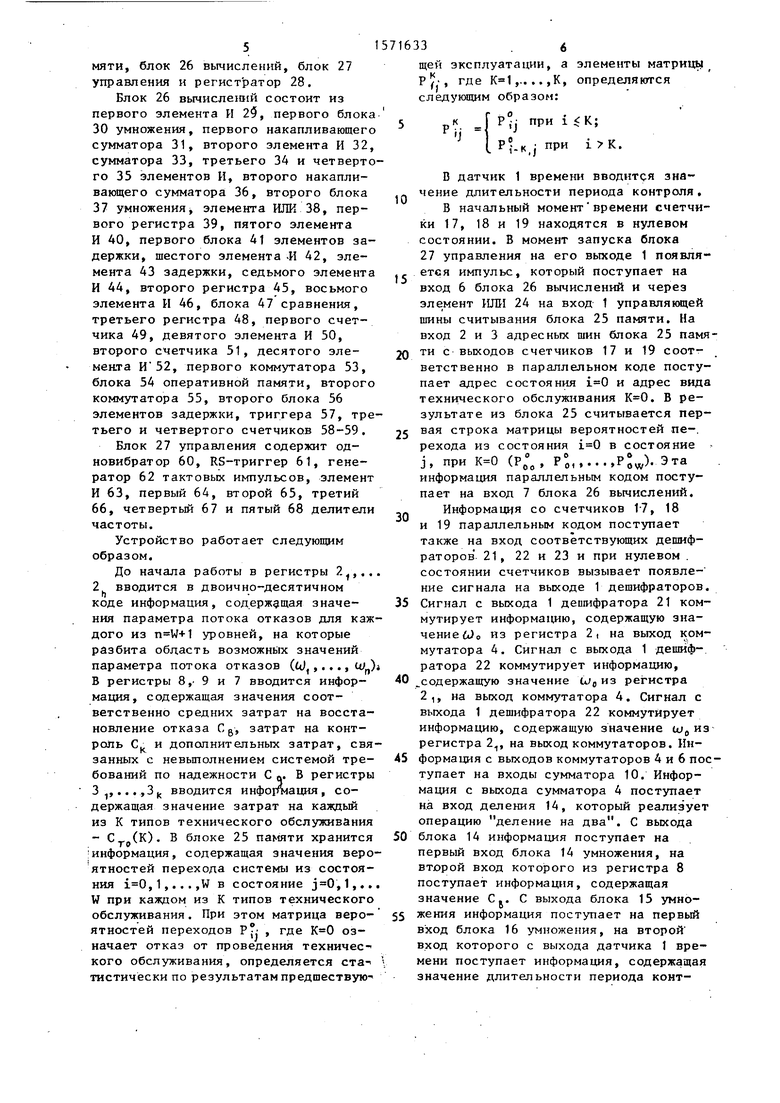

Блок 26 вычислений состоит из первого элемента И 25, первого блока 30 умножения, первого накапливающего сумматора 31, второго элемента И 32, сумматора 33, третьего 34 и четвертого 35 элементов И, второго накапливающего сумматора 36, второго блока 37 умножения, элемента ИЛИ 38, первого регистра 39, пятого элемента И 40, первого блока 41 элементов задержки, шестого элемента -И 42, элемента 43 задержки, седьмого элемента И 44, второго регистра 45, восьмого элемента И 46, блока 47 сравнения, третьего регистра 48, первого счетчика 49, девятого элемента И 50, второго счетчика 51, десятого элемента И 52, первого коммутатора 53, блока 54 оперативной памяти, второго коммутатора 55, второго блока 56 элементов задержки, триггера 57, третьего и четвертого счетчиков 58-59.

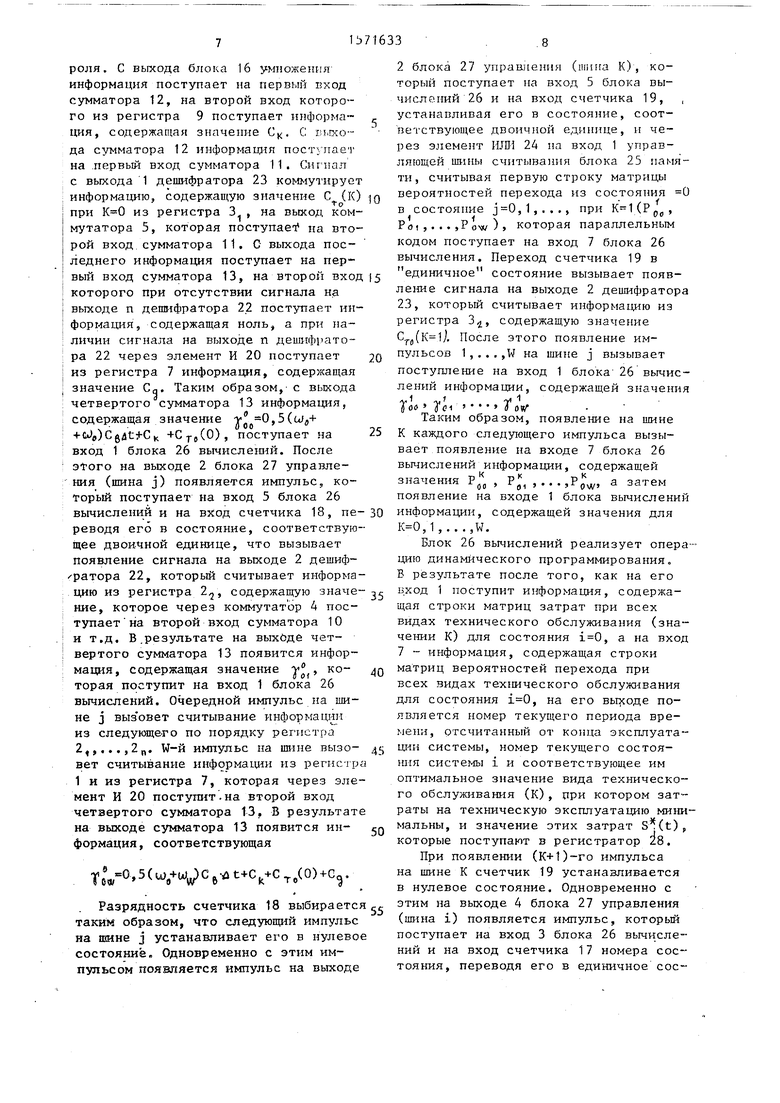

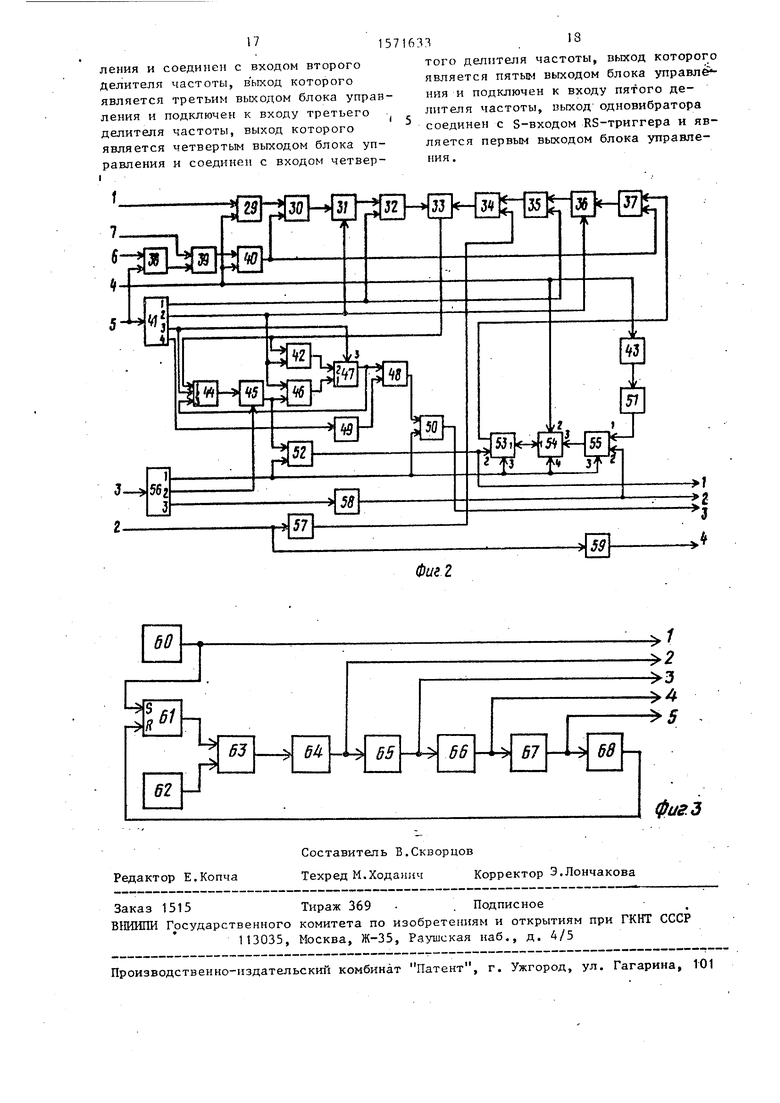

Блок 27 управления содержит од- новибратор 60, RS-триггер 61, генератор 62 тактовых импульсов, элемент И 63, первый 64, второй 65, третий 66, четвертый 67 и пятый 68 делители частоты.

Устройство работает следующим образом.

До начала работы в регистры 2.,

2вводится в двоично-десятичном коде информация, содержащая значения параметра потока отказов для каждого из уровней, на которые разбита область возможных значений

параметра потока отказов (CJtц п)

В регистры 8, 9 и 7 вводится информация, содержащая значения соответственно средних затрат на восстановление отказа С6, затрат на контроль Ск и дополнительных затрат, связанных с невыполнением системой требований по надежности С ,,. В регистры

3,,...,3k вводится информация, содержащая значение затрат на каждый из К типов технического обслуживания - С (К). В блоке 25 памяти хранится информация, содержащая значения вероятностей перехода системы из состояния ,1W в состояние ,1,..

W при каждом из К типов технического обслуживания. При этом матрица вероятностей переходов Р°- , где означает отказ от проведения техничес кого обслуживания, определяется ста- тистически по результатам предшествую-1

щей эксплуатации, а элементы матрицы

, где ,К, определяются

следующим образом:

1P°J при i К; P.K(j при .

0

5

0

В датчик 1 времени вводится значение длительности периода контроля.

В начальный момент времени счетчики 17, 18 и 19 находятся в нулевом состоянии. В момент запуска блока 27 управления на его выходе 1 появляется импульс, который поступает на вход 6 блока 26 вычислений и через элемент ИЛИ 24 на вход 1 управляющей шины считывания блока 25 памяти. На вход 2 и 3 адресных шин блока 25 памяо ти с выходов счетчиков 17 и 19 соответственно в параллельном коде поступает адрес состояния и адрес вида технического обслуживания . В результате из блока 25 считывается пер-

5 вая строка матрицы вероятностей пе-. рехода из состояния в состояние - J, при (Р0°о, Р 00,,...,P°w). Эта информация параллельным кодом поступает на вход 7 блока 26 вычислений.

Информация со счетчиков 17, 18 и 19 параллельным кодом поступает также на вход соответствующих дешифраторов 21, 22 и 23 и при нулевом . состоянии счетчиков вызывает появле- ние сигнала на выходе 1 дешифраторов.

5 Сигнал с выхода 1 дешифратора 21 коммутирует информацию, содержащую значение dJ0 из регистра 2( на выход коммутатора 4. Сигнал с выхода 1 дешифратора 22 коммутирует информацию,

0 содержащую значение и„ из регистра 2,, на выход коммутатора 4. Сигнал с выхода 1 дешифратора 22 коммутирует информацию, содержащую значение из регистра 2.,, на выход коммутаторов. Ин5 формация с выходов коммутаторов 4 и 6 поступает на входы сумматора 10. Информация с выхода сумматора 4 поступает на вход деления 14, который реализует операцию деление на два. С выхода

0 блока 14 информация поступает на первый вход блока 14 умножения, на второй вход которого из регистра 8 поступает информация, содержащая значение С.. С выхода блока 15 умно5 жения информация поступает на первый вход блока 16 умножения, на второй вход которого с выхода датчика 1 времени поступает информация, содержащая значение длительности периода конт

роля. С выхода блока 16 умножения информация поступает на первый вход сумматора 12, на второй вход которого из регистра 9 поступает информация, содержащая значение Ск. С п.ко- да сумматора 12 информация поступает на первый вход сумматора 11. Сигнал с выхода 1 дешифратора 23 коммутирует информацию, содержащую значение Ст(К) при из регистра 3 , на выход коммутатора 5, которая поступает1 на второй вход сумматора 11. С выхода последнего информация поступает на первый вход сумматора 13, на второй вход которого при отсутствии сигнала на выходе п дешифратора 2.2 поступает информация, содержащая ноль, а при наличии сигнала на выходе п дешифратора 22 через элемент И 20 поступает из регистра 7 информация, содержащая значение Сд. Таким образом, с выхода четвертого сумматора 13 информация, содержащая значение ,5(we+ + )CgattCK +СТ„(0), поступает на вход 1 блока 26 вычислений. После

К каждого следующего импульса вызывает появление на входе 7 блока 26 вычислений информации, содержащей

значения Р, , Р, , ...,, а затем появление на входе 1 блока вычислений

этого на выходе 2 блока 27 управления (шина j) появляется импульс, который поступает на вход 5 блока 26

вычислений и на вход счетчика 18, пе-30информации, содержащей значения для

реводя его в состояние, соответствую-K 0,1,...,W.

щее двоичной единице, что вызывает Блок 26 вычислений реализует опера- появление сигнала на выходе 2 дешиф-цию динамического программирования. ратора 22, который считывает информа-В результате после того, как на его цию из регистра 2, содержащую значе- вход 1 поступит информация, содержание, которое через коммутатор 4 пос-щая строки матриц затрат при всех тупает на второй вход сумматора 10видах технического обслуживания (зна40

45

чении К) для состояния , а на вход 7 - информация, содержащая строки матриц вероятностей перехода при всех видах технического обслуживания для состояния , на его выходе появляется номер текущего периода времени, отсчитанный от конца эксплуатации системы, номер текущего состояния системы i и соответствующее им оптимальное значение вида технического обслуживания (К), при котором затраты на техническую эксплуатацию минимальны, и значение этих затрат S(t), которые поступают в регистратор 28.

При появлении ()го импульса на шине К счетчик 19 устанавливается в нулевое состояние. Одновременно с Разрядность счетчика 18 выбирается этим на выходе 4 блока 27 управления таким образом, что следующий импульс (шина i) появляется импульс, который на шине j устанавливает его в нулевое поступает на вход 3 блока 26 вычисле- состояние. Одновременно с этим им- ний и на вход счетчика 17 номера сое- пульсом появляется импульс на выходе тояния, переводя его в единичное соеи т.д. В.результате на выходе четвертого сумматора 13 появится информация, содержащая значение у, которая поступит на вход 1 блока 26 вычислений. Очередной импульс на шине j выз овет считывание информации из следующего по порядку регистра 2,,...,2п. W-й импульс на шине вызовет считывание информации из регис-ipa 1 и из регистра 7, которая через элемент И 20 поступит.на второй вход четвертого сумматора 13, В результате на выходе сумматора 13 появится информация, соответствующая

TeV0 5K+4 C t+Ck+CT.

50

0

5

2 блока 27 управления (шина К), который поступает на вход 5 блока вычислений 26 и на вход счетчика 19, , устанавливая его в состояние, соответствующее двоичной единице, и через элемент ИЛИ 24 на вход 1 управляющей шины считывания блока 25 памяти, считывая первую строку матрицы вероятностей перехода из состояния 0 в состояние ,1,..., при (Рро, Pot ,. .. ,Р ow ) которая параллельным кодом поступает на вход 7 блока 26 вычисления. Переход счетчика 19 в единичное состояние вызывает появление сигнала на выходе 2 дешифратора 23, который считывает информацию из регистра 3, содержащую значение СТО( После этого появление импульсов 1,...,W на шине j вызывает поступление на вход 1 блока 26 вычислений информации, содержащей значения

УОО и $ о#

Таким образом, появление на шине

К каждого следующего импульса вызывает появление на входе 7 блока 26 вычислений информации, содержащей

значения Р, , Р, , ...,, а затем появление на входе 1 блока вычислений

тояние, что изменяет значение адреса на входе 2 блока памяти. В этом слуае (К+1)-й импульс на шине К, пройя через элемент ИЛИ 24, считывает из блока 25 памяти информацию, соержащую значение вероятностей перехода для состояния системы (Pfo , Р ,.. . ,Р w . Появление импульсов на шине, а затем и на шине К вызовет поступление на вход 7 блока вычислений информации, содержащей значения , Р , ...,PfKw, а на вход 1 блока вычислений информации, содержащей значения у,..., | В результате решения уравнения динамического программирования в регистратор поступит

значение К опт и S(t) для и .

Одновременно с появлением (W- -l)-ro импульса на шине, который переводит счетчик номера состояния i 25 в нулевое состояние, появляется импульс на выходе 5 блока 27 управления (шина t), который поступает на РХОД 2 блока вычисления и процесс вычислений Копт и S (t) повторяется при следующем периоде времени. После вычисления Копти S(t) для всех ,1Т

процесс оканчивается. В результате по данным, хранящимся в регистраторе, определяется для каждого времени контроля и возможного состояния системы необходимо (при К 0) или нет (при

К 0) техническое обслуживание,

Блок 26 вычислений работает следующим образом.

Информация, содержащая значение Р;; , поступает параллельным кодом на вход 1 регистра 39. На вход 6 блока вычислений при запуске блока 27 управления или на вход 5 при дальнейшей работе поступают импульсы, которые, пройдя через элемент ИЛИ 38, поступают на вход 2 регистра 39 и разрешают запись параллельным кодом информации, поступившей на первый вход этого регистра. Импульс, пришедший по шине на пход 4 блока 26-, поступает на вторые входы элементов И 29 и 40. Информация, содержащая значения -у1 и Р ; соответственно через элементы И 29 и 40 поступает на .блок 30 умножения, перемножается поступает на вход накапливающего сумматора 31. Таким образом, в суматоре 31 содержится информация, сок к ответствующая сумме Р ;j (,; После

рихода по шине j(W+1)-ro импульса

0

5

5

5

в сумматоре 31 записывается инфор- . мация, содержащая значение S ;

тпг К К

Ё Р) If Одновременно с (W-M)-M

| о

импульсом по шине j на вход 5 блока вычислений по шине К приходит импульс, который через элемент ИЛИ 38 поступает на вход 2 регистра 39 и разрешает запись в нег.о параллельным кодом очередной строки матрицы Р .. Этот же импульс поступает на вход блока 41 элементов задержки. Через интервал времени, необходимый для вычисления и записи значения S в сум0

0

матор 31, на выходе 1 блока 41 появляется импульс, который поступает на второй вход элемента И 32 и считывает информацию параллельным кодом из сумматора 31 в сумматор 33.

На нулевом этапе времени, который эквивалентен времени окончания эксплуатации системы, триггер 57 и счетчик 59 периодов времени находятся в нулевом состоянии. С выхода счетчика 59 информация с номера этапа эксплуатации поступает на выход блока вычислений. Сигнал с выхода триггера 57 запрещает выдачу информации из .накапливающего сумматора 36 и на второй вход сумматора 33 поступает информация, соответствующая нулю.

После этого на выходе 2 блока 41 появляется задержанный импульс, кото$ рый устанавливает сумматор 31 в нулевое состояние и поступает на первые входы элементов И 42 и 46, считывая информацию из сумматора 33 и регистра 45, который находился в первона0 чальный момент в нулевом состоянии. Информация с выходов обоих регистров параллельным кодом поступает на входы блока 47 сравнения. Если величина, поступившая на вход 2 блока 47 срав5 нения меньше величины, поступившей на вход 1, на выходе блока 47 сравнения появляется сигнал, который поступает на третий вход элемента И 44 и управляющий вход регистра 48, переQ иисывая информацию из счетчика 49 в этот регистр. Появившийся после этого импульс на выходе 3 блока 41 поступает на первый вход элемента И 44 и переписывает информацию из сумматора 33 в регистр 45, а также поступает на вход 3 блока 47 сравнения, устанав-; ливая ее в исходное состояние. После этого импульс с выхода 4 блока 41 поступает на вход счетчика 49 и прибавляется к его младшему разряду., Таким образом, в регистре 45 хранится минимальное на данное время значение Sj , а в регистре 48 -.соответствующее этому значению К. После прихода (К-М)-го импульса по шине К в ре- истре 45 будет храниться минимальное io всем возможным К значение S(t), а в регистре-48 - соответствующее :)той величине значение (К + 1)й импульс, пришедший по шине К, устанавливает ее счетчик 49 в нулевое состояние. Одновременно с этим импульсом на вход 3 блока вычислений по шине i поступает импульс в блок 56 эле- ентов задержки. Через время, необ- одимое для вычисления S,(t), на вы- оде 1 блока 56 появляется импульс, который, поступая на второй вход элемента И 50, считывает хранящееся s регистре 48 значение К ог , которое поступает на выход 3 блока вычислений. Этот же импульс, поступая на второй вход элемента И 52, считывает из регистра 45 значение S(t), кото- Ьое поступает на вход 2 коммутатора 53.. Счетчик 58 номера состояния находится в нулевом состоянии и информа- |Ция с его выхода поступает на выход блока вычислений и на вход 2 коммутатора 55. Импульс с выхода 1 блока 56 поступает на вход 3 коммутатора 53, переключает его вход 2 на выход 4, который соединен с шиной данных (вход 1) блока 54 оперативной памяти (Импульс-, поступивший на вход 3 ком- мутатора 55, переключает его вход 2 на выход, который соединен с адресной шиной (вход 3) блока 54 памяти.

При наличии импульса на управляющей зоне записи (вход 4) блока 54 происходит запись в ячейку с номером состояния i-значения S;(t).

После того, как для всех состояний ,...,W будет определено S(t) и К0птна вход блока вычисления по шине t приходит имлульс, который переводит триггер 57 в единичное состояние и прибавляет единицу в младший разряд счетчика 59 периодов времени 59, Сигнал с выхода триггера 57 поступает на второй вход элемента И 34 снимая запрет на прохождение .информации из сумматора 36 на второй вход сумматора 33.

Коммутатор 53 при отсутствии импульса на его входе 3 находится в положении, при котором его вход 4

5

0

5

скоммутирован с выходом 1. В комму- таторе 55 при отсутствии сигнала на его входе 3 с выходом скоммутирован вход 1.

Счетчик 51 номера состояния в начальный момент времени находится в нулевой состоянии. Первый импульсJ появившийся на шине, поступает на вход 2 управляющей шины считывания блока 54 памяти и считывает из ячейки с нулевым адресом значение S(t). После этого, пройдя через элемент 43 задержки, импульс по шине поступает на вход счетчика номера состояния j 23, прибавляя единицу в его младший разряд, подготавливая тем самым адрес первой ячейки блока 54. Информация, содержащая значение S j(t) с выхода 1 коммутатора 53 поступает на второй вход блока умножения 37, на первый вход которого поступает значение Р f; . Информация с выхода блока 37 умножения , поступает на первый вход сумматора 36. При приходе (W+1)-ro импульса по шине j в сумматоре 36 будет храниться информация, содержащая значение

0

5

0

5

0

5

w

Р Кч Sf(t-1) . Эта информация счиU J

И тается импульсом, пришедшим по шине

К с выхода 1 блока 41 на второй вход элемента И 35 и через элемент И 34 поступает на второй вход сумматора 33. После этого импульсом с шины К, пришедшим с выхода 2 блока 41 на второй вход сумматора 36, он устанавливается в нулевое состояние. В результате для каждого периода времени и номера состояния системы на вход блока вычислений выдается номер оптимального вида технологического обслуживания (К) и минимальные затраты на период времени от данного до конца эксплуатации системы (sf(t)).

Блок управления (фиг.З) работает следующим образом.

При запуске блока управления одно- вибратор (0В) 60 формирует импульс, который поступает на выход 1 блока управления и на вход S триггера 61, переводя его в единичное состояние. Сигнал с выхода триггера 61 поступает на первый вход элемента И 63, разрешая прохождение импульсов с выхода генератора 62 тактовых импульсов, которые поступают на вход элемента И 63. С выхода элемента И 63 импульсы поступают на вход делителя частоты 64.

С выхода делителя частоты 64 импульсы поступают па выход 2 блока управления (шина j) и па вход делителя 65 частоты. После прихода па вход делителя частоты 65 (W-H)-ro импульса на его выходе появляется импулы-, который поступает на выход 3 блока управления (шина К) и на вход делителя 66 частоты. Аналогичным образом импульсы с выхода делителя 66 частоты поступают на выход 4 блока управления (шина i), ас выхода делителя частоты 67 на выход 5 блока управления (шина j) и на вход делителя 68 частоты. После прихода на вход делителя 68 частоты количества импульсов, равного установленному числу периодов контроля, на его выходе появится импупьс, который поступает на R-вход триггера 61 и останавливает блок управления.

Формула изобретения

0

5

0

5

0

входу регистратора, выходы первого блока регистров соединены с инфор- мационными входами третьего коммутатора, выход которого подключен к второму входу первого сумматора, выход которого соединен с входом блока деления, выход первого регистра соединен с первым входом элемента И, выход

Q второго регистра подключен к второму входу первого блока умножения, выход которого соединен с первым входом второго блока умножения, второй вход которого подключен к выходу датчика

j времени, выход третьего регистра соединен с вторым входом третьего сумматора, выход которого подключен к первому входу второго сумматора, выход которого соединен с вторым входом

0 четвертого сумматора, выход которого подключен к первому входу блока вычислений, второй вход которого соединен с пятым выходом блока управления, второй выход которого подключен к

5 четвертому входу блока вычислений и к входу второго счетчика, выход которого соединен с входом второго дешифратора, выходы которого подключены к управляющим входам третьего коммутатора, последний выход второго дешифратора соединен с вторым входом элемента И, выход второго коммутатора подключен к второму входу третьего сумматора, первый выход блока управления соединен с шестым входом блока вычислений и первым входом элемента ИЛИ, выход которого подключен к первому входу блока памяти, выход которого соединен с седьмым входом блока вычислений, третий вход которого подключен к четвертому выходу блока управления и объединен с входом первого счетчика, выход которого соединен с вторым входом блока памяти, третий выход блока управления соединен с вторым входом элемента ИЛИ, пятым входом блока вычислений и входом третьего счетчика, выход которого подключен к третьему входу блока памяти и к входу третьего дешифратора, выходы которого соединены с управляющими входами второго коммутатора.

, блок оперативной памяти, первый второй блоки элементов издержки, первого по четвертый счетчики, элент задержки, триггер, элемент ИЛИ, первого по десятый элементы И, перй вход первого элемента И является рвым входом блока вычислений, входы иггера и четвертого счетчика объедины и являют.ся вторым входом блока числений, вход второго блока эле- нтов задержки является третьим вхо- м блока вычислений, вход элемента держки объединен с вторыми

10

по бл тр от ре ка вт до ро оп ко вы ко вт ро на ро ве со эл к го да ни ме вх И то да су да тр за се бл со И м п р с х ду с эл

входами блока оперативной памяти и первого элемента И и с первым входом пятого элемента И и является четвер- входом блока вычислений; вход первого блока элементов задержки объе с первым входом элемента ИЛИ и является пятым входом блока вычислений, второй вход элемента ИЛИ являет- сЈ шестым входом блока вычислений, первый вход первого регистра является седьмым входом блока вычислений, вЬкод десятого элемента И подключен к второму входу первого коммутатора и является первым выходом блока вычислений, выход третьего счетчика соединен с вторым входом второго коммутатора и- является вторым выходом бЛока вычислений, выход девятого эле- мЈнта И является третьим выходом бло- к4 вычислений, выход четвертого счет- чйка - четвертым выходом блока вычис- , выход первого элемента И подключен к первому входу первого блока умножения, выход которого соединен с первым входом первого накапливающего сумматора, выход которого подключен к первому входу второго элемента И, которого.соедине н с первым вхо- дбм сумматора, выход которого подключен к первым входам шестого и седьмого элементов И, выход последнего из которых соединен с первым входом второго регистра, выход которого подключен к первым входам десятого и восьмого элементов И, выход последнего из которых соединен с первым входом блока сравнения, выход которого подключен к третьему входу седьмого элемента. И и к первому входу третьего регистра, выход которого соединен с- первым входом девятого элемента И, второй вход которого объединен с вторым входом десятого элемента И, третьими входами первого и второго коммутаторов, четвертым входом блока оперативной памяти и

16

5

0

5

0

5

0

5

0

5

подключен к первому выходу второго блока элементов задержки, второй и третий выходы которого соединены соответственно с вторым входом второго регистра и с входом третьего счетчика, выход элемента задержки через второй счетчик соединен с первым входом второго коммутатора, выход которого подключен к третьему входу блока оперативной памяти, первый выход-вход которого соединен с первым входом- выходом первого коммутатора, выход которого подключен к первому входу второго блока умножения, выход которого соединен с первым входом второго накапливающего сумматора, выход которого подключен к первому входу четвертого элемента И, выход которого соединен с первым входом третьего элемента И, выход которого подключен к второму входу сумматора, выход пятого элемента И соединен с вторыми входами первого и второго блоков умножения, первый выход первого блока элементов задержки подключен к вторым входам второго и четвертого элементов И, второй выход первого блока элементов задержки соединен с вторыми входами первого и второго накапливающих сумматоров и подключен к вторым входам шестого и восьмого элементов И, третий выход первого блока элементов задержки подключен к второму входу седьмого элемента И и к третьему входу блока сравнения, второй вход которого соединен с выходом шестого элемента И, четвертый выход первого блока элементов задержки через первый счетчик подключен к второму входу третьего регистра, выход элемента ИЛИ соединен с вторым входом первого регистра, выход которого подключен к второму входу пятого элемента И, выход триггера соединен с вторым входом третьего элемента И.

3„ Устройство по п.1, отличающееся тем, что блок управления содержит одновибратор, RS-триг- гер, генератор тактовых импульсов, элемент И, с первого по пятый делители частоты, выход последнего из которых соединен с R-входом RS-тригге- ра, выход которого подключен к первому входу элемента И, второй вход которого соединен с выходом генератора тактовых импульсов, выход элемента И соединен с входом первого делителя частоты, выход которого является вторым выходом блока управления и соединен с входом второго делителя частоты, выход которого является третьим выходом блока управления и подключен к входу третьего делителя частоты, выход которого является четвертым выходом блока управления и соединен с входом четвертого делителя частоты, выход которого является пятым выходом блока управле - ния и подключен к входу пятого делителя частоты, выход одновибратора соединен с S-входом RS-триггера и является первым выходом блока управления.

Авторы

Даты

1990-06-15—Публикация

1987-12-11—Подача