Изобретение относится к средствам вычислительной техники и может быть использовано при моделировании динамики и управления полетами летательных аппаратов.

Цель изобретения - повышение точности.

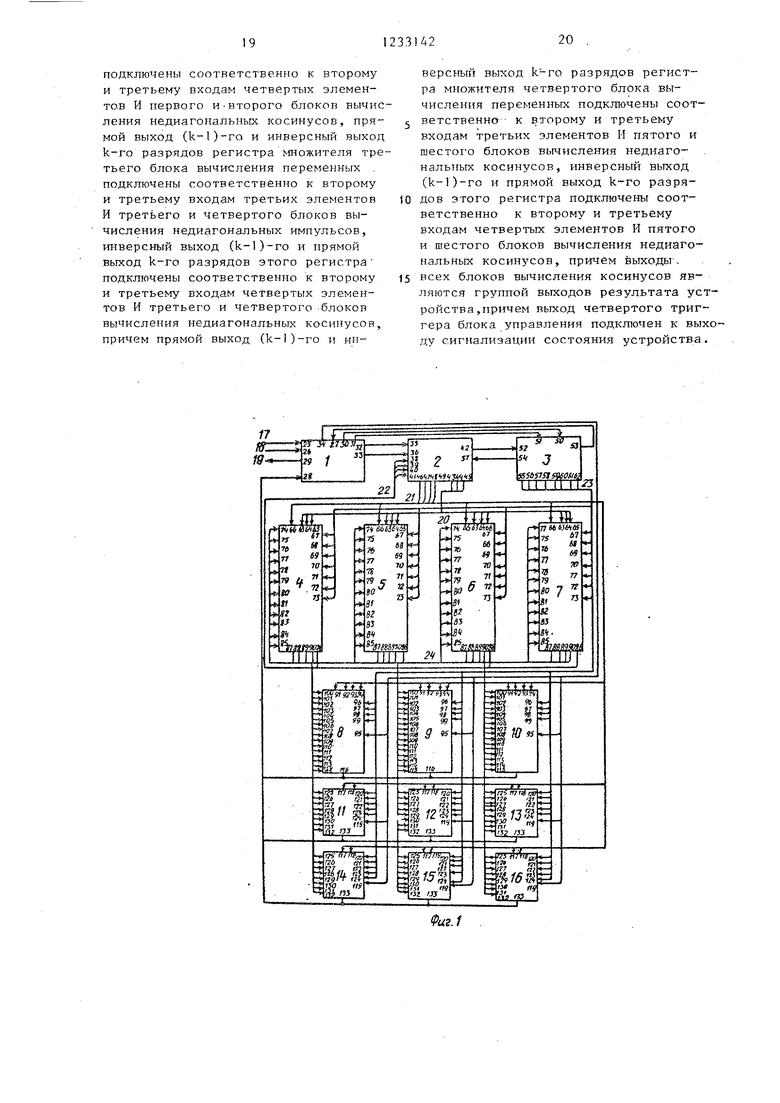

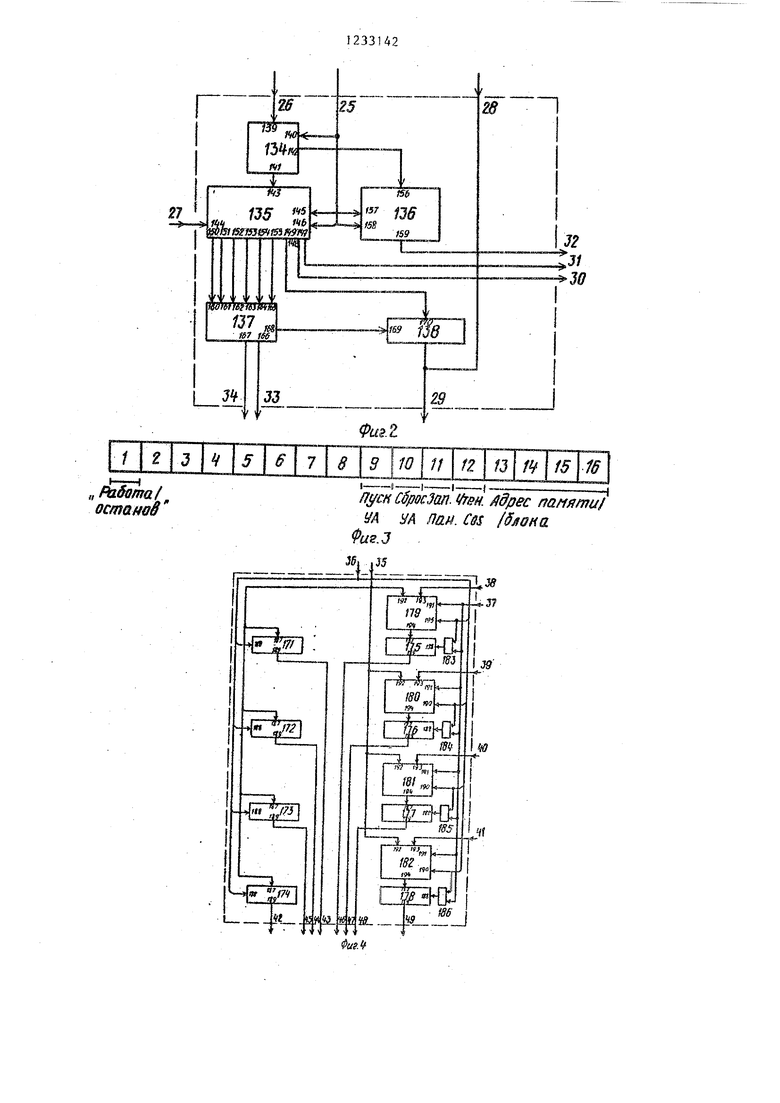

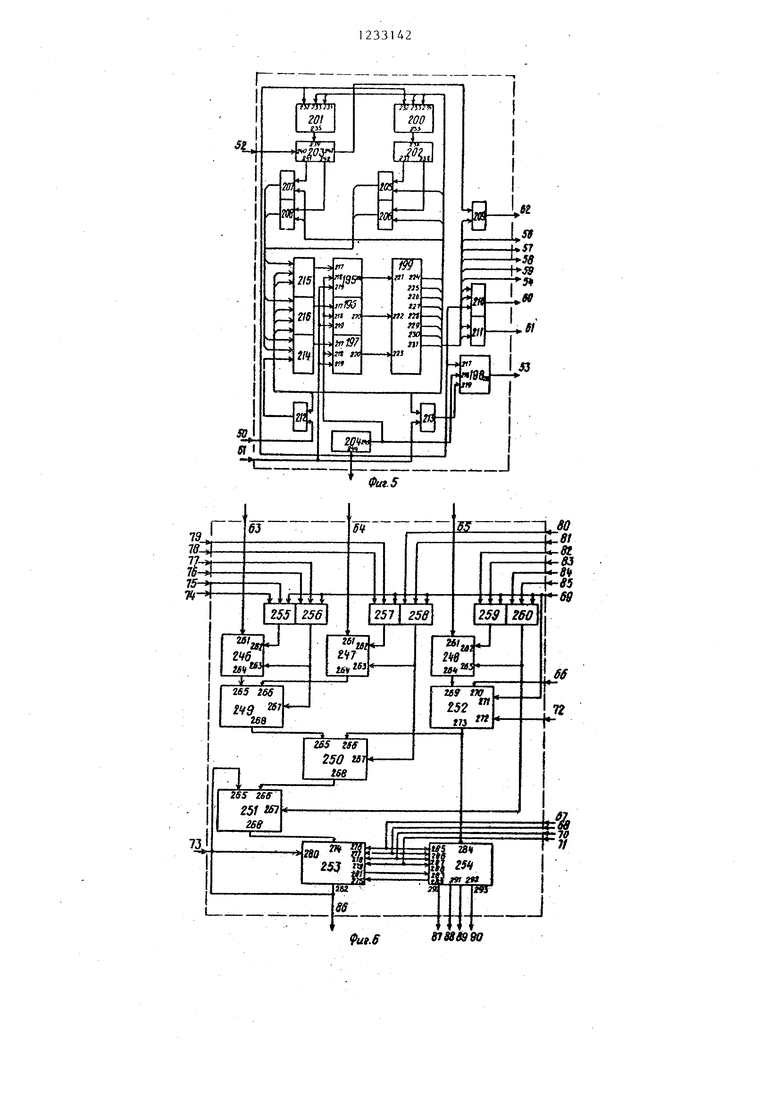

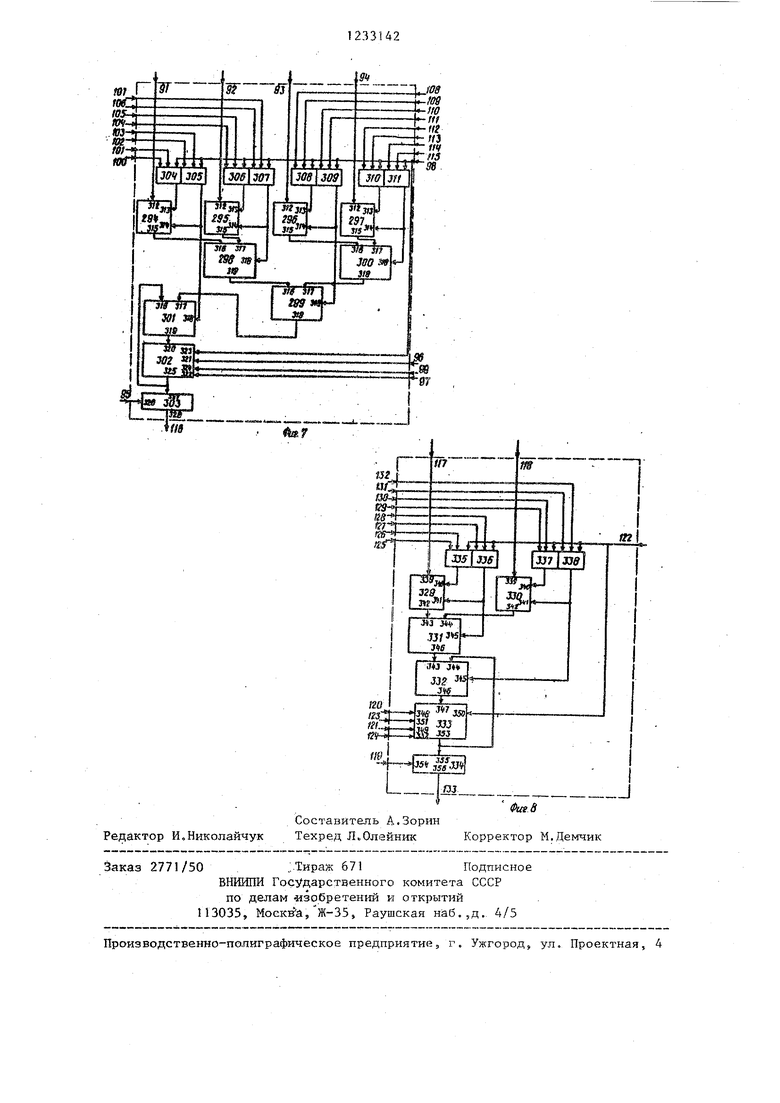

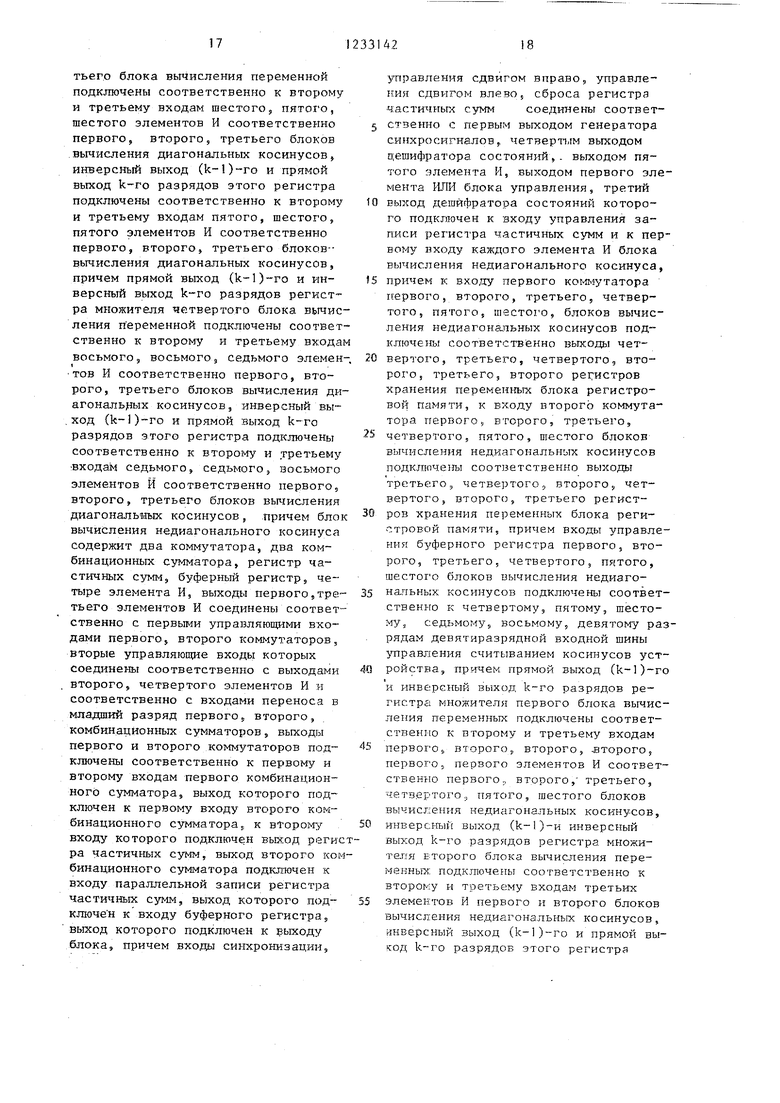

На фиг. 1 представлена блок-схема устройства для вычисления матрицы направляющих косинусов; tia фиг. 2 - блок-схема блока сопряжения; на фиг. 3 - формат команды; на фиг. 4 - блок-схема блока регистровой памяти , на фиг. 5 - блок-схема блока управления} на фиг. 6 - блок-схема блока вы числения переменной , на фиг. 7 - блок-схема блока вычисления диагонального косинуса; на фиг. 8 - блок- схема блока вычисления недиагонального косинуса.

Блок-схема (фиг. 1) содержит блок 1 сопряжения, блок 2-регистровой памяти, блок 3 управления, блоки 4-7 .вычисления переменных, блоки 8-10 вычисления диагональных косинусов, блоки П-16 вычисления недиагональных косинусов, входную управляющую шину 17, входную 18 и выходную 19 информационные шины, шину 20 О), шину 21 выходных }( , шину 2 2 входных А , ШИ.НУ 23 управления, шину 24 условий, первый-четвертый входы 25-28 и пер- вый шестой выходы 29-34 блока 1 сопряжения, первый-седьмой входы 35- 41 и пер вый-восьмой выхода 42-49 блока 2 регистровой памяти, пер- вый-третий входы 50-52 и первый-де- сятый выходы 53-62 блока 3 управле- ния,первый-двадцать третий входы 6385 и первый-пятый выходы 86-90 блока вы , числения переменной Л;,первый-двадцать пятый входы 91-1 5 и выход 116 блока вычисления диагонального косинуса, пер- вый-шестнадцатый входы 117-132 и выход 133 - блока вычисления неди- агонального косинуса. Блок-схема блока I сопряжения (фиг. 2) содержит коммутатор 134, регистр 135 команд, регистр 136 данных, дешифратор 137 вы борки,, буфер- ный регистр 138 с открытым коллектором, информадионный вход 139, управляющий вход 140j| первьш 141 и второй 142 выходы коммутатора, вход 143 параллельной записи во все разряды регистра команд, кроме первого, вход 144 записи в первый разряд регистра команд, вход .145 управления записи регистра команд, вход 146 синхронизации регистра команд, выход 147 девятого разряда регистра команд, выход 148 десятого разряда регистра команд, выход 149 всех разрядов регистра команд, выходы 150-155 одиннадцатого-тестнадцатого разрядов регистра команд, вход 156 1)егистра данных., вход 157 управления записи регистра данных, вход 158 синхронизации регистра данных, выход 159 регистра данных, входы 160-165 и первый-третий выходы 166-168 дешифратора выборки, вход 169 управления буфернО ГО регистра с открытым коллектором и вход 170 буферного регистра с ОТКРЫТЫМ коллектором.

На фиг, 3 представлен формат команды, которая хра11ится в регистре 135 команд. Первый (старший) бит устанавливается по сигналу управляющего устройства из блока 3 управления и означает Работа/останов, содержание разрядов с второго по восьмой несущественно, девятый разряд Пуск запускает управляющий автомат в начальное состояние, одиннадцатый разряд Запись управляет записью в блок 2 регистровой памяти содержимого регистра 136 данных, двенадцатый разряд Чтение управляет считыванием на выходную информационную шину 19 результатов, полученных в одном из блоков П-16 вычисления косинусов, отсутствие активных значений (1) в этих разрядах приводит к счи- гьшанию на шину 19 содержимого регистра 135 команд, тринадцатый, шест- |надцатый разряды которого содержат адрес регистра памяти или блока вы- чиеления косинуса в позиционном коде.

Блок-схема блока 2 регистровой памяти (фиг. 4) содержит регистры 171- 178 для хранения переменных и,, ы , велич:ины Н, переменных , , (l АЗ соответственно, первый-четвертый мультиплексоры 179-182, элементы ИЛИ 183-186, информационный вход 187 регистра, вход 188 управления записи регистра,, выход 189 регистра, первый 190 и второй 19; управляющие входы мультиплексора, первый 92 и второй 193 иргформадионный входр и выход 194 мультиплексора.

Блок-схема блока 3 управления (фиг. 5) содержит первый-четвертый Е -триггеры 195-198, дешифратор 199 состояний, счетчик 200 тактов умно3

жеиия, счетчик 201 числа сдвигов, дешифратор 202 окончания умножения, дешифратор 203 сдвигов, генератор 204 синхросигналов, элементь И 205- 209, дешифратор 210 сигнала Запись элемент ИЛИ 211, элемент И 212, элементы ИЛИ 213-2 16,3)-вход 217 триггера, С-вход 218 триггера, вход 219 сброса триггера, выход 220 триггера первый-третий входные разряды 221- 223 дешифратора состояний (первый - младший разряд), первый-восьмой выходные разряды 224-231 дешифратора состояний (первый - младший разряд) вход 232 синхронизации счетчика, выход 233 сброса счетчика, вход +1 234 счетчика, выход 235 счетчика, вход 236 и прямой 237 и инверсный 238 выходы дешифратора окончания умножения, вход 239, второй вход 240, первые прямой 241 и инверсный 242 выходы и второй прямой выход 243 дешифратора 203 сдвигов, первый 244 и второй 245 выходы генератора 204 синхросигналов.

Блок вычислершя переменной (фиг.6 содержит коммутаторы 246-248, первый-третий комбинационные сумматоры 249-251, мультиплексор 252, регистр 253 частичных сумм, регистр 254 множителя, элементы И 255-260, информационный вход 261, первый 262 и второй 263 управляющие входы и выход 264 коммутатора, входы 265 и

266комбинационного сумматора, вход

267переноса в кшадший разряд комбинационного сумматора, выход 268 комбинационного сумматора, первый 269 и второй 270 информационные входы, первый 271 и второй 272 управляющие входы и выход 273 мультиплексора вход 274 параллельной записи, вход 275 сдвига влево и вход 276 синхронизации регистра частичн-ьгх сумм,

входы 277-280 управления сбросом, сдвигом вправо, сдвигом влево и записи регистра соответственно, выход

281 сдвига вправо этого регистра, I

выход 282 регистра частичных сумм, вход 283 сдвига вправо регистра мно- жителя, вход 284 параллельной записи во все разряды, кроме младшего, и вход 285 синхронизации этого регистра, входы 286-288 управления записи во все разряды, кроме млад- шего, и сброса младшего, сдвига вправо и сдвига влево соответственно регистра, вьшод 289 сдвига влево ре

5 Ю 15 20 25

о

г

0 5

5

424

гистра, прямой 290 и инверсный 291 выходы предпоследнего разряда регистра множителя, прямой 292 и инверсный 293 выходы последнего (младшего) разряда регистра множителя.

Блок-схема блока вычисления диагонального косинуса (фиг. 7) содержит первый-четвертый коммутаторы 294-297, первый-четвертый комбинационные сумматоры 298-301, регистр

302частичных сумм, буферный регистр

303с открытым коллектором, элементы И 304-311, информационный вход 312

и первый 313 и второй 314 управляющие входы коммутатора, выход 3I5 формирователя,входы 316 и 317 комбинационного сумматора, вход 318 пере-. носа в младший разряд комбинационного сумматора, выход 319 сумматора, вход 320 параллельной записи в регистр частичных сумм, вход 321 синх- ронизацрш этого регистра, входы 322- 324 соответственно управления сбросом, записью и сдвигом вправо регистра частичных сумм, выход 325 этого регистра, вход 326 управления буферным регистром с открытым коллектором, информационный вход 327 и выход 328 буферного регистра.

Блок-схема блока вычисления недиагонального косинуса (фиг. 8) содержит первый 329 и второй 330 коммутаторы, первый 331 и второй

332комбинационные сумматоры, регистр

333частичных сумм, буферный регистр

334с открь тым коллектором, элементы И 335-338, информационный вход 339, первый 340 и второй 341 управляющие входы и выход 342 коммутатора, входы 343 и 344 комбинационного сумматора, вход 345 переноса в младший разряд сумматора, выход 346 сумматора, вход 347 параллельной записи регистра частичных сумм, вход 348 синхронизации регистра, входы 349- 352 соответственно управления сбро-, сом, записи, сдвигом вправо и сдвигом влево регистра, выход 353 .регистра, вход 354 управления, информационный вход 355 и вьпсод 356 буферного регистра.

Устройство работает следующим образом.

Матрица направляющих косинусов вычисляется через параметры Родрига- Гамильтона:

, J

C,,( Лo, , Ла)

C,2t- A, Aa -A.lO C,r2(,i A, J-,

)l 11 )

(-АЛ, . C,, 2U,, С,(- Х,0,4 Л КОс,..

Параметры Родрига-Гамильтона связаны между .собой системой дифференциальных уравнений:

(,. + )/2

1 (,,)l il , A,-tO,,)|2

(w, c0.j,,-co,.,)/2.

Для .определения в момент времени t требуется значение переменных СО в момент времени t и начальных значений переменных Л; в момент времени .

Для решения систем(1 используется алгоритм Эйлера,, где

A(t)ft«()+H Ao-, X,(t)- A., , H(t) ), A,(t).()+H A3}

„ I при этом и - mar интегрирования, a

; определяется из системы уравнений, н выбирается в виде числа, равного 2 J когда 3 -1ножение на Н сводится к сдвигу на определенное число разрядов. Так как при умножении Ui Л; результат. находится в регистре множителя 5 то для объединения выравнивания результата с умножением на н 2 используется эквивалентный сдвиг влево на величину.n-k-, где п - разрядность представления инфор- , нации.

Работа устройства протекает в несколько этапов: загрузка начальных значений переменных -Я- в регистры блока 2 регистровой памяти из внешней вычислительной системы перед началом численного интегрирования, загрузка величины Н и переменных 03j в регистры блока 2 регистровой памяти и вывод из устройства через блок 1 . сопряжения вычисленной матрицы направляющих косинусов

Запись данных в регистры блока 2 регистровой памяти из внешней вычислительной системы и считывание косинусов управляются блоком I: сопряжения, а ход вычислений - блоком 3 управления . Блок 1 сопряжения управляет работой блока 3 управления, переводя управляюсгий автомат в на- 5 чальное состояние, выдав сигнал на выход 31 б.пока 1 сопряжения, и запуская управляющий автомат, выдав сигнал запуска на выход 30 блока 1 сопряжения.

10 Для выполнения действий на первом этапе внешняя вычислительная система выдает на первьш и второй разряды втравляющей шины 17 сигналы и команду записи переменной Лц в регистр

15 176 для хранения переменной . Эта команда пропускается коммутатором 134 на выход 14 и по синхроимпульсу на четвертом разряде шины 17 запи-- сывается в регистр 135 команд. За20 тем внешняя вычислительная система выдает сигнал на третий разряд ШИРШ 17, сняв сигнапы с первых двух разрядов этой шин1з, и выдает информацию переменную .о ка входную информаци5 онную шину 18. Эта информация пропускается коммутатором 134 на выход 142 и по синхросигналу записывается в регистр 136 данных. Разряды регистра 135 команд дешифрируются дешифра01 тором 137 выборки и в соответствующем разряде выхода 166 этого дешифратора появляется сигнал выборки, который с выхода 33 блока 1 сопряжения поступает па вход 36 блока 2

5 регистровой памяти в соответствующий разряд, подключенный к входу 191 мультиплексора 179 и через элемент ИЛИ 183 к входу 188 управления записи регистра 175 для хранения переменной.

0 Информация с выхода 32 блока сопряжения передается с входа 193 мультиплексора 179 на выход 194 и записывается Е регистр 175. Аналогично TI 1 записывается в регистр 176, - 5 в регистр 177., А - в регистр 178. Сначала в регистр 135 команд записывается соответствующая команда, затем в регистр 136 данных - данное, . а затем опо переписывается в соот0 ветствуюпщй ему регистр в блоке 2 регистровой памяти.

Выполнение действий на втором этапе аналогично, однако в командах выдается сигнал Сброс. В результа- . те Б регистре 171 записана переменная «i, в регистре 172 - ад , в регистре 174 - величина Н, в регистре

73

со,

На третьем этапе внешняя вычислительная система записывает в регистр 138 команду, содержащую сигнал Пуск. На предыдущем этапе управля- ющий автомат переведен в исходное состояние (триггеры 195-198 обнулены сигналом сброса на входе 51 блока 3.управления, поступившим с выхода 31 блока i сопряжения, на пер- вом выходном разряде 224 дегяифратора 199 состояний появился сигнал). Теперь, при переходе управляющего автомата в следующее состояние., в устанавливается триггер 198, что при водит к установленю в 1 первого разряда регистра 135 команд сигналом на входе 27 блока 1 сопряжения, к сбросу счетчиков 200 и 201 в блоке 3 управления. На выходах 56 и 61 блока 3 управления появляются управляющие сигналы, по которьм мультиплесоры 252 в блоках 4-7 пропускают значения переменных Я; с выходов 86 этих блоков, которые поступили через шину 21 выходных с выходов 46-49 блока 2 регистровой памяти. Эти данные записываются во все разряды, кроме младшего, в регистры 254 множителя. Регистры 253, 302 и 333 частичных сумм в блоках 4-16 и младший разряд регистров 254 в блоках 4-7 обнуляются.

В следующем такте работы управляющего автомата сигналы присутствуют на выходах 57 и 60 блока 3. Через шину 23 управления они поступают в блоки 4-16, где на входы элементов И 255-260 в блоках 4-7, входы элементов И 304-311 в блоках 8-10 и вхо дь элементов И 335-338 в блоках 11- 16 через шину 24 условий поступают значения двух младших разрядов регистров 254 множителя в парафазном коде с выходов 87-90 блоков 4-7. Управляющие сигналы элементов И используются для получения произведений в регистрах 253 частичных сумм в блоках 4-7, регистрах 302 в блоках 8-10 и регистрах 333 в блоках 11-16. Блоки 4-16 построены так, что при изменении младших разрядов множителя из 1 в О множимое с входов 63-г65 в блоках 4-7, входов 91-94

esf .

В блоках 8-10 и входов 117 и 118 в блоках 11-16 проходит через соответствующие коммутаторы бе.з изменений, при изменении младших разрядов из

5

5 10 5 20 0

5 0 5 0

О в 1 входной код инвертируется на соответствующем коммутаторе и поступает на сумматор, а на вход переноса в 4ладший разряд соответственно сзт матора поступает 1, что эквивалентно вычитанию множимого. Управление коммутаторами осуществляется соответствующими элементами И, сложение множимого с частичной суммой обеспечивается сигналом с выхода соответствующего нечетного элемента, а вычитание - с выхода соответствующего четного элемента, если младшие разряды множителей равны, то сигналы на выходе соответствующих элементов И отсутствуют и на выходе ком- ryтaтopa появляется нулевой код. После выполнения описанных действий данные складываются на комбинационных сумматорах и записываются в регистры частичных сумм.

Выход счетчика 200 тактов умножения, дешифрируется дешифратором 202 окончания умножения. Если умножение окончено, дешифратор выдает сигнал на выходе 237, а если нет - на выходе 238, В этом случае в следующем такте работы управляющего автомата на выходе 58 блока 3 появляется управляющий сигнал, по которому во всех регистрах блоков 4-16 происходит модифицированный сдвиг вправо, причем младший разряд регистра 253 с выхода 281 передается на вход 283 регистра 254. Счетчик 200 увеличивается на единицу. После этого управляющий автомат возвращается в преды-iv дущее состояние и описанные действия повторяются, пока не возникнет сигнал на выходе .237 дешифратора 202. Тогда управляющий автомат переходит в следующее состояние, где счетчик 201 числа сдвигов увеличивается на единицу, а в блоках 4-7 и 11-16 происходит сдвиг регистров на один разряд влево, так как на их управляющие входы поступают сигналы управления с выходов 59 и 62 блока 3. Старший разряд регистра 254 с выхода 289 поступает на вход 275 регистра 253. В этом такте сигналы с выхода 235 счетчика 201 поступают на вход 239 дешифратора 203, где они сравниваются с величиной Н, поступившей на вход 240 дешифратора 203 с входа 52 блока 3 из блока 2 регистровой памяти. Если на выходе 243

дешифратора 203 появится сигнал, свидетельствующий о равенстве, то управляющий автомат в следующем такте переходит в следующее состояние, если нет, то остается в этом, но сигнал с выхода 62 блока 3 сн -1мается так как изменилось состояние счетчика 201 и исчез сигнал с выхода 243 дешифратора 203. Таким образом, про- исходит сдвиг влево Н раз в блоках 4-7., одип раз в блоках , что эквивалентно y нoжeнию чисел на Н в блоках 4-7 и умножению на два суммы произведений в блоках 11-16.

В следующем состоянии управляющего автомата сигналы присутствуют на выходах 60- и. 61 блока 3. По этим сигналам в блоках 4-7 происходит пропуск переменной из регистров бло- ка 2 через мультиплексор 252 на сумматор 250 и сложение этого числа с содержимым регистра 253 частичной суммы с последующей записью результата в этот регистр.В следующем состоянии управляюще- то автомата сигнал присутствует на выходе 64 блока 3. По 3TONry сигн;1лу мультиплексоры 179-182 в блоке 2 пропускают на выходы информацию с вхо- дов 38-41 блока 2, куда через шину 22 входных 7, подключены выходы 86 блоков 4-7 соответственно. На входы управления записи регистров 175-178 через элементы ИЛИ 18,3-186 поступа- ет сигнал с выхода 54 блока 3 через вход 37 блока 2 и осуществляется параллельная запись в регистры 175- 178 значений, вычисленных на данном шаге и содержащихся в регистрах ча- стичных сумм блоков 4-7, В блоке 3 сбрасывается триггер 198, что приводит к обнулению первого разряда регистра 35 команд. Команда запуска сним ается внешней вычислительной системой во время рабО1Ъ1 устройства К концу третьего этапа в регистрах блоков 8-16 находятся направляющие косину е.ы, а в регистрах блока 2 - вычисленные значения il; .

Во время вычислений.внещняя вы- числительная система вьщает команду чтения регистра команд,, что приводит к тому, что на вькоде 168 деширатора 137 выборки возникает сигнал который переводит буферный регистр 138 с открытым коллектором в активное состояние. Тогда на выходной информационной типе 19 присутствует информация из регистра команд. По заверщению вычислений изменяется состояние первого бита регистра команд, что сигнализирует о возможности ввода косинусов. Выходы регистров в блоках 8-16 подключены к буферт гм регистрам с открытьгм коллектором, которые поразрядно подключены к входу 28 блока и являются выходом 29 этого же блока.

На четвертом этапе внешняя вычислительная система выводит из устройства вычисленные значения косинусов, для чего выдает предварительно команду чтения косинуса с соответствующим адресом. Активизируется буферный регистр с открытым коллектором, подсоединенный к соответствующему разряду выхода 167 дешифратора 137 выборки блока I ,, и информация вводится во внеишюю вычислительную систему .

После ввода косинусов устройство по команде внешней вычислительной системы продолжает работать либо с первого, либо с второго этапа, используя в последнем случае в качестве начальньк значений значения, вычисленные на предыдущем шаге в третьем этапе.

Формула изобретения

Устройство для вычисления матрицы направляющих косинусов,, содержащее блок регистровой памяти, блок управления, отличающееся тем, что 5 с целью повьгаения точности,- в него введены четыре блока вы- чксле ия переменных 5 три блока вычисления диагоггальных косинусов, шесть блоков вычисления недиагональных ко- синусоз, причем блок регистровой памяти содержит регистр хранения величнны цага, три регистра хранения значений угловых скоростей, четыре регистра хранения перемен1а х, четыре мультиплексора,, выходы которых соеди нены с информационными входами регистров храи:ения переме шых,, причем ипформационмый вход устройства под- к,пючен к информационным входам регисров хранения значений угловых скоростей и. величины шага и к первым информационным входам мультиплексоров, первые четыре разряда входа управления приемом данных устройства подключены соответственно к входам упраления записью первого, второго, третьего регистров хранения значений угловых скоростей и регистра хранени величины шаГа, а последние четыре разряда подключены соответственно к первым управляющим йхрдам первого, второго, третьего, четвертого нуль- типлексоров и соответственно к первы входам первого, второго, третьего, четвертого элементов ИЛИ, выходы которых подключены соответственно к управляющим входам записи первого, второго, третьего, четвертого регистров хранения переменных, причем блок управления содержит четыре триггера, дешифратор состояний, счетчик тактов умножения, счетчик числа сдви- гов, дешифратор окончания умножения, дешифратор сдвигов, генератор синх росигналов, шесть элементов И, пять элементов ИЛИ и дешифратор записи, причем выходы первого, второго, тре- тьего триггеров соединены с входами дешифратора состояний, первый выход которого соединен с входами установки в нулевое состояние счетчика тактов умножения и счетчика числа сдви- гов, счетные входы которых соединены соответственно с четвертым и пятым выходами дешифратора состояний, входы синхронизации счетчика, числа сдвигов и счетчика тактов умножения подключены к первому выходу генератора синхросигналов, выходы счетчика тактов умножения и счетчика числа сдвигов подключены соответственно к входу дешифратора окончания умноже- ния и первой группе входов дешифратора сдвигов, вторая группа входов которого соединена с разрядными выходами регистра хранения величины шага блока регистровой памяти., пря- мой и инверсный выходы дешифратора окончания умножения подключены соответственно к первым входам первого и второго элементов И, к вторым входам которых подключен третий выход дешифратора состояний, первые прямой и инверсный .выходы дешифратора сдвигов соединены .соответственно с пе.р выми входами третьего и четвертого элементов И, вторые входы которых соединены с пятым выходом дешифратора состояний, третий и шестой выходы которого подключены соответственно к

первому и второму входам.дешифратора записи, третий вход которого соединен с первым выходом генератора синхросигналов, пятый выход дешифратора состояний подключен к первому входу пятого элемента И, к второму входу которого подключен второй прямой выход дешифратора сдвигов, второ выход дешифратора состояний подключен к информационному входу четвертого триггера и первому входу первого элемента ИЛИ, к второму входу которого подключен шестой выход дешифратора состояний, седьмой выход которого соединен с первым входом второго элемента ИЛИ, второй вход которого является входом установки устройства в начальное состояние, выход второго элемента ИЛИ соединен с входом установки в нулевое состояние четвертого триггера, вход запуска устройства соединен с первым входом шестого элемента И, второй вход которого соединен с первым выходом дешифратора состояний, а выход шестого элемента И подключен к первому входу третьего элемента ИЛИ, второй и третий входы которого, соединены соответственно с выходами второго и третьего элементов И, выход третьего элемента ИЛИ соединен с информационным входом третьего триггера, выходы четвертого и пятого элементов ИЛИ соединены соответственно с информационньми входами первого и второго триггеров, первый, второй и третий входы четвертого элемента ИЛИ соединены с выходами соответственно первого элемента И, пятым и шестым выходами дешифратора состояний, второй, третий и шестой выходы которого и выход второго элемента И подключены соответственно к первому, второму, третьему и четвертому входам пятого элемента ИЛИ, входы синхронизации триггеров соединены с вторым выходом генератора синхросигналов, причем входы установки в нулевое состояние первого, второго, третьего триггеров соеди-- нены с входом установки устройства

в начальное состояние, седьмой выход дешифратора состояний подключен к вторым управлякяцим входам мультиплексоров и элементов ИЛИ блока регистровой памяти, прнчем блок вычисления переменной содержит три ком мутатора, три комбинационных сумматора, регистр частичных сумм, регис множителя, мультиплексор и шесть элементов И, выходы первого, третьего, пятого элементов И соединены с первыми управляющими входами соответственно первого, второго, третьего коммутаторов, вторые управляюпще входы которых соединены соответственно с выходами второго, четверто- го, шестого элементов И и соответственно с входами переноса в младший разряд первого, второго, третьего комбинационных сумматоров, первый и второй входы первого комби национного сумматора соединены соответственно с выходами первого и второго коммутаторов, выход третье Го коммутатора подключен к первому информационному входу мультиплексо- ра, выход которого соединен с первым входом второго комбинационного сумматора и с входом параллельной

записи во все разряда:, кроме младшего регистра множителя, второй вхо второго комбинационного, сумматора соединен с выходом первого комбинационного сумматора, выход второго комбинационного сумматора соединен с первым входом третьего комбинацио ного сумматора, второй вход которого соединен с выходом регистра частичных сумм, выход третьего комбинационного сумматора подключен к входу параллельной записи регистра частичных сумм, выход сдвига вправо которого соединен с входом сдвига вправо регистра множителя, выход сдвига влево которого соединен с вхдом сдвига влево регистра частичньк сумм, причем входы синхронизации,, управления сдвигом вправо, управления сдвигом влево обоих регистров подключены.соответственно к первому выходу генератора синхросигналов четвертому и пятому выходам дешифратора состояний блока управления,входы сброса регистра частичных сумм и сброса последнего разряда и параллельной записи во все разряды, кро- ме последнего, регистра множите- ля подключены к выходу первого эле- мента ИЛИ блока управления, вход управления параллельной записи регистра частичных сумм соединен с выходо дешифратора записи блока управления первый управляющий вход мультиплексра и первые входы каждого элемента

И блока вычисления переменной соединены с третьим выходом дешифратора состояний блока управления, второй управляющий вход мультиплексора подключен к второму выходу дешифратора состояний блока управления, причем информационные входы первого, второго , третьего коммутаторов соединены соответственно с выходами первого, второго, третьего регистров хранения значений угловых скоростей блока регистровой памяти, выходы первого, второго, третьего, четвертого регистров хранения переменньгх блока регистровой памяти подключены к вторым информационным входам мультиплексоров соответственно первого, второго, третьего четвертого блоков вычисления переменных, а выходы регистров частичных сумм первого, второго, третьего, четвертого блоков вычисления переменной подключены соответственно к вторым информационным входам первого., второго, третьего, четвертого мультиплексоров в блоке регистровой памяти, причем прямой выход k и инверсный выход k-i разрядов регистра множителя (k - разрядность множнт гля первого блока вычисления переменных) подключены соответственно к второму и третьему входам второго, четвертого, шестого элементов И соответственно второго, третьего, четвертого блоков вычисления переменных, инверсный выход k-ro и прямой выход (k-t)-го разрядов регистра множителя первого блока вычисления переменных подключены соответственно к второму и третьему входам первого, третьего, пятого элементов И соответственно второго, третьего, четвертого блоков, причем прямой выход k-ro и инверсный выход (k- -1)-го разрядов регистра, множителя второго блока вычисления переменных подключены соответстзенно- к второму и третьему входам первого, пятого, четвертого элементов И соответственно первого5 третьего, четвертого блоков вычисления переменньгх, инверсный выход и прямой выход (k-Ij-ro разрядов этого регистра подключены Соответственно к второму и третьему входам третьего., шестого, первого элементов И соответственно первого, второго, четвертого блоков вычислени переменных, инверсный выход k-ro и

прямой выход (k-)-.ro разрядов этого регистра подключены соответственно к BTopobfy и третьему входам четвертого, пятого, второго элементов И со- ответственно первого, второго, четвертого блоков вычисления перемен- ньгк, причем прямой выход k-ro и ин- версньш выход (k-l)-ro разрядов регистра множителя четвертого блока вы числения переменных подключены соответственно к второму и третьему входам пятого, третьего, второго элементов И соответственно первого, второго, третьего блоков вычисления переменных, инверсьгый выход k-ro и прямой выход (k-l)-ro разрядов этого регистра подключены соответственно к второму и третьему входам шестого, четвертого, первого элементов

И соответственно первого, второго, третьего блоков вычисления переменных, причем блок вычисления диагонального косинуса содержит четыре коммутатора, четыре комбинационных сумматора, регистр частичных сумм, буферньй регистр, восемь элементов И, выходы первого, третьего, пятого седьмого элементов И соединены с первыми управляющими входами соответственно первого, второго, третьего, четвертого коммутаторов, вторые управляющие входы которых соединены cooTBeTCTBeftHo с выходами второго, четвертого, шестого, восьмого эле- ментов И и соответственно с входами переноса в младший разряд первого, второго, третьего, четвертого комбинационных сумматоров, первый и второй входы первого комбинационного сумматора соединены соответственно с выходами первого и второго коммутаторов, выход первого комбинационного су матора подключен к первому,.входу второго комбинационного сумматора,к второму входу которого подключен выход третьего комбинационного сумматора, к первому и второму входам которого подключены соответственно выходы третьего и четвертого коммута торов, к первому и второму входам четвертого комбинационного сумматора подключены соответственно выходы.регистра, частичных сумм и третьего комбинационного сумматора, выход чет- вертого комбинационного сумматора подключен к входу параллельной записи регистра частичных сумм, выход 5 О

0

5

0

которого подключен к входу буферного регистра, выход которого соединен с выходом блока, причем входы синх- рониэа1дии, управления сдвигом вправо, сброса регистра част1гчньгх сумм соединены соответственнос первым выходом генератора синхросигналов, выходом четвертого разряда дешифратора состояний, выходом первого элемента ИЛИ блока управления, третий выход дешифратора состояния -которого подключен к входу управления ,записи регистра частичных сумм и первым входам всех элементов И блока вычисления диагонального косинуса, причем к входам первого, второго, третьего и четвертого коммутаторов блока вычисления диагонального косинуса подключены соответственно выходы первого, второго, третьего, четвертого регистров хранения переменных блока регистровой памяти, входы управления буфер№1х первого, второго, третьего регистров блоков вычисления диагональных косинусов подключены соответственно к первому, втором и третье - му разрядам девятиразрядной входной шины управления считыванием косинусов устройства, причем прямой выход предпоследнего и инверсный выход последнего разрядов регистра множителя первого блока вычисления переменных подключен соответственно к второму и третьему входам первых элементов И каждого блока вычисления диагональных косинусов, инверсный выход (k- -i)-ro и прямой выход k-ro разрядов этого регистра подключены соответственно к второму и третьему входам вторых элементов И каждого блока вычисления диагонального косинуса,причем прямой выход (k-l)-ro и инверсный выход k-ro разрядов регистра множителя второго блока вычисления переменных подключены соответственно к второму и третьему входам третьего, четвертого, четвертого элементов И соответственно первого, второго, третьего блоков вычисления диагональных косинусов, инверсный выход (k- -1)-го и прямой выход k-ro разрядов этого регистра подключены соответственно к второму и третьему входам четвертого, третьего блоков вычисления диагональных косинусов, прямой выход (k-l)-ro и инверсный выход k-ro разрядов регистра множителя третьег.о блока вычисления переменной подключены соответственно к второму и третьему входам шестого, пятого, шестого элементов И соответственно первогоJ второго, третьего блоков

.вычисления диагональных косинусов, инверсный выход (k-)ro и прямой выход k-ro разрядов этого регистра подключены соответственно к второму и третьему входам пятого, шестого, пятого элементов И соответственно первого, второго, третьего блоков-- вычисления диагональных косинусов, причем прямой выход (k-l)-ro и ин версный выход k-ro разрядов регистра множителя четвертого блока вычисления Переменной подключены соответственно к второму и третьему входа восьмого, восьмого, седьмого элемен

тов И соответственно первого, второго, третьего блоков вычисления ди агональэых косинусов, инверсный вы, ход (k-l) и прямой выход разрядов этого регистра подключены соответственно к второму и третьему входам седьмого, седьмого, восьмого элементов И соответственно первого, второго, третьего блоков вычисления диагональных косинусов, .причем блок вычисления недиагонального косинуса содержит два коммутатора, два комбинационных сумматора, регистр частичных сумм, буферный регистр, четыре элемента И, выходы первого,тре- тьего элементов И соединены соответственно с первыми управляющими входами первого, второго коммутаторов, вторые управляющие входы которых соединены соответственно с выходами второго, четвертого элементов И и соответственно с входами переноса в младший разряд первого,, второго, комбин.ационных сумматоров, выходы первого и второго коммутаторов под- ключены соответственно к первому и второму входам первого комбинацион-- ного сумматора, выход которого подключен к первому входу второго комбинационного сумма тора J к втором входу которого подкЛ оч€ Н вькод регисра частичных сумм, вьгхоД второго комбинационного сумматора подюшчен к входу параллельной записи регистра частичных сумм, выход которого под- ключе н к входу буферного регистра,

выход которого подключен к выходу блока, причем входы синхронизации.

управления сдвигом вправо, управления сдвигом влево, сброса регистра частичньк сумм соединены соответ- стзешго с первым выходом генератора синхросигналов,, четверт1лм выходом дешифратора состояний,. выходом пятого элемента И, выходом первого элемента ИЛИ блока управления, третий Еыход дешифратора состояний которого подключен к входу управления записи регистра частичных сумм и к первому лходу каждого элемента И блока вычисления недиагонального косинуса, причем к входу первого коммутатора первого, второго, третьего, четвертого, пятого, шестого, блоков вычисления недиагональных косинусов под- ключегш соответствЁнно выходы четвертого, третьего, четвертого, второго, третьего, второго ре1:истров хранения переменных блока регистровой памяти, к входу второго коммутатора ггервого,, второго, третьего, четвертого, пятого, шестого блоков вычисления недиагональных косинусов подключены соответственно выходы третьего,, четвертого, второго., четвертого, второго, третьего регистров хранения переме 1ных блока регистровой памяти, причем входы управления буферного регистра первого, второго, третьего, четвертого, пятого, шестог о блоков вычисления недиаго- напьньж косинусов подключены соответ ствен1-го к четвертому, пятому, шестому, седьмому, восьмому, девятому рарядам девятиразрядной входной шины управления считыванием косинусов устройства, причем прямой выход (k-l)-r и инверсный выход разрядов регистра множителя первого блока вычисления переменных подключены соответственно к второму и третьему входам первог о,, второго, второго, второго, первог о 5 первого элементов И соответственно первого., второго, третьего, четз.ертого,, пятого, шестого блоков вычисления недиагональных косинусов, инверсьгый выход (k-l)-H инверсный выход k-ro разрядов регистра множи- те.г.я второго блока вычисления переменных подключены соответственно к второму и третьему входам третьих элементов И первого и второго блоков вычисления недиагональных косинусов, инверсный выход (k-l)--ro и прямой вы к;од k-ro разрядов этого регистра

подключены соответственьш к второму и третьему входам четвертых элемен- то.в И первого и-второго блоков вычисления недиагоиальньк косинусов, прямой выход (k-l)-ro и инверсный выход k-ro разрядов регистра множителя третьего блока вычисления переменных , подключены соответственно к второму и третьему входам третьих элементов И третьего и четвертого блоков вычисления недиагональных импульсов, инверсный выход (k-l)-ro и прямой выход k-ro разрядов этого регистра подключены соответственно к второму и третьему входам четвертых элементов И третьего и четвертого блоков вычисления недиагональных косинусов, причем прямой выход (k-l)-ro и инверсный выход k-ro разрядов регистра множителя четвертого блока вычисления переменных подключены соот- ветственно к второму и третьему входам третьих элементов И пятого и шестог о блоков вычисления недиагональных косинусов, инверсный выход (k-)-ro и прямой выход разряДОН этого регистра подключены соответственно к второму и третьему входам четвертых элементов И пятого и tttecToro блоков вычисления недиагональных косинусов, причем выходыч

всех блоков вычисления косинусов являются группой выходов результата устройства, причем выход четвертого триггера блока управления подключен к выходу сигнализации состояния устройства.

1

0ta.5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления выражения вида @ | 1989 |

|

SU1644135A1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

| Вычислительное устройство | 1984 |

|

SU1180883A1 |

| Программируемый цифровой фильтр | 1986 |

|

SU1374244A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Устройство для умножения | 1981 |

|

SU1013946A1 |

| Вычислительное устройство | 1985 |

|

SU1269124A1 |

| Устройство для реализации двухмерного быстрого преобразования Фурье | 1982 |

|

SU1164730A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

Устройство относится к средствам вычислительной техники и может быть использовано при моделировании динамики и управления полетами летательных аппаратов. Цель изобретения - повышение точности. Устройство содержит блок сопряжения, блок регистровой памяти, блок устройства управления, четыре блока вычисления переменшях Хд , 7 , Лг , Лз соответственно, три блока вычисления диагональных косинусов С„, Cjj, €53 СООТ ветственно и шесть блоков вычисления недиагональных косинусов С,, С,, С, C,zj, С„, С,2соответственно. 8 ил. с S

.6

stsiiaso

2771/50

.Мираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам «зобретений и открытий П3035, Моекна, ж-35, Раушская наб..,д., 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Патент США № 3975625, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Патент США № 3763358, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

Авторы

Даты

1986-05-23—Публикация

1983-12-20—Подача