Изобретение относится к измерительной технике и может быть использовано для измерения коэффициента модуляции амплитудно-модулированного сигнала и его уровня несущей.

Цель изобретения - расширение динамического диапазона путем автоматического регулирования коэффициентов передачи усилителя входного АМ-сигна- ла и усилителя огибающей.

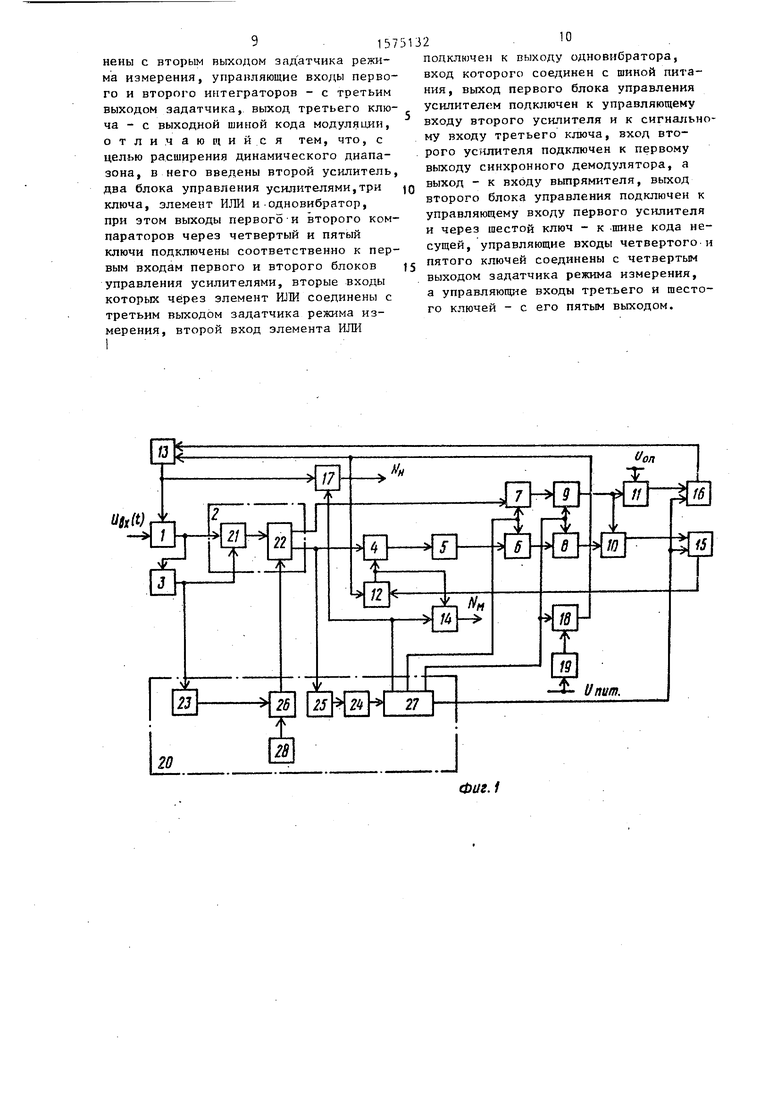

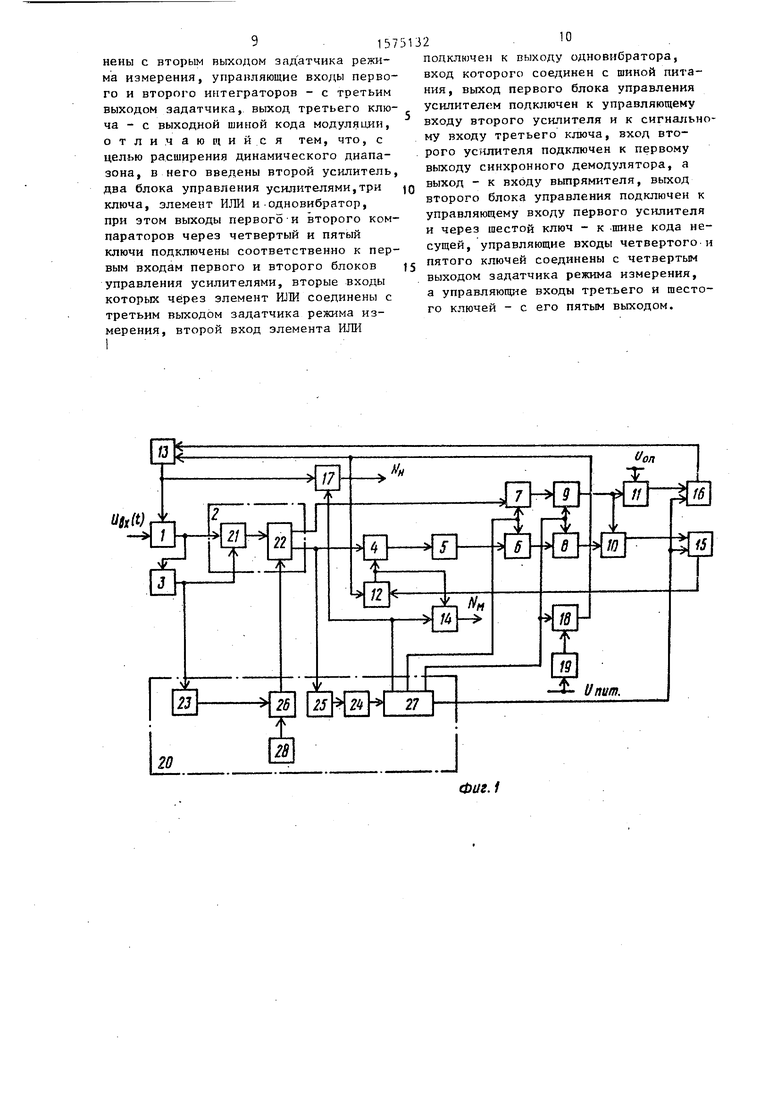

На фиг. 1 приведена функциональная схема преобразователя; на фиг.2 - функциональная схема блока управления усилителем; на фиг. 3 - временные диаграммы.

Преобразователь содержит усилитель , 1 входного сигнала, синхронный демодулятор 2, формирователь 3 управляющего напряжения, усилитель 4 и выпрямитель 5 огибающей АМ-сигнала, первый 6 и второй 7 ключи, первый 8 и второй 9 интеграторы с входящими в них ключами обнуления, первый 10 и второй 11 компараторы, первый 12 и второй 13 блоки управления усилителями, третий - шестой ключи 14 - 17, элемент ИЛИ 18, одновибратор 19, задатчик 20 режима измерения.

Синхронный демодулятор 2, как пример выполнения, содержит ключ 21 и ин терполирующий фильтр 22.

Задатчик 20 режима измерения, как пример, выполнения, содержит первый in второй делители 23 и 24 частоты,

СЛ :Л

i

усилитель-ограничитель 25, первый и второй дешифраторы 26 и 27, формирователь 28 кода периода дискретизации,

Блоки 12 и 13 управления усилителя-, ра 22 - с третьим входом демодулятора

ми, как пример выполнения (фиг. 2), содержат регистр 29 сдвига и п триг- герных ячеек 30.1...30.п.

Усилитель 1 сигнальным входом соединен с источником АМ-сигнала lLSx(t), а выходом с первым (сигнальным) входом синхронного демодулятора 2 и че- рез формирователь 3 управляющего напряжения с его вторым (управляющим)

2, первый и второй выходы интерполирующего фильтра подключены соответственно к первому и второму выходам демодулятора 2. Ю Делитель 23 частоты входом соединен с первым входом задатчика 20 режима измерения, а выходом через дешифратор 26, вторым входом соединенный с выходом формирователя 28 кода перира 22, управляющий вход ключа 21 - с вторым входом демодулятора 2, а управляющий вход интерполирующего фильт

2, первый и второй выходы интерполирующего фильтра подключены соответственно к первому и второму выходам демодулятора 2. Делитель 23 частоты входом соединен с первым входом задатчика 20 режима измерения, а выходом через дешифратор 26, вторым входом соединенный с выходом формирователя 28 кода пери

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь значения коэффициента модуляции амплитудно-модулированного сигнала | 1986 |

|

SU1379750A1 |

| Преобразователь коэффициента амплитудной модуляции в код | 1988 |

|

SU1569749A1 |

| Преобразователь значения коэффициента модуляции амплитудно-модулированного сигнала в цифровой код | 1986 |

|

SU1370618A1 |

| Преобразователь коэффициента амплитудной модуляции в код | 1987 |

|

SU1429055A1 |

| Преобразователь значения коэффициента модуляции амплитудно-модулированного сигнала | 1986 |

|

SU1337830A1 |

| Цифровой интегрирующий вольтметр | 1983 |

|

SU1093984A2 |

| Цифровой интегрирующий вольтметр | 1985 |

|

SU1285392A1 |

| Амплитудно-фазовый анализатор гармоник периодических напряжений | 1985 |

|

SU1303950A2 |

| Устройство цифрового преобразования видеосигнала | 1989 |

|

SU1660210A1 |

| Преобразователь значения коэффициента модуляции амплитудно-модулированного сигнала | 1983 |

|

SU1095106A2 |

Изобретение относится к измерительной технике и может быть использовано для измерения коэффициента модуляции амплитудно-модулированного сигнала и его уровня несущей. Цель - расширение динамического диапазона путем автоматического регулирования коэффициента передачи усилителя входного АМ сигнала и усилителя огибающей. Для ее достижения в преобразователь введены усилитель 4, блоки 12, 13 управления усилителями, ключи 15-17, элемент ИЛИ 18 и одновибратор 19. Преобразователь содержит также усилитель 1 входного сигнала, синхронный демодулятор 2, формирователь 3 управляющего напряжения, задатчик 20 режима измерения, выпрямитель 5, ключи 6, 7, 14, интеграторы 8, 9, компараторы 10, 11, шину опорного напряжения. 3 ил.

входом, а также первым входом задатчи-,5 ода дискретизации, с первым выходом

25

ка 20 режима измерения, первым выходом подключенного к третьему (управляющему) входу синхронного демодулятора 2. Первый выход синхронного демодулятора 2 соединен с вторым входом задатчика 20 режима измерения и через усилитель 4, выпрямитель 5 и нормально разомкнутый ключ 6 с сигнальным входом интегратора 8, выходом подключенного к первому входу компаратора 10, второй выход синхронного демодулятора 2 через нормально разомкнутый ключ 7 соединен с сигнальным входом интегратора 9, выходом подключенного к первому входу компаратора 11 и второму входу компаратора 10, второй вход компаратора 11 соединен с источником опорного напряжения Uen . Управляющие входы слючей 6 и 7 подключены к второму выходу задатчика 20 режима измерения, управляющие входы интеграторов 8 и 9 и первый вход элемента ИЛИ 18 - к третьему выходу задатчика 20, выходы компараторов 10 и 11 через ключи 15 и 16 соединены соответственно с первыми .п входами блоков 12 и 13 управления усилителями 4 и 1, вторыми входами подключенных к выходу элемента ИЛИ 18. Вторые входы ключей 15 и 16 соединены

задатчика 20. Усилитель-ограничитель 25 входом соединен с вторым входом задатчика 20, а выходом через делите 24 частоты - с входом дешифратора 27 2Q первый - четвертый выходы дешифратор 27 соединены соответственно с вторым пятым выходами задатчика 20.

Регистр 29 блоков 12 и 13 управле ния усилителями (фиг. 2) входом соед нен с входом блока, а выходами с пер выми входами триггерных ячеек 30.1.. ..оЗО.п, вторыми входами подключенны к второму входу блоков 12 и 13, выхо триггерных ячеек 30.1...ЗО.п являются выходами блоков 12 и 13.

Устройство работает следующим образом

После подачи напряжения питания одновибратор 19 в интервале

(фиг. 3.1) формирует одиночный импульс, через элемент ИЛИ 18, поступающий на первые входы блоков 1 и 13 управления усилителями 1 и 4 и включающий их старшие разряды с весом 2

На вход усилителя 1 поступает All- сигнал вида (фиг. 3.2)

lie (t)V(1+M sin# t)sinu t, (1)

30

35

ипит O...t

с четвертым выходом задатчика 20, вто-. где V - амплитуда немодулированного nni эттотлчэитя WHIT 1 я иопоо (лгти/л-несущего нап ряжения,

W 27Tf - угловая частота несущей;

рой вход элемента ИЛИ 18 через одно- вибратор 19 соединен с шиной питания

UnuT , Выходы блоков 12 и 13 подключены к управляющим входам усилителей 4 и 1 соответственно и сигнальным входам ключей 14 и 17, управляющими входами ® соединенных с пятым выходом задатчика 20 Выходы ключей 14 и 17 являются выходами кода модуляции и кода несущей соответственно.

Первый (сигнальный) вход синхрон- | ного демодулятора 2 через нормально разомкнутый ключ 21 соединен с сигнальным входом интерполирующего фильт5

п

задатчика 20. Усилитель-ограничитель 25 входом соединен с вторым входом задатчика 20, а выходом через делитель 24 частоты - с входом дешифратора 27, Q первый - четвертый выходы дешифратора 27 соединены соответственно с вторым - пятым выходами задатчика 20.

Регистр 29 блоков 12 и 13 управления усилителями (фиг. 2) входом соединен с входом блока, а выходами с первыми входами триггерных ячеек 30.1... ..оЗО.п, вторыми входами подключенных к второму входу блоков 12 и 13, выходы триггерных ячеек 30.1...ЗО.п являются выходами блоков 12 и 13.

Устройство работает следующим образом

После подачи напряжения питания одновибратор 19 в интервале

(фиг. 3.1) формирует одиночный импульс, через элемент ИЛИ 18, поступающий на первые входы блоков 12 и 13 управления усилителями 1 и 4 и включающий их старшие разряды с весом 2

На вход усилителя 1 поступает All- сигнал вида (фиг. 3.2)

lie (t)V(1+M sin# t)sinu t, (1)

0

5

ипит O...t

- угловая частота огибающей;

М - коэффициент модуляции. Считаем, что коэффициент передачи усилителей 1 и 4 определяются соответственно выражениями:

К1 Ne/N,; К 2 VNi

(2)

где

Ne 2

NL

и N - числовые значения текущих кодов, поступающих

из блоков 13 и 12 соответственно,

п - число разрядов кодов Nf N , задаваемых регистрами 29 блоков 13 и 12 соответственно.

Напряжение . (t)™7 U.ex(t) поступает на входы демодулятора 2 и формирователя 3. На выходе формирователя 3 образуются прямоугольные импульсы частоты си с фронтами, соответствующими моментам перехода через ноль напряжения несушей частоты (см.фиг.3.3), поступающие на управляющий вход ключа 21 демодулятора 2 к на вход делителя 23 частоты задатчика 20. В результате с выхода дешифратора 26 на управляющий вход интерполирующего фильтра 22 поступают прямоугольные импульсы, следующие с периодом

Т о 1/K3W,

(3)

где Кэ - коэффициент деления, задаваемый формирователем 28.

Импульсы с частотой ш(см. фиг. 3.3), поступающие с выхода формирователя 3 на управляющий вход ключа 21 демодулятора 2, открывают его в интервалы времени, соответствукэдие, например, положительным полуволнам напряжения, поступающего на его сигнальный вход,

В результате низкочастотной фильтрации выпрямленного ключом 21 напряжения интерполирующим фильтром 22 на втором выходе демодулятора 2 р,бразу- ется сигнал, содержащий постоянную составляющую, определяемую уровнем несущей, и огибающую входного АМ-нап- ряжения (фиг, 3, 4).

U t)j-j-- К 4 (MVsinSl t+V), (4)

1

где K - коэффициент передачи тракта

вход ключа 21 - выход демодулятора 2.

Причем в данном случае N 1 . Одновременно на первом выходе демодулятора 2 образуется первая производная сигнала (4) (фиг. 3.5)

N

U1(t)4K5MVcOS t.

14 1

где ,К5 - коэффициент передачи тракта вход ключа 21 - выход демодулятора 2.

В данном случае N, 2 .f

Минимальная частота дискретизации

г

SJ,. -- выбирается исходя из условия

Ч т

5

получения необходимой среднеквадрати ческой погрешности восстановления непрерывного сигнала (А) и его производной (5).

Напряжение (5) усилителем-ограничителем 25 преобразуется в прямоугольные импульсы (фиг. 3.6), через делитель 24 частоты поступающие на вход дешифратора 27.

Импульсы с третьего выхода задатчика 20 (фиг. 3.7) поступают на входы обнуления интеграторов 8 и 9 и через элемент ИЛИ 18 на первые входы блоков 12 и 13, с второго выхода (фиг. 3.8)

на управляющие входы ключей 6 и 7, с четвертого выхода (фиг. 3.9) на управляющие входы ключей 15 и 16, с пятого выхода (см, фиг. 3.10) - на управляющие входы ключей 14 и 17. В резуль5 тате в моменты t3, tfr и т.д. t , (фиг. 3,8) на выходах интеграторов 8 и 9 образуются средневыпрямленное U и среднее Uco. напряжения соответственСР

но:

N

tbt

J |U4(t)|dt;

(6)

Jcp ,

35

-N«

Nr 1 L:

S MOdt, (7)

где

40

45

, Г - постоянные времени интеграторов 6 и 7 соответственно;Т 1/F.

Коэффициент передачи выпрямителя 5 приняли равным единице.

Преобразование напряжения UCp, в код NK, пропорциональный уровню несущей V, и напряжения U С8. в код NM, пропорциональный коэффициенту модуляций М производится путем сравнения в интервалах t3,...,tn, ti...t1 и т.д.

(фиг. 3.9) напряжений U Cp, компаратором 11, а также U,

и U

on и U

55

се, - ср,

5Q компаратором 10.

При этом процесс уравновешивания производится в направлении от старших разрядов блоков 13 и 12 к младшим, аналогично аналого-цифровым преобразователям поразрядного уравновешивания компенсирующие напряжения изменяются по закону:

У-f (1,2 -,

ьг

j , bj

ГЧ

(8)

ср,

--К V

сз 4

(i

at

)- N

1575132 (9)

где п - число разрядов регистров 29,

блоков 12 и 13;5

a)t состояния i j-x разрядов регистра 29 блоков 12 и 13 соответственно. В первом цикле в интервале tA... tj,

на выходах интеграторов 8 и 9 образу- О

ются напряжения:

N|

2-121

(10)

IT . V ---- иср, C,K«V 2-1

(11)

.. Компаратором 11 производится сравнение напряжений Uon, а компаратором 10 - напряжений UcS i и U Cp . Выходные сигналы компараторов 10 и 11 через ключи 15 и 16 соответственно в Интервале tb.,. t 4поступают в блоки 12 и 13 управления усилителями 4 и 1. В зависимости от знака разности между

и между U се, « и с,

ы регистра 29 блоков 12 твенно остаются включенЬ, 1) либо сбрасываются

О,- а, О,

Ь1 1; а, 1,

цикле в интервале t.,. ..t.

сигналом с третьего выхода задатчика 19 (фиг„ 3.7) происходит обнуление интеграторов 8 и 9 и включение через элемент ИЛИ 18 вторых разрядов регистра 29 блоков 12 и 13 с весом 2 В момент t на выходах интеграторов 8

и 9 образуются жения:

соответственно напря

а+2- 0 2- ът+Л,)8

,+2-гаг).

(12) (13)

По результатам сравнения UCp и

Uon компаратором 11, а также Мер компаратором 10 в tt .. .t 7

UCfl И

Cfl2

интервале

(фиг. 3.9), определяемым открытым состоянием ключей 15 и 16, вторые разряды регистров 29 блоков 13 и 12 остаются либо включенными (а г I, Ь2 1) либо сбрасываются (а 0, а , Ь7 1, ,

b 4 0) и т.д.

В конце уравновешивания те

в U

en исвп

U

п

ИЛИ

(14)

(15)

Время преобразования коэффициента модуляции в код пропорционально числу разрядов регистров 29 блоков 12 и 13.

Т„ h/K.

35

0

45

0

5

Формула изобретения

Преобразователь амплитудно-модули- рованного сигнала в код, пропорциональный коэффициенту модуляции, содержащий усилитель входного сигнала, выходом подключенный к первому входу синхронного демодулятора и через формирователь управляющего напряжения - к его второму входу и к первому входу эадагчика режима измерения, первым выходом соединенного с третьим входом синхронного демодулятора, первый выход которого подключен к второму входу задатчика режима измерения, выход выпрямителя через последовательно соединенные первый ключ и первый интегратор подключен к первому входу первого компаратора, второй выход синхронного демодулятора через последовательно соединенные второй ключ и второй интегратор соединен с первым входом второго компаратбра и вторым входом первого компаратора, второй вход второго компаратора подключен к шине опорного напряжения, управляющие входы первого и второго ключей соеди9137

нены с вторым выходом задатчика режима измерения, управляющие входы первого и второго интеграторов - с третьим выходом задатчика, выход третьего ключа - с выходной шиной кода модуляции, отличающийся тем, что, с целью расширения динамического диапазона, в него введены второй усилитель, два блока управления усилителями,три ключа, элемент ИЛИ и одновибратор, при этом выходы первого и второго компараторов через четвертый и пятый ключи подключены соответственно к первым входам первого и второго блоков управления усилителями, вторые входы которых через элемент ИЛИ соединены с третьим выходом задатчика режима измерения, второй вход элемента ИЛИ

210

подключен к выходу одновнбратора, вход которого соединен с шиной питания, выход первого блока управления усилителем подключен к управляющему входу второго усилителя и к сигнальному входу третьего ключа, вход второго усилителя подключен к первому выходу синхронного демодулятора, а выход - к входу выпрямителя, выход второго блока управления подключен к управляющему входу первого усилителя и через шестой ключ - к шине кода несущей, управляющие входы четвертого и

пятого ключей соединены с четвертым выходом задатчика режима измерения, а управляющие входы третьего и шестого ключей - с его пятым выходом.

Фиг.1

Л4

,t

35 XV /Ч / / / / / /

7 ч/ 7 7 7 7 Чх f

Дб( I-i m i-i ri n г гп г,

37 L jel

0шод

Фиг. г

| Преобразователь коэффициента амплитудной модуляции в код | 1987 |

|

SU1429055A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Щербаков В.И | |||

| Электронные схемы на операционных усилителях, Киев: Техника, 1983 | |||

| Зельдин Е.А | |||

| Цифровые интегральные микросхемы в информационно-измерительной аппаратуре | |||

| Л.: Энергоатомиздат, 1986. | |||

Авторы

Даты

1990-06-30—Публикация

1988-09-20—Подача