Фиг.1

Изобретение относится.к импульсной технике и может быть использовано для измерения коэффициента модуляции амплитудно-модулированных (AM) сигналов.

Цель изобретения - получение непрерывной информации при измерении коэффициента амплитудной модуляции.

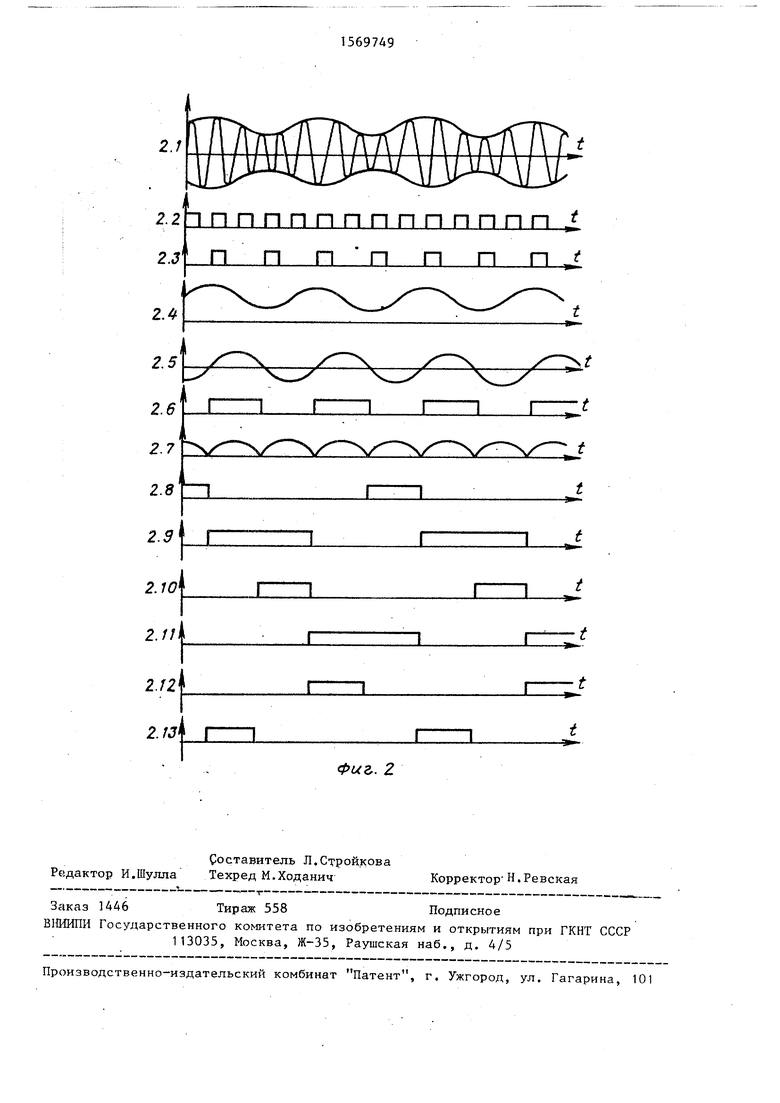

На фиг. Г показана функциональ- ная схема преобразователя; на фиг„2- диаграммы его работы.

Преобразователь содержит усилитель 1 входного сигнала, формирова- ,тель 2 управляющего напряжения, за- датчик 3 режима измерения, синхронный демодулятор 4, выпрямитель 5, третий 6, шестой 7, седьмой 8 и первый 9 ключи, второй интегратор 10, четвертый ключ 11, первый интегра- тор 12, второй ключ 13, третий интегратор 14, восьмой ключ 15, четвертый интегратор 16, девятый 17, двенадцатый 18 и тринадцатый 19 ключи, первый элемент ИЛИ 20, десятый 21 и одиннадцатый 22.ключи, первый 23 и второй 24 компараторы, второй элемент ИЛИ 25, первый элемент И 26, аналого-цифровой преобразователь (АЦП) 27, второй элемент И 28, первый RS-триггер 29, третий элемент ИЛИ 30, второй RS-триггер 31, пятый ключ 32, регистрирующий блок 33. При этом усилитель 1 входного сигнала выходом подключен к первому входу синхронного демодулятора 4 и через формирователь 2 управляющего напряжения к второму входу синхронного демодулятора 4 и первому входу за датчика 3 режима измерения, первым выходом соединенного с третьим входо синхронного демодулятора 4, первый выход которого подключен к второму входу задатчика 3 режима измерения и через выпрямитель 5 и ключ 9 к перво му входу интегратора 12, выходом чере ключ 13 соединенного с вторым входом интегратора 12, второй выход синхронного демодулятора 4 через ключ 6 подключен к первому входу интегратора 10, выходом соединенного через ключ 11 с вторым входом интегратора 10, второй выход задатчика 3 режима измерения подключен к управляющим входам ключей 6 и 9, а управляющие входы ключей 11 и 13 объединены, кроме того, первые входы компараторов 23 и 24 соединены с первым входом АЦП 27, второй вход которого подклю

,.

Q

5 0 5 о о 45 50

5

чен к второму входу компаратора 24, а выход через ключ 32 соединен с регистрирующим блоком 33,второй вход компаратора 23 подключен к шине опорного сигнала, а его выход соединен с первым входом элемента И 26, третий выход задатчика 3 режима измерения соединен с управляющими входами ключей 7 и 8, сигнальные входы которых подключены соответственно к сигнальным входам ключей 6 и 9, а выходы - к первым входам интеграторов 14 и 16 соответственно, выходами через ключи 15 и 17 соединенных со своими вторыми входами, выходы интеграторов 14 и 16 соответственно через ключи 21 и 22 подключены к первому и второму входам компаратора 24, управляющие входы ключей 15 и 17 соединены с четвертым выходом задатчика 3 режима измерения, пятым выходом подключенного к управляющим входам ключей 18 и 19 и через элемент 20 ИЛИ к второму .. и первому входам элементов И 26 и 28, выходы которых соединены соответственно с первыми входами RS-триггеров 29 и 31, второй вход RS-триггера 29 подключен к первому входу элемента ИЛИ 25, управляющим входам ключей 11 и 13 и шестому выходу задатчика 3 режима измерения, второй вход RS-триггера 31 iсоединен с вторым входом второго элемента ИЛИ 25, выходом соединенного с третьим входом АЦП 27 и управляющими входами ключей 17 и 15, выходы RS-триггеров 29 и 31 подключены соответственно к первому и второму входам элемента ИЛИ 30, выходом соединенного с управляющим входом ключа 32, седьмой выход задатчика 3 ре-, жима измерения соединен с вторым входом элемента ИЛИ 20 и управляющими входами ключей 21 и 22, сигнальные входы которых подключены соответственно к выходам интеграторов 14 и 16, их выходы - к первому и второму входам АЦП 27 соответственно, а выход компаратора 24 соединен с вторым входом элемента И 28.

Синхронный демодулятор 4 содержит ключ 34 и интерполирующий фильтр 35, причем первый вход ключа 34 подключен к выходу усилителя 1 входного сигнала и является первым входом демодулятора 4, второй вход ключа 34 подключен к выходу формирователя 2 управляющего напряжения и первому входу задатчика 3 режима измерения и

является вторым входом демодулятора - 4, а выход подключен к сигнальному входу интерполирующего фильтра 35, управляющим входом соединенного с первым выходом задатчика 3 режима измерения , а выходами - с выходами I и II демодулятора 4.

Задатчик 3 режима измерения содержит делитель 36 частоты, дешифратор 37, формирователь 38 кода периода дискретизации, формирователь 39 кода времени измерения, усилитель- ограничитель 40, делитель 41 частоты, дешифратор 42, инвертор 43, элемент И 44, инвертор 45, элементы И 46-48, причем делитель 36 частоты входом соединен с входом задатчика 3 режима измерений, а выходом - с первым входом дешифратора 37, вторым входом соединенного с формирователем 38 кода периода дискретизации, а выходом - с первым выходом задатчика 3, усилитель-ограничитель 40 входом подключен к второму входу задатчика 3, а выходом - к выходам делителя 41 частоты, инвертора 45, элементов И 44 и 46, выход делителя Л1 частоты соединен с первым входом дешифратора 42, вторым входом подключенного к выходу Формирователя 39 кода времени измерения, а выходом - с вторым выходом задатчика 3, вторым входом элемента И 44, первым входом элемента И Д8 и через инвертор 43 с третьим выходом задатчика 3, вторыми входами элементов И 46 и 47, первый и второй входы элементов И 47 и 48 подключены к выходу инвертора 45, выходы элементов И 44, 46-48 подключены соответственно(к седьмому, пятому, шестому и четвертому выходам задатчика 3 режима измерения.

Преобразователь работает следующим образом.

На вход усилителя 1 поступает АМ-сигнал (фиг. 2.J)

U8x(t)V(l+M sinflt)s-inwt, (1)

где V - амплитуда немодулированного несущего напряжения; )/f - угловая частота несущей; - угловая частота огибающей.

Выходное напряжение усилителя 1 поступает на сигнальный вход ключа 34 демодулятора 4 и через формирователь 2 на управляющий вход ключа 34 и вход I задатчика 3. Выходные импульсы формирователя 2 частоты f с

фронтами, соответствующими моментам.; перехода через нуль несущей частоты (фиг. 2.2), запускают делитель 36 частоты. В результате поразрядного сравнения выходного кода делителя 36 и выходного кода формирователя 38, задающего код периода дискретизации, на выходе дешифратора 37 образуются прямоугольные импульсы (фиг. 2.3), следующие с периодом

т -1 Kqf

(2)

К- - коэффициент деления, задаваемый формирователем 38. Прямоугольные импульсы с выхода формирователя 2 открывают ключ 34 в интервале времени, соответствующем положительным полуволнам входного сигнала, В результате низкочастотной фильтрации выпрямленного ключом 34 сигнала (1) интерполирующим фильтром 35 с периодом дискретизации Тд, задаваемым сигналом (фиг. 2.3) через вход III на управляющем входе интерполирующего фильтра 35, на выходе II демодулятора 4 обраяуется сигнал (фиг. 2.4)

30

. sinRt+V), (3)

5

где

Kf К, коэффициент передачи усилителя 1 ;

коэффициент передачи тракта вход I - выход II демодулятора 4.

Одновременно на выходе II демодулятора 4 образуется первая производная (3) сигнала (фиг. 2.5)

40

U7(t)K,K2K3MV cosftt, (4)

5

0

где

кз5

коэффициент передачи тракта вход I - выход I демодулятора 4. Минимальная частота дискретизации

FQ -- выбирается, исходя из требуе Ч

мой среднеквадратичной погрешности

восстановления сигналов (3) и (4) из пульсирующего сигнала на выходе ключа 34 и длительности переходного процесса.

Напряжение (4) усилителем-ограничителем 40 преобразуется в прямоугольные импульсы (фиг. 2.6), через делитель 41 поступающие на первый вход дешифратора 42, вторым входом подключенного к выходу формирователя 39, задающего код времени измерения.

В результате логического преобразования выходного сигнала усилителя- ограничителя АО (фиг. 2.6) и выходных сигналов дешифратора 42 инверторами и 45 и элементами И 44, 46- 48 на выходах VII, V, VI, IV, а также выходе II, подключенного непосредственно к выходу дешифратора 42, образуются управляющие импульсы (фиг. 2.13, 2.12, 2.10, 2.8, 2.9).

При этом время замыкания ключей 9 и 6 (фиг. 2.9) и 7 и 8 (фиг. 2.10 соответствует интервалам измерения в соответствии с выражением

n/F,

(5)

где ,2,,..

Ключи 13 и 11, замкнутые в интервалах O...t,,, t4...ty и т.д., сиг- налом с выхода 6 задатчика (фиг. 2.8 обеспечивают исходное состояние интеграторов 12 и 10 соответственно и размыкаются одновременно с замыкание ключей 9 и 6 сигналом с выхода II задатчика 3 (фиг. 2.9). Напряжение (3) через ключ 6 поступает на вход интегратора 10, а напряжение (4), выпрямленное выпрямителем 5 через ключ 9 - на вход интегратора 12. В результате в моменты t3, t- и т.д. н выходах интеграторов 10 и 12 образуются соответственно среднее и средне-выпрямленное напряжения, соответствующие интервалам измерения

...tj, tj...t7 и т.д.

v pf r S Mtfct т 6

J О1

1 I

Vci, Ц Ut(t)dt -Ј .VKf.a

где -Я С - постоянные времени соответственно интеграторов 10 и 12; K - коэффициент формы огиба-

ющей; 131,3,5,..- номер интервала измерения.

Аналогичным образом ключи 15 и 17 замкнутые в интервалах t...tj, t.,.t7 и т.д. сигналом с выхода задатчика 3 (фиг. 2.10), размыкаются одновременно с замыканием ключей 7 и 8 сигналом с выхода III задатчика 3 (фиг. 2.11). При этом выход II фильтра 35 и выход выпрямителя 5 соответственно через ключи 6 и 9 подключаются к входам интеграторов 14 и 16, на выходах которых образу

5

5

0

0

5

0

5

0 5

ются напряжения V,,,, - и V.. -, соответстСр J C8j

вующие интервалам измерения t3...t5., t...t и т.д. и определяемые выражениями (6) и (7), при этом ,4, 6,... - номер интервала измерения. Полагаем, что постоянные времени интеграторов 14 и 16 равны соответственно постоянным времени интеграторов 12 и 10. Напряжение UCp,-через ключ 18, открытый в интервалах tj...t« t...tg и т.д. сигналом с выхода V задатчика 3 (фиг. 2.12), поступает, на первые входы компараторов 23 и 24 и АЦП 27, а напряжение V . через ключ

vB 1

19, открытый в тех же интервалах, - на вторые входы компаратора 24 и АЦП 27.

Аналогично напряжение Vc-, через ключ 21, открытый в интервалах ts...tt, tj...t(0 и т.д. сигналом с выхода VII задатчика (фиг. 2.13), поступает на первые входы компараторов 23 и 24 и АЦП 27, а напряжение VC8:через ключ 22, открытый в тех же интервалах, - на вторые входы компаратора 24 и АЦП 27.

На выходе с АЦП 27, устанавливаемого в исходное состояние одновременно с интеграторами 12, 10 либо 14, 16, сигналами с выходов VI и IV задатчика 3 через элемент ИЛИ 25 в интервалах t3...t4, t д. ..tt, t-j ...tg и т.д. формируется код

и... gam. . (8)

J ,j S

где ,3,5 и т.д. - номер интервалов измерения tj...t4, tf...tg и т.д.;

,4,6 и т.д. - номер интервалов измерения tj-. ,.t(, tg...t1fl

и т.д.

Компаратор 23, сравнивая напряжение Vc. } :с опорным напряжением Von, определяет минимально допустимый уровень несущей V, а компаратор 24, срав- нивая напряжение Vc - .с напряжением

Vr.; - минимально допустимый коэффи - I циент модуляции.

Пороги срабатывания компараторов 23 и 24 выбираются в соответствии с выражениями

ср1 , 5

(9) (Ю)

Vn,t KSvcfi,i К4 и К5 - коэффициенты передачи компараторов 23 и 24 по опорным входам.

91

Из (10) с учетом(6) и (7) можно получить выражение,определяющее минимально допустимоезначение коэффициента модуляции

М

/ИНН , J

СЮ

кэк

При выполнении условий (9)-(11) ,в интервалах t3...t4, ts...tt и т.д. ..задаваемых выходами V, VII задатчика /3 через элемент ИЛИ 20 и элементы И 26 и 28, выходные сигналы компараторов 23 и 24 переводят RS-триггер 29, 31 в состояние, обеспечивающее выдачу кода АШ1 27 через ключ 32 в регистрирующий блок 33. Установка триггеров 29 и 31 в исходное состояние обеспечивается соответственно в интервалах 0. . .t .,, t4. . .t j и т.д. и t2...tg, t(.,.tj и т.д. сигналами с выходов VI, IV задатчика 3.

Формула изобретения

j к Первым входам третьего и четвертого интеграторов соответственно, выходами через восьмой и девятый ключи соединенных со своими вторыми входами, выходы третьего и четвертого интеграторов соответственно через десятый и -одиннадцатый ключи подключены к первому и второму входам второго компаратора, управляющие входы восьмо го и девятого ключей соединены с четвертым выходом задатчика режима из мерения, седьмым выходом подключенного к управляющим входам десятого и одиннадцатого ключей и через первый элемент ИЛИ - к второму и первому вхоПреобразователь коэффициента амплитудной модуляции в код, содержащий усилитель входного сигнала, выходом подключенный к первому входу синхронного демодулятора и через формирова- 30 дам первого ц второго элементов И, тель управляющего напряжения - к вто- выходы которых соединены соответствен рому входу синхронного демодулятора но с первыми входами первого и второ- и первому входу задатчика режима из- го RS-триггеров, второй вход первого мерения, первым выходом соединенного RS-триггера подключен к первому входу с третьим входом синхронного демодуля зз второго элемента ИЛИ, управляющим вхо1 тора, первый выход которого подклю- дам четвертого и второго ключей и

шестому выходу задатчика режима измерения, второй вход второго RS-триггера соединен с вторым входом второ- 40 го элемента ИЛИ, выход которого соединен с третьим входом аналого-цифрового преобразователя и управляющим входом девятого ключа, выходы первого

чен к второму входу задатчик а режима измерения и через выпрямитель и первый ключ - к первому входу первого . интегратора, выходом через второй ключ соединенного с вторым входом первого интегратора, второй выход синхронного демодулятора через третий

10

опорного сигнала, а его выход соединен с первым входом первого элемента И, отличающийся тем, что, с целью получения непрерывной информации, в него введены восемь ключей, два интегратора, два RS-триггера, три элемента ИЛИ и второй элемент И, при этом третий выход задатчика реQ жима измерения соединен с управляющими входами шестого и седьмого ключей, сигнальные входы которых подключены соответственно к сигнальным входам третьего и первого ключей, а выходы к Первым входам третьего и четвертого интеграторов соответственно, выходами через восьмой и девятый ключи соединенных со своими вторыми входами, выходы третьего и четвертого интеграторов соответственно через десятый и -одиннадцатый ключи подключены к первому и второму входам второго компаратора, управляющие входы восьмого и девятого ключей соединены с четвертым выходом задатчика режима измерения, седьмым выходом подключенного к управляющим входам десятого и одиннадцатого ключей и через первый элемент ИЛИ - к второму и первому вхо0

5

0 дам первого ц второго элементов И, выходы которых соединены соответствен но с первыми входами первого и второ- го RS-триггеров, второй вход первого RS-триггера подключен к первому входу зз второго элемента ИЛИ, управляющим вхо1 дам четвертого и второго ключей и

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь значения коэффициента модуляции амплитудно-модулированного сигнала в цифровой код | 1986 |

|

SU1370618A1 |

| Преобразователь амплитудно-модулированного сигнала в код, пропорциональный коэффициенту модуляции | 1988 |

|

SU1575132A1 |

| Преобразователь коэффициента амплитудной модуляции в код | 1987 |

|

SU1429055A1 |

| Преобразователь значения коэффициента модуляции амплитудно-модулированного сигнала | 1986 |

|

SU1379750A1 |

| Преобразователь значения коэффициента модуляции амплитудно-модулированного сигнала | 1986 |

|

SU1337830A1 |

| Цифровой интегрирующий вольтметр | 1983 |

|

SU1093984A2 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА ПЕРЕДАЧИ ДАННЫХ | 2012 |

|

RU2504830C2 |

| Устройство для цифровой записи-воспроизведения цифровой информации | 1990 |

|

SU1788521A1 |

| Способ измерения времени установления выходного сигнала цифроаналоговых преобразователей и устройство для его осуществления | 1987 |

|

SU1494216A1 |

| Широтно-импульсный регулятор для управления вентильным преобразователем | 1983 |

|

SU1181074A1 |

Изобретение относится к импульсной технике и может быть использовано для измерения коэффициента модуляции амплитудно-модулированных сигналов. Целью изобретения является получение непрерывной информации при измерении коэффициента амплитудной модуляции. Устройство содержит усилитель 1 входного сигнала, формирователь 2 управляющего напряжения, задатчик 3 режима измерения, синхронный демодулятор 4, выпрямитель 5, ключи 6 - 9, интеграторы 10, 12, 14, 16, ключи 11, 13, 15, 17, 18, 19, 32, элементы ИЛИ 20, 25, 30, ключи 21 и 22, компараторы 23 и 24, элементы И 26, 28, аналого-цифровой преобразователь 27, триггеры 29 и 31, регистрирующий блок 33. 2 ил.

ключ подключен к первому входу вто- и второго RS-триггеров подключены со- рого интегратора, выходом соединен- 45 ответственно к первому и второму ного через четвертый ключ с вторым входом второго интегратора, второй выход задатчика режима измерения подключен к управляющим входам первого и третьего ключей, а управляющие вхо- 50 входом первого элемента ИЛИ и управ- ды второго и четвертого ключей объе- ляющими входами двенадцатого и три--- динены, первые входы первого и второго компараторов соединены с первым входом аналого-цифрового преобразователя, второй вход которого подключен -55 Р°в их выходы - к первому и второму к второму входу второго компаратора, входам аналого-цифрового преобразова- а выход через пятый ключ соединен с теля соответственно, а выход второго регистрирующим блоком, второй вход компаратора соединен с вторым входом первого компаратора подключен к шине второго элемента И.

входам третьего элемента ИЛИ, выход которого соединен с управляющим входом пятого ключа, пятый выход задатчика режима измерения соединен с вторым

надцатого ключей, сигнальные входы которых подключены соответственно к выходам второго и первого интегратои второго RS-триггеров подключены со- ответственно к первому и второму входом первого элемента ИЛИ и управ- ляющими входами двенадцатого и три--- Р°в их выходы - к первому и второму входам аналого-цифрового преобразова- теля соответственно, а выход второго компаратора соединен с вторым входом второго элемента И.

входам третьего элемента ИЛИ, выход которого соединен с управляющим входом пятого ключа, пятый выход задатчика режима измерения соединен с вторым

и второго RS-триггеров подключены со- ответственно к первому и второму входом первого элемента ИЛИ и управ- ляющими входами двенадцатого и три--- Р°в их выходы - к первому и второму входам аналого-цифрового преобразова- теля соответственно, а выход второго компаратора соединен с вторым входом второго элемента И.

надцатого ключей, сигнальные входы которых подключены соответственно к выходам второго и первого интеграто

| Преобразователь значения коэффициента модуляции амплитудно-модулированного сигнала | 1986 |

|

SU1337830A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь коэффициента амплитудной модуляции в код | 1987 |

|

SU1429055A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-06-07—Публикация

1988-04-05—Подача