t

(21)4337731/24-07

(22)04.12.87

(46) 07.07.90. Бкш. № 25

(71)Уфимский авиационный институт им.Серго Орджоникидзе

(72)0.Л.Рыжиков, В .И.Шарабыров, В.Ю.Карпов и А.В.Никитин

(53)621.314.27 (088.8)

(56)Авторское свидетельство СССР № 1332487, кл, Н 02 М 7/48, 1985.

(54)ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ТРЕХФАЗНЫМ ШИРОТНО-ИМПУЛЬСНЫМ ИНВЕРТОРОМ

(57)Изобретение относится к электротехнике, а именно к управлению транзисторными и тиристорными преобразователями. Целью изобретения является обеспечение регулирования при широт- но-импульсной модуляции (ШИМ) выходного напряжения инвертора. Устройство содержит задающий генератор, два счетчика импульсов, блок инвертирующих элементов, реверсивные счетчи-

ки, вычитающие счетчики, RS-триггеры, формирователи импульсов управления по числу фаз и узлы управления по числу фаз, в состав каждого из которых входят два элемента ИЛИ-НЕ, элемент И, RS-триггер и DT-триггер. Применение вычитающих счетчиков совместно с реверсивными в каждой фазе дает возможность аппаратным способом организовать прямой синтез ШИМ по синусоидальному закону. Второй счетчик импульсов служит для установки начальных состояний реверсивных счетчиков. Узлы управления выдают сигналы на входы направления счета и входы разрешения счета реверсивных счетчиков соответствующей фазы в зависимости от состояния двух .других фаз. Осуществление прямого синтеза ШИМ по синусоидальному закону позволяет простыми средствами обеспечить регулирование выходного напряжения трехфазных широтно-импульсных инверторов и делает возможным централизованное управление от ЭВМ. 2 ил.

(Л

ел J

оэ со

Јь

4

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИЕМОПЕРЕДАЧИ ДАННЫХ | 2001 |

|

RU2209524C2 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1996 |

|

RU2115952C1 |

| Преобразователь напряжения с многозонной импульсной модуляцией | 1985 |

|

SU1259449A1 |

| ДИСКРЕТНО-АНАЛОГОВЫЙ СИНУС-ГЕНЕРАТОР | 1995 |

|

RU2108657C1 |

| Аналого-цифровой преобразователь в код системы остаточных классов | 1991 |

|

SU1797158A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2115165C1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ СТЕНДОМ ДЛЯ ШЕРОХОВКИ ПОВЕРХНОСТИ ЛИСТА | 1990 |

|

RU2009833C1 |

| Цифровое устройство для управления широтно-импульсным преобразователем | 1986 |

|

SU1446674A1 |

| Устройство для управления шаговым двигателем | 1986 |

|

SU1374179A1 |

| ТЕСТЕР УРОВНЯ ИННОВАЦИОННОГО ИНТЕЛЛЕКТА ЛИЧНОСТИ | 2013 |

|

RU2522992C1 |

Изобретение относится к электротехнике, а именно к управлению транзисторными и тиристорыми преобразователями. Целью изобретения является обеспечение регулирования при широтно-импульсной модуляции (ШИМ) выходного напряжения инвертора. Устройство содержит задающий генератор, два счетчика импульсов, блок инвертирующих элементов, реверсивные счетчики, вычитающие счетчики, R-S-триггеры, формирователи импульсов управления по числу фаз и узлы управления по числу фаз, в состав каждого из которых входят два элемента ИЛИ-НЕ, элемент И, R-S-триггер и T-триггер. Применение вычитающих счетчиков совместно с реверсивными в каждой фазе дает возможность аппаратным способом организовать прямой синтез ШИМ по синусоидальному закону. Второй счетчик импульсов служит для установки начальных состояний реверсивных счетчиков. Узлы управления выдают сигналы на входы направления счета и входы разрешения счета реверсивных счетчиков соответствующей фазы в зависимости от состояния двух других фаз. Осуществление прямого синтеза ШИМ по синусоидальному закону позволяет простыми средствами обеспечить регулирование выходного напряжения трехфазных широтно-импульсных инверторов и делает возможным центризованное управление от ЭВМ. 2 ил.

Изобретение относится к электротехнике и может быть использовано для управления тиристорными и транзисторными трехфазными инверторами с широтно-импульсной модуляцией выходного напряжения.

Целью изобретения является обеспечение регулирования при широтно-импульсной модуляции выходного напряжения инвертора.

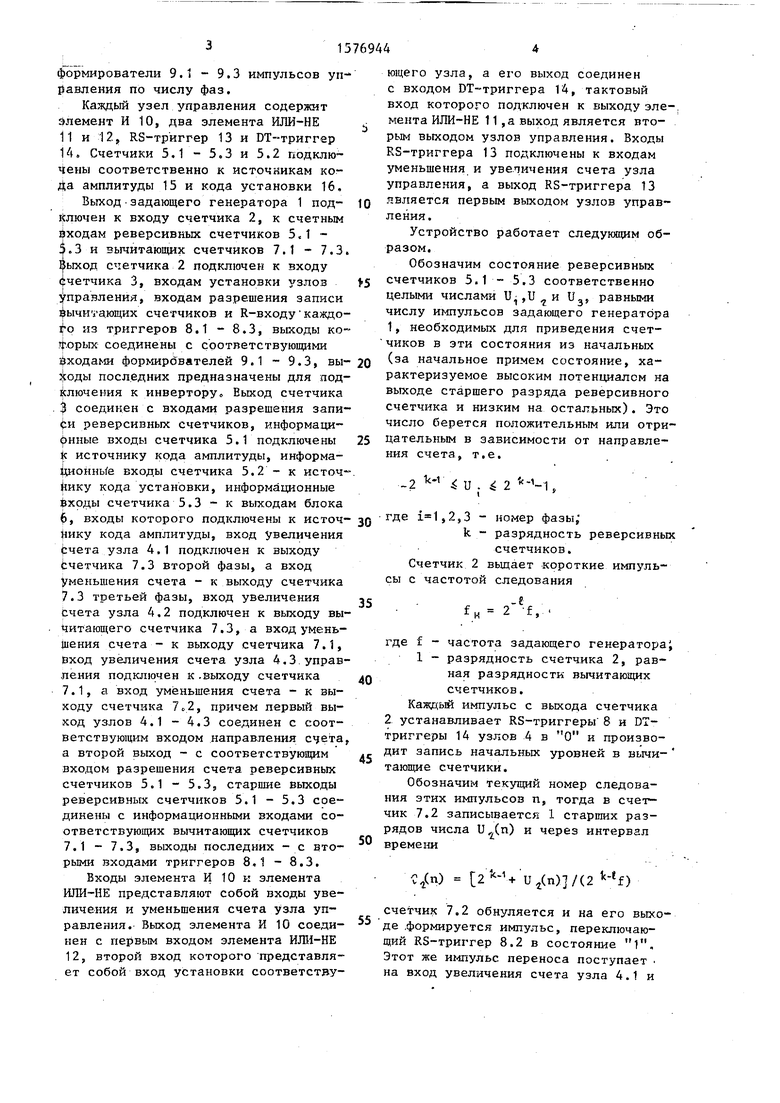

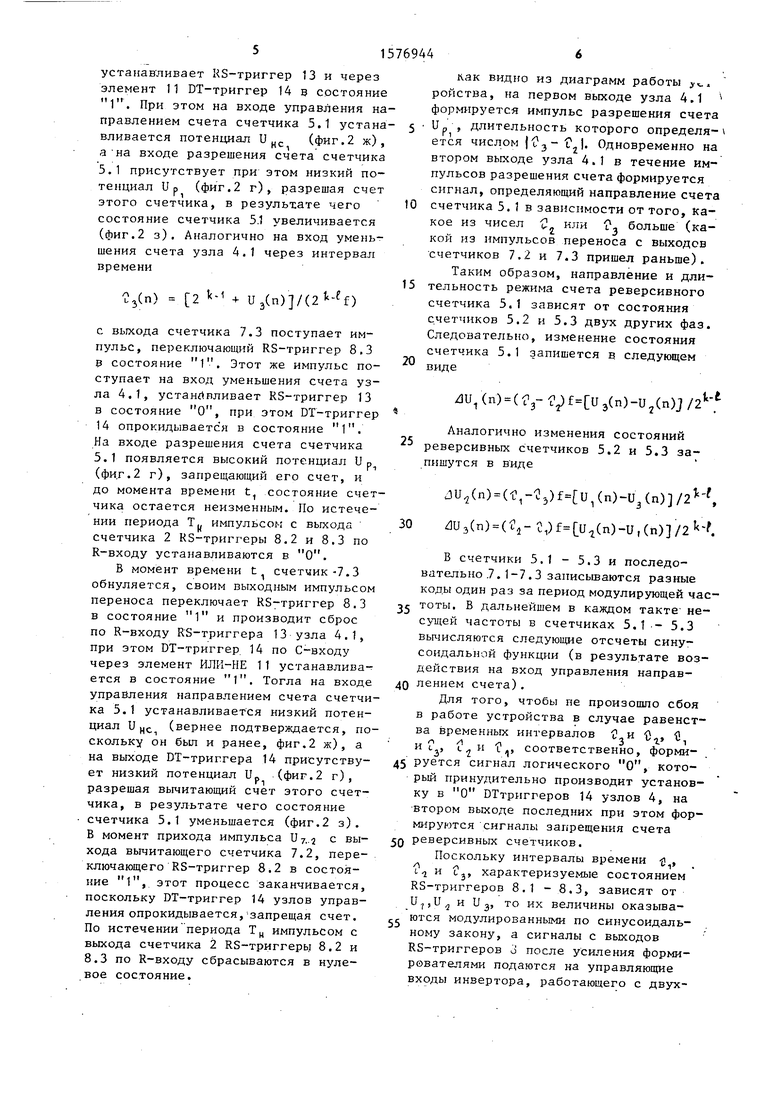

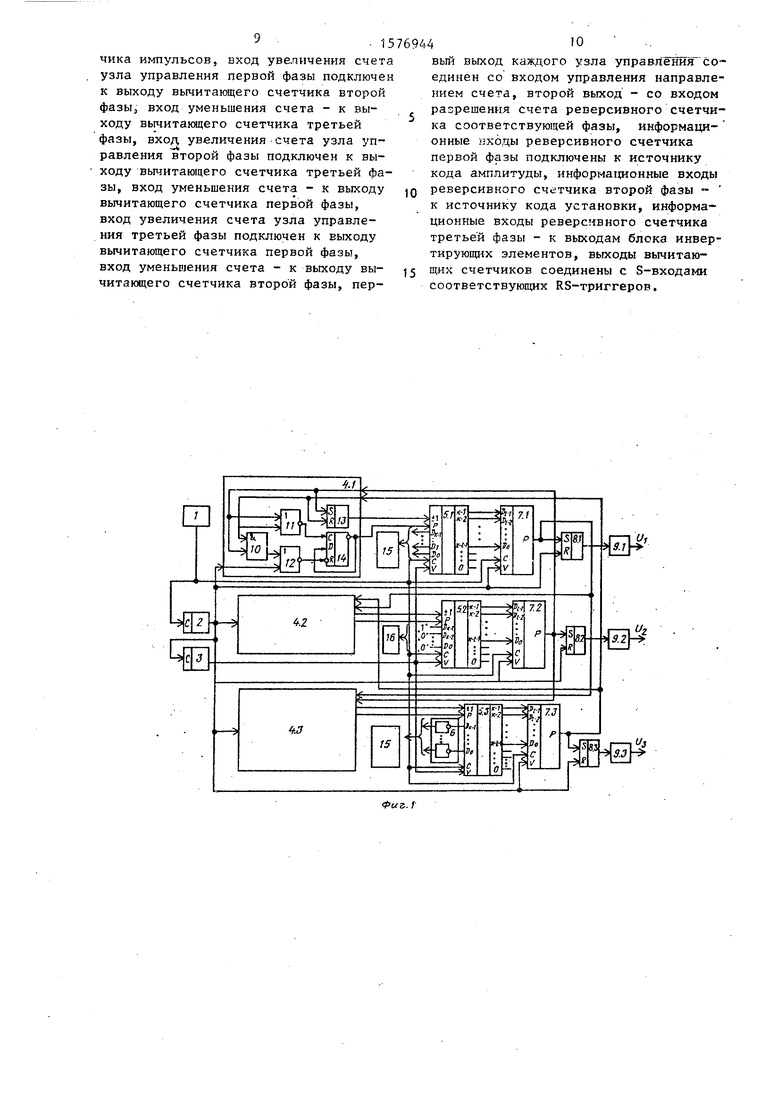

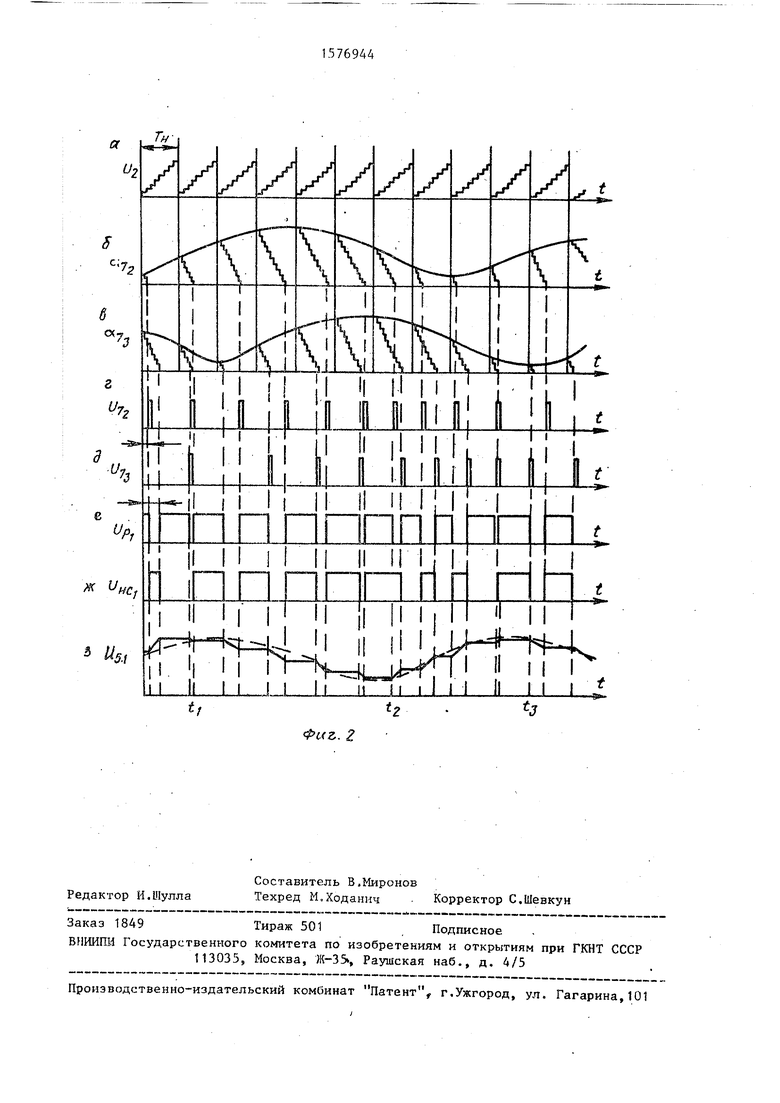

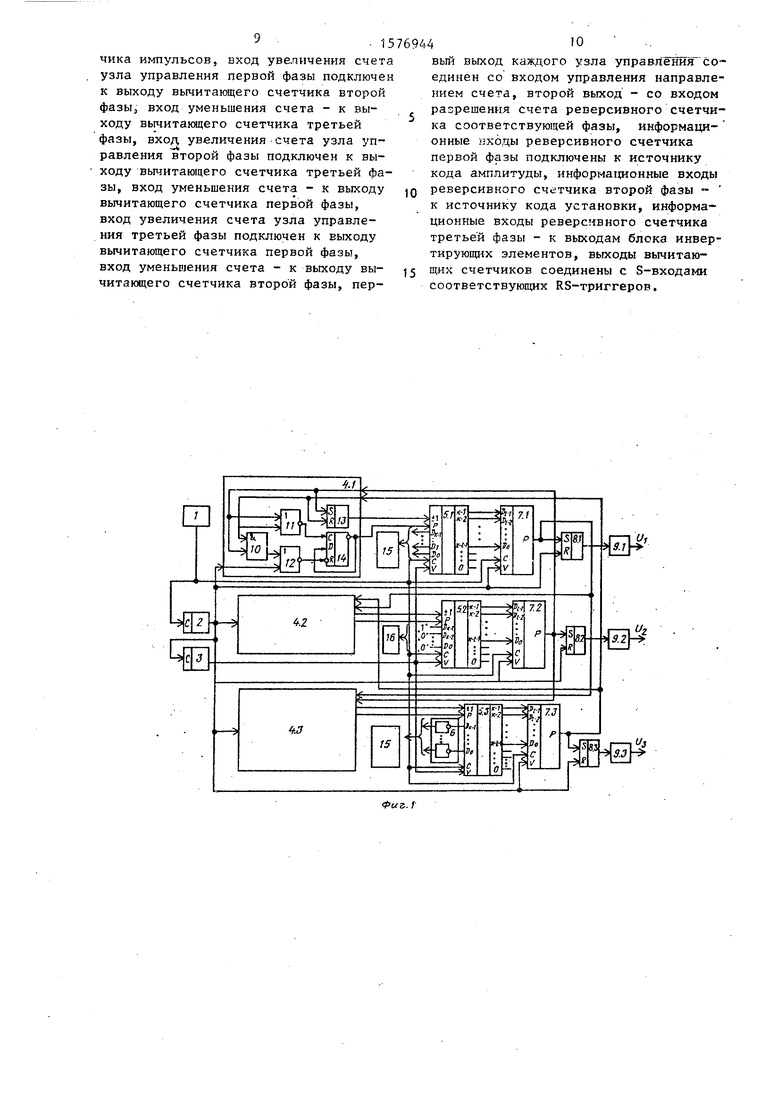

На фиг.1 представлена структурная схема устройства; на фиг.2 - диаграммы, поясняющие его работу.

Устройство содержит задающий генератор 1, счетчики 2 и 3 импульсов, узлы 4.1 - 4.3 управления по числу фаз, реверсивные счетчики 5.1 - 5.-3 по числу фаз, блок 6 инвертирующих элементов, вычитающие счетчики 7.1 - 7.3, RS-триггеры 8.1 - 8.3 и

формирователи 9.1 - 9.3 импульсов управления по числу фаз.

Каждый узел управления содержит элемент И 10, два элемента ИЛИ-НЕ 11 и 12, RS-триггер 13 и DT-триггер 14, Счетчики 5,1 - 5.3 и 5.2 подключены соответственно к источникам кода амплитуды 15 и кода установки 16. Выход задающего генератора 1 подключен к входу счетчика 2, к счетным входам реверсивных счетчиков 5.1 - 5.3 и вычитающих счетчиков 7.1 - 7.3. Выход счетчика 2 подключен к входу счетчика 3, входам установки узлов управления, входам разрешения записи вычиуающих счетчиков и R-входу каждого из триггеров 8.1 - 8.3, выходы которых соединены с соответствующими входами формирователей 9.1 - 9.3, вы ходы последних предназначены для под1 ключения к инвертору Выход счетчика 3 соединен с входами разрешения запи си реверсивных счетчиков, информационные входы счетчика 5.1 подключены к источнику кода амплитуды, информационные входы счетчика 5.2 - к источ нику кода установки, информационные входы счетчика 5.3 - к выходам блока 6, входы которого подключены к источ нику кода амплитуды, вход увеличения счета узла 4.1 подключен к выходу счетчика 7.3 второй фазы, а вход уменьшения счета - к выходу счетчика 7.3 третьей фазы, вход увеличения счета узла 4.2 подключен к выходу вычитающего счетчика 7.3, а вход уменьшения счета - к выходу счетчика 7.1, вход увеличения счета узла 4.3 управления подключен к .выходу счетчика 7.1, а вход уменьшения счета - к выходу счетчика 7„2, причем первый выход узлов 4.1 - 4.3 соединен с соответствующим входом направления счета а второй выход - с соответствующим входом разрешения счета реверсивных счетчиков 5.1 - 5.3, старшие выходы реверсивных счетчиков 5.1 - 5.3 соединены с информационными входами соответствующих вычитающих счетчиков 7.1 - 7.3, выходы последних - с вторыми входами триггеров 8.1 - 8.3. Входы элемента И 10 к элемента ИЛИ-НЕ представляют собой входы увеличения и уменьшения счета узла управления. Выход элемента И 10 соединен с первым входом элемента ИЛИ-НЕ 12, второй вход которого представляет собой вход установки соответству

I-

-

5

0

5

ющего узла, а его выход соединен с входом DT-триггера 14, тактовый вход которого подключен к выходу элемента ИЛИ-НЕ 11 ,а выход является вторым выходом узлов управления. Входы RS-триггера 13 подключены к входам уменьшения и увечичения счета узла управления, а выход RS-триггера 13 является первым выходом узлов управления.

Устройство работает следующим образом.

Обозначим состояние реверсивных счетчиков 5.1 - 5.3 соответственно целыми числами U,,U г и U3, равными числу импульсов задающего генератора 1, необходимых для приведения счетчиков в эти состояния из начальных (за начальное примем состояние, характеризуемое высоким потенциалом на выходе старшего разряда реверсивного счетчика и низким на остальных). Это число берется положительным или отрицательным в зависимости от направления счета, т.е.

-2

iU. i 2 -l,

30

где ,2,3 - номер фазы;

k - разрядность реверсивных

счетчиков.

Счетчик 2 выдает короткие импульсы с частотой следования

35

f

Л 2 f,

где f - частота задающего генератора 1 - разрядность счетчика 2, равная разрядности вычитающих счетчиков.

Каждый импульс с выхода счетчика 2 устанавливает RS-триггеры 8 и DT- триггеры 14 узлов 4 в О и производит запись начальных уровней в вычи- тающие счетчики.

Обозначим текущий номер следования этих импульсов п, тогда в счетчик 7.2 записывается 1 старших разрядов числа U(n) и через интервал времени

Сг(п) 2k-1+ Ut(n)1/(2 ЫЈ)

счетчик 7.2 обнуляется и на его выходе формируется импульс, переключающий RS-триггер 8.2 в состояние 1. Этот же импульс переноса поступает на вход увеличения счета узла 4.1 и

устанавливает RS-триггер 3 и через элемент 11 DT-триггер 14 в состояние 1. При этом на входе управления направлением счета счетчика 5.1 устанавливается потенциал U нс (фиг.2 ж), а на входе разрешения счета счетчика 5.1 присутствует при этом низкий потенциал Up (фиг.2 г), разрешая счет этого счетчика, в результате чего состояние счетчика 51 увеличивается (фиг.2 з). Аналогично на вход уменьшения счета узла 4.1 через интервал времени

С3(п) 2 Ь 1 + из(п)/()

с выхода счетчика 7.3 поступает импульс, переключающий RS-триггер 8.3 В состояние 1. Этот же импульс поступает на вход уменьшения счета узла 4.1, устан пливает RS-триггер 13 в состояние О, при этом DT-триггер 14 опрокидывается в состояние 1. На входе разрешения счета счетчика 5.1 появляется высокий потенциал U рп (фиг.2 г), запрещающий его счет, и до момента времени t, состояние счетчика остается неизменным. По истечении периода Тц импульсом с выхода счетчика 2 RS-триггеры 8.2 и 8.3 по R-входу устанавливаются в О.

В момент времени 11 счетиик-7.3 обнуляется, своим выходным импульсом переноса переключает RS-триггер 8.3 в состояние 1 и производит сброс по R-входу RS-триггера 13 узла 4.1, при этом DT-триггер 14 по С-входу через элемент ИЛИ-НЕ 11 устанавливается в состояние Г1. Тогла на входе управления направлением счета счетчика 5.1 устанавливается низкий потенциал Uнс (вернее подтверждается, поскольку он был и ранее, фиг.2 ж), а на выходе DT-триггера 14 присутствует низкий потенциал Up (фиг.2 г), разрешая вычитающий счет этого счетчика, в результате чего состояние счетчика 5.1 уменьшается (фиг.2 з). В момент прихода импульса U7. i с выхода вычитающего счетчика 7.2, переключающего RS-триггер 8.2 в состояние 1, этот процесс заканчивается, поскольку DT-триггер 14 узлов управления опрокидывается, запрещая счет. По истечении периода Тн импульсом с выхода счетчика 2 RS-триггеры 8.2 и 8.3 по R-входу сбрасываются в нулевое состояние.

как видно из диаграмм работы , ройства, на первом выходе узла 4.1 формируется импульс разрешения счета

Up , длительность которого определи- ется числом |С3 2 Одновременно на втором выходе узла 4.1 в течение импульсов разрешения счета формируется сигнал, определяющий направление счета

счетчика 5. 1 в зависимости от того, Какое из чисел Ј или 3 больше (какой из импульсов переноса с выходов счетчиков 7.2 и 7.3 пришел раньше). Таким образом, направление и длительность режима счета реверсивного счетчика 5.1 зависят от состояния счетчиков 5.2 и 5.3 двух других фаз. Следовательно, изменение состояния

счетчика 5.1 запишется в следующем

виде

l-fc

U1(n) ((n)-U2(n)J/2k;

Аналогично изменения состояний реверсивных счетчиков 5.2 и 5.3 запишутся в виде

JUl(n) ()(n)-U3(n)/2), 4U3(n) (V 4)f4Mn)-U (n)/2H

В счетчики 5.1 - 5.3 и последовательно 7. 1-7.3 записываются разные коды один раз за период модулирующей частоты. В дальнейшем в каждом такте несущей частоты в счетчиках 5.1 - 5.3 вычисляются следующие отсчеты синусоидальной функции (в результате воздействия на вход управления направпением счета).

Для того, чтобы не произошло сбоя в работе устройства в случае равенства временных интервалов Ј и 0., $ и ., О и Г, соответственно, формируется сигнал логического О, который принудительно производит установку в О ОТтриггеров 14 узлов 4, на втором выходе последних при этом формируются сигналы запрещения счета

реверсивных счетчиков.

Поскольку интервалы времени 2,, Р-г и , характеризуемые состоянием RS-триггеров 8.1 - 8.3, зависят от и,ил и U 3, то их величины оказыва

ются модулированными по синусоидальному закону, а сигналы с выходов RS-триггеров о после усиления формирователями подаются на управляющие входы инвертора, работающего с двухполярной ШИМ с несущей частотой f

рп

2 f и выходным синусоидальным напряжением частотой

V2

л

е-ь

farctg(2 /3)/2

Для того, чтобы погрешность, связанная с усечением при выполнении вычислительных операций в счетчиках с ограниченной разрядностью, не накапливалась, а также для управления амплитудой выходного сигнала в устройство введен счетчик 3 с коэффициентом пересчета близким к N Јu/f,

п /

2 ///arctg(2 УЗ).

Выходные импульсы этого счетчика, следующие с частотой выходного синусоидального напряжения, поступают на входы управления записью реверсивных счетчиков и тем самым устанавливают начальные состояния реверсивных счетчиков соответственно U,j(0), U2(0) , Uq(0), после чего в течение периода Тм отрабатывается синусоидальное колебание, по истечении периода операции установки начальных состояний реверсивных счетчиков повторяются, что обеспечивает стабилизацию амплитуды выходных сигналов и возможность управления амплитудой выходных сигналов от источника кода амплитуды.

Таким образом, объединение трех широтно-импульсных цифровых модуляторов, т.е. устройств, преобразующих код в длительность импульса, дает возможность одновременно с преобразованием вычислять следующее значение кода. Причем в силу организации воздействия на входы направления счета вычитающих счетчиков значения кода вычисляют по синусоидальному закону с определенной частотой.

Таким образом, в цифровом устройстве достаточно простыми схемо-техни- ческими средствами обеспечивается регулирование выходного напряжения трехфазного широтно-импульсного инвертора путем широтно-импульсной модуляции по синусоидальному закону с помощью цифровых аналогов динамических звеньев, выполненных на счетчиках со стабилизацией амплитуды выходных сигналов путем периодической установки начальных состояний реверсивных счетчиков, и узлов управления по числу фаз, управляющих состоянием дина

0

5

0

5

0

5

0

5

мических звеньев соответствующих фаз в зависимости от состояния динамических звеньев двух других фаз.

Формула изобретения

Цифровое устройство для управления трехфазным широтно-импульсным инвертором, содержащее задающий генератор, выход которого подключен к входу первого счетчика импульсов, реверсивные счетчики по числу фаз, счетные входы которых подключены к выходу задающего генератора, блок инвертирующих элементов, входы которого подключены к источнику кода амплитуды, RS-триггеры по числу фаз, R-вход каждого из которых соединен с выходом первого счетчика импульсов, выходы подключены к входам формирователей импульсов управления, выходы которых предназначены для подключения к инвертору, о т- личающееся тем, что с целью обеспечения регулирования широтно-импульсной модуляции выходного напряжения инвертора, оно снабжено вторым счетчиком импульсов, вычитающими счетчиками по числу фаз, источником кода установки и узлами управления по числу фаз, каждый из которых содержит элемент И, два элемента ИЛИ-НЕ, RS- и DT-триггеры, причем в каждом узле управления S- и R-входы RS-триг- гера являются входами увеличения и уменьшения счета соответствующего узла и соединены с входами элемента И и первого элемента ИЛИ-НЕ, выход элемента И соединен с первым входом второго элемента ИЛИ-НЕ, второй вход которого является входом установки соответствующего узла, выходы первого и второго элементов ИЛИ-НЕ соеди- нены соответственно с С- и R-входами DT-триггера, выход RS-триггера и ин-- версный выход DT-триггера являются первым и вторым выходами узла управления, счетные входы вычитающих счетчиков подключены к выходу задающего генератора, входы разрешения записи - к выходу первого счетчика импульсов, информационные входы - к старшим выходам реверсивных счетчиков соответствующей фазы, вход второго счетчика импульсов подключен к выходу первого счетчика импульсов, выход - к входам разрешения записи реверсивных счетчиков, входы установки узлов управления соединены с выходом первого елгЬт-

чика импульсов, вход увепичения счета узла управления первой фазы подключен к выходу вычитающего счетчика второй фазы, вход уменьшения счета - к выходу вычитающего счетчика третьей фазы, вход увеличения счета узла управления второй фазы подключен к выходу вычитающего счетчика третьей фазы, вход уменьшения счета - к выходу вычитающего счетчика первой фазы, вход увеличения счета узла управления третьей фазы подключен к выходу вычитающего счетчика первой фазы, вход уменьшения счета - к выходу вычитающего счетчика второй фазы, пер0

5

выи выход каждого узла управления соединен со входом управления направлением счета, второй выход - со входом разрешения счета реверсивного счетчика соответствующей фазы, информаци- онные реверсивного счетчика первой фазы подключены к источнику кода амплитуды, информационные входы реверсивного счетчика второй фазы - к источнику кода установки, информационные входы реверсивного счетчика третьей фазы - к выходам блока инвертирующих элементов, выходы вычитающих счетчиков соединены с S-входами соответствующих RS-триггеров.

а

ж и

Us

II I i iTli i И I 11 И I /

J

/

Фиг,. 2

И

J

Авторы

Даты

1990-07-07—Публикация

1987-12-04—Подача