Изобретение относится к вычислительной технике, в частности к устройствам психологического моделирования действий лиц, вовлеченных в практически важные ситуации, с последующей оценкой этих действий, к области испытаний профессиональной пригодности и связанному с ними обучению, к области психометрических измерений интеллекта, проводимых в психологии. Устройство может использоваться для проведения индивидуальных экспресс-тестов профессиональной пригодности в условиях отсутствия ресурсов для более полного и точного оценивания уровня готовности личности к инновационной деятельности в практически важных ситуациях, а также при формировании команд для эффективного решения узкоспециализированных наукоемких творческих задач.

Известна автоматизированная система для обучения и контроля знаний (Патент RU №2110095 C1, G09B 7/00), выполненная на базе персонального компьютера, состоящая из пульта управления, устройства ввода ответов и реакций обучаемого, блоков ввода информации, дешифратора управляющих сигналов, буфера данных, устройства управления и синхронизации, счетчика адреса, блока памяти, цифроаналогового преобразователя и аналогового мультиплексора.

Первый аналог позволяет использовать информационную стимуляцию на субсенсорном уровне восприятия в процессе ускоренного индивидуального обучения и контроля знаний.

Недостатками первого аналога являются громоздкость и относительно высокая стоимость одного рабочего места из-за использования в качестве базы персонального компьютера.

Известна система тестирования «Телетестинг» (RU 2186423 С2, G09B 7/00), предназначенная для проверки объема и качества знаний при дистанционном обучении, при заочном автоматизированном определении профпригодности, при организационно-управленческом, профориентационном и индивидуально-личностном консультировании, а также при аттестационном контроле кадрового состава предприятий. Система базируется на компьютерных сетевых информационных технологий и включает в себя блоки подготовительных модулей, модули тестирования, телекоммуникационные модули и модули анализа и обработки.

Второй аналог позволяет реализовать дистанционное одновременное тестирование множества испытуемых, находящихся территориально в различных местах и обеспечивает секретность тестовых заданий для повышения достоверности получаемых результатов.

Недостатками второго аналога являются относительная сложность системы и высокая стоимость одного рабочего места, необходимость разработки специального программного обеспечения для подсчета тестовых баллов в процессе телекоммуникации.

Наиболее близким аналогом (прототипом) по своей технической сущности заявленному устройству является прибор контроля знаний (RU 2110096 C1, G09B 7/07), включающий в себя несколько пультов учащихся, преобразователи угла поворота в код, блок двухпозиционных датчиков, пульт управления прибора, электрическую схему формирования оценок, табло и источник электропитания.

Схема прототипа позволяет использовать его для экспресс-тестинга испытуемых, существенно снизить при этом стоимость одного рабочего места.

Однако устройство-прототип имеет недостатки.

1. Зависимость конструкции прибора от количества и сложности проводимых тестов. В связи с этим для проведения комплексной оценки испытуемого при большом количестве гетерогенных тестовых заданий требуется пропорциональное усложнение конструкции прибора (трудно масштабировать).

2. Необходимость централизованного управления приборами для задания ключей к тестам и управления процессом тестирования.

Целью изобретения является разработка устройства тестирования, обеспечивающего оперативную оценку уровня инновационного интеллекта испытуемых, упрощение масштабирования в соответствии с требуемым количеством испытуемых за счет использования автономных индивидуальных пультов тестирования, децентрализации управления процессом тестирования за счет применения технологии микропрограммных автоматов, возможность применения гетерогенных тестовых заданий с большим количеством вопросов различной сложности и вариантов ответов за счет использования оперативных запоминающих устройств.

Поставленная цель достигается тем, что в известное устройство тестирования, содержащее блок датчиков, D-разрядный, где D≥2 информационный выход которого подключен к D-разрядному информационному входу блока кодирования ответов, блок вычисления частных показателей, второй управляющий выход которого подключен к первому управляющему входу блока индикации 7, а N-разрядный, где N≥2 управляющий вход блока вычисления частных показателей 5 подключен к TV-разрядному управляющему выходу блока управления, Р-разрядный, где Р≥2, информационный вход которого подключен к Р-разрядному управляющему выходу блока датчиков, пятый управляющий выход которого подключен к третьему управляющему входу блока управления, а третий управляющий выход блока датчиков подключен к первому управляющему входу блока управления и третьему управляющему входу блока индикации, K-разрядный и M-разрядный, где К≥2 и М≥2 информационные выходы блока управления подключены соответственно к K-разрядному информационному входу блока кодирования ответов и к M-разрядному информационному входу блока индикации, дополнительно введены блок синхронизации, блок предварительных подсчетов баллов, блок вычисления обобщенного показателя, S-разрядный, где S≥2, информационный вход которого подключен к S-разрядному информационному выходу блока вычисления частных показателей. Третий, четвертый и пятый синхронизирующие входы блока вычисления обобщенного показателя подключены соответственно к шестому, седьмому и восьмому синхронизирующим выходам блока синхронизации. Второй управляющий вход и шестой управляющий S-разрядный вход блока вычисления обобщенного показателя подключены соответственно к первому управляющему выходу блока датчиков и к S-разрядному управляющему выходу блока управления. S-разрядный информационный выход блока вычисления обобщенного показателя подключен к S-разрядному информационному входу блока индикации. S-разрядные информационные вход и выход блока предварительных подсчетов баллов подключены соответственно к S-разрядным информационным выходу блока кодирования ответов и входу блока вычисления частных показателей. S-разрядный управляющий вход и управляющий вход блока предварительных подсчетов баллов подключены соответственно к S-разрядному второму управляющему выходу блока управления и к выходу БД. Четвертый управляющий вход БД подключен к выходу БС. Второй и третий синхронизирующие входы блока предварительных подсчетов баллов подключены соответственно к второму и третьему синхронизирующим выходам блока синхронизации, первый синхронизирующий выход которого подключен к синхронизирующему входу блока кодирования ответов. Четвертый и пятый синхронизирующие выходы блока синхронизации 8 подключены соответственно к второму и третьему синхронизирующим входам блока вычисления частных показателей. Шестой управляющий выход и четвертый управляющий вход блока управления подключены соответственно к первому управляющему входу и девятому выходу блока синхронизации. Второй управляющий вход блока синхронизации подключен к первому управляющему выходу блока датчиков. Блок синхронизации и блок управления снабжены соответственно F-разрядным, где F≥2, и W-разрядным, где W≥2, вводами исходных данных.

Блок предварительных подсчетов баллов состоит из каскадно включенных по S-разрядному информационному сигналу первого накопительного сумматора, делителя, умножителя и второго накопительного сумматора, первого и второго элементов «ИЛИ», выходы которых подключены соответственно к обнуляющим входам первого и второго накопительных сумматоров. S-разрядные информационные вход первого и выход второго накопительных сумматоров являются соответственно S-разрядными информационными входом и выходом блока промежуточных подсчетов баллов. Синхронизирующий вход делителя является вторым синхронизирующим входом блока промежуточных подсчетов баллов. Вход первого элемента «ИЛИ» и вход умножителя объединены и являются третьим синхронизирующим входом блока промежуточных подсчетов баллов. Первый вход второго элемента «ИЛИ» является четвертым управляющим входом блока промежуточных подсчетов баллов. Второй S-разрядный управляющий вход делителя и объединенные вторые входы первого и второго элементов «ИЛИ» являются соответственно S-разрядным шестым и пятым управляющими входами блока предварительных подсчетов баллов.

Блок вычисления обобщенного показателя состоит из каскадно включенных по S-разрядному информационному сигналу умножителя, накопительного сумматора, вычислителя квадратного корня и делителя. Первый S-разрядный информационный вход умножителя и третий S-разрядный информационный выход делителя являются соответственно S-разрядными информационными входом и выходом блока вычисления обобщенного показателя. S-разрядный управляющий вход делителя является шестым S-разрядным управляющим входом блока вычисления обобщенного показателя. Синхронизирующие вход умножителя, вход вычислителя квадратного корня и вход делителя являются соответственно третьим, четвертым и пятым синхронизирующими входами блока вычисления обобщенного показателя. Управляющий вход накопительного сумматора является вторым управляющим входом блока вычисления обобщенного показателя.

Блок синхронизации состоит из генератора тактовых импульсов, триггерного ключа, дешифратора, счетчика тактовых импульсов, компаратора, счетчика адреса, регистра памяти, элемента задержки и элемента «ИЛИ». Информационный выход компаратора подключен к входу «Стоп» триггерного ключа и через элемент задержки к информационному входу счетчика адреса D-разрядные, где D≥2, первый и второй информационные входы компаратора подключены соответственно к D-разрядным информационным выходу счетчика тактовых импульсов и выходу регистра памяти, R-разрядный, где R≥3 управляющий выход счетчика адреса подключен к R-разрядным управляющим входам регистра памяти и дешифратора. Информационный выход триггерного ключа подключен к информационному входу счетчика тактовых импульсов и информационному входу дешифратора. Выход генератора тактовых импульсов подключен к первому информационному входу триггерного ключа. Управляющий вход «Старт» триггерного ключа подключен к выходу элемента «ИЛИ», пятый вход которого является первым управляющим входом блока синхронизации. Информационные выходы дешифратора являются соответствующими синхронизирующими выходами блока синхронизации. Второй, четвертый, шестой и седьмой информационные выходы дешифратора подключены соответственно к первому, второму, третьему и четвертому входам элемента «ИЛИ». Информационный выход компаратора является девятым управляющим выходом блока синхронизации. Входы «Установка нуля» счетчика тактовых импульсов и счетчика адреса объединены и являются вторым управляющим входом блока синхронизации. D-разрядный информационный вход/выход и R-разрядный адресный вход регистра памяти образуют F-разрядный вход исходных данных блока синхронизации, где F=D+R.

Указанные в формуле изобретения буквенные обозначения имеют следующий смысл:

S - количество разрядов кода, соответствующего максимальному количеству баллов, начисляемых за решение одного тестового задания.

Р - количество разрядов кода, соответствующего максимальному количеству тестовых заданий.

D - количество разрядов кода, соответствующего максимальному количеству вопросов в тестовом задании.

М - количество разрядов кода, отражающего максимальный объем данных одного тестового задания.

R - количество разрядов адресного входа дешифратора БС (в рассматриваемом случае R≥3).

V - количество разрядов кода, соответствующего максимальному значению обобщенного показателя.

Q - количество разрядов кода, соответствующего количеству оцениваемых частных показателей (в рассматриваемом случае Q≥3).

U - количество разрядов, соответствующее разрядности управляющих входов графического ЖКИ.

Благодаря новым совокупностям существенных признаков при реализации устройства обеспечивается двухуровневая оценка общего показателя инновационного интеллекта, простота модификации структуры и содержания тестов и автоматизация всех процедур, т.е. повышение оперативности проведения исследований.

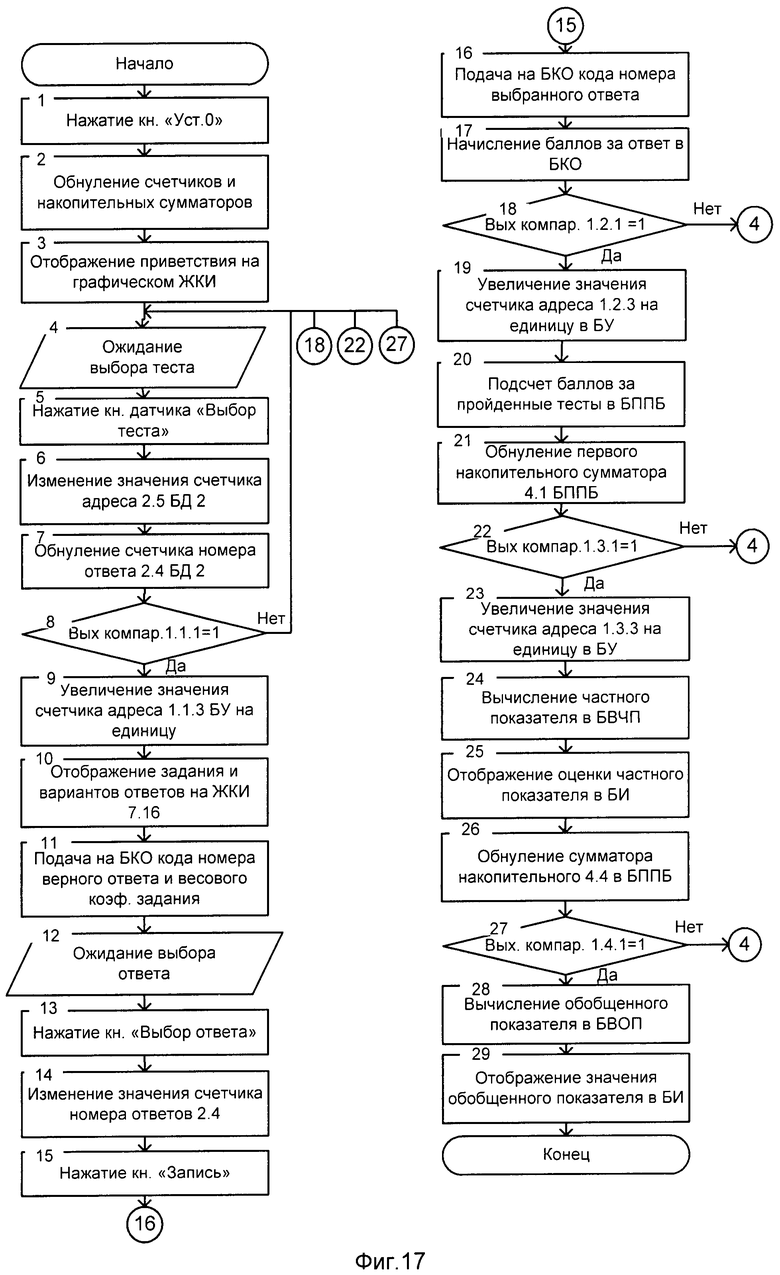

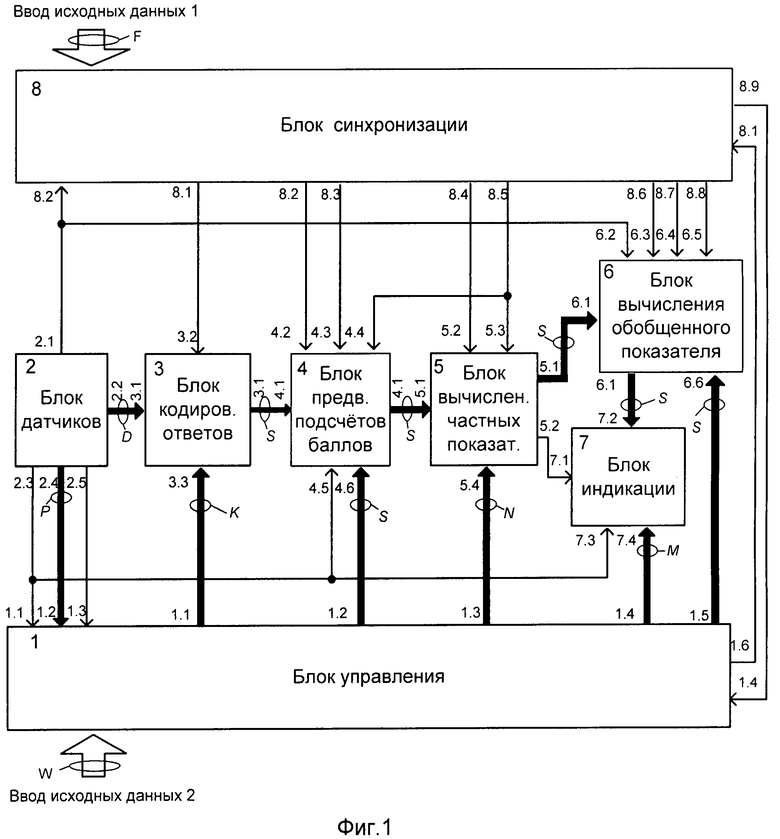

Изобретение поясняется чертежами, на которых показаны:

на фиг.1 - структурная схема устройства;

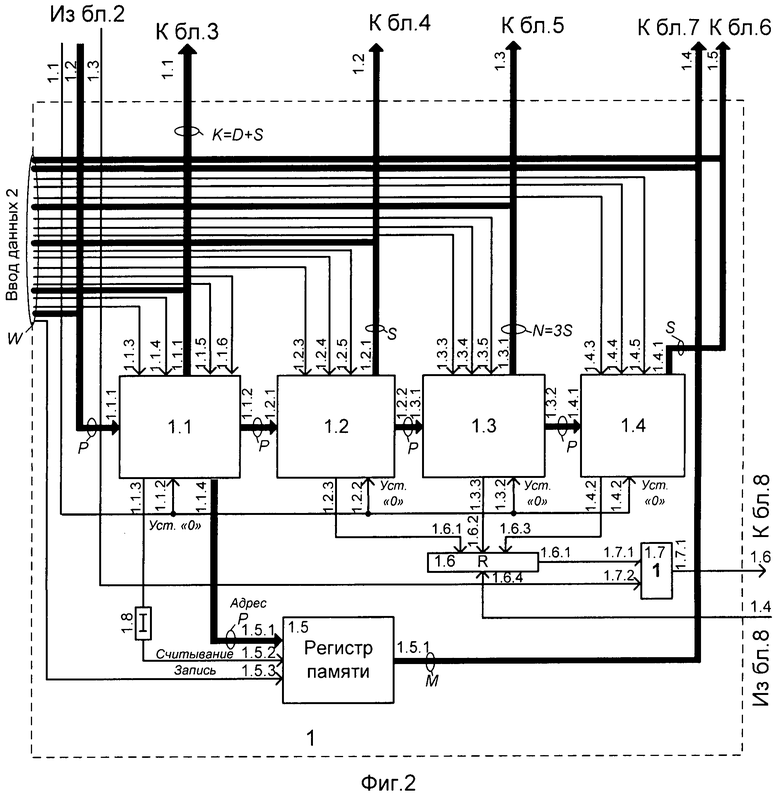

на фиг.2 - структурная схема блока управления (БУ);

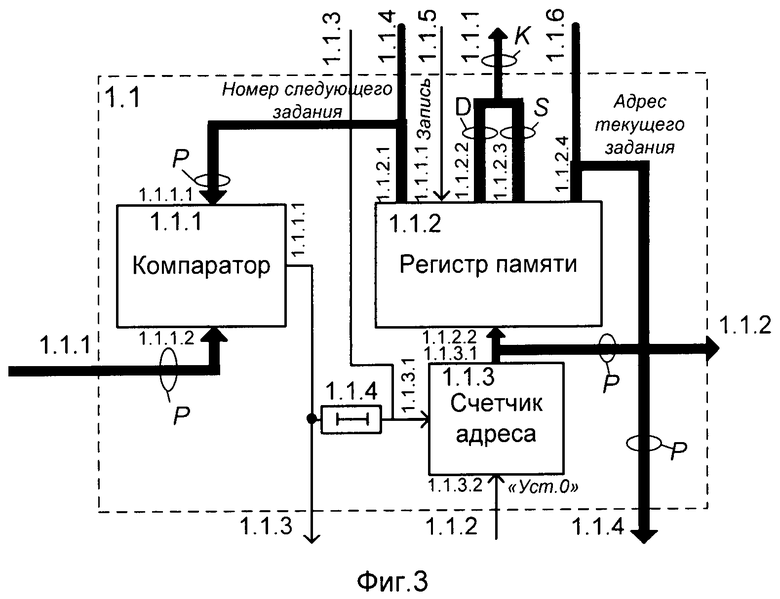

на фиг.3-6 - структурные схемы микропрограммных модулей блока управления;

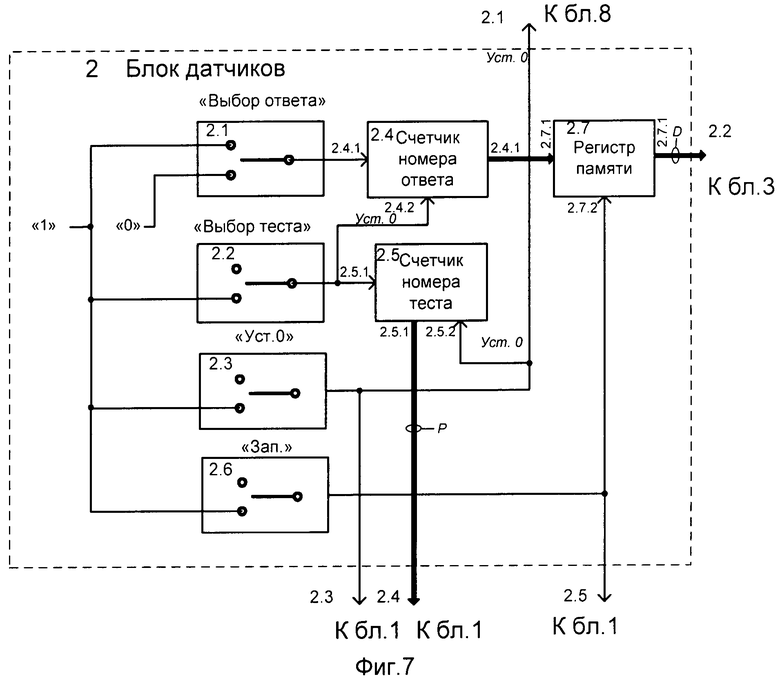

на фиг.7 - структурная схема блока датчиков (БД);

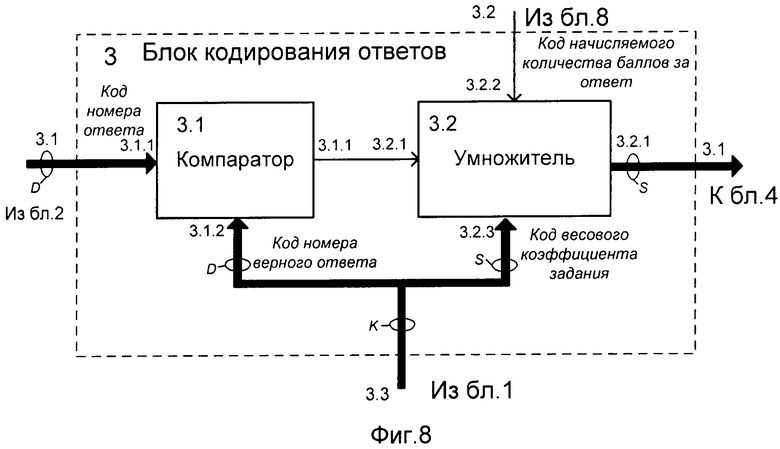

на фиг.8 - структурная схема блока кодирования ответов (БКО);

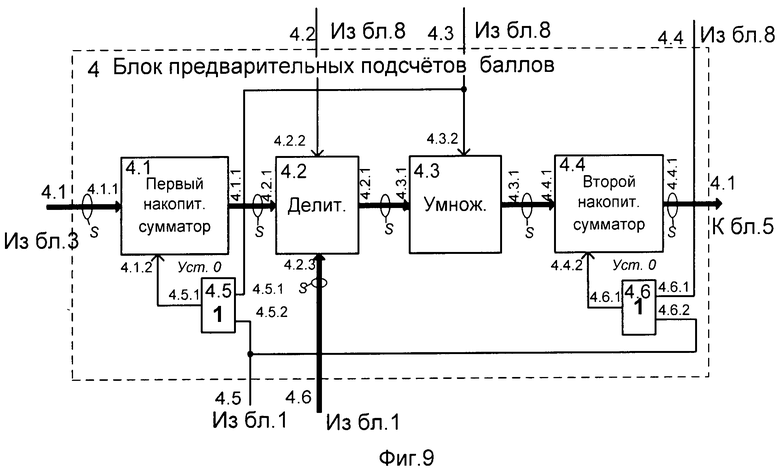

на фиг.9 - структурная схема блока предварительных подсчетов баллов (БППБ);

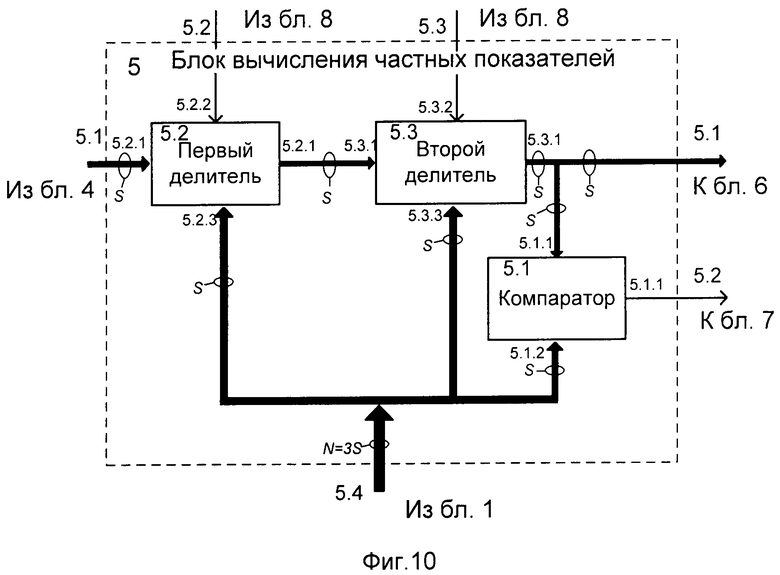

на фиг.10 - структурная схема блока вычисления частных показателей (БВЧП);

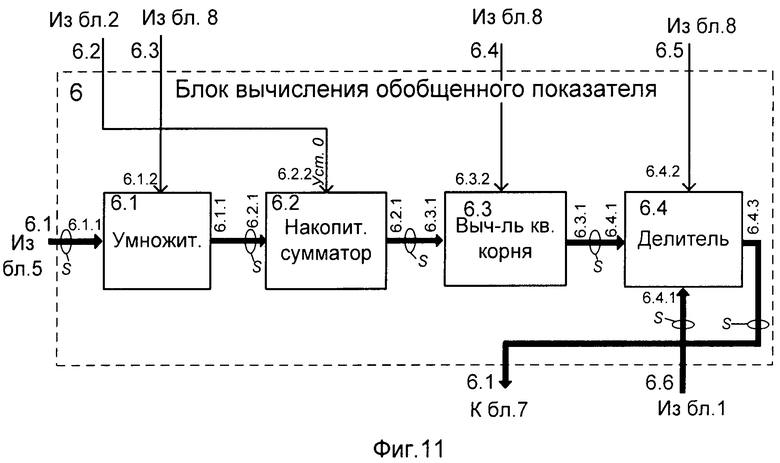

на фиг.11 - структурная схема блока вычисления обобщенного показателя (БВОП);

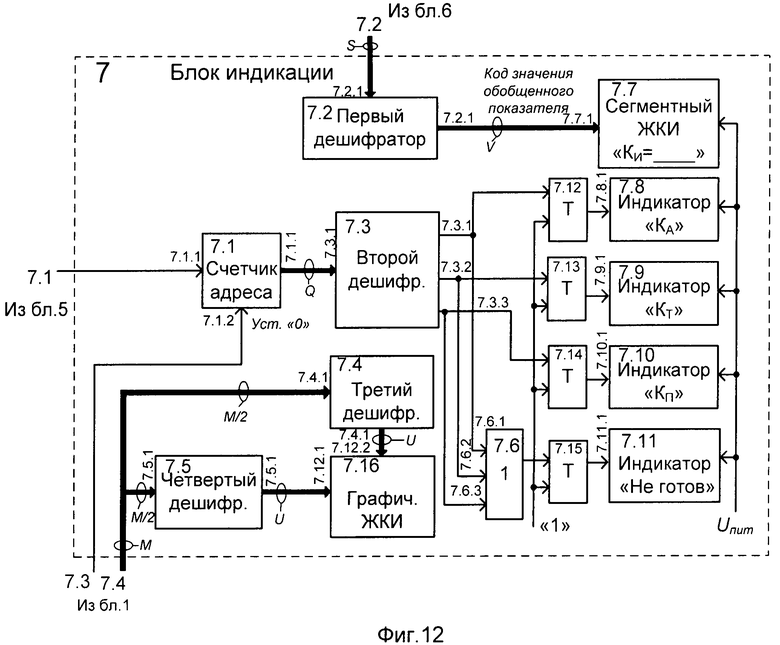

на фиг.12 - структурная схема блока индикации (БИ);

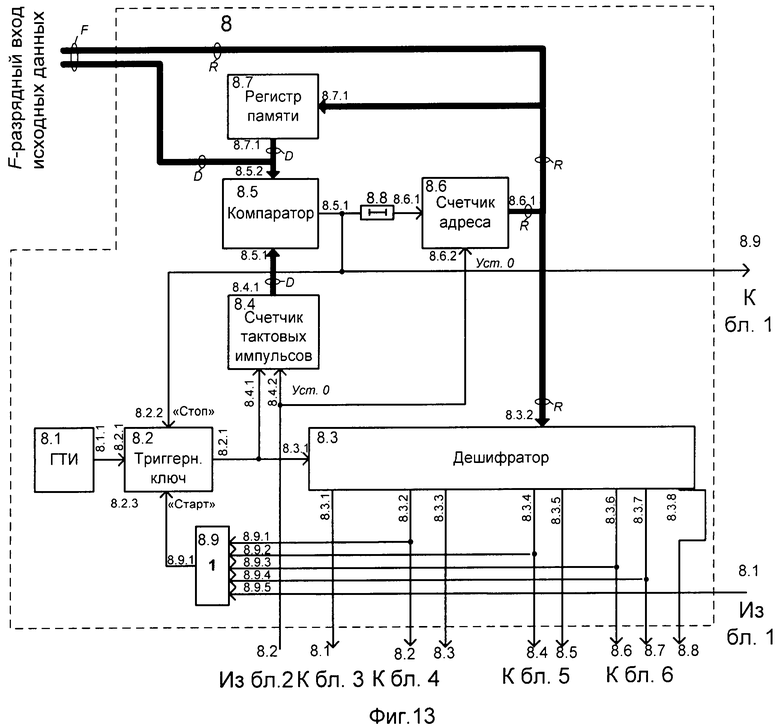

на фиг.13 - структурная схема блока синхронизации (БС);

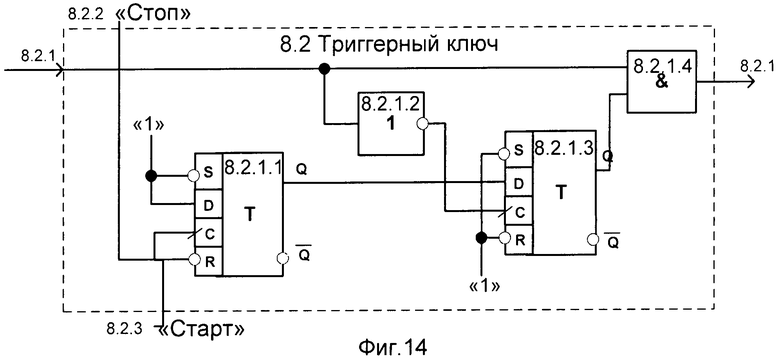

на фиг.14 - структурная схема триггерного ключа БС;

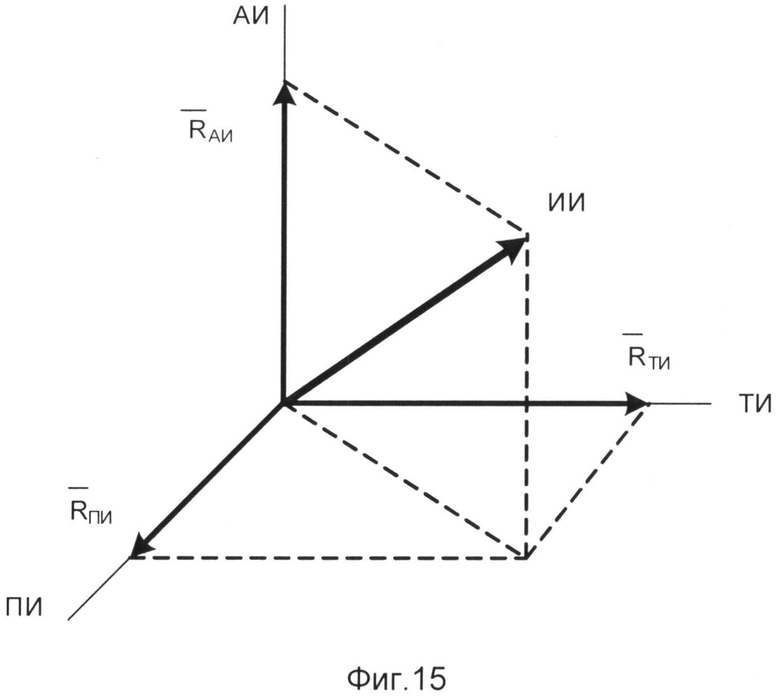

на фиг.15 - трехкомпонентная модель инновационного интеллекта;

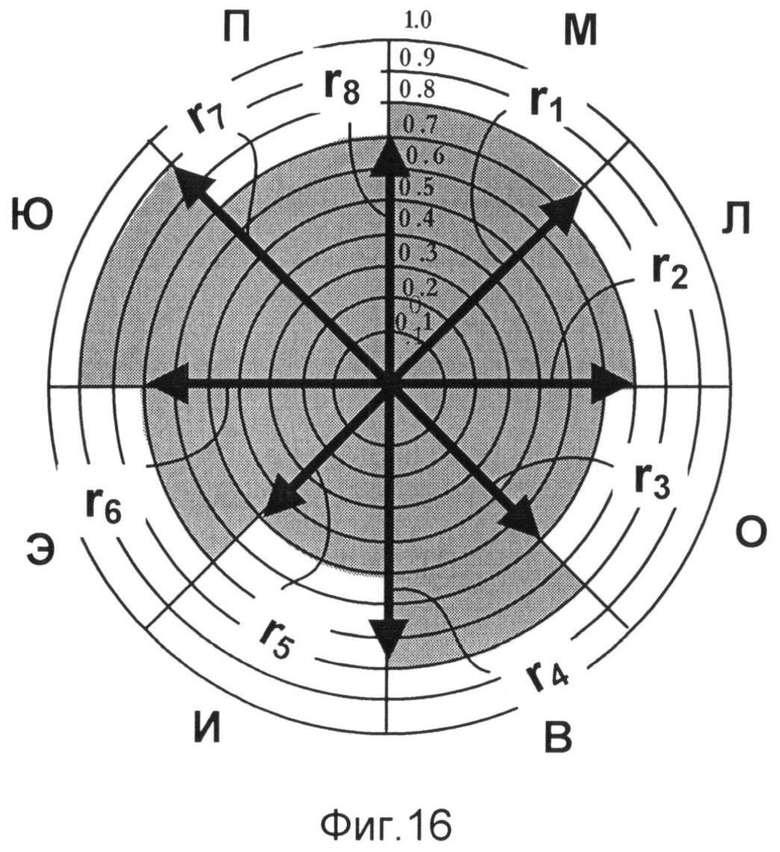

на фиг.16 - дискограмма оцениваемых показателей;

на фиг.17 - блок-схема алгоритма функционирования устройства.

Заявленное устройство, показанное на фиг.1, состоит из блока управления 1, блока датчиков 2, блока кодирования ответов 3, блока предварительных подсчетов баллов 4, блока вычисления частных показателей 5, блока вычисления обобщенного показателя 6, блока индикации 7, блока синхронизации 8.

D-разрядный, где D≥2 информационный выход 2.2 БД 2 подключен к D-разрядному информационному входу 3.1 БКО 3. Второй управляющий выход 5.2 БВОП 5 подключен к первому управляющему входу 7.1 БИ 7. N-разрядный, где N≥2 управляющий вход 5.4 БВЧП 5 подключен к N-разрядному управляющему выходу 1.3 БУ 1. Р-разрядный, где Р≥2, информационный вход 1.2 БУ 1 подключен к Р-разрядному управляющему выходу 2.4 БД 2. Пятый 2.5 управляющий выход БД 2 подключен к третьему 1.3 управляющему входу БУ 1. Третий управляющий выход 2.3 БД 2 подключен к первому управляющему входу 1.1 БУ 1 и третьему управляющему входу 7.3 БИ 7. K-разрядный 1.1 и M-разрядный 1.4, где К≥2 и М≥2 информационные выходы БУ 1 подключены соответственно к K-разрядному информационному входу 3.3 БКО 3 и к M-разрядному информационному входу 7.4 БИ 7. S-разрядный, где S≥2, информационный вход 6.1 БВОП 6 подключен к S-разрядному информационному выходу 5.1 БВЧП 5. Третий 6.3, четвертый 6.4 и пятый 6.5 синхронизирующие входы БВОП 6 подключены соответственно к шестому 8.6, седьмому 8.7 и восьмому 8.8 синхронизирующим выходам БС 8. Второй управляющий вход 6.2 и шестой управляющий 5-разрядный вход 6.6 БВОП 6 подключены соответственно к первому управляющему выходу 2.1 БД 2 и к S-разрядному управляющему выходу 1.5 БУ 1. S-разрядный информационный выход 6.1 БВОП 6 подключен к S-разрядному информационному входу 7.2 БИ 7. S-разрядные информационные вход 4.1 и выход 4.1 БППБ 4 подключены соответственно к S-разрядным информационным выходу 3.1 БКО 3 и входу 5.1 БВЧП 5. S-разрядный управляющий вход 4.6 и управляющий вход 4.5 БППБ 4 подключены соответственно к S-разрядному второму 1.2 управляющему выходу БУ 1 и к выходу 2.3 БД 2. Четвертый управляющий вход 4.4 БППБ 4 подключен к выходу 8.5 БС 8. Второй 4.2 и третий 4.3 синхронизирующие входы БППБ 4 подключены соответственно к второму 8.2 и третьему 8.3 синхронизирующим выходам БС 8. Первый синхронизирующий выход 8.1 БС 8 подключен к синхронизирующему входу 3.2 БКО 3. Четвертый 8.4 и пятый 8.5 синхронизирующие выходы БС 8 подключены соответственно к второму 5.2 и третьему 5.3 синхронизирующим входам БВЧП 5. Шестой 1.6 управляющий выход и четвертый 1.4 управляющий вход БУ 1 подключены соответственно к первому 8.1 управляющему входу и девятому 8.9 выходу БС 8. Второй управляющий вход 8.2 БС 8 подключен к первому 2.1 управляющему выходу БД 2, причем БС 8 и БУ 1 снабжены соответственно F-разрядным, где F≥2, и W-разрядным, где W≥2, вводами исходных данных.

Блок управления 1, структурная схема которого представлена на фиг.1, предназначен для хранения данных тестовых заданий, назначения весовых коэффициентов сложности тестовых заданий, а также для выдачи необходимых данных на основные блоки устройства. Реализация блока может быть различной, в частности, как показано на фиг.2, на основе принципа построения микропрограммного автомата [4, 5, 6].

БУ 1 осуществляет своевременную выдачу данных в такие элементы устройства, как умножители, делители, компараторы. Он состоит из четырех каскадно включенных по Р-разрядному, где Р≥2, управляющему сигналу типовых модулей 1.1, 1.2, 1.3, 1.4, которые реализуют принцип работы микропрограммного автомата, регистра памяти 1.5 для хранения данных тестовых заданий, регистра сдвига 1.6 с параллельной записью и последовательным считыванием из очереди типа FIFO, элемента «ИЛИ» 1.7 и элемента задержки 1.8. Первый 1.7.1, элемента «ИЛИ» подключен к первому 1.6.1 информационному выходу регистра сдвига 1.6, а второй 1.7.2 вход элемента ИЛИ 1.7 является третьим 1.3 управляющим входом БУ 1. Информационный выход 1.7.1 элемента «ИЛИ» 1.7 является шестым 1.6 управляющим выходом БУ 1. Первый 1.6.1, второй 1.6.2 и третий 1.6.3 информационные входы регистра сдвига 1.6 подключены соответственно к третьему 1.2.3 управляющему выходу второго модуля 1.2, третьему 1.3.3 управляющему выходу третьего модуля 1.3 и второму 1.4.2 управляющему выходу четвертого модуля 1.4. Четвертый управляющий вход 1.6.4 регистра сдвига 1.6 является четвертым 1.4 управляющим входом БУ 1. Третий 1.1.3 и Р-разрядный четвертый 1.1.4 управляющие выходы первого модуля 1.1 подключены соответственно через элемент задержки 1.8 к второму 1.5.2 и первому 1.5.1 управляющим входам регистра памяти 1.5. Четвертый 1.6.4 управляющий вход элемента «ИЛИ» 1.6 является третьим 1.3 управляющим входом БУ 1. Р-разрядный управляющий вход 1.1.1 первого модуля 1.1 является вторым 1.2 управляющим входом БУ 1. Обнуляющие входы «Уст. 0» 1.1.2, 1.2.2, 1.3.2, 1.4.2 модулей 1.1-1.4 объединены и образуют первый 1.1 управляющий вход БУ 1. Информационные выходы 1.1.1, 1.2.1, 1.3.1, 1.4.1 модулей 1.1, 1.2, 1.3, 1.4 являются соответственно K-разрядным первым 1.1, S-разрядным вторым 1.2, N-разрядным третьим 1.3 и S-разрядным четвертым 1.4 управляющими выходами БУ 1. M-разрядный, где М≥2, выход 1.5.1 регистра памяти 1.5 является пятым 1.5 управляющим выходом БУ 1.

Каждый типовой модуль, схемы которых показаны на фиг.3, 4, 5, состоит из компаратора 1.1.1-1.4.1, регистра памяти 1.1.2-1.4.2, счетчика адреса 1.1.3-1.4.3 и элемента задержки 1.1.4-1.4.4. Типовой модуль имеет следующую структуру, которую можно рассмотреть на примере первого модуля (см. фиг.3). Адресный вход 1.1.2.2 регистра памяти 1.1.2 подключен к информационному выходу 1.1.3.1 счетчика адреса 1.1.3, а первый информационный выход 1.1.2.1 регистра памяти 1.1.2 подключен к первому информационному входу 1.1.1.1 компаратора 1.1.1. Выход компаратора 1.1.1.1 подключен через элемент задержки 1.1.4 к информационному входу 1.1.3.1 счетчика адреса.

Первый модуль 1.1 (фиг.3) обеспечивает работу БКО 2. Второй информационный вход 1.1.1.2 компаратора 1.1.1 является первым управляющим входом 1.1.1 модуля 1.1. Второй управляющий вход 1.1.3.2 счетчика адреса 1.1.3 является вторым управляющим входом 1.1.2 модуля 1.1. Информационный выход 1.1.1.1 компаратора 1.1.1 является третьим 1.1.3 управляющим выходом модуля 1.1. D-разрядный второй 1.1.2.2 и S-разрядный третий 1.1.2.3 информационные выходы регистра памяти 1.1.2 образуют K-разрядный, где K=D+S, первый управляющий выход 1.1.1 модуля 1.1. P-разрядные первый информационный выход 1.1.3.1 счетчика адреса 1.1.3 и четвертый информационный выход 1.1.2.4 регистра памяти 1.1.2 являются соответственно вторым 1.1.2 и четвертым 1.1.4 управляющими выходами модуля 1.1. Первый 1.1.3.1 информационный вход счетчика адреса 1.1.3, первый 1.1.2.1, второй 1.1.2.2, третий 1.1.2.3, четвертый 1.1.2.4 информационные выходы и первый 1.1.1.1 управляющий вход «Запись» регистра памяти 1.1.2 используются для предварительного ввода исходных данных в модуль 1.1.

Второй модуль 1.2 (см. фиг.4) обеспечивает работу БППБ 4. Второй 1.2.1.2 информационный вход компаратора 1.2.1 является первым управляющим входом 1.2.1 модуля 1.2. Второй управляющий вход 1.2.3.2 счетчика адреса 1.2.3. является вторым 1.2.2 управляющим входом модуля 1.2. Выход компаратора 1.2.1 является третьим 1.2.3 управляющим выходом модуля 1.2. S-разрядный второй 1.2.2.2 информационный выход регистра памяти 1.2.2 и Р-разрядный первый 1.2.3.1 информационный выход счетчика адреса 1.2.3 являются соответственно первым 1.2.1 и вторым 1.2.2 управляющими выходами модуля 1.2. Первый 1.2.3.1 информационный вход счетчика адреса 1.2.3, первый 1.2.2.1 и второй 1.2.2.2 информационные выходы, а также первый управляющий вход «Запись» 1.2.2.1 регистра памяти 1.2.2 используются для предварительного ввода данных в модуль 1.2.

Третий модуль 1.3 обеспечивает работу БВЧП 5. Р-разрядный второй информационный вход 1.3.1.2 компаратора 1.3.1 и второй управляющий вход 1.3.3.2 счетчика адреса 1.3.3 являются соответственно первым 1.3.1 и вторым 1.3.2 управляющими входами модуля 1.3. Выход 1.3.1.1 компаратора 1.3.1 является третьим 1.3.3 управляющим выходом модуля 1.3. S-разрядные второй 1.3.2.2, третий 1.3.2.3 и четвертый 1.3.2.4 информационные выходы регистра памяти 1.3.2 образуют N-разрядный, где N=3S, первый 1.3.1 управляющий выход модуля 1.3. Р-разрядный первый выход 1.3.3.1 счетчика адреса 1.3.3 является вторым 1.3.2 управляющим выходом 1.3.2 модуля 1.3. Первый информационный вход 1.3.3.1 счетчика адреса 1.3.3, первый 1.3.2.1, второй 1.3.2.2, третий 1.3.2.3, четвертый 1.3.2.4 информационные выходы и первый 1.3.2.1 управляющий вход регистра памяти 1.3.2 используются для предварительного ввода исходных данных в модуль 1.3.

Четвертый модуль 1.4 обеспечивает работу БВОП 6. Р-разрядный второй информационный вход 1.4.1.2 компаратора 1.4.1 и второй управляющий вход 1.4.3.2 счетчика адреса 1.4.3 являются соответственно первым 1.4.1 и вторым 1.4.2 управляющими входами модуля 1.4. S-разрядный второй 1.4.2.2 информационный выход регистра памяти 1.4.2 является первым 1.4.1 управляющим выходом модуля 1.4. Выход 1.4.1.1 компаратора 1.4.1 является вторым 1.4.2 управляющим выходом модуля 1.4. Первый информационный вход 1.4.3.1 счетчика адреса 1.4.3, первый 1.4.2.1 и второй 1.4.2.2 информационные выходы и первый 1.4.2.1 управляющий вход регистра памяти 1.4.2 используются для предварительного ввода исходных данных в модуль 1.4.

Регистр сдвига 1.6 предназначен для обеспечения согласованной работы БУ 1 и БС 8. Через его информационные входы 1.6.1-1.6.3 записываются разрешающие сигналы, соответствующие логической единице и считываются по очереди от первого к третьему при поступлении тактовых импульсов на четвертый 1.6.4 вход регистра сдвига.

БД 2, схема которого представлена на фиг.7, предназначен для кодирования двоичным кодом номера теста и номера ответа, которые выбираются испытуемым, а также для установки в исходное состояние всех счетчиков устройства. БД 2 может быть реализован различным образом, например, как показано на фиг.7: с помощью двухпозиционных датчиков 2.1, 2.2, 2.3, 2.6, счетчика номера теста 2.5, реверсивного счетчика номера ответа 2.4 и регистра памяти 2.7. D-разрядный первый информационный вход 2.7.1 регистра памяти 2.7 подключен к D-разрядному информационному выходу 2.4.1 счетчика номера ответа 2.4. Второй управляющий вход 2.7.2 регистра памяти 2.7 подключен к выходу датчика «Запись» 2.6. Первый информационный вход 2.4.1 счетчика номера ответа 2.4 подключен к выходу датчика «Выбор ответа» 2.1, а второй обнуляющий вход 2.4.2 счетчика номера ответа подключен к выходу датчика «Выбор теста» 2.2. Первый информационный вход 2.5.1 счетчика номера теста 2.5 подключен к выходу датчика «Выбор теста» 2.2, а второй обнуляющий вход 2.5.2 счетчика номера теста 2.5 подключен к выходу датчика «Установка 0» 2.3. На входы датчика «Выбор ответа» 2.1 подаются потенциалы, соответствующие логическим нулю и единице, а на входы датчиков «Выбор теста» 2.2, «Установка 0» 2.3 и «Запись» 2.6 подается потенциал, соответствующий логической единице.

Выход датчика «Установка 0» 2.3 является первым 2.1 и третьим 2.3 управляющими выходами БД 2. D-разрядный выход регистра памяти 2.7 и P-разрядный выход 2.5.1 счетчика номера теста 2.5 являются соответственно вторым 2.2 и четвертым 2.4 информационными выходами БД 2. Выход датчика «Запись» 2.6 является пятым 2.5 управляющим выходом БД 2.

БКО 3 предназначен для определения количества баллов за выбранный ответ на тестовое задание в соответствии с предварительно заданными вестовыми коэффициентами заданий. БКО 3 может быть реализован различным образом, в частности, как показано на фиг.8.

БКО 3 состоит из компаратора 3.1 и умножителя 3.2. Первый информационный вход 3.2.1 умножителя 3.2 подключен к выходу 3.1.1 компаратора 3.1. Первый 3.1.1 информационный вход компаратора 3.1 и информационный выход 3.2.1 умножителя 3.2 являются соответственно D-разрядным информационными входом 3.1 и S-разрядным выходом 3.1 БКО 3, а второй вход 3.1.2 компаратора 3.1 и третий вход 3.2.3 умножителя 3.2 образуют K-разрядный управляющий вход БКО 3, где K=S+D. Второй синхронизирующий вход 3.2.2 умножителя является вторым 3.2 синхронизирующим входом БКО 3.

БППБ 4 предназначен для вычисления суммарного и среднего количества баллов, начисляемых по результатам выполнения тестовых заданий и подготовки исходных данных для вычисления частных показателей интеллекта. БППБ 4 может быть реализован различным образом, в частности, как показано на фиг.9.

БППБ 4 состоит из каскадно включенных по S-разрядному информационному сигналу первого накопительного сумматора 4.1, делителя 4.2, умножителя 4.3, второго накопительного сумматора 4.4, первого 4.5 и второго 4.6 элементов «ИЛИ». Умножитель 4.3 осуществляет возведение в квадрат числа, поступающего в двоичном коде на первый его вход 4.3.1.

Первый вход 4.1.1 первого и первый выход 4.4.1 второго накопительного сумматора являются соответственно информационным входом 4.1 и выходом 4.1 БППБ 4. Входы 4.5.2 и 4.6.2 первого 4.5 и второго 4.6 элементов «ИЛИ» являются пятым 4.5 управляющим входом БППБ 4. Первый вход 4.6.1 второго элемента «ИЛИ» является четвертым 4.4 управляющим входом БППБ 4. Синхронизирующие входы 4.2.2, 4.3.2 делителя 4.2 и умножителя 4.3 являются синхронизирующими входами 4.2 и 4.3 БПП 4. S-разрядный третий 4.2.3 управляющий вход делителя 4.2 является шестым 4.6 управляющим входом БППБ 4.

Начальная установка в исходное состояние накопительных сумматоров 4.1 и 4.4 осуществляется подачей на их управляющие входы 4.1.2 и 4.4.2 через первый 4.5 и второй 4.6 элементы «ИЛИ» потенциала логической единицы, который поступает через пятый 4.5 управляющий вход БППБ 4. Подготовка БППБ 4 к очередному этапу работы осуществляется обнулением накопительных сумматоров 4.1. и 4.4 тактовыми импульсами, поступающими через третий 4.3 и четвертый 4.4 синхронизирующие входы БППБ 4.

БВЧП 5 предназначен для вычисления значений частных показателей интеллекта и формирования по результатам вычисления информационного сигнала на БИ 7, а также для подготовки исходных данных для вычисления значения обобщенного показателя. БВЧП 5 может быть реализован различным образом, в частности, как показано на фиг.10.

БВЧП 5 состоит из каскадно включенных по S-разрядному информационному сигналу первого 5.2 и второго 5.3 делителей и компаратора 5.1.

Первый вход 5.2.1 первого делителя 5.2 и выход 5.3.1 второго делителя 5.3 являются соответственно информационными входом 5.1 и выходом 5.1 БВЧП 5. Выход компаратора 5.1 является вторым 5.2 управляющим выходом БВЧП 5. Синхронизирующие входы 5.2.2 и 5.2.3 делителей 5.2 и 5.3 являются соответственно вторым 5.2 и третьим 5.3 синхронизирующими входами БВЧП 5, а третьи информационные входы 5.2.3, 5.3.3 делителей 5.2 и 5.3 и второй информационный вход 5.1.2 компаратора 5.1 образуют управляющий N-разрядный вход 5.4 БВЧП 5, где N=3S.

БВОП 6 предназначен для вычисления значения обобщенного показателя интеллекта испытуемого и формирования информационного сигнала в БИ 7. БВОП 6 может быть реализован различным образом, в частности, как показано на фиг 11.

БВОП 6 состоит из каскадно включенных по S-разрядному информационному сигналу умножителя 6.1, накопительного сумматора 6.2, вычислителя квадратного корня 6.3 и делителя 6.4. S-разрядные вход 6.1.1 умножителя 6.1 и выход 6.4.3 делителя 6.4 являются соответственно информационным входом 6.1 и информационным выходом 6.1 БВОП 6. Синхронизирующие входы 6.1.2, 6.3.2, 6.4.2 умножителя 6.1, вычислителя квадратного корня 6.3 и делителя 6.4 являются синхронизирующими входами 6.3-6.5 БВОП 6. S-разрядный вход 6.4.1 делителя 6.4 и обнуляющий вход 6.2.2 накопительного сумматора 6.2 являются управляющими входами 6.6 и 6.2 БВОП 6.

БИ 7 предназначен для представления испытуемому содержания тестовых заданий, а также отображения результатов вычисления частных и обобщенного показателей интеллекта. БИ 7 может быть реализован различным образом, в частности, как показано на фиг.12.

БИ 7 состоит из счетчика адреса 7.1, дешифраторов 7.2-7.5, элемента «ИЛИ» 7.6, сегментного жидкокристаллического индикатора ЖКИ 7.7, индикаторов состояния 7.8-7.11, триггеров 7.12-7.15 и графического жидкокристаллического индикатора ЖКИ 7.16. Управление графическим ЖКИ 7.16 осуществляется через его входы 7.12.1 и 7.12.2, к которым подключены выходы 7.5.1 и 7.4.1 четвертого 7.5 и третьего 7.4 дешифраторов. Управление сегментным ЖКИ 7 осуществляется через его вход 7.7.1, к которому подключен выход 7.2.1 первого дешифратора 7.2. Управление индикаторами состояния 7.8-7.10 осуществляется через соответствующие входы 7.8.1-7.10.1, которые посредством триггеров 7.1.2-7.1.4 подключены к выходам 7.3.1-7.3.3 дешифратора 7.3. Индикатор «Не готов» 7.11 управляется через его вход 7.11.1, который посредством триггера 7.15 и элемента «ИЛИ» 7.6 подключен к выходам 7.3.1-7.3.3 второго дешифратора 7.3. Q-разрядный управляющий вход 7.3.1 второго дешифратора 7.3 подключен к выходу 7.1.1 счетчика адреса 7.1. Информационный вход 7.1.1 счетчика адреса 7.1 является первым информационным входом 7.1 БИ 7. S-разрядный информационный вход 7.2.1 первого дешифратора 7.2 является вторым 7.2 информационным входом БИ 7. М/2-разрядные информационные входы 7.4.1 и 7.5.1 третьего 7.4 и четвертого 7.5 дешифраторов образуют четвертый 7.4 M-разрядный информационный вход БИ 7. Второй 7.1.2 обнуляющий вход счетчика адреса 7.1 является третьим 7.3 управляющим входом БИ 7.

БС 8 предназначен для формирования синхронизирующих сигналов и выдачи их в другие блоки в соответствии с алгоритмом работы устройства, он обеспечивает согласованную работу таких элементов устройства, как умножители, делители и вычислитель квадратного корня. БС 8 может быть реализован различным образом, в частности, как показано на фиг.13.

БС 8 состоит из генератора тактовых импульсов 8.1, триггерного ключа 8.2, дешифратора 8.3, счетчика тактовых импульсов 8.4, компаратора 8.5, счетчика адреса 8.6 и регистра памяти 8.7, элемента задержки 8.8 и элемента «ИЛИ» 8.9. Информационный выход 8.5.1 компаратора 8.5 подключен к входу «Стоп» 8.2.2 триггерного ключа 8.2.2 и через элемент задержки 8.8 к информационному входу 8.6.1 счетчика адреса 8.6. D-разрядные первый 8.5.1 и второй 8.5.2 информационные входы компаратора 8.5 подключены соответственно к D-разрядным информационным выходу 8.4.1 счетчика тактовых импульсов 8.4 и выходу 8.7.1 регистра памяти 8.7. R-разрядный управляющий выход 8.6.1 счетчика адреса 8.6 подключен к R-разрядным управляющим входу 8.7.1 регистра памяти 8.7 и входу 8.3.2 дешифратора 8.3. Информационный выход 8.2.1 триггерного ключа 8.2 подключен к информационному входу 8.4.1 счетчика тактовых импульсов 8.4 и информационному входу 8.3.1 дешифратора 8.3. Выход 8.1.1 генератора тактовых импульсов 8.1 подключен к первому информационному входу 8.2.1 триггерного ключа 8.2. Управляющий вход «Старт» 8.2.3 триггерного ключа 8.2 подключен к выходу 8.9.1 элемента «ИЛИ» 8.9, пятый вход 8.9.5 которого является первым 8.1 управляющим входом блока синхронизации 8, а информационные выходы 8.3.1-8.3.8 дешифратора 8.3 являются соответствующими синхронизирующими выходами 8.1-8.8 блока синхронизации 8. Второй 8.3.2, четвертый 8.3.4, шестой 8.3.6 и седьмой 8.3.7 информационные выходы дешифратора 8.3 подключены к входам элемента «ИЛИ» 8.9. Входы «Установка нуля» 8.4.2 счетчика тактовых импульсов 8.4 и 8.6.2 счетчика адреса 8.6 объединены и являются вторым 8.2 управляющим входом блока синхронизации 8. D-разрядный информационный выход 8.7.1 и R-разрядный адресный вход 8.7.1. регистра памяти 8.7 образуют F-разрядный вход блока синхронизации 8 для ввода данных, где F=D+R.

Схема триггерного ключа 8.2 должна пропускать импульсы равной длительности. Триггерный ключ 8.2 может быть реализован различным образом, в частности, как показано на фиг.14. Он состоит из первого 8.2.1.1 и второго 8.2.1.3 RS-триггеров, элемента инверсии 8.2.1.2 и элемента «И» 8.2.1.4. Выход первого триггера 8.2.1.1 подключен к D-входу второго триггера 8.2.1.3. Выход второго триггера 8.2.1.3 подключен ко второму входу элемента «И» 8.2.1.4. Синхронизирующий вход второго триггера 8.2.1.3 подключен к выходу элемента инверсии 8.2.1.2. Входы элемента инверсии 8.2.1.2 и элемента «И» 8.2.1.4 объединены и образуют первый информационный вход 8.2.1 триггерного ключа 8.2. Инверсный R-вход первого триггера 8.2.1.1 является вторым 8.2.2 управляющим входом «Стоп» триггерного ключа 8.2. Синхронизирующий вход первого триггера 8.2.1.1 является третьим 8.2.3 управляющим входом «Старт» триггерного ключа. Выход элемента «И» 8.2.1.4 является первым 8.2.1 информационным выходом триггерного ключа 8.2. На D-вход, инверсный S-вход, первого триггера 8.2.1.1 и инверсные входы R и S второго триггера 8.2.1.3 подается потенциал логической единицы.

Все элементы описанных блоков устройства выполнены на стандартных потенциально-импульсных элементах и описаны в известной литературе:

- генератор тактовых импульсов [7] с.243-273, [1] с.96;

- делитель двоичных чисел [8, 9];

- умножитель двоичных чисел [8];

- дешифратор [7] с.112-127 [1] с.173-177;

- демультиплексор [7] с.128-134, [1] с.178-180, [2] с.76;

- компаратор [1] с.230-234;

- сумматор накопительный [1] с.149-150, 216-221, 228;

- счетчик [7] с.189-205, [1] с.102-106, 125-140, [2] с.96;

- реверсивный счетчик [1] с.106-108;

- умножитель [1] с.225-227;

- вычислитель корня квадратного [3];

- параллельный регистр сдвига [7] с.177-189, [1] с.144-148;

- регистровая память [1] с.272-274, [2] с.95;

- флеш-память [1] с.275-276;

- оперативные запоминающие устройства [1] с.263-272;

- триггеры [7] с.153-177, [1] с.65-80;

- триггерный ключ [1] с.93-94;

- сегментный жидкокристаллический индикатор [7] с.273-278;

- графический жидкокристаллический индикатор [10].

В основу заявленного устройства положен способ оценки инновационного интеллекта личности, известный по патенту РФ №2230490 от 20.06.2004 г. [Бюл. №17, 2004 г.]. В способе использована концепция трехвекторной модели инновационного интеллекта и графическое представление вычисляемых ее показателей как элементов части площади соответствующих секторов дискограммы единичной окружности, подробно описанной в [11, с.184-187].

Инновационный интеллект личности - это образ мыслей, позволяющий осознать и проанализировать возникшее в культуре противоречие и для его устранения выдвинуть идею и реализующее ее творческое решение, которого не было на предшествующих этапах развития культуры, после чего с учетом возможных последствий способствовать его социализации в культуре [11, с.44].

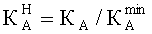

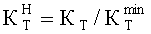

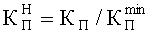

В трехвекторной модели инновационного интеллекта (ИИ) его составляющими являются; аналитический интеллект (АИ), творческий интеллект (ТИ) и практический интеллект (ПИ) (фиг.15). Указанные составляющие оцениваются соответствующими коэффициентами, которые являются частными показателями инновационного интеллекта: КА, КТ, КП.

Исходные данные включают минимально допустимые уровни

В рассматриваемом примере число субтестов и число полученных промежуточных частных численных результатов тестирования n=8. Значение показателя по каждому субтесту определяется путем подсчета числа совпадений ответов испытуемого с ответами ключа.

Исходными для дальнейшей оценки промежуточных психодиагностических показателей являются численные результаты тестирования по n субтестам. Нормирование значений промежуточных показателей выполняется путем деления полученных численных результатов по каждому субтесту на максимально возможный численный результат Pm по данному субтесту.

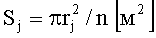

Дискограмма (фиг.17) представляет собой единичную окружность, радиус которой Rо=1. Для принятого шага дискретизации Δr число m вписанных в концентрических окружностей равно m=1/Δr-1. В данном случае, Δr=0,1, т.е. m=9.

Радиус i-й концентрической окружности ri=1-iΔr.

В рассматриваемом примере r1=1-1×0,1=0,9; r2=0,8 и т.д.

После нормирования значений численных результатов тестирования они округляются с учетом принятого шага дискретизации Δr. Например, полученные значения: МН=0,78; ЛН=0,71; ОН=0,58 и т.д., округляются до ближайшего значения, кратного Δr=0,1, т.е. после округления нормированные значения:

Округленные численные результаты по всем субтестам отображают на дискограмме путем штриховки части соответствующего сектора единичной окружности от ее центра до дуги вписанной концентрической окружности, радиус которой rj равен округленному численному результату соответствующего субтеста, т.е.

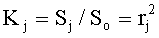

Полученные промежуточные результаты дают основание для определения как частных, так и обобщенного Кт психодиагностических показателей через соотношение заштрихованных Sj и общей So площадей соответствующих секторов. Этот факт обусловлен тем, что для достижения наивысших показателей тестируемый должен правильно ответить на все вопросы, что соответствует значениям всех частных показателей, равных единице, и, следовательно, заштрихованной окажется вся единичная окружность. При отличающихся от единицы частных показателях, заштрихованной окажется только часть единичной окружности (сектора). Соотношение заштрихованной и полной площадей единичной окружности (сектора) и показывает уровень суммарного (частного) показателя без привлечения каких-либо субъективных оценок исследователя.

Для единичной окружности полная площадь So ее любого j-го углового сектора So=π/n [м2]; площадь Sj заштрихованной части углового сектора на уровне вписанной концентрической окружности с радиусом rj равна

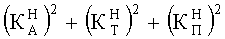

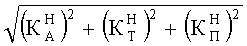

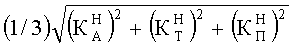

Обобщенный показатель инновационного интеллекта в соответствии с трехвекторной моделью (фиг.16) оценивается как среднеквадратическое значение нормированных частных показателей:

Нормированные значения частных показателей определяются по отношению к заданным минимальным допустимым значениям (

Полученные элементарные соотношения позволяют автоматизировать обработку и окончательную оценку психодиагностического показателя с помощью ЭВМ.

Таким образом, первое действие, выполняемое заявленным устройством - суммирование количества баллов РП за правильное выполнение субтестов.

Вторым действием устройства является нормирование промежуточных показателей тестирования путем деления по формуле (1).

Третьим действием является вычисление среднеквадратического значения по формуле (2), для чего необходимо выполнить:

а) возведение в квадрат

б) суммирование

в) деление на количество тестов в батарее тестов (1/т)

Четвертым действием является вычисление обобщенного показателя инновационного интеллекта по формуле (3), для чего необходимо выполнить:

а) деление:

б) возведение в квадрат:

в) суммирование:

г) вычисление корня квадратного:

д) деление:

В зависимости от целей, содержания и назначения теста качественная оценка уровней показателей: «низкий», «средний», «высокий» может быть различной. В частном случае применения тестов достижений, креативности или специальных способностей, представляющих психодиагностические методики для измерения соответствующих навыков, знаний, умений; творческих способностей или отдельных аспектов интеллекта и психомоторных функций, в зависимости от численных значений психодиагностических показателей К, соответствующие характеристики личности оцениваются как: «низкие» при К≤0,3; «средние» при 0,3<К≤0,6; «высокие» при К>0,6.

Пятым действием устройства является сравнение значений частных показателей с предварительно заданными значениями и отображение результатов оценки.

Заявленное устройство работает следующим образом.

Порядок работы устройства представлен блок-схемой алгоритма (фиг.15).

Предварительно в блок синхронизации БС 8 через «Ввод исходных данных 1» записываются данные, необходимые для согласования работы элементов устройства. В блок управления БУ 1 через «Ввод исходных данных 2» записывают данные тестовых заданий и данные, необходимые для вычисления частных и обобщенного показателей интеллекта. При этом запись содержания тестовых заданий осуществляется в регистр памяти 1.5 блока управления 1 (см. фиг.1, фиг.2) через его информационный выход 1.5.1 и адресный вход 1.5.1 при подаче потенциала логической единицы на управляющий вход «Запись» 1.5.3. Запись данных в регистры памяти микропрограммных модулей 1.1-1.4 БУ 1 осуществляется через соответствующие информационные выходы/входы регистров памяти и входы счетчиков адреса.

Устройство готовится к работе нажатием кнопки датчика «Установка 0» 2.3 БД 2, при этом все счетчики и накопительные сумматоры устройства устанавливаются в исходное (нулевое) состояние. На графическом жидкокристаллическом индикаторе 7.16 БИ 7 отображается информация приветствия из начального адреса регистра памяти 1.5 БУ. Устройство переходит в режим «Ожидание выбора теста».

Выбор первого или очередного теста осуществляется однократным нажатием на кнопку датчика «Выбор теста» 2.2 БД 2, при этом изменяется состояние счетчика номера теста 2.5 и двоичный код номера теста подается на выход 2.4 БД 2. При этом счетчик номера ответа 2.4 обнуляется, а с выхода 2.4 БД 2 двоичный код номера теста подается на второй вход 1.1.1.2 компаратора 1.1.1 первого 1.1 модуля БУ 1. Из начального адреса регистра памяти 1.1.2 на первый 1.1.1.1 вход компаратора 1.1.1 первого модуля БУ 1 подается двоичный код номера первого тестового задания. При совпадении двоичных кодов на входах компаратора 1.1.1 с его выхода 1.1.1.1 поступает потенциал логической единицы на вход 1.1.3.1 счетчика адреса 1.1.3. Счетчик адреса 1.1.3 изменяет свое состояние, и с его выхода поступает двоичный код адреса данных на вход 1.1.2.2 регистра памяти 1.1.2. Из соответствующей ячейки памяти регистра памяти 1.1.2 с его четвертого выхода 1.1.2.4 подается двоичный код адреса текущего задания через выход 1.1.4 модуля 1.1 на адресный вход 1.5.1 регистра памяти 1.5 БУ 1, а с первого выхода 1.1.2.1 регистра памяти 1.1.2 подается двоичный код номера следующего тестового задания на вход 1.1.1.1 компаратора 1.1.1. Из соответствующего адреса регистра памяти 1.5 через выход 1.4 БУ 1 данные подаются на вход 7.4 БИ 7, в результате чего на графическом жидкокристаллическом индикаторе 7.16 отображается содержание очередного тестового задания и варианты ответов к нему.

Из регистра памяти 1.1.2 первого модуля 1.1 через его выход 1.1.1 и выход 1.1 БУ 1 на второй вход 3.1.2 компаратора 3.1 БКО 3 подается двоичный код номера верного варианта ответа, а на вход 3.2.3 умножителя 3.2 БКО 3 подается двоичный код весового коэффициента тестового задания. Таким образом, устройство переходит в режим «Ожидания выбора ответа».

Выбор номера одного из вариантов ответа происходит нажатием кнопки датчика «Выбор ответа» 2.1 БД 2. При этом изменяется состояние реверсивного счетчика номера ответов 2.4. Двоичный код номера выбранного ответа с выхода счетчика номера ответа 2.4 поступает на вход регистра памяти 2.7 БД 2. При нажатии кнопки датчика «Запись» 2.6 двоичный код номера ответа записывается в регистр памяти 2.7 и через выход 2.2 БД 2, вход 3.1 БКО 3 подается на первый вход 3.1.1 компаратора 3.1 БКО 3. Если выбранный вариант ответа правильный, то коды на входах компаратора 3.1 совпадают и на его выходе 3.1.1 появляется потенциал логической единицы, который поступает на вход 3.2.1 умножителя 3.2 БКО 3. Если выбранный вариант ответа неверный, то с выхода 3.1.1 компаратора 3.1 поступает потенциал логического нуля на вход 3.2.1 умножителя 3.2.

Начисление баллов за верный ответ осуществляется подачей на второй синхронизирующий вход 3.2.2 умножителя 3.2 БКО 3 тактовых импульсов, которые формируются блоком синхронизации. Разрешающим сигналом для подачи тактовых импульсов на умножитель 3.2 является потенциал логической единицы, который поступает при нажатии кнопки датчика «Запись» 2.6. БД 2 через выход 2.5 БД, второй вход 1.7.2 элемента «ИЛИ» 1.7 на выход 1.6 БУ 1 и далее на вход 8.1 БС 8.

Таким образом, за верный ответ начисляется количество баллов, соответствующее весовому коэффициенту задания, а за неверный ответ начисляется нулевое количество баллов. Двоичный код, соответствующий количеству начисляемых баллов поступает с выхода 3.2.1 умножителя 3.2 через выход 3.1 БКО 3, вход 4.1 БППБ 4 на вход 4.1.1 первого накопительного сумматора 4.1 БППБ, который выполняет суммирование поступающего двоичного кода со своим исходным двоичным кодом.

БС 8 работает по принципу микропрограммного автомата [4, 5, 6], при этом количество подаваемых тактовых импульсов определяется предварительно записанными в регистр памяти 8.7 данными. Состояние счетчика адреса 8.6 определяет адрес выхода дешифратора 8.3, с которого подаются тактовые импульсы на соответствующие блоки устройства, а также адрес ячейки регистра памяти 8.7, в котором записан двоичный код соответствующего количества подаваемых на эти блоки тактовых импульсов. Из начального или очередного адреса регистра памяти 8.7. на второй информационный вход 8.5.2 компаратора подается двоичный код количества тактов для очередного этапа работы устройства. С выхода 1.8 БУ 1 потенциал логической единицы поступает через первый 8.1 вход БС 8, элемент «ИЛИ» 8.9 на вход «Старт» 8.2.3 триггерного ключа 8.2, который при этом открывается. С ГТИ 8.1 тактовые импульсы поступают на вход 8.3.1 дешифратора 8.3 и вход 8.4.1 счетчика тактовых импульсов 8.4. При совпадении кодов на входах компаратора 8.5, с его выхода 8.5.1 подается импульс на вход «Стоп» 8.2.2 триггерного ключа, который при этом закрывается и через выход 8.9 БС 8 на вход 1.4 БУ 1. Через элемент задержки 8.8 импульс от компаратора 8.5 поступает на счетчик адреса 8.6, он увеличивает свое значение на единицу и БС 8 приводится в готовность к следующему этапу работы устройства. Длительность управляющего импульса на выходе 8.5.1 компаратора 8.5 определяется интервалом задержки элемента задержки 8.8. На БППБ 4, БВЧП 5 последовательно подаются по две серии, а на БВОП 6 - три серии тактовых импульсов из БС 8, для чего выходы 8.3.2, 8.3.4, 8.3.6, 8.3.7 дешифратора подключены через элемент «ИЛИ» 8.9 к входу «Старт» 8.2.3 триггерного ключа 8.2.

Описанные этапы работы устройства повторяются до тех пор, пока компаратор 1.2.1 модуля 1.2 БУ 1 не зафиксирует равенства кодов «Количество заданий в тесте» на выходе регистра памяти 1.2.2 и выходе счетчика адреса 1.1.3 модуля 1.1 БУ 1.

Предварительный подсчет баллов включает в себя суммирование на первом накопительном сумматоре 4.1 БППБ 4 общего количества баллов за все выполненные тестовые задания первого (или очередного теста), вычисление на делителе 4.2 среднего количества баллов, начисленных за тест, вычисление суммы квадратов средних значений баллов за батарею тестов с помощью умножителя 4.3 и второго накопительного сумматора 4.4. На второй информационный вход 4.2.3 делителя 4.2 из регистра памяти 1.2.2 модуля 1.2 БУ 1 подается двоичный код, соответствующий значению количества тестовых заданий в тесте. На умножителе 4.3 выполняется возведение в квадрат значения среднего количества баллов за тест. С выхода умножителя код, соответствующий квадрату среднего количества баллов за тест подается на второй накопительный сумматор 4.4. Второй накопительный сумматор 4.4 осуществляет последовательное сложение поступающих на его вход двоичных кодов, в результате чего на его выходе формируется код, соответствующий сумме квадратов средних значений количества баллов, начисленных за пройденные тесты.

Разрешающим сигналом для поочередной подачи тактовых импульсов на делитель 4.2 и затем на умножитель 4.3 является импульс, поступающий с выхода 1.2.1.1 компаратора 1.2.1 через выход 1.2.3 модуля 1.2, регистр сдвига 1.6, элемента «ИЛИ» 1.7, выход 1.6 БУ 1 на вход 8.1 БС 8, через элемент «ИЛИ» 8.9 БС 8 на триггерный ключ 8.2. Длительность управляющего сигнала на выходе 1.2.1.1 компаратора 1.2.1 определяется интервалом элемента задержки 1.2.4 модуля 1.2.

Обнуление первого накопительного сумматора 4.1 для подготовки его к следующему тесту осуществляется тактовым импульсом, поступающим через вход 4.3 БППБ 4, первый элемент «ИЛИ» 4.5 на вход 4.1.2 первого накопительного сумматора 4.1.

Описанные этапы работы устройства повторяются до тех пор, пока компаратор 1.3.1 модуля 1.3 БУ 1 не зафиксирует равенство кодов «Количество тестов в батарее тестов» на выходе счетчика адреса 1.2.3 модуля 1.2 и на выходе регистра памяти 1.3.2.

Вычисление частного показателя включает в себя вычисление среднего значения количества баллов за батарею тестов на первом делителе 5.2, вычисление нормированного значения частного показателя на втором делителе 5.3, сравнение нормированного значения с предварительно заданным минимальным значением частного показателя на компараторе 5.1.

Потенциал логической единицы на выходе компаратора 1.3.1 модуля 1.3 БУ 1 является управляющим сигналом для счетчика адреса 1.3.3, по которому из соответствующего адреса регистра памяти 1.3.2 подаются данные для вычисления частного показателя. При этом двоичный код, соответствующий количеству тестов в батарее тестов и код, соответствующий нормировочному значению частного показателя, а также код, соответствующий минимально допустимому нормированному значению частного показателя с выходов 1.3.2.2-1.3.2.4 регистра памяти 1.3.2 модуля 1.3 подаются с выхода 1.5 БУ 1 через вход 5.4 БВЧП 5 на делители 5.2, 5.3 и компаратор 5.1 БВЧП 5.

Разрешающим сигналом для последовательной подачи серий тактовых импульсов на первый 5.2 и второй 5.3 делители является импульс, поступающий с выхода компаратора 1.3.1 модуля 1.3 БУ 1, через его выход 1.3.3, регистр сдвига 1.6, элемент «ИЛИ» 1.7, выход 1.6 БУ 1, на вход 8.1 БС 8. Элемент задержки 1.3.4 модуля 1.3 БУ 1 определяет длительность управляющего импульса на выходе 1.3.1.1 компаратора 1.3.1. По окончанию двух последовательных серий тактовых импульсов, поступающих из БС 8 на БВОП 5, на выходе 5.1 БВОП формируется двоичный код, соответствующий значению частного показателя.

Отображение оценки частного показателя осуществляется по сигналу с выхода 5.1.1 компаратора 5.1 БВЧП 5, который формируется при низком значении частного показателя относительно заданного минимального нормированного уровня. В данном случае, через вход 7.1 БИ 7 поступает потенциал логической единицы на вход 7.1.1 счетчика адреса 7.1, который изменяет свое состояние и подает двоичный код, соответствующий порядковому номеру вычисляемого частного показателя на вход дешифратора 7.3. С выходов 7.3.1-7.3.3 дешифратора 7.3 потенциал логической единицы подается на триггеры 7.12-7.14 для включения одного из индикаторов 7.3, 7.6, 7.7, а через элемент «ИЛИ» 7.1 и триггер 7.15 включается индикатор «Не готов» 7.2.

Обнуление второго накопительного сумматора 4.4 БППБ 4 для подготовки его к следующей батарее тестов осуществляется тактовым импульсом, поступающим через вход 4.4 БППБ 4, второй элемент «ИЛИ» 4.6 на второй вход 4.4.2 второго накопительного сумматора 4.4 БППБ 4.

Описанные этапы работы устройства повторяются до тех пор, пока компаратор 1.4.1 модуля 1.4 БУ 1 не зафиксирует равенство кодов «Количество батарей тестов» на выходе счетчика адреса 1.3.3 модуля 1.3 и на выходе регистра памяти 1.4.2 модуля 1.4 БУ 1.

Вычисление обобщенного показателя в БВОП 6 включает в себя вычисление суммы квадратов значений частных показателей с помощью умножителя 6.1 и накопительного сумматора 6.2, вычисление среднеквадратического значения частных показателей с помощью вычислителя квадратного корня 6.3 и делителя 6.4.

Потенциал логической единицы на выходе четвертого компаратора 1.4.1 модуля 1.4 БУ 1 является управляющим сигналом для счетчика адреса 1.4.3, по которому из регистра памяти 1.4.2 модуля 1.4 через его выход 1.4.1, выход 1.7 БУ 1, через вход 6.6 БВОП 6 подается на первый информационный вход 6.4.1 делителя 6.4 БВОП 6 двоичный код «Количество батарей тестов».

Разрешающим сигналом для подачи последовательных серий тактовых импульсов на умножитель 6.1, вычислитель квадратного корня 6.3 и делитель 6.4 БВОП 6 является импульс, который формируется на выходе 1.4.1.1 четвертого компаратора 1.4.1 модуля 1.4 и поступает через его выход 1.4.2, регистр сдвига 1.6, элемент «ИЛИ» 1.7 БУ 1 на выход 1.6 БУ 1, через вход 8.1 БС 8 и элемент «ИЛИ» 8.9 на вход «Старт» 8.2.3 триггерного ключа 8.2.

На завершающем этапе работы устройства разрешающие сигналы на БС 8 для подачи тактовых импульсов поступают из второго, третьего и четвертого модулей БУ 1 с задержкой, соответствующей параметрам элементов задержки 1.2.4-1.4.4. При этом своевременная подача очередного разрешающего сигнала из модулей БУ 1 на БС 8 обеспечивается регистром сдвига 1.6 БУ 1, который выполняет задержку разрешающих сигналов до момента завершения очередного этапа работы устройства. Синхронизирующим сигналом, обеспечивающим согласованную работу БУ 1 и БС 8 является импульс, поступающий с выхода 8.5.1 компаратора 8.5 БС 8 через его девятый выход 8.9, четвертый вход 1.4 БУ 1 на четвертый синхронизирующий вход 1.6.4 регистра сдвига 1.6.

Отображение результата вычисления обобщенного показателя осуществляется на сегментном жидкокристаллическом индикаторе 7.7, на который через V-разрядный выход дешифратора 7.2 подается код «Значение обобщенного показателя» с выхода делителя 6.4 БВОП 6.

Таким образом, введение новых узлов и конструктивных связей позволяет обеспечить оперативность, упростить масштабирование в зависимости от числа испытуемых, повысить достоверность оценки за счет возможности использования гетерогенных тестов и двухуровневой оценки с помощью частных и обобщенного показателя, обеспечить простую модификацию структуры и содержания тестов изменением исходных данных в микропрограммных автоматах устройства.

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ ИНФОРМАЦИИ

1. Наумкина Л.Г. Цифровая схемотехника. Конспект лекций по дисциплине «Схемотехника». - М.: Издательство «Горная книга», Издательство Московского горного университета, 2008. - 308 с.

2. Подъяков Е.А., Орлик В.В. Импульсные и цифровые устройства: Учебное пособие. - Новосибирск: Изд-во НГТУ, 2005. - 116 с.

3. Описание изобретения к авторскому свидетельству СССР №957209 от 07.09.89 «Устройство для извлечения квадратного корня» авторов А.Н.Флоренсов, В.И.Потапов, М.Ю.Плотников (Омский политехнический институт).

4. Самофалов К.Г., Романкевич A.M. и др. Прикладная теория цифровых автоматов. - Киев: «Вища школа», 1987.

5. Соловьев Г.Н. Арифметические устройства ЭВМ. - М. «Энергия». 1978.

6. Савельев А.Я. Прикладная теория цифровых автоматов - М. «Высшая школа». 1987.

7. Зибчук В.И., Сигорский В.П., Шкуро А.Н. Справочник по цифровой схемотехнике.

8. http://www.elektrotehno.ru/cfsxem_umndel.html.

9. Способ деления целых двоичных чисел без остатка, начиная с младших разрядов. И.П.Осинин.

10. http://www.display.by/ru/graphicmodules.htm.

11. Холодкова Л.А. Инновационная культура субъектов военного профессионального образования: теория и практика. Монография. - СПб.: ВУС, 2004. - 236 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРИБОР ДЛЯ РЕЙТИНГОВОЙ ОЦЕНКИ УРОВНЯ ГОТОВНОСТИ К ИННОВАЦИОННОЙ ДЕЯТЕЛЬНОСТИ | 2014 |

|

RU2548478C1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ РОЛЕВОЙ ФУНКЦИИ УЧАСТНИКА ТВОРЧЕСКОГО КОЛЛЕКТИВА | 2013 |

|

RU2541431C1 |

| Способ и устройство автоматизированного структурирования мультикультурных учебных групп | 2016 |

|

RU2618387C1 |

| УСТРОЙСТВО ВЫЧИСЛЕНИЯ МНОГОПАРАМЕТРИЧЕСКОГО ИНТЕГРАЛЬНОГО ПОКАЗАТЕЛЯ | 2017 |

|

RU2661749C1 |

| Цифровой анализатор спектра | 1987 |

|

SU1413545A1 |

| Адаптивный анализатор спектра | 1985 |

|

SU1291893A1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1997 |

|

RU2115135C1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО БИНС | 2011 |

|

RU2469376C1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ И ПРОВЕРКИ ЗАВЕРЕННОГО ЦИФРОВЫМ ВОДЯНЫМ ЗНАКОМ ЭЛЕКТРОННОГО ИЗОБРАЖЕНИЯ | 2009 |

|

RU2411579C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ОБУЧЕНИЕМ И ОЦЕНИВАНИЕМ ЗНАНИЙ ОБУЧАЮЩИХСЯ В СИСТЕМЕ ДИСТАНЦИОННОГО ОБУЧЕНИЯ | 2011 |

|

RU2467388C1 |

Изобретение относится к вычислительной технике, в частности к устройствам, используемым для психологических измерений интеллекта. Техническим результатом является повышение оперативности тестирования сложного конструкта инновационного интеллекта личности. Тестер состоит из блоков: управления 1, датчиков 2, кодирования ответов 3, предварительных подсчетов баллов 4, вычисления частных показателей 5, вычисления обобщенного показателя 6, индикации 7, синхронизации 8. Тестер снабжен: P-разрядным и W-разрядным входами исходных данных. Блоки управления 1 и синхронизации 8 совместно с другими блоками и соответствующими связями между ними обеспечивают возможность проведения тестирования произвольного числа испытываемых, оперативное изменение содержания тестов и обработку результатов тестирования. 3 з.п. ф-лы, 17 ил.

1. Тестер уровня инновационного интеллекта личности, содержащий блок датчиков, D-разрядный, где D≥2 информационный выход которого подключен к D-разрядному информационному входу блока кодирования ответов, блок вычисления частных показателей, второй управляющий выход которого подключен к первому управляющему входу блока индикации, а N-разрядный, где N≥2 управляющий вход блока вычисления частных показателей подключен к N-разрядному управляющему выходу блока управления 1, P-разрядный, где Р≥2, информационный вход которого подключен к Р-разрядному управляющему выходу блока датчиков, пятый управляющий выход которого подключен к третьему управляющему входу блока управления, а третий управляющий выход блока датчиков подключен к первому управляющему входу блока управления и третьему управляющему входу блока индикации, K-разрядный и M-разрядный, где K≥2 и М≥2 информационные выходы блока управления подключены соответственно к K-разрядному информационному входу блока кодирования ответов и к M-разрядному информационному входу блока индикации, отличающийся тем, что дополнительно введены блок синхронизации, блок предварительных подсчетов баллов, блок вычисления обобщенного показателя, S-разрядный, где S≥2, информационный вход которого подключен к S-разрядному информационному выходу блока вычисления частных показателей, третий, четвертый и пятый синхронизирующие входы блока вычисления обобщенного показателя 6 подключены соответственно к шестому, седьмому и восьмому синхронизирующим выходам блока синхронизации, второй управляющий вход и шестой управляющий S-разрядный вход блока вычисления обобщенного показателя подключены соответственно к первому управляющему выходу блока датчиков и к S-разрядному управляющему выходу блока управления, S-разрядный информационный выход блока вычисления обобщенного показателя подключен к S-разрядному информационному входу блока индикации, S-разрядные информационные вход и выход блока предварительных подсчетов балов подключены соответственно к S-разрядным информационным выходу блока кодирования ответов и входу блока вычисления частных показателей, S-разрядный управляющий вход и управляющий вход блока предварительных подсчетов баллов подключены соответственно к S-разрядному второму управляющему выходу блока управления и к выходу блока датчиков, а четвертый управляющий вход блока предварительных подсчетов баллов подключен к выходу блока синхронизации, второй и третий синхронизирующие входы блока предварительных подсчетов баллов подключены соответственно к второму и третьему синхронизирующим выходам блока синхронизации, первый синхронизирующий выход которого подключен к синхронизирующему входу блока кодирования ответов, а четвертый и пятый синхронизирующие выходы блока синхронизации подключены соответственно к второму и третьему синхронизирующим входам блока вычисления частных показателей, шестой управляющий выход и четвертый управляющий вход блока управления подключены соответственно к первому управляющему входу и девятому выходу блока синхронизации, а второй управляющий вход блока синхронизации подключен к первому управляющему выходу блока датчиков, причем блок синхронизации и блок управления снабжены соответственно F-разрядным, где F≥2, и W-разрядным, где W≥2, вводами исходных данных.

2. Устройство по п.1, отличающееся тем, что блок предварительных подсчетов баллов состоит из каскадно включенных по 5-разрядному информационному сигналу первого накопительного сумматора, делителя, умножителя и второго накопительного сумматора, первого и второго элементов «ИЛИ», выходы которых подключены соответственно к обнуляющим входам первого и второго накопительных сумматоров, причем S-разрядные информационные вход первого и выход второго накопительных сумматоров являются соответственно S-разрядными информационными входом и выходом блока промежуточных подсчетов баллов, синхронизирующий вход делителя является вторым синхронизирующим входом блока промежуточных подсчетов баллов, вход первого элемента «ИЛИ» и вход умножителя объединены и являются третьим синхронизирующим входом блока промежуточных подсчетов баллов, первый вход второго элемента «ИЛИ» является четвертым управляющим входом блока промежуточных подсчетов баллов, а второй S-разрядный управляющий вход делителя и объединенные вторые входы первого и второго элементов «ИЛИ» являются соответственно, S-разрядным шестым и пятым управляющими входами блока предварительных подсчетов баллов.

3. Устройство по п.1, отличающееся тем, что блок вычисления обобщенного показателя состоит из каскадно включенных по S-разрядному информационному сигналу умножителя, накопительного сумматора, вычислителя квадратного корня и делителя, причем первый S-разрядный информационный вход умножителя и третий S-разрядный информационный выход делителя являются соответственно S-разрядными информационными входом и выходом блока вычисления обобщенного показателя, S-разрядный управляющий вход делителя является шестым S-разрядным управляющим входом блока вычисления обобщенного показателя, синхронизирующие вход умножителя, вход вычислителя квадратного корня и вход делителя являются соответственно третьим, четвертым и пятым синхронизирующими входами блока вычисления обобщенного показателя, а управляющий вход накопительного сумматора является вторым управляющим входом блока вычисления обобщенного показателя.

4. Устройство по п.1, отличающееся тем, что блок синхронизации состоит из генератора тактовых импульсов, триггерного ключа, дешифратора, счетчика тактовых импульсов, компаратора, счетчика адреса, регистра памяти, элемента задержки и элемента «ИЛИ», информационный выход компаратора подключен к входу «Стоп» триггерного ключа и через элемент задержки к информационному входу счетчика адреса, D-разрядные, где D≥2, первый и второй информационные входы компаратора подключены соответственно к D-разрядным информационным выходу счетчика тактовых импульсов и выходу регистра памяти, R-разрядный, где R≥2, управляющий выход счетчика адреса подключен к R-разрядным управляющим входам регистра памяти и дешифратора, информационный выход триггерного ключа подключен к информационному входу счетчика тактовых импульсов и информационному входу дешифратора, выход генератора тактовых импульсов подключен к первому информационному входу триггерного ключа, управляющий вход «Старт» триггерного ключа подключен к выходу элемента «ИЛИ», пятый вход которого является первым управляющим входом блока синхронизации, а информационные выходы дешифратора являются соответствующими синхронизирующими выходами блока синхронизации, причем, второй, четвертый, шестой и седьмой информационные выходы дешифратора подключены соответственно к первому, второму, третьему и четвертому входам элемента «ИЛИ», информационный выход компаратора является девятым управляющим выходом блока синхронизации, входы «Установка нуля» счетчика тактовых импульсов и счетчика адреса объединены и являются вторым управляющим входом блока синхронизации, а D-разрядный информационный вход/выход и R-разрядный адресный вход регистра памяти объединены и являются F-разрядным входом исходных данных блока синхронизации, где F=D+R.

| ПРИБОР КОНТРОЛЯ ЗНАНИЙ | 1994 |

|

RU2110096C1 |

| СИСТЕМА ТЕСТИРОВАНИЯ "ТЕЛЕТЕСТИНГ" | 1998 |

|

RU2186423C2 |

| Автомат для сборки и завальцовки поддона с крышкой форменных пуговиц | 1949 |

|

SU89741A1 |

| US20030059750 A1, 27.03.2003 | |||

| US20100055655 A1, 04.03.2010 | |||

Авторы

Даты

2014-07-20—Публикация

2013-02-08—Подача