Изобретение относится к технике передачи сигналов и может использоваться в устройствах приема дискретных сигналов с неизвестным временем их прихода, работающих в условиях сильных импульсных помех.

Цель изобретения - исключение ис- кажений длительности принимаемых посылок сигнала.

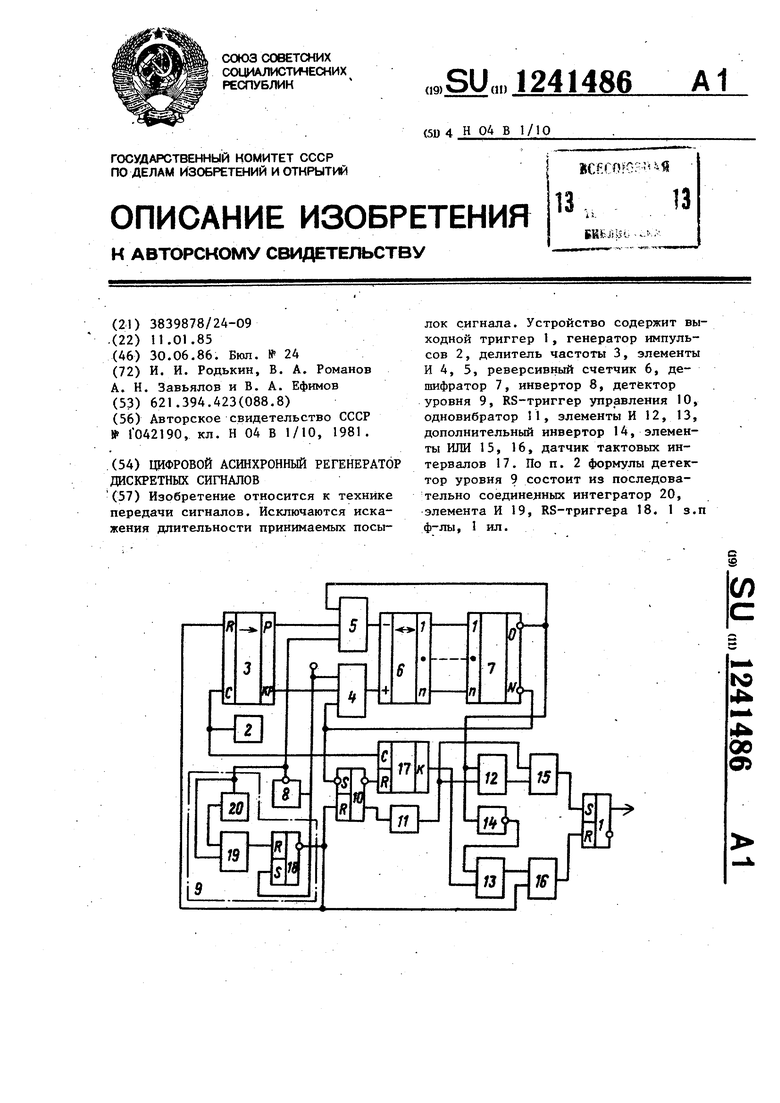

На чертеже изображена структурная электрическая схема предлагаемого .цифрового асинхронного регенератора. Цифровой асинхронный регенератор дискретных сигналов содержит выходной триггер 1, генератор 2 импульсов, делитель 3 частоты, элементы И 4 и 5, реверсивный счетчик 6, дешифратор 7, инвертор 8, детектор 9 уровня, RS- триггер 10 управления, од новибра- тор 11, элементы И 12 и 13, дополнительный инвертор 14, элементы ИЛИ 15 и 16, датчик 17 тактовых импульсов. Детектор 9 уровня состоит из RS-триг- гера 18, э.лемента И 19 и интеграто ра 20.

Цифровой асинхронный регенератор дискретных сигналов работает следующим образом.

При отсутствии сигнала на входе регенератора на выходе детектора 9 уровня присутствует сигнал, который образуется путем установки RS-триг- гера 18 в нулевое состояние по R- входу сигналом с выхода элемента И 19 Сигнал на выходе элемента И 19 образуется за счет поступающих с выхода инвертора 8 и интегратора 20 сигналов . Постоянная времени интегратора 20, например, интегрирующей RS-цепоч- ки, устанавливается больше максимального возможного времени существования во входном сигнале подряд идущих пауз (сигнала логического О), что обеспечивает надежное детектирование поступающих на вход регенератора сигналов . Сигналом с выхода детектора 9 удерживаются в исходном состоянии делитель 3 частоты по установочному входу, RS-триггер 10 по R-входу и выходной триггер 1 по входу установки нуля через элемент ИЛИ 16. Сигналом с -инверсного выхода RS-триггера 10 удерживается в исходном состоянии датчик 17 тактовых интервалов по установочному входу. В качестве датчика 17 может быть использован делитель частоты, построенньй, например, на интегральных микросхемах счетчи

. 10

15

20

25

414862

ков с программируемым,модулем, на- . пример, 564 ИЕ 19..

При поступлении на вход регенератора сигнала логической 1 сигнал на выходе детектора 9 уровня принимает нулевое значение и тем самым разрешается работа делителя 3 частоты RS-триггера 10 и выходного триггера 1,. Датчик 17 тактовых интервалов остается в не рабочем состоянии, так как на S-вход RS-триггера 10 еще не поступил сигнал. Поскольку только на одном выходе дешифратора 7 присутствует сигнал, то импульсы с первого выхода делителя 3 частоты, образованные путем деления частоты следо1зания импульсов генератора 2, поступают через элемент И 4 на суммирующий вход реверсивного счетчика 6. При поступлении числа импульсов, достаточного для заполнения ревер;г. сивного счетчика 6, дешифратор 7 формирует на выходе сигнал заполнения, который прекращает поступление через элемент И 4 на суммирующий вход реверсивного счетчика 6 импульсов и устанавливает по S-входу RS-триггер 10 управления регенерацией. Инверсия по S-входу RS-триггера 10 позволяет использовать в прямом виде сигнал с первого выхода дешифратора 7. Пере- ключе.ние RS-триггера 10 обеспечивает начало « юрмирования тактового интервала в датчике 17 и появление одиночного импульсного сигнала на выходе одновибратора 11, который поступает через первый элемент ИЛИ 15 на вход установки единицы выходного триггера 1. Таким образом на выходе регенератора устанавливается сигнал единичного уровня. Если сигнал логической 1 на входе регенератора сохраняется на протяжении тактового интервала, то датчик 17 тактовых интервалов формирует импульсный сигнал, который: через элемент И 12 и элемент ИЛИ 15 дублирует ранее произведенную одновибратором 11 установку выходного триггера 1 в единичное состояние. Прохождение импульса тактового интервала через элемент И 12 обеспечивает сигнал с другого выхода дешифратора 7, который, поступая через дополни- тельньй инвертор 14 на элемент И 13, запрещает поступление того же импуль- 55 са на вход установки нуля выходного триггера 1. Процесс поступления импульсов тактовых интервалов на вход установки единицы выходного триггера

30

35

40

45

50

3

протекает до тех пор, пока на входе

регенератора не происходит изменени значения сигнала с логической 1 н логический О.

Входной сигнал логическгго О,, постзшая через инвертор 8 на третий вход элемента И 5, разрешает поступление импульсов с второго выхода делителя 3 частоты на вычитающий вход реверсивного счетчика 6. Заполнение последнего уменьшается и при достижении нулевого состояния прекращается вследствие поступления сигнала с второго выхода дешифратора 7 на вход элемента И 5. Изменение сигнала на втором выходе дешифратора 7, вызванное обнулением реверсивного счетчика 6, обеспечивает прохождение импульса тактового интервала с датчика 17 тактовых интервалов через элемент И 13 и на вход установки нуля выходного триггера 1. Таким образом, завершается регенерация входного сигнала логической 1. Импульсы тактовых интервалов поступают на вход установки нуля выходного триггера 1 до тех пор, пока на входе регенератора не происходит смена значения сигнала.

Из описания процессов регенерации единичных и нулевых посьшок входного сигнала следует, что изменение значения сигнала на выходе регенератора происходит только в моменты окончания тактовых интервалов, формируемых датчиком 1 7 по сигналам генера .тора 2 импульсов, причем значения выходного сигнала определяются по результатам интегрирования единичных и нулевых посылок входного сигнала. Помехоустойчивое определение значения выходного сигнала достигается в результате установления различных значений постоянной времени интегрирования для единичных и нулевых посылок входного сигнала путем подачи на суммирующий и вычитающий входы реверсивного счетчика 6 импульсов с различной частотой следования, соответствующим выбором объема счетчика 6 и соответствующей настройки дешифратора 7. Чтобы исключить влияние импульсных помех, как наиболее вероятных, постоянная времени интегрирования единичных посылок устанавливается больше постоянной интегрирования нулевых посылок входного сигнала, что достигается подачей на суммирующий вход реверсивно414864

го счетчика 6 импульсов с выхода делителя 3 частоты, дающего большой коэффициент деления, на вычитающий вход счетчика 6 с выхода делителя 3 частоты, дающего меньший коэффициент деления частоты следования импульсов генератора 2.

При регенерации входного сигнала, имеющего дробления посылок, на длительности каждого тактового интерto

15

20

вала происходит чередование указанных процессов. Если суммарная длительность единичных отрезков больше суммар11ой длительности нулевых отрезков на величину постоянной интегрирования единичных посьшок, то для такого тактового интервала регенерируется единичная посыпка, в противном случае регенерируется нулевая посылка.

Формула изобретения

1. Цифровой асинхронный регенератор дискретных сигналов, содержащий выходной триггер, генератор импульсов, выход которого соединен с одним входом делителя частоты, выходы которого соединены с первыми входами первого и второго элементов И, выходы которых через реверсивный счетчик соединены с входами дешифратора, выходы которого соединены соответственно с вторыми входами первого и второго элементов И, третий вход

первого элемента И объединен с входом инвертора и является входом цифрового асинхронного регенератора, выход инвертора соединен с третьим входом второго элемента И, о т л и чающийся тем, что, с целью исключения искажений длительности принимаемых посьшок сигнала, в него введены детектор уровня, RS-триггер управления, одновибратор, датчик

тактовых интерваловJ третий и четвертый элементы И, два элемента ИЛИ и дополнительный инвертор, причем выход генератора импульсов соединен с первым входом датчика тактовых

интервалов, второй вход которого соединен с инверсным выходом RS- триггера управления, S-вход которого , соединен с одним из выходов дешифратора, R-вход - с выходом детектора

уровня, первый вход которого объединен с входом инвертора, выход которого соединен с вторым входом детектора уровня, прямой выход RS-трнггера

управления через одновибратор соединен с объединенными первыми входами третьего элемента И и первого элемента ИЛИ, выход датчика тактовых интервалов, соединен с первым входом четвертого элемента И, другой выход дешифратора соединен с вторым входом, третьего элемента И и через дополнительный инвертор с вторым входом четвертого элемента И, выход детектора уровня соединен с другим входом делителя частоты и первым входом второ го элемента ИЛИ, выходы третьего и четвертого элементов И соединены со- ответственно с вторыми входами обоих

Редактор С. Лисина

Заказ 3614/56Тираж 624Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

элементов ИЛИ, выходы которых соединены с соответствующими входами выходного триггера.

2. Регенератор по п. 1, отличающийся тем, что детектор уровня состоит из последовательно соединенных интегратора, элемента И,

0 RS-триггера, причем S-вход КЗ-триггера является первым входом детектора уровня, вход интегратора объединен с другим входом элемента И и является вторым входом детектора уровня,

5 выходом которого является выход RS-триггера.

Составитель Н. Лазарева

Техред О.Гортвай Корректор Г. Решетник

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой асинхронный регенератор дискретных сигналов | 1990 |

|

SU1788582A1 |

| Устройство для приема сигналов с относительной фазовой модуляцией | 1986 |

|

SU1356253A1 |

| Устройство для пуска синхронной @ -фазной машины | 1990 |

|

SU1823119A1 |

| ПРОТИВОУГОННАЯ СИСТЕМА | 1995 |

|

RU2086437C1 |

| Устройство для приема сигналов с относительной фазовой модуляцией | 1990 |

|

SU1714817A1 |

| Анализатор занятости канала связи | 1984 |

|

SU1225021A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

| Устройство для регулирования напряжения | 1982 |

|

SU1115198A1 |

| БЕСКОНТАКТНАЯ СИСТЕМА ЗАЖИГАНИЯ | 1991 |

|

RU2039884C1 |

Изобретение относится к технике передачи сигналов. Исключаются искажения длительности принимаемых посылок сигнала. Устройство содержит выходной триггер 1, генератор импульсов 2, делитель частоты 3, элементы И 4, 5, реверсивный счетчик 6, дешифратор 7, инвертор 8, детектор уровня 9, RS-триггер управления 10, одновибратор П, элементы И 12, 13, дополнительный инвертор 14, элементы ИЖ 15, 16, датчик тактовых интервалов 17. По п. 2 формулы детектор уровня 9 состоит из последовательно соединеяных интегратор 20, элемента И 19, RS-триггера 18. 1 з.п ф-лы, 1 ил. 4 )и 00 о

| Устройство для защиты электрических установок от сверхтоков | 1934 |

|

SU42190A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-06-30—Публикация

1985-01-11—Подача