Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычислительной техники при повышенных требованиях к массогабаритным и надежностным характеристикам.

Цель изобретения - повышение надежности.

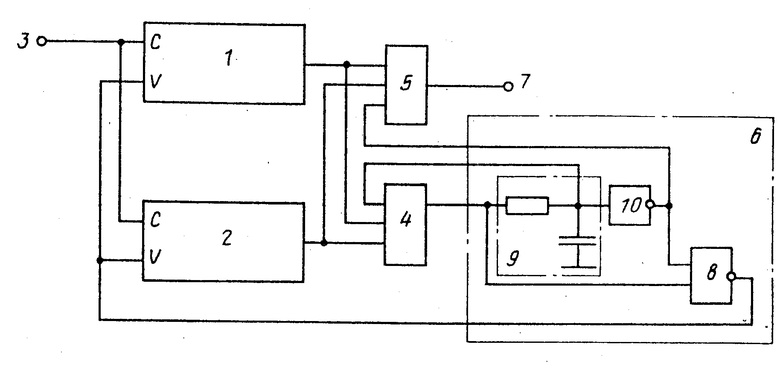

На чертеже приведена электрическая структурная схема устройства.

Резервированный делитель частоты содержит первый и второй делители 1 и 2 частоты, тактовые входы которых соединены с входной шиной 3, выходы - соответственно с первым и вторым входами первого и второго мажоритарных элементов 4 и 5, входы управления - с первым выходом формирователя 6 импульсов, второй выход которого соединен с третьим входом первого мажоритарного элемента 4, выход которого соединен с входом формирователя 6 импульсов, а третий выход соединен с третьим входом второго мажоритарного элемента 5, выход которого соединен с выходной шиной 7.

Формирователь 6 импульсов содержит элемент ИЛИ-НЕ 8, выход которого соединен с первым выходом формирователя 6 импульсов, вход которого соединен с первым входом элемента ИЛИ-НЕ 8 и через интегрирующую, например, резистивно-емкостную цепь 9 с вторым входом формирователя 6 импульсов и с входом инвертора 10, выход которого соединен с вторым входом элемента ИЛИ-НЕ 8 и с третьим выходом формирователя 6 импульсов.

Устройство работает следующим образом. В исходном состоянии делители 1 и 2 обнулены, на их выходах - логические сигналы низкого уровня, на выходах элементов 4 и 5 - логические сигналы низкого уровня, на выходе инвертора 10 - логический сигнал высокого уровня, на выходе элемента 8 - логический сигнал низкого уровня. На тактовые входы делителей 1 и 2 с шины 3 поступают импульсы входной частоты. По заполнении делителей 1 и 2 на половину их емкости на их выходах, если они исправны, одновременно появляются сигналы высокого уровня, в результате сигналы высокого уровня появляются на выходах элементов 4 и 5 и с задержкой на время, определяемое цепью 9, на выходе инвертора 10 появляется сигнал низкого уровня. По переполнении делителей 1 и 2 на их выходах появляются сигналы низкого уровня, т.е. делители 1 и 2 возвращаются в исходное состояние, в результате сигналы низкого уровня появляются на выходах элементов 4 и 5, на шине 7 и с задержкой на время, определяемое цепью 9, на выходе инвертора 10 появляется сигнал высокого уровня. В течение времени задержки, начиная с момента переполнения делителей 1 и 2, на входах элемента 8 присутствуют логические сигналы низкого уровня, а на его выходе формируется импульс в виде логического сигнала высокого уровня, который, действуя по входам управления делителей 1 и 2, подтверждает их исходное состояние. По прекращению импульса установки описанный выше цикл работы устройства повторяется.

Если в результате сбоя произойдет рассинхронизация делителей 1 и 2, то логический сигнал на выходе элемента 4 будет повторять форму на выходе отстающего делителя частоты, а логический сигнал на выходе элемента 5 - форму сигнала на выходе опережающего делителя частоты. По переполнении отстающего делителя частоты на выходе элемента 4 появится логический сигнал низкого уровня, а на выходе элемента 8 - импульс установки, который установит оба делителя 1 и 2 в исходное состояние. По окончании импульса установки с первого выхода формирователя 6 делители 1 и 2 начнут работать синхронно.

Если произойдет отказ, например, делителя 1, в результате которого он остановится в состоянии, когда на его выходе имеется логический сигнал низкого уровня, то первый же (считая с момента отказа) логический сигнал низкого уровня на выходе делителя 2 установит логический сигнал низкого уровня на выходе элемента 4 и с задержкой - логический сигнал низкого уровня на выходе инвертора 10. Таким образом, после данного отказа на первом входе элемента 5 установится логический сигнал низкого уровня, а на третьем входе - логический сигнал высокого уровня, и логические сигналы на шине 7 будут повторять форму сигналов на выходе исправного делителя 2.

Если произойдет отказ, например, делителя 1, в результате которого он остановится в состоянии, когда на его выходе имеется логический сигнал высокого уровня, то первый же (считая с момента отказа) логический сигнал высокого уровня на выходе делителя 2 установит логический сигнал высокого уровня на выходе элемента 4 и с задержкой - логический сигнал низкого уровня на выходе инвертора 10. Таким образом, после данного отказа на первом входе элемента 5 установится логический сигнал высокого уровня, а на третьем входе - логический сигнал низкого уровня, и логические сигналы на шине 7 будут повторять форму сигналов на выходе исправного делителя 2.

Если произойдет отказ, например, делителя 1, в результате которого его коэффициент деления уменьшится в два раза, причем, чаще всего, такой отказ приводит к рассинхронизации делителей частоты, то при первом же (считая с момента отказа) появлении на выходе элемента 4 логического сигнала низкого уровня на выходе элемента 8 сформируется импульс установки, после которого делители 1 и 2 будут работать синхронно, т.е. срез (переход логического сигнала с высокого уровня на низкий уровень) каждого импульса на выходе исправного делителя 2 будет совпадать со срезом каждого второго импульса на выходе неисправного делителя 1. По окончании импульса установки, восстановившего синхронность работы делителей 1 и 2, на их выходах и, следовательно, на выходах элементов 5 и 4 будут присутствовать логические сигналы низкого уровня, на выходе инвертора 10, а также на третьем входе элемента 5 будет присутствовать логический сигнал высокого уровня. Через четверть периода работы исправного делителя 2 неисправный делитель 1 отработает половину своего периода работы и на его выходе, а также на первом входе элемента 5 появится логический сигнал высокого уровня, который совместно с логическим сигналом на третьем входе элемента 5 приведет к появлению логического сигнала высокого уровня на его выходе. Через половину периода работы исправного делителя 7 на его выходе появится логический сигнал высокого уровня, и одновременно на выходе неисправного делителя 1 появится логический сигнал низкого уровня. В этот момент времени из-за гонки фронтов на выходах делителей 1 и 2 может сформироваться паразитный импульс или на выходе элемента 4, или на выходе элемента 5. Одним из критерием выбора параметров цепи 9 является условие tз > tпим, где tз - время задержки, tпим - максимально возможная длительность паразитного импульса. Следовательно, в обоих случаях на выходе цепи 9 сохранится логический сигнал низкого уровня, а на выходе инвертора 10 - сигнал высокого уровня и на выходе элемента 5 и на шине 7 после возможного паразитного импульса восстановится логический сигнал высокого уровня. Через три четверти периода работы исправного делителя 2 на выходе неисправного делителя 1 появится логический сигнал высокого уровня и с задержкой на время tз на выходе инвертора 10 - логический сигнал низкого уровня. На выходе элемента 5 сохранится логический сигнал низкого уровня. По переполнении исправного делителя 2 (в этот же момент переполнится и неисправный делитель 1) на выходах делителей 1 и 2 одновременно появятся логические сигналы низкого уровня, на выходах элементов 4 и 5 появятся логические сигналы низкого уровня, с задержкой на время tз на выходе инвертора 10 появится логический сигнал низкого уровня и на выходе элемента 8 сформируется импульс установки делителей 1 и 2 в исходное состояние, по окончании которого начнется следующий цикл работы устройства.

Таким образом, в результате указанного отказа на выходе резервированного делителя частоты (если не учитывать возможные короткие паразитные импульсы, которые, например, можно подавить с помощью дополнительной интегрирующей RC-цепи, установленной между выходом элемента 5 и шиной 7) частота импульсов не изменится. Из описания работы видно, что в данном устройстве исключается блокировка обоих делителей частоты при отказе одного из них.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1993 |

|

RU2111609C1 |

| САМОКОРРЕКТИРУЮЩИЙСЯ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2036554C1 |

| Устройство для управления @ -фазным преобразователем | 1983 |

|

SU1290463A1 |

| Мажоритарное устройство | 1983 |

|

SU1119196A1 |

| САМОКОРРЕКТИРУЮЩИЙСЯ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1986 |

|

SU1455980A1 |

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ (3 ВАРИАНТА) | 2014 |

|

RU2580791C2 |

| САМОКОРРЕКТИРУЮЩИЙСЯ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1984 |

|

SU1156570A1 |

| Устройство для перезапуска и контроля электропитания микроЭВМ | 1989 |

|

SU1797122A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1991 |

|

RU2036550C1 |

| Резервированное многоканальное устройство для формирования тактовых импульсов | 1990 |

|

SU1714607A1 |

Изобретение относится к импульсной технике и может использоваться в устройствах автоматики и вычислительной техники при повышенных требованиях к массогабаритным и надежностным характеристикам. Цель изобретения - повышение надежности - достигается за счет введения мажоритарных элементов 4 и 5 и организации новых функциональных связей. Устройство также содержит делители 1 и 2 частоты, формирователь 6 импульсов, входную и выходную шины 3 и 7. 1 з.п.ф-лы, 1 ил.

| САМОКОРРЕКТИРУЮЩИЙСЯ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1984 |

|

SU1156570A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1994-12-15—Публикация

1989-02-09—Подача