Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления, к которым предъявляются жесткие требования по исключению аварийного повышения тактовой частоты.

Цель изобретения - повышение надежности за счет исключения возможности аварийного повышения частоты на выход устройства в результате двойных отказов элементов.

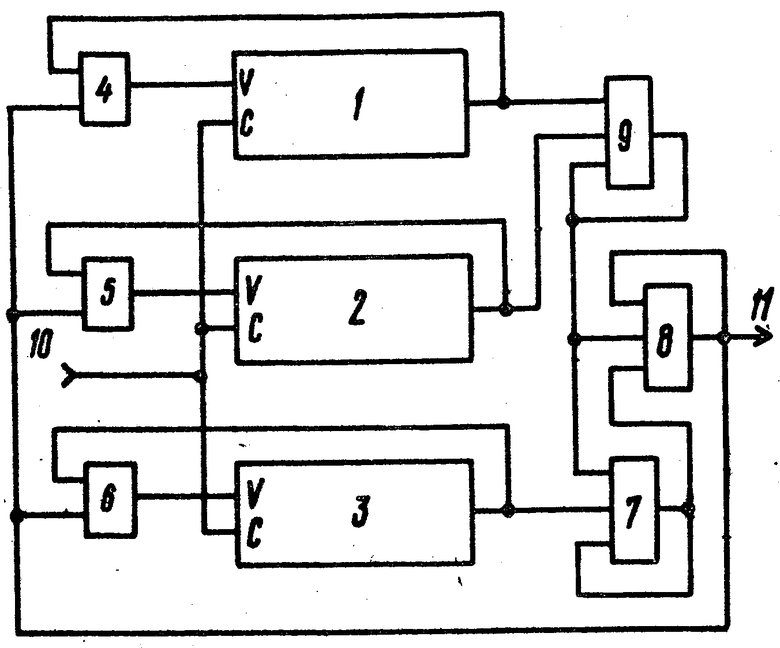

На чертеже приведена электрическая функциональная схема самокорректирующегося делителя частоты.

Устройство содержит первый, второй и третий делители 1, 2 и 3 частоты, первый, второй и третий элементы 4, 5 и 6 ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй и третий мажоритарные элементы 7, 8 и 9, входную и выходную шины 10 и 11, счетные входы первого, второго и третьего делителей 1, 2 и 3 частоты соединены с входной шиной 10, выходы - с первыми входами соответственно первого, второго и третьего элементов 4, 5 и 6 ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы которых соединены с выходной шиной 11, с выходом и с третьим входом второго мажоритарного элемента 8, выход третьего делителя 3 частоты соединен с первым входом первого мажоритарного элемента 7, второй вход и выход которого соединены с первым входом второго мажоритарного элемента 8, второй вход которого соединен с третьим входом первого мажоритарного элемента 7, с выходом и с первым входом третьего мажоритарного элемента 9, выходы первого и второго делителей 1 и 2 частоты соединены соответственно с вторым и третьим входами третьего мажоритарного элемента 9.

Устройство работает следующим образом.

В исходном состоянии делителя 1, 2 и 3 частоты обнулены, на их выходах - сигналы (логические) низкого уровня, на выходах элементов 7, 8 и 9 - сигналы низкого уровня, на управляющих входах делителей 1, 2 и 3 - сигналы низкого уровня, разрешающие их работу. На счетные входы делителей 1, 2 и 3 частоты поступают импульсы с шины 10. По заполнении делителей 1, 2 и 3 частоты на половину их емкости на их выходах сигналы высокого уровня появляются одновременно. На выходах элементов 7, 8 и 9 появляются сигналы высокого уровня, а на управляющих входах делителей 1, 2 и 3 частоты остаются сигналы низкого уровня, разрешающие дальнейшую их работу. По переполнении делителей 1, 2 и 3 частоты на их выходах появляются сигналы низкого уровня, на выходах элементов 7, 8 и 9 появляются сигналы низкого уровня, а на управляющих входах делителей 1, 2 и 3 частоты по-прежнему остаются сигналы низкого уровня, разрешающие работу делителей 1, 2 и 3 частоты. Далее начинается следующий цикл работы, аналогичный описанному (при исправных делителях 1, 2 и 3 частоты).

Если в одном из делителей 1, 2 и 3 частоты, например в первом, произошел отказ типа просчета триггера, который привел к уменьшению коэффициента деления, а, следовательно, и к уменьшению емкости делителя 1 частоты в два раза, устройство работает следующим образом. В исходном состоянии делители 1, 2 и 3 частоты обнулены, на их выходах - сигналы низкого уровня, на выходах элементов 7, 8 и 9 - сигналы низкого уровня, на управляющих входах делителей 1, 2 и 3 - сигналы низкого уровня, разрешающие их работу. Делитель 1 заполнителя на половину емкости через время Т/4, где Т - длительность цикла работы исправного делителя частоты. При этом на его выходе появится сигнал высокого уровня, а на выходах делителей 2 и 3 и элементов 7, 8 и 9 будут оставаться сигналы низкого уровня. На управляющем входе делителя 1 появится сигнал высокого уровня, запрещающий его работу, а на управляющих входах делителей 2 и 3 будут оставаться сигналы низкого уровня, разрешающие их работу. Через время Т/2 относительно начала цикла делители 2 и 3 заполняются на половину своей емкости и на их выходах появляются сигналы высокого уровня. На выходах элементов 7, 8 и 9 также появляются сигналы высокого уровня, что вызовет появление сигнала низкого уровня на управляющем входе делителя 1. Вторую половину цикла работы все три делителя 1, 2 и 3 частоты начинают одновременно с одинаковых состояний. Через время 3 Т/4 относительно начала цикла делитель 1 переполнится, на выходе его появится сигнал низкого уровня. На выходах делителей 2 и 3 и элементов 7, 8 и 9 будут оставаться сигналы высокого уровня. На управляющем входе делителя 1 появится сигнал высокого уровня, запрещающий его работу, а на управляющих входах делителей 2 и 3 будут оставаться сигналы низкого уровня, разрешающие их работу. По переполнении делителей 2 и 3 на их выходах появляются сигналы низкого уровня, на выходах элементов 7, 8 и 9 - сигналы низкого уровня, на управляющих входах делителей 1, 2 и 3 устанавливаются сигналы низкого уровня, разрешающие дальнейшую их работу. Далее начинается следующий цикл работы, аналогичный описанному.

Если произойдет двойной отказ, который приведет к уменьшению коэффициента деления, а следовательно, и к уменьшению емкости, например, делителей 1 и 2 в два раза, то устройство будет работать следующим образом. Через время Т/4 относительно начала цикла до половины своей емкости заполняется делители 1 и 2. При этом на их входах и на выходе элемента 9 появятся сигналы высокого уровня, однако на выходах делителя 3 и элементов 7 и 8 останутся сигналы низкого уровня. Поэтому на управляющих входах делителей 1 и 2 появятся сигналы высокого уровня, запрещающие их работу. Через время Т/2 относительно начала цикла до половины своей емкости заполнится делитель 3 и на его выходе, а также на выходах элементов 7 и 8 появятся сигналы высокого уровня, которые приведут к появлению на управляющих входах делителей 1, 2 и 3 сигналов низкого уровня, разрешающих их дальнейшую работу. Через время 3 Т/4 относительно начала цикла делители 1 и 2 переполнятся и на их выходах, а также на выходе элемента 9 появятся сигналы низкого уровня. Но на выходах делителя 3 и элементов 7 и 8 будут оставаться сигналы высокого уровня. Это приведет к появлению на управляющих входах делителей 1 и 2 сигналов высокого уровня, запрещающих их работу. По переполнении делителя 3 на его выходе, а также на выходах элементов 7 и 8 появятся сигналы низкого уровня, что приведет к появлению сигналов низкого уровня, на управляющих входах делителей 1, 2 и 3, после чего начнется следующий цикл работы делителя, аналогичный описанному.

Отказ от одного из делителей частоты, например первого, который приводит к уменьшению коэффициента деления, в сочетании с отказом соответствующего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ типа "Ложный 0 на выходе" приводит к повышению частоты на выходе данного делителя, но не приводит к повышению частоты на выходе устройства. Аналогичный отказ одного из делителей, например третьего, в сочетании с отказом соответствующего ему первого мажоритарного элемента, который приводит к пропусканию сигналов с первого входа мажоритарного элемента на его выход независимо от сигналов на его втором и третьем входах, не приводит к повышению частоты на выходе устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1989 |

|

SU1579423A1 |

| САМОКОРРЕКТИРУЮЩИЙСЯ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2036554C1 |

| УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ | 2000 |

|

RU2175167C1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1991 |

|

RU2036550C1 |

| РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1993 |

|

RU2111609C1 |

| Резервированный генератор | 1978 |

|

SU746975A1 |

| УСТРОЙСТВО ДЛЯ МАЖОРИТАРНОГО ВЫБОРА СИГНАЛОВ (3 ВАРИАНТА) | 2014 |

|

RU2580791C2 |

| Мажоритарно-резервированное счетное устройство | 1986 |

|

SU1363216A1 |

| Устройство для мажоритарного выбора асинхронных сигналов | 1982 |

|

SU1115255A1 |

| Резервированный генератор импульсов | 1983 |

|

SU1188920A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления, к которым предъявляются требования по исключению аварийного повышения тактовой частоты. Изобретение позволяет повысить надежность за счет исключения возможного аварийного повышения частоты на выходе устройства в результате двойных отказов элементов. Для этого в устройство дополнительно введены мажоритарные элементы 7, 8 и 9 и делитель 3 частоты. Кроме того, устройство содержит делители 1 и 2 частоты, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 4, 5 и 6, входную 10 и выходную 11 шины. Отказ одного из делителей частоты, например первого, который приводит к уменьшению коэффициента деления, в сочетании с отказом соответствующего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ типа "Ложный О на выходе" приводит к повышению частоты на выходе данного делителя, но не приводит к повышению частоты на выходе устройства. 1 ил.

САМОКОРРЕКТИРУЮЩИЙСЯ ДЕЛИТЕЛЬ ЧАСТОТЫ, содержащий первый и второй делители частоты, счетные входы которых соединены с входной шиной, выходы - с первыми входами соответственно первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, третий элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и выходную шину, отличающийся тем, что, с целью повышения надежности, в него введены первый, второй и третий мажоритарные элементы и третий делитель частоты, счетный вход которого соединен с входной шиной, выход - с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с первым входом первого мажоритарного элемента, второй вход и выход которого соединены с первым входом второго мажоритарного элемента, второй вход которого соединен с первым входом и выходом третьего мажоритарного элемента, второй и третий входы которого подключены к выходам соответственно первого и второго делителей частоты и с третьим входом первого мажоритарного элемента, третий вход и выход - с выходной шиной и с вторыми входами первого, второго и третьего элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых соединены с управляющими входами соответственно первого, второго и третьего делителей частоты.

| САМОКОРРЕКТИРУЮЩИЙСЯ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1984 |

|

SU1156570A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-01-20—Публикация

1986-10-14—Подача