Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известен резервированный делитель частоты, содержащий три канала, каждый из которых состоит из счетчика импульсов на IK-триггерах, счетный вход первого из которых соединен с входной шиной, мажоритарного элемента, входы которого соединены с выходами счетчиков импульсов каждого канала, и логического элемента эквивалентности, входы которого соединены с выходами счетчика импульсов и мажоритарного элемента данного канала, а выход подключен к I- и K-входам первого IK-триггера счетчика импульсов данного канала.

Недостаток этого известного устройства состоит в значительной сложности при необходимости получить высокую надежность функционирования.

Наиболее близким по технической сущности является самокорректирующийся делитель частоты, содержащий два канала деления, каждый из которых состоит из делителя частоты, счетные входы и выходы которых соединены с соответствующими входными и выходными шинами, блока контроля и элемента памяти, при этом входы элемента памяти каждого канала подключены к выходам блока контроля, а выход - к входу блока контроля и входу управления делителя частоты, выход которого через элемент задержки соединен с входом элемента памяти другого канала деления, блок контроля каждого канала состоит из контрольного делителя частоты, первого и второго элементов совпадение и инвертора, выход делителя частоты подключен к первым входам элементов совпадения, выход контрольного делителя частоты подключен к второму входу первого элемента совпадения и через инвертор - к второму входу второго элемента совпадения, выходы элементов совпадения соединены с входами элементами памяти.

Недостатком этого устройства является низкая надежность функционирования за счет невозможности при ее использовании обеспечить полную автономность каналов. Автономность каналов предполагает, что для исключения влияния неисправного канала по тепловому потоку, элементы разных каналов должны быть разделены конструктивно и не должны объединяться в составе корпусов функциональных узлов (например, в корпусах микросхем общего применения). Питание каждого из каналов должно осуществляться от автономных источников. Из этих требований следует, что наличие функциональных связей между каналами существенно затрудняет их согласование из-за того, что они имеют разные источники питания. Так, например, для КМОП интегральных микросхем существуют жесткие ограничения по параметрам указанного согласования, оно должно производиться с помощью специальных устройств, что приводит к дополнительным затратам.

Цель изобретения - повышение надежности функционирования.

Поставленная цель достигается тем, что в самокорректирующийся делитель частоты, содержащий первый и второй делители частоты, счетные входы и выходы которых соединены с соответствующими входными и выходными шинами, элемент памяти и первый и второй элементы совпадения, введены элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и первый и второй формирователи импульсов, входы которых соединены с выходом соответственно первого и второго делителей частоты, первые выходы - соответственно с первым и вторым входами элемента памяти, вторые выходы - соответственно с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первыми входами первого и второго элементов совпадения, вторые входы которых соединены с соответствующими выходами элемента памяти, а выходы - с входами управления соответствующих делителей частоты, кроме того, тем, что формирователь импульсов самокорректирующегося делителя частоты содержит интегрирующую, например RC, цепь и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с входом интегрирующей цепи и входом фоpмирователя импульсов, выход - с первым выходом формирователя импульсов, второй вход - с выходом интегрирующей цепи и с вторым выходом формирователя импульсов.

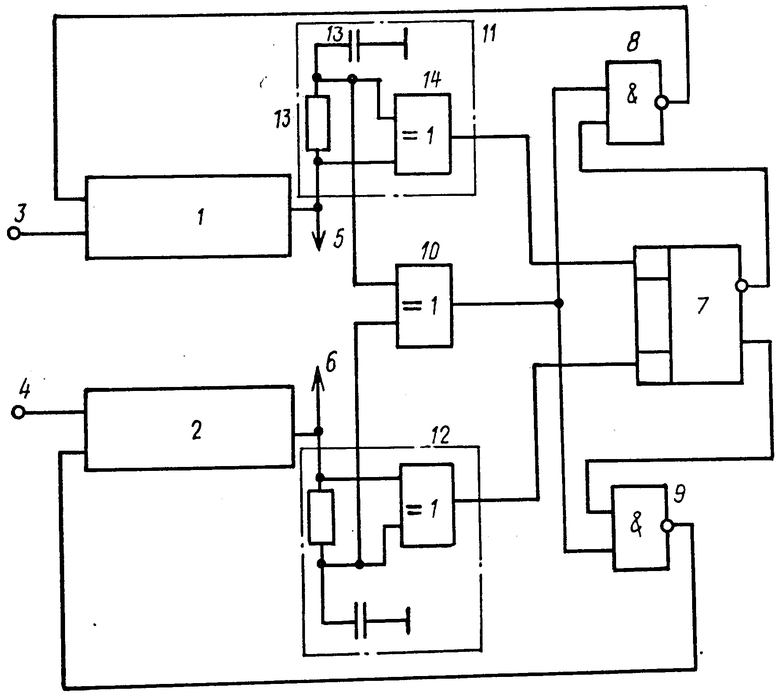

На чертеже изображена электрическая структурная схема устройства.

Самокорректирующийся делитель частоты содержит первый и второй делители 1 и 2 частоты, счетные входы и выходы которых соединены с соответствующими входными 3 и 4 и выходными 5 и 6 шинами, элемент 7 памяти и первый и второй элементы 8 и 9 совпадения, элемент 10 ИСКЛЮЧАЮЩЕЕ ИЛИ и первый и второй формирователи 11 и 12 импульсов, входы которых соединены с выходом соответственно первого и второго делителей 1 и 2 частоты, первые выходы - соответственно с первым и вторым входами элемента 7 памяти, вторые выходы - соответственно с первым и вторым входами элемента 10 ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первыми входами первого и второго элементов 8 и 9 совпадения, вторые входы которых соединены с соответствующими выходами элемента 7 памяти, а выходы - с входами управления соответствующих делителей 1 и 2 частоты, кроме того, формирователь 11 и 12 импульсов содержит интегрирующую, например RC, цепь 13 и элемент 14 ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого соединен с входом интегрирующей цепи 13 и входом формирователя импульсов, выход - с первым выходом формирователя импульсов, второй вход - с выходом интегрирующей цепи 13 и с вторым выходом формирователя импульсов.

Входные шины 3 и 4 в частном случае могут быть соединены между собой.

Устройство работает следующим образом.

При одинаковых частотах импульсов на шинах 3 и 4 и синхронной работе делителей 1 и 2 на выходе элемента 10 присутствует уровень "0" (логического), на выходах элементов 8 и 9 - уровень "1". Формирователи 11 и 12 формируют на своих выходах импульсы положительной полярности после каждого изменения уровня сигнала на своих входах. Предположим, что элемент 7 представляет собой триггер, первый и второй входы которого являются входами соответственно сброса и запуска, а первый и второй выходы соответственно инверсным и прямым выходами.

Допустим, что в результате сбойной ситуации, на шине 5 перепад напряжения появился раньше, чем на шине 6, тогда на инверсном выходе элемента 7 появится уровень "1". Одновременно с этим задержанный интегрирующей цепью 13 формирователя 11 перепад напряжения, поступает на первый вход элемента 14, на выходе которого появляется уровень "1", а на выходе элемента 8 - уровень "0". Последний поступает на управляющий вход делителя 1 и останавливает в нем счет. На выходе делителя 1 при этом сохраняется тот уровень сигнала, который вызвал появление уровня "1" на выходе элемента 10.

После появления на выходе делителя 2 уровня сигнала, соответствующего уровню сигнала на выходе делителя 1, на выходе элемента 10 появляется уровень "0", а на выходе элемента 8 - уровень "1", и делитель 1 продолжит счет входных импульсов. Изменение уровня сигнала на выходе делителя 2 вызывает появление импульса на выходе формирователя 12 и переключение элемента 7, однако при этом изменения уровня сигнала на управляющем входе делителя 2 не произойдет.

Аналогичным образом происходит корректировка делителя 2 в случае, если рассогласование делителей 1 и 2 произойдет за счет изменения сигнала на его выходе.

Необходимо отметить, что поскольку в устройстве состояние делителей 1 и 2 анализируется только по состоянию элемента 7, то возможны случаи сбоев, с переключением элемента 7, когда полное (по всем разрядам) согласование делителей 1 и 2 происходит в два этапа корректировки, за два периода колебаний на их выходах.

Данное устройство по сравнению с прототипом имеет достоинство, заключающееся в повышении надежности его функционирования в составе двухканальной резервированной системы. Новая организация взаимной синхронизации делителей частоты в каждом канале системы позволяет, во-первых, исключить взаимные связи каналов, и во-вторых, формировать выходные сигналы делителей частоты при любых рассогласования и сбоях информации в делителях частоты, а также при использовании независимых рассогласованных по частоте сигналов на их входах. Указанные свойства позволяют выполнить резервированные каналы полностью автономными с использованием в каждом из каналов двух независимых источников входных сигналов (задающих генераторов) и независимых источников питания каждого из каналов.

Устройство может быть эффективным в составе системы, к которой, наряду с высокими требованиями по надежности, предъявляются жесткие требования по отсутствию повышенной частоты на выходах каналов при отказах отдельных элементов.

| название | год | авторы | номер документа |

|---|---|---|---|

| САМОКОРРЕКТИРУЮЩИЙСЯ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2036554C1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ | 1991 |

|

RU2036550C1 |

| Устройство для управления шаговым двигателем | 1977 |

|

SU663058A1 |

| Устройство для определения момента экстремума | 1985 |

|

SU1292171A1 |

| Резервированный генератор импульсов | 1982 |

|

SU1102066A2 |

| Резервированное многоканальное устройство для формирования тактовых импульсов | 1978 |

|

SU767764A1 |

| РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1993 |

|

RU2111609C1 |

| Устройство для синхронизации резервированного делителя частоты | 1981 |

|

SU1001104A1 |

| Тактовый генератор с контролем | 1986 |

|

SU1378021A1 |

| Резервированное многоканальное устройство | 1981 |

|

SU1058098A1 |

| Резервированный делитель частоты | 1974 |

|

SU499672A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-01-09—Публикация

1984-01-06—Подача