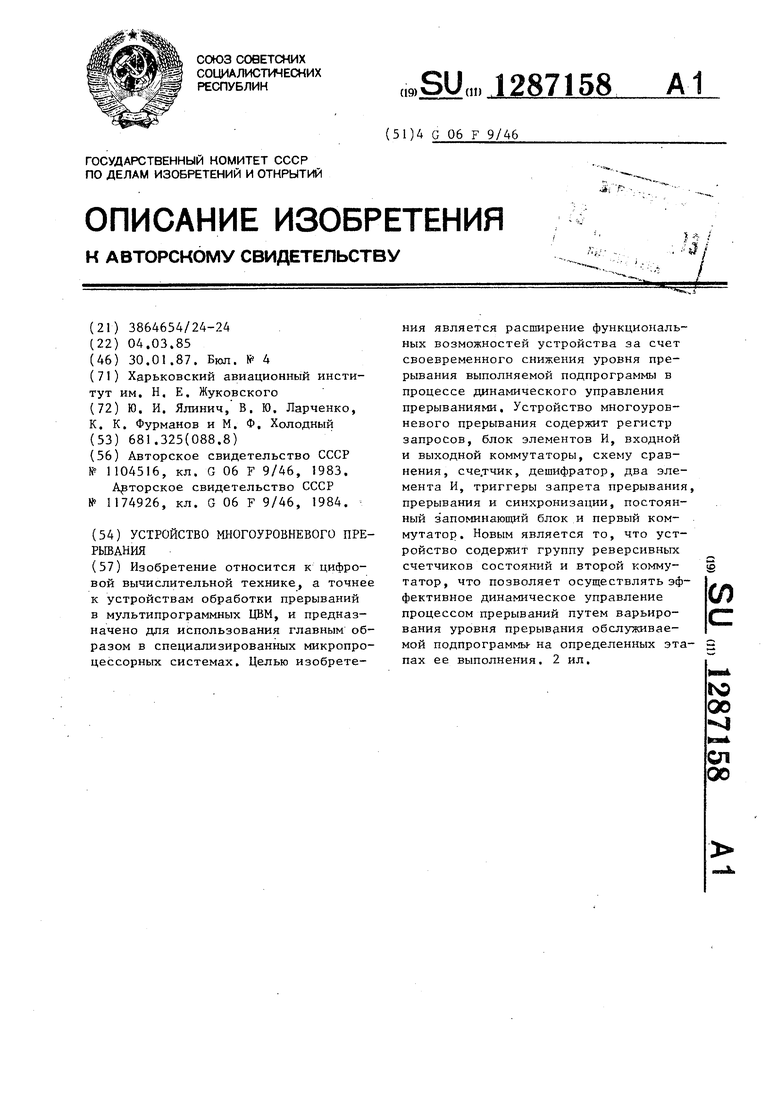

Изобретение относится к цифровой вычислительной технике, а точнее к устройствам обработки прерываний в мультипрограммных ЦВМ, и предназначено для использования-, в частности, в специализированных вь1числительных и управляющих системах, организованных на основе микропроцессоров.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности своевременного снижения уровня прерывания выполняемой подпрограммы в процессе динамического управления прерываниями.

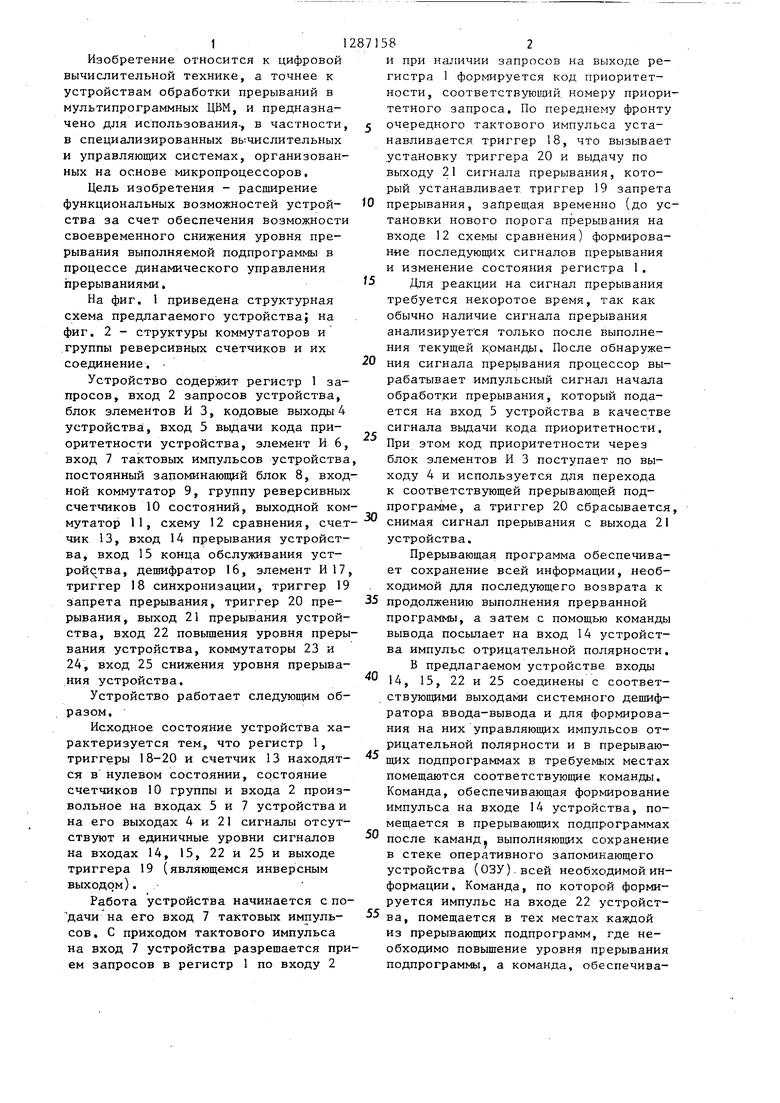

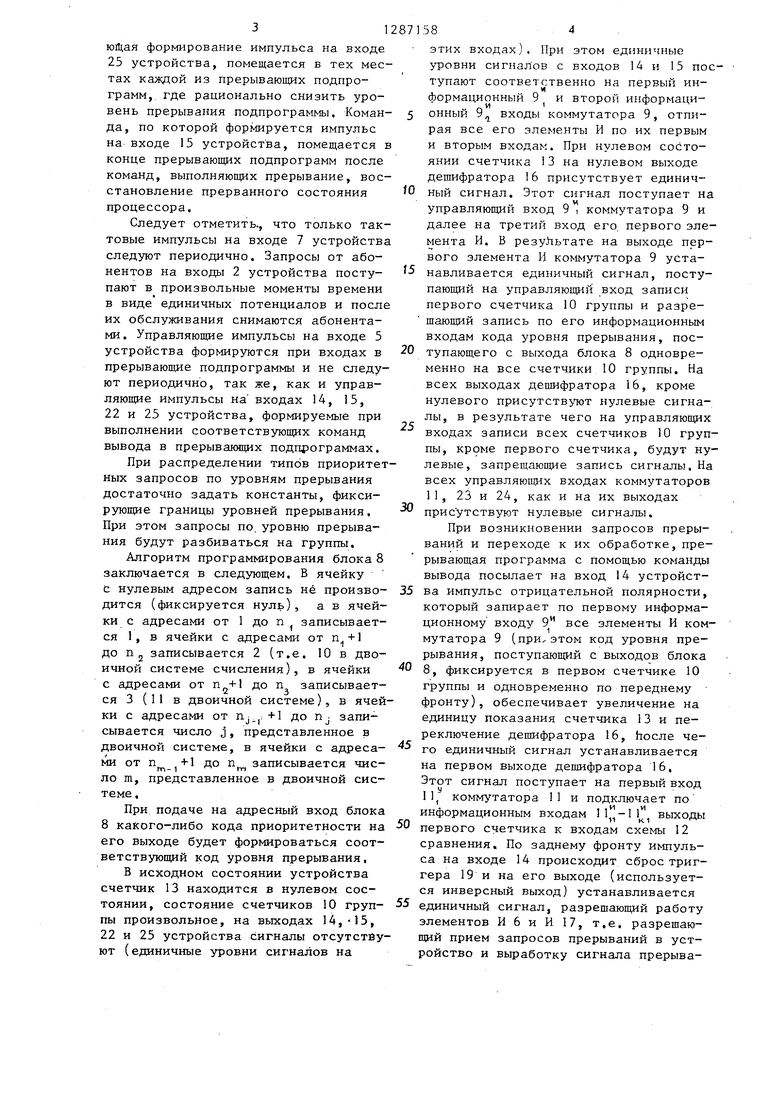

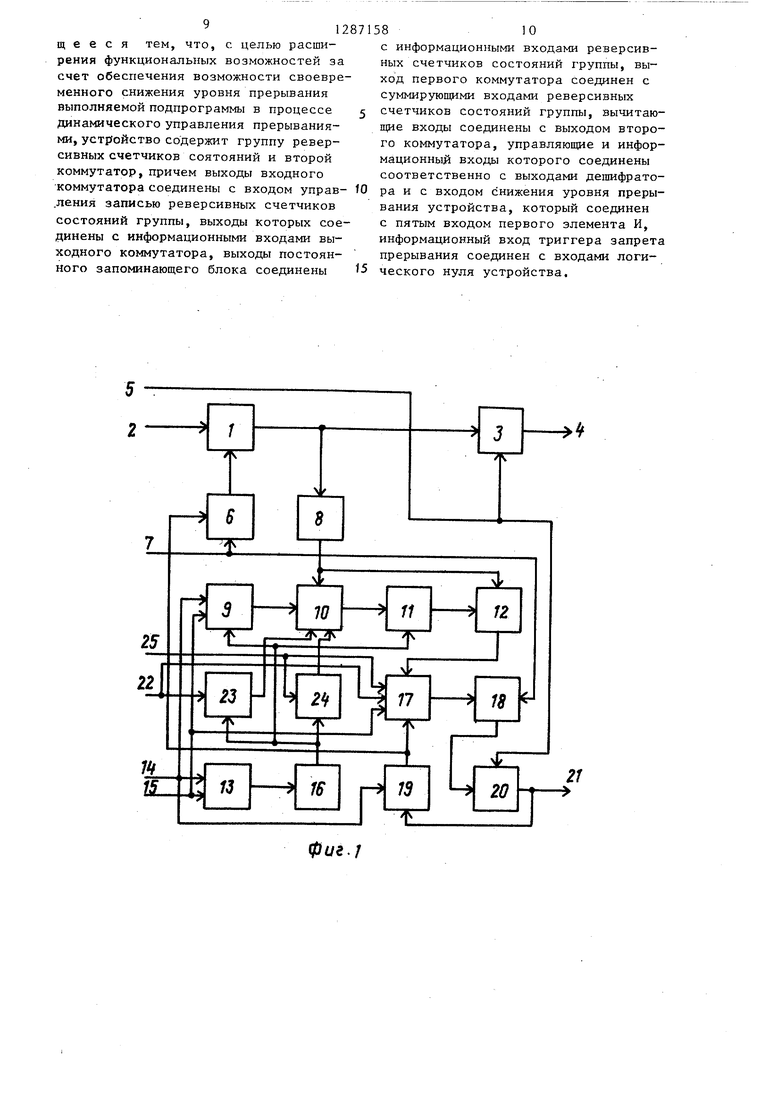

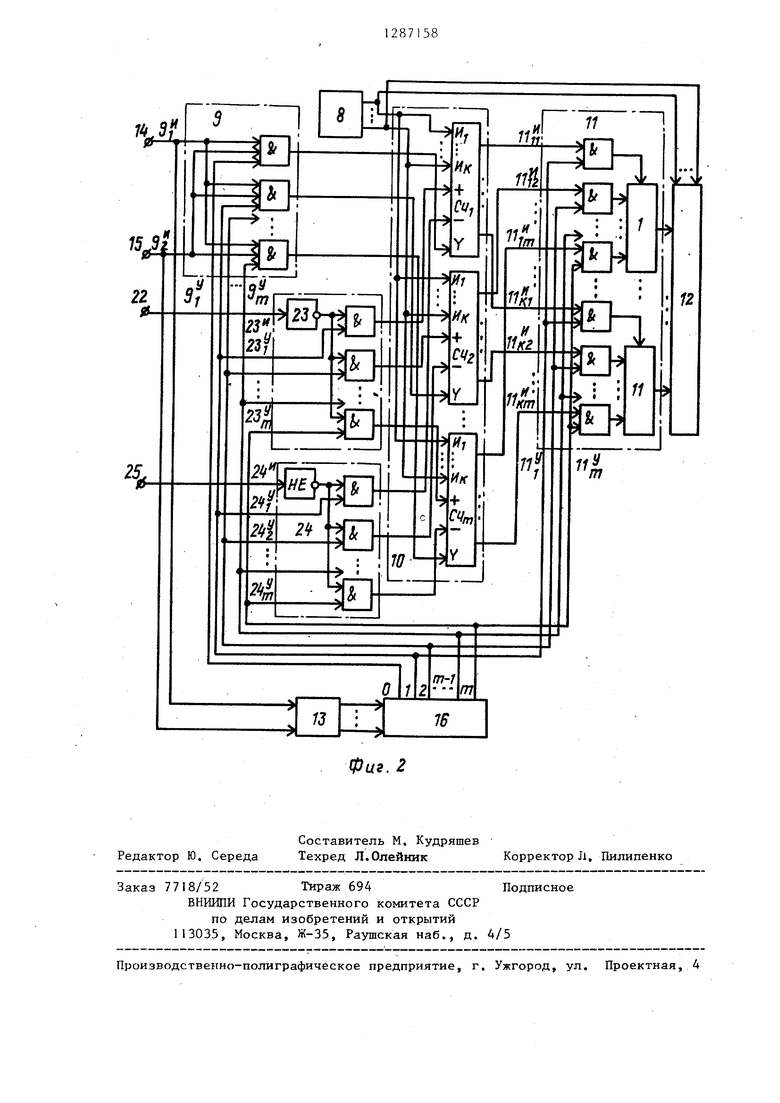

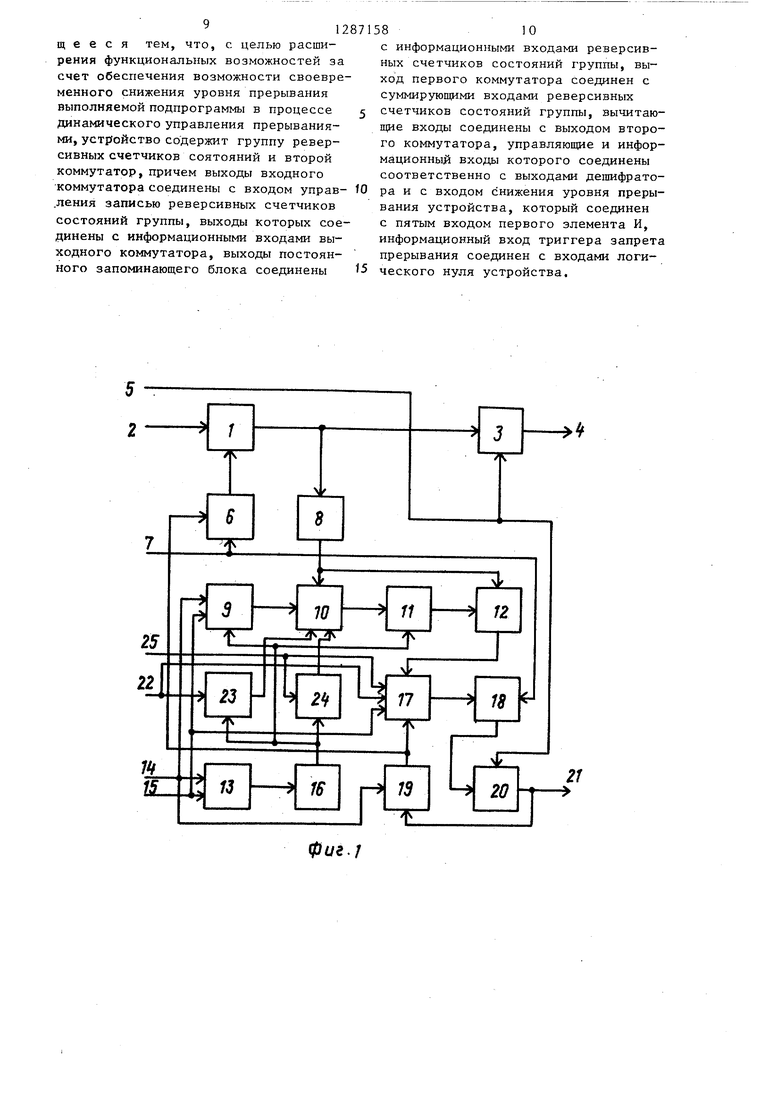

На фиг, 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - структуры коммутаторов и группы реверсивных счетчиков и их соединение.

Устройство содержит регистр 1 запросов, вход 2 запросов устройства, блок элементов И 3, кодовые выходы 4 устройства, вход 5 вьщачи кода приоритетности устройства, элемент И 6, вход 7 тактовых импульсов устройства постоянный запоминающий блок 8, входной коммутатор 9, группу реверсивных счетчиков 10 состояний, выходной коммутатор 11, схему 12 сравнения, счетчик 13, вход 14 прерывания устройства, вход 15 конца обслуживания уст- , дешифратор 16, элемент И 17, триггер 18 синхронизации, триггер 19 запрета прерывания, триггер 20 прерывания, выход 21 прерывания устройства, вход 22 повышения уровня прерывания устройства, коммутаторы 23 и 24, вход 25 снижения уровня прерывания устройства.

Устройство работает следующим образом.

Исходное состояние устройства характеризуется тем, что регистр 1, триггеры 18-20 и счетчик 13 находятся в нулевом состоянии, состояние счетчиков 10 группы и входа 2 произвольное на входах 5 и 7 устройства и на его выходах 4 и 21 сигналы отсутствуют и единичные уровни сигналов на входах 14, 15, 22 и 25 и выходе триггера 19 (являющемся инверсным выходом).

Работа устройства начинается с по- дачи на его вход 7 тактовьпс импульсов, С приходом тактового импульса на вход 7 устройства разрешается прием запросов в регистр 1 по входу 2

5

0

5

и при наличии запросов на выходе регистра 1 формируется код приоритетности, соответствующий, номеру приоритетного запроса. По переднему фронту очередного тактового импульса устанавливается триггер 18, что вызывает установку триггера 20 и выдачу по выходу 21 сигнала прерывания, который устанавливает триггер 19 запрета прерывания, запрещая временно (до установки нового порога прерывания на входе 12 схемы сравнения) формирование последуюш;их сигналов прерывания и изменение состояния регистра 1.

Для реакции на сигнал прерывания требуется некоротое время, так как обычно наличие сигнала прерывания анализируется только после выполнения текущей команды. После обнаружения сигнала прерывания процессор вырабатывает импульсный сигнал начала обработки прерывания, который подается на вход 5 устройства в качестве сигнала выдачи кода приоритетности. При этом код приоритетности через блок элементов И 3 поступает по выходу 4 и используется для перехода к соответствующей прерывающей подпрограмме, а триггер 20 сбрасывается, снимая сигнал прерывания с выхода 21 устройства.

Прерывающая программа об ;спечива- ет сохранение всей информации, необ- . ходимой для последующего возврата к

5 продолжению выполнения прерванной программы, а затем с помощью команды вывода посылает на вход 14 устройства импульс отрицательной полярности.

В предлагаемом устройстве входы 14, 15, 22 и 25 соединены с соответствующими выходами системного дешифратора ввода-вывода и для формирования на них управляющих импульсов от рицательной полярности и в прерываю- подпрограммах в требуемых местах помещаются соответствующие команды. Команда, обеспечивающая формирование импульса на входе 14 устройства, помещается в прерывающих подпрограммах после каманд выполняюш 1х сохранение в стеке оперативного запоминающего устройства (ОЗУ).всей необходимой информации. Команда, по которой формируется импульс на входе 22 устройст 5 ва, помещается в тех местах каждой из прерывающих подпрограмм, где необходимо повышение уровня прерывания подпрограммы, а команда, обеспечива0

0

5

0

31

юЩая формирование импульса на входе 25 устройства, помещается в тех местах каждой из прерываю1цих подпрограмм, где рационально снизить уровень прерывания подпрограммы, Коман- да, по которой формируется импульс на входе 15 устройства, помещается в конце прерывающих подпрограмм после команд, выполняющих прерывание, восстановление прерванного состояния процессора.

Следует отметить., что только тактовые импульсы на входе 7 устройства следуют периодично. Запросы от абонентов на входы 2 устройства посту- пают в произвольные моменты времени в виде единичных потенциалов и после их обслуживания снимаются абонентами , Управляющие импульсы на входе 5 устройства формируются при входах в прерывающие подпрограммы и не следуют периодично, так же, как и управ- ляюш:ие импульсы на входах 14, 15, 22 и 25 устройства, формируемые при выполнении соответствующих команд вывода в прерывающих подпрограммах.

При распределении типов приоритетных запросов по уровням прерывания достаточно задать константы, фиксирующие границы уровней прерывания, При этом запросы по. уровню прерывания будут разбиваться на группы.

Алгоритм программирования блока 8 заключается в следующем, В ячейку с нулевым адресом запись не произво- дится (фиксируется нуль), а в ячейки с адресами от 1 до п записывается 1, в ячейки с адресами от до п2 записывается 2 (т,е, 10 в двоичной системе счисления), в ячейки с адресами от до п записывается 3 (11 в двоичной системе), в ячейки с адресами от +1 до nj записывается число j, представленное в двоичной системе, в ячейки с адреса- ми от п +1 до п записывается число т, представленное в двоичной системе ,

При подаче на адресный вход блока 8 какого-либо кода приоритетности на его выходе будет формироваться соответствующий код уровня прерывания,

В исходном состоянии устройства счетчик 13 находится в нулевом состоянии, состояние счетчиков 10 груп- пы произвольное, на выходах 14,-15, 22 и 25 устройства сигналы отсутствуют (единичные уровни сигналов на

584 .

этих входах). При этом единичные уровни сигналов с входов 14 и 15 поступают соответственно на первый информационный 9 и второй информационный 9 входы коммутатора 9, отпирая все его элементы И по их первым и вторым входам. При нулевом состоянии счетчика 13 на нулевом выходе дещифратора 16 присутствует единичный сигнал. Этот сигнал поступает на управляюпщй вход 9 i коммутатора 9 и далее на третий вход его. первого элемента И, В pe3yhbTaTe на выходе первого элемента И коммутатора 9 устанавливается единичный сигнал, поступающий на управляющий вход записи первого счетчика 10 группы и разре- щающий запись по его информационным входам кода уровня прерывания, поступающего с выхода блока 8 одновременно на все счетчики 10 группы. На всех выходах дешифратора 16, кроме нулевого присутствуют нулевые сигналы, в результате чего на управляющих входах записи всех счетчиков 10 группы, кроме первого счетчика, будут нулевые, запрещающие запись сигналы. На всех управляющих входах коммутаторов 11, 23 и 24, как и на их выходах присутствуют нулевые сигналы.

При возникновении запросов прерываний и переходе к их обработке, прерывающая программа с помощью команды вывода посылает на вход 14 устройства импульс отрицательной полярности, который запирает по первому информационному входу 9 все элементы И коммутатора 9 ( код уровня прерывания, поступающий с выходов блока 8, фиксируется в первом счетчике 10 группы и одновременно по переднему фронту), обеспечивает увеличение на единицу показания счетчика 13 и переключение дешифратора 16, Ьосле чего единичный сигнал устанавливается на первом выходе дещифратора 16, Этот сигнал поступает на первый вход II, коммутатора П и подключает по

И И

информационным входам 1 1.,-1 1 выходы первого счетчика к входам схемы 12 сравнения. По заднему фронту и myль- са на входе 14 происходит сброс триггера 19 и на его выходе (используется инверсный выход) устанавливается единичный сигнал, разрещающий работу элементов И 6 и И 17, т,е, разрешающий прием запросов прерываний в устройство и выработку сигнала прерыва5

ПИЯ ил Bbix(v;t - 1 в случае, если поступит запрос;, уровень прерывания которого превысит уровень прерывания, записанный в первом счетчике 10 группы .

Каждая прерывающая подпрограмма с помощью команд вывода, помещенных в соответствуюЕГИх ее местах, может повышать свой уровень прерывания, а затем снижать его, что обеспечивает эффективное динамическое управление процессом прерываний. Если по команде вывода управляющий импульс отрицательной полярности подается на вход 22 устройства, то обеспечивает- ся повышение на единицу уровня прерывания обслуживаемой подпрограммы. Осуществляется это с помощью коммутатора 23, передающего (с инверсией) управляющий импульс на суммирующий вход того счетчика 10 группы, номер которого равен номеру выхода дешифратора 16, на котором присутствует единичный сигнал. Если единичный сигнал действует на первом выходе дешиф ратора 16, то от поступает на первый управляющий вход 23 коммутатора 23 разрешая передачу управляющего импульса через первый элемент И коммутатора 23 на суммируюш;ий вход перво- го счетчика 10 группы, в результате чего содержимое этого счетчика увеличивается на единицу. Если по команде вывода управляющий импульс отрицательной полярности подается на вход 25 устройства, то обеспечивается снижение на единицу уровня прерывания обслуживаемой подпрограммы. Производится это с помощью коммутатора 24, передающего (с инверсией) управляющий импульс на вычитающий вход того счетчика 10 группы, номер которого равен номеру выхода дешифратора 16, на котором присутствует единичный сигнал. Если единичный сиг нал действует на первом выходе де- щифратора 16, то он поступает на первый управляющий вход 24 коммутатора 24, разрешая передачу управляющего импульса через первый элемент И коммутатора 24 на вычитающий вход первого счетчика, в результате чего его содержимое уменьшается на единиц

После завершения выполнения прерывающей подпрограммы восстанавлива- ется последнее из прерванных состояний процессора и с помощью команды вывода на вход 15 устройства посылается отрицательный импульс, который

586

запирает по ivrcjpoMy информационному входу 9 все злемептрл ,И коммутатора 9, исключая иозможность искажения информации в счетчиках 10 группы во время переходных процессов, и одновременно (по переднему фронту) обеспечивает уменьшение на единицу показания счетчика 13 и соответствующее переключение дешифратора 16, подключающего через коммутатор 11 на входы схемы 12 сравнения выходы того счетчика группы 10, в котором хранится код уровня прерывания последнего из прерванных состояний (основной программе соответствует нулевой код уровня прерывания).

Если во время выполнения прерывающей подпрограммы поступает запрос, уровень прерывания которого превышает уровень прерывания обслуживания подпрограммы, то на выходе 21 формируется сигнал прерывания. После обнаружения сигнала прерывания на вход 5 устройства поступает импульсный сигнал выдачи кода приоритетности, после чего на вход 14 поступает отрицательный импульс, который запирает коммутатор 9, фиксируя код уровня прерывания, поступаю1ций с выходов блока 8 в соответствующем счетчике 10 группы, номер которого на единицу больше номера выхода дешифратора 16, на котором действует единичный сигнал. Если единичный сигнал присутствует на первом выходе дешифратора 16, связанном с вторым управУ

входом 9 коммутатора 9, фиксация кода уровня прерывания, поступающего с выходов блока 8, произойдет во втором счетчике 10 группы и одновременно выполняется процесс переключения дешифратора 16, после чего единичный сигнал установится на втором выходе дешифратора 16. Этот сигнал поступает на второй управляюU

щий вход 112 коммутатора 11 и подключает по информационным входам . . и . , и iQ кг выходы второго счетчика по

входам схемы 12 сравнения. Кроме того, единица с второго выхода дешифратора 16, поступая на вторые управUU

ляюшJ e входы 23 и 24 коммутаторов 23 и 24, подготавливают к работе вторые элементы И этих коммутаторов, связанные с cyммиpyющ м и В 1читающим входами второго счетчика. Наряду с этим единичный сигнал с второго выхода дешифратора 16, поступля мл третий управляющий вход У, коммутатор,

12

9, подготавливает к работе третий элемент И коммутатора 9, выход которого связан с управляющим входом разрешения записи третьего счетчика 10 группы. Теперь же запись (после окон- чания «мпульса на выходе 14) кода уровня прерывания с выходов блока 8 будет производиться в третий счетчик 10 группы, а импульсы, поступающие на входы 22 и 25, будут передаваться коммутаторами 23 и 24 соответственно на суммирующий и вычитающий входы второго счетчика 10 группы. После завершения выполнения прерывающей под- программы восстанавливается послед- нее из прерванных состояний процессора и с помощью команды вывода на вход 15 устройства посылается отрицательный импульс, который уменьшает на единицу показание счетчика 13, в результате чего с второго выхода дешифратора 16 снимается единичный сигнал, а единица устанавливается на первом выходе дешифратора 16, что

обеспечивает подключение через комму татор 11 на вход схемы 12 сравнения выходов первого счетчика, в котором хранится код уровня прерывания прерванной подпрограммы (каким он был в

момент прерывания обслуживания под- программы), Теперь уже к работе подготовлены первые элементы И коммута- торов 23 и 24, связанные с первым счетчиком, а запись кода уровня прерывания с выходов блока 8 будет про- изводиться во второй счетчик 10 группы. Процесс обслутшвания прерванной ранее подпрограммы продолжается и т,д

Следует отметить, что управляющие импульсы, поступающие на входы 14, 15, 22 и 24 запирают элемент И 17 и тем самым исключают возможность формирования ложного сигнала прерывания под воздействием вызываемых ими переходных процессов (при поступлении управляющего импульса на вход 14 элемент И 17 заперт нулевым сигналом с выхода триггера 19), Формирование ложного сигнала прерывания под воздействием гонок исключается с помо- щью синхронизашии приема запросов в регистр 1 и формирования сигнала прерывания на вы:ходе триггера 18.

Формула изобретен.и я

Устройство многоуровневого прерывания, содержащее регистр запросов,

5 -25

- 35 .

0 -50

55

588

блок элементов И, входной и выход - ной коммутаторы, схему сравнет1ия, счетчик, дешифратор, два элемента И, триггер запрета прерывания, триггер прерывания, триггер синхронизации, постоянный запоминающий блок, первый коммутатор, причем информационные входы регистра запросов являются входами запросов устройства, выходы регистра запросов соединены с адресным входом постоянного запоминающего блока и с группой входов блока элементов И, вход которого соединен с входом сброса триггера прерывания и входом выдачи кода приоритетности устройства, выходы блока .элементов И являются кодовыми выходами устройства, вход прерывания устройства соединен с синхронизирующим входом триггера запрета прерывания, с первым информационным входом входного коммутатора и с суммируюш 1м входом счетчика, выходы которого соединены с входами дешифратора, выходы которого соединены с управляющими входами входного и выходного коммутаторов, выходы выходного коммутатора соединены с первыми входами схемы сравнения, вторые входь которой соединены с выходом постоянного запоминающего блока, выход схемы сравнения соединен с первым входом первого элемен- . та И, выход которого соединен с информационным входом триггера синхронизации, выход которого соединен с единичным входом триггера прерывания, выход которого является выходом.прерывания устройства и соединен с входом установки в l триггера запрета прерывания, выход которого соединен с вторым входом первого элемента И и первым входом второго элемента И, выход которого соединен с управляющим входом регистра запросов, вход тактовых импульсов устройства соединен с вторым входом второго элемента И и с тактовым входом триггера синхронизации, вход конца обслуживания устройства соединен с вычитаюш 1м входом счетчика, с вторым информационным входом входного коммутатора и третьим входом первого элемента И, вход повышения уровня прерывания устройства соединен с четвертым входом первого элемента И и информационным входом первого коммутатора, управляющие входы которого соединены с выходом дешифратора, отличаю912

щ е е с я тем, что, с. целью расширения функциональных возможностей за счет обеспечения возможности своевременного снижения уровня прерывания выполняемой подпрограммы в процессе динамического управления прерываниями, устр(ойство содержит группу реверсивных счетчиков соятояний и второй коммутатор, причем выходы входного коммутатора соединены с входом управ- .ления записью реверсивных счетчиков состояний группы, выходы которых соединены с информационными входами выходного коммутатора, выходы постоянного запоминающего блока соединены

фиг.

810

с информационными входами реверсивных счетчиков состояний группы, выход первого коммутатора соединен с суммирующими входами реверсивных счетчиков состояний группы, вычитающие входы соединены с выходом второго коммутатора, управляющие и информационный входы которого соединены соответственно с выходами дешифратора и с входом снижения уровня прерывания устройства, который соединен с пятым входом первого элемента И, информационный вход триггера запрета прерывания соединен с входами логического нуля устройства.

Составитель М, Кудряшев Редактор Ю. Середа Техред Л.Олейник Корректор Л. Пилипенко

..«---««------ ----------.--------------- - -------- ----

Заказ 7718/52 Тираж 694Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. А/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, А

Фт. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство многоуровневого прерывания | 1984 |

|

SU1174926A1 |

| Устройство многоуровневого прерывания | 1983 |

|

SU1104516A1 |

| Устройство для программного управления | 1985 |

|

SU1267362A2 |

| Устройство для моделирования системы сбора данных | 1988 |

|

SU1534469A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для обработки прерываний | 1986 |

|

SU1606975A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1134949A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1156073A1 |

Изобретение относится к цифровой вычислительной технике, а точнее к устройствам обработки прерываний в мультипрограммных ЦВМ, и предназначено для использования главным образом в специализированных микропроцессорных системах. Целью изобретения является расширение функциональных возможностей устройства за счет своевременного снижения уровня прерывания выполняемой подпрограммы в процессе динамического управления прерываниями. Устройство многоуровневого прерывания содержит регистр запросов, блок элементов И, входной и выходной коммутаторы, схему сравнения, сче.тчик, дешифратор, два элемента И, триггеры запрета прерывания, прерывания и синхронизации, постоянный запоминающий блок и первый коммутатор. Новым является то, что устройство содерткит группу реверсивных счетчиков состояний и второй коммутатор, что позволяет осуш;ествлять эффективное динамическое управление процессом прерываний путем варьирования уровня прерывания обслуживаемой подпрограммы- на определенных этапах ее выполнения. 2 ил. Ю (Л N5 00

| Устройство многоуровневого прерывания | 1983 |

|

SU1104516A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство многоуровневого прерывания | 1984 |

|

SU1174926A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-01-30—Публикация

1985-03-04—Подача