Изобретение относится к вычислительной технике и может быть использовано для параллельного и приоритетного распределения информации между элементами вычислительных систем.

Цель изобретения - сокращение времени настройки в режиме свободного поиска каналов. .

Наращивание емкости коммутатора происходит без изменения функциональной структуры матриц . При этом практически сохраняется скорость настройки на групповые каналы, кото- ,рая остается постоянно минимальной

и в тех же случаях, когда одновременно устанавливаются внешние связи, например, как между 10 внешними абонентами, так и 16 (и т.д,). За счет этого производительность может возрасти приблизительно в 1 ,5-2 раза при настройке групповых каналов бо- лее 4.

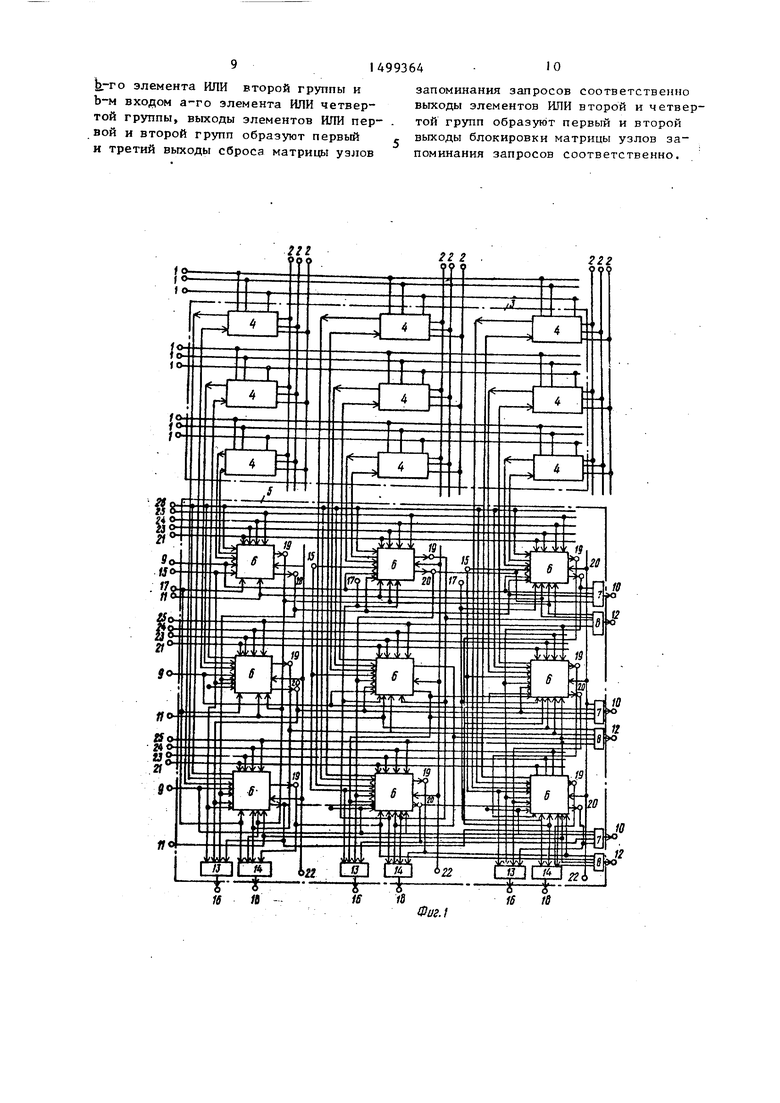

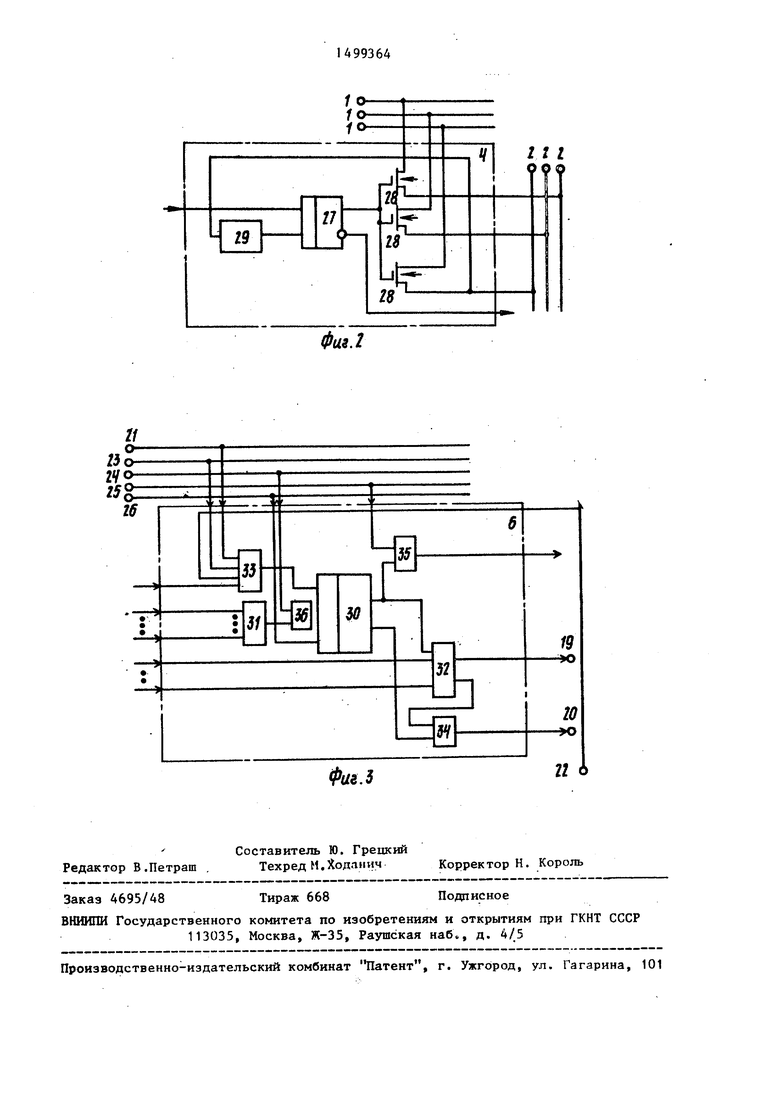

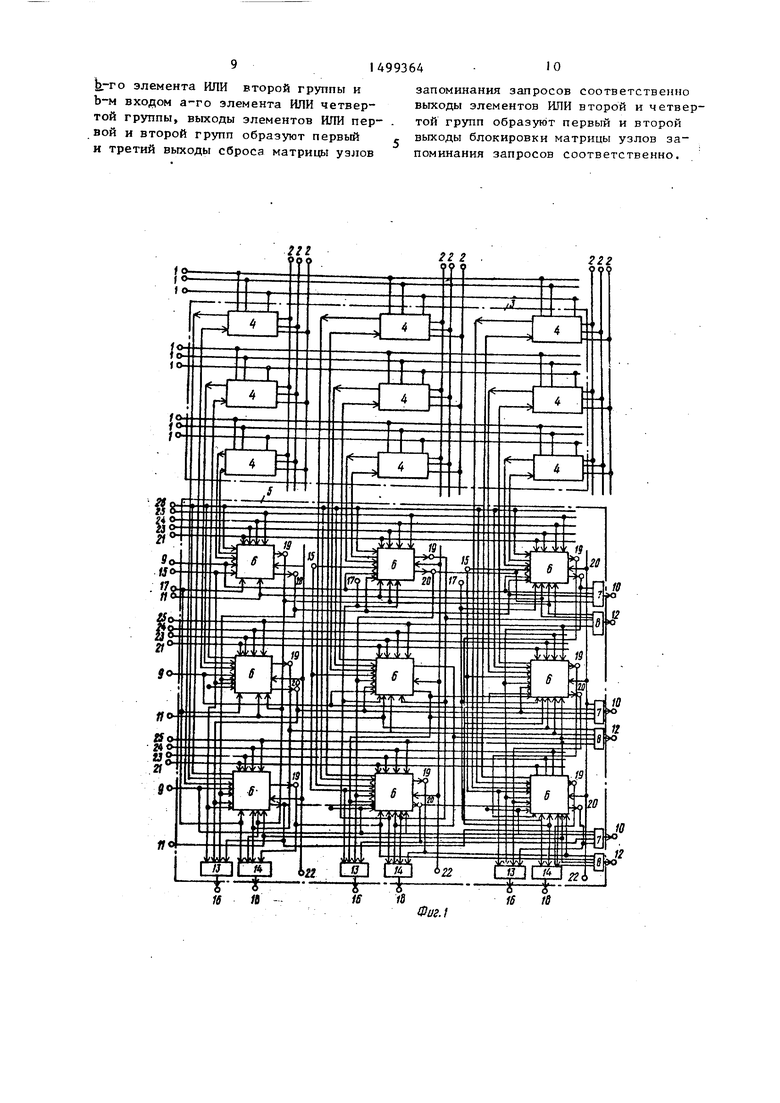

На фиг. 1 представлена блок-схема матричного коммутатора; на фиг. 2 - функциональная схема коммутационного узла; на фиг. 3 - функциональная схема узла запоминания запросов.

Коммутатор содержит коммутируемых входов-выходов I и 2, матри- ,

J

со

со

Од 05

31499364

Цу 3 () узлов 4 коммутации, блок управления, выполненный в виде матри- цы 5 (КхР) узлов 6 запоминания запросов, первую 7 и вторую 8 группы элементов ИЛИ, вход 9 и выход 10 сброса коммутатора, вход II и выход

12блб сировки коммутатора, третью

13и четвертую 14 группы элементов ИЛИ, вход 15 и выход 16 сброса, вход ю 17 и выход 18 блокировки ксммутато-

ра, выходы 1 9 и 20 сброса и блокировки соответственно, входы 21 и 22 запросов, тактирующие входы 23-25, вход 26 общего сброса.15

Узел 4 (фиг. 2) содержит RS-триг- гер 27, группу ключевых транзисторов 28 и элемент 29 задержки.

Узел 6 (фиг. 3)содержит RS-триг- гер 20, многовходовый элемент ИЛИ 31,20 два многовходовых элемента И 32 и 33, элемент ИЛИ 34 и два двухвходовых элемента И 35 и 36.

Работа устройства происходит в дующих четырех основных режимах:

возбуждение и запоминание всех возможных каналов между свободными входами 21 и 22;

фиксация корневых вершин прямо- 30 угольных деревьев на матрице 5 устройства;

одновременная фиксация параллельных каналов между группой свободных горизонтальных I и вертикальных 2 jj коммутируемых входов-выходов;

разрушение всех волн в матрице 5 коммутатора,

Для выполнения первого режима формируется потенциал на первом входе ,40 23 синхронизации, который в 6 матрищл 5 открьгоает второй многовхо- довьгй. элемент И 33, последний дол- жен быть также открыт потенциалами со свободных горизонтальных сигналь- j ньпс входов, свободных вертикальных сигнальных входов 23 и управляющего входа узла 6. Появление потенциалов : на управляющих входах узлов 6 определяется наличием потенциалов на уп50

равляющих выходах коммутационных уз-, лов 4. Действительно, если триггер 27 находится в нулевом состоянии, то на его выходе R - высокий потенциал, который и. включает свой узел 6. В jj свою очередь, на выходе S данного , RS-триггера 27 присутствует нулевой потенциал, который закрывает группу ключевых транзисторов 28 и тем са

5

0 5

0

j

0 j

0

j

мым исключает наличие каналов между коммутируемыми входами-выходами 1 и 2.

Таким образом, на всех свободных входах 21 и 22 присутствуют потенциалы, которые записьшаются через вторые многовходовые элементы И 33 в триггеры 30 только тех узлов 6 матрицы 5, которые связаны с невключенными узлами 4 матрицы 3 (как отмечено Bbmiej включенными считаются те узлы 4, в которых RS-триггер 27 находится в единичном состоянии). Следовательно, в конце первого режима запоминаются в триггерах 30 соответствующих узлов 6 матрицы 5 все возможные каналы между, свободными горизонтальными 21 и вертикальными 22 входами. Причем для них считается, что они имеют разный приоритет для дальнейшего их включения в конечный канал, т.е. для горизонтальных входов 21 на фиг. 1 сверху вниз, а для вертикальных входов 22 слева направо ;

Исходя из последнего, рассмотрим переходные процессы, протекающие по- еле включения триггеров 30 соответствующих узлов 6. Так, в самом верхнем и левом возбужденном узле 6 матрицы 5, находящемся, например, во второй строке и первом столбце, ока- зьюается включенным первый многовхо- довый элемент К 32 в связи с тем, что на него не поступают нулевые потенциалы с входов блокировки данного узла 6, и, наоборот, присутствует высокий потенциал с прямого выхода RS-триггера 30. Следовательно, на выходе первого многовходового элемента И 32 и выходе 19 сброса появ ляются высокие потенциалы. С другой стороны, выход 20 блокировки данного узла 6 обнуляется, так как на него через элемент ИЛИ 34 поступают нулевые потенциалы с инверсного выхода триггера 30 и инверсного выхода элемента И 32. Поэтому нулевой потенциал с выхода 20 блокировки данного узла 6 поступает на все остальные включенные узлы 6 искомого столбца (в данном случае первого) и необходимой строки (второй).

В результате, из включенных узлов 6 вьзделяется прямоугольне пра- дерево, у которого корневой вершиной является тот узел 6, в котором выход I9 сброса находится в единичном состоянии, а выход 20 блоки51499364

- в нулевом состоянии. В то же

ж тр за эл

время в остальных возбужденных узлах 6, относящихся к одному прадереву, выход 19 сброса находится в нулевом состоянии, так как на соответствующи .элементы И 32 с входов блокировки поступают нулевые потенциалы. Однако тогда инверсный выход данных элементов И 32 находится в возбужденном состоянии и потенциал с него через элемент ИЛИ 34 поступает на выход 20 блокировки и в сиязи с этим остальны включенные узлы 6 данного прямоугольного прадерева не влияют на образование корневых вершин в формируемых прямоугольных деревьях. Окончательно можно сказать, что на матрице 5 потенциалы с выходов|19 и 20 включенных узлов 6 выделят ровно столько прямоугольныхпрадеревьев, сколько на

данный момент в первом режиме было возбуждено горизонтальных 21 или вертикальных 22 сигна.пьных входов. При этом в каждом прадереве корневой

вершиной является включенньш узел 6, находящийся в вершине прямого угла.

При выполнении второго режима возбуждается второй тактовый вход 24, потенциал с которого во всех узлах 6 открьюает второй двухвходовый элемент И 36, на второй вход которого может поступить потенциал сброса с многовходового элемента ИЛИ 31 . Очевидно, что такой потенциал сброса поступает всегда только с выходов 19 сброса тех узлов 6, которые в прадеревь ях находятся левее в строках и ниже в столбцах по сравнению с корневыми вершинами. В узлах 6,- относящихся к корневым вершинам, он не возникает и, следовательно, в них через открытый элемент И 36 не происходит переброс включенного триггера 30 в нулевое состояние. Наборот,во всех остальных узлах 6, не относящихся к корневым вершинам, происходит через элемент ИЛИ 31, открытый элемент

И 36 и второй вход сброса переброс триггеров 30 в нулевое состояние. В конце второго режима за счет .оставшихся включенных узлов 6 фиксируются все одинарные возможные каналы от

свободных К свободным К,

горизонтальных 21 к вертикальным- 22 входам. Причем, если К К , то число одинарных зафиксированных каналов равно К, а при К Кг оно равно К .

В третьем режиме происходит перезапись единичных состояний триггеров 30, включенных в предьщущем режиме, в триггеры 27 своих узлов 4. Для этого возбуждается потенциал на третьем тактовом входе 25, который затем открьшает первые двухвходовые элементы И 35. Через них считьшают0 ся единичные потенциалы с прямых выходов включенных триггеров 30 на управляющие выходы соответствующих узлов 6 и затем далее через управляющие входы необходимых узлов 4 записы5 ваютс я в триггеры 27. После этого считается, чфо зафиксированы групповые связи (размером К или К) между коммутируемыми входами-выходами 1 и 2.

0В четвертом режиме работы возбуждается вход 26 общего сброса, потенциал с которого через первый вход сброса сбрасывает все триггеры 30 узлов 6 и тем самым разрушает все

5 волны в матрице 5.

Коммутатор готов к поиску и фиксации групповых каналов между освобождающимися коммутируемыми входами- выходами 1 и 2 при наличии на соот0 ветствующих входах 21 и 22 потенциалов. При этом освобождение каналов в устройстве происходит при возбуждении либо последнего в группе из К коммутируемого входа-выхода 1, либо

5 первого в группе из К входа-выхода 2 Тогда, как видно из фиг. 2, потенциал с возбужденного коммутируемого входа-выхода 1 , пройдя через открытый ключевой транзистор 28, или с

0 возбужденного входа-вьтода 2 непосредственно поступает на элемент 29 задержки, потенциал с которого через вход сброса устанавливает в нулевое состояние триггер 27 требуемого узла

5 4. Таким же образом можно разрушить одновременно произвольную группу каналов, информируя при этом пассивных абонентов,

Для матричного наращивания емкости

0 коммутатора необходимо объединять между собой различные матрицы 3 и матрицы 5 следующим образом:

по двум координатам X и Y(T.e. по строкам и столбцам) матрицы 3 соеди5 няются через соответствующие коммутируемые входы-выходы 1 и 2,

предыдущая матрица 5 по координате X (т.е. по строкам) соединяется с последующей матрицей 5 в строкё через выходы 10 сброса и 12 блокировки, которые последовательно должны подсоединяться к соответствующим входам 9 сброса и 11 блокировки, находящимся в последующей матрице 5

предыдущая матрица 5 в столбце (т.е. по координате Y) соединяется с последующей матрицей 5 в столбце j через выходы 16 сброса и 18 блокировки, которые последовательно под- ключают к соответствующим входам.; 15 сброса и 17 блокировки, йаходящимся в последующей матрице 5. Формула изобретений

1. Матричный коммутатор, содержа- щий блок управления и матрицу КиР узлов коммутации, где К и Р - количество коммутируемых абонентов по строкам и столбцам матрицы соответственно, первый и второй информационные входы-входы С, Т-го узла коммутации (С 1 ,..., К, Т 1 ,..., Р) соединены с С-м и Т-м информационны- ми входами-выходами коммутатора для подключения к информационным входам-выходам С-г и Т-го абонентов со- ответствеино, управляющие входы всех узлов коммутации матрицы соединены с соответствующими выходами управления соединением блока уйравлеиия, отличающийся тем, что, с целью сокращения времени настройки в режиме свободного поиска каналов, блок управления выполнен в виде матрицы К узлов запоминания запросов, соответствующие входы сброса, блокировки С, Т-го узла запоминания запросов соединенны с входами сброса и блокировки коммутатора для подключения. К одноименным выходам С-го и Т-то абонентов еоответственно, первый и второй входы запросов С,Т-го узла запоминания запросов соединены с односменными входами коммутатора для подключения к выходам запросов соответственно С-го и Т-го абонентов, вход начальной установки и с первого по третий тактовые входы коммутатора соединены с одноименш ми входами всех узлов запся4ииания-запросов, выходы управления соединением которых образуют выходы управления соединением блока управления, выход п|ризнака отсутствия соединения С,Т-го узла коммутации матрицы соединен с одноименным лходом С,Т-го узла запоминания

запросов матрицы, выходы сброса и блокировки С,Т-го узла запоминания запросов матрицы соединены с одно- именными соответствующими входами а,Ь-х узлов запоминания запросов матрицы (а С+1,...,К, Ь Т+1 , ,с)

2.Коммутатор по п. 1, о т л и - чающийся тем, что каждый

узел запоминания запросов содержит триггер, четыре элемента И, два зле- мента ИЛИ, причем входы первого зле- мента ИЛИ подключены к входу сброса

узла, а выход - к первому входу первого элемента И, второй вход которог го подключен к второму тактовоу входу узла, а выход - к второму входу сброса триггера, первый и второй i

входы второго элемента И подключень к соответствующим входам запроса узла, а третий вход - к первому тактовому входу узла,- четвертый вход

второго элемента И подключен к вхо

ду признака отсутствия соединения

узла запоминания запросов, а выход - к входу установки в 1 триг- , гера, второй вход сброса которого соединен с входом начальной установ-

ки узла, прямой выход триггера соедиг нен с первыми входами третьего и чет- вертого элементов И, инверсный выход - с первым вхЬдом второго элемента ИЛИ, второй вход третьего элемента И соединен с третьим тактовым входом узла, а выход - с выходом уп- равления установлением соединения, вторые входы четвертого элемента И соединены с входом сброса узла, инверсный выход четвертого элемента И соединен с вторым входом второго элемента ШШ, выход которого соединен с выходом сброса узла, а прямой выход четвертого элемента И соединен с

выходом блокировки узла.

3.Коммутатор поп. 1, о т л и - ч а ю щи и с я тем, что, с целью расширения области применения путем

обеспечения нарапщваемости структуры, в него введены первая и вторая груп- пы из К и третья и четвертая группы из Р элементов ШШ, причей выход сброса а,Ь-го узла запоминания запросов соединен с а-м входом Ь-го элет мента ИЛИ первой группы и Ь- входе а-го элемента ИЛИ третьей группы, выход блокировки а,Ь-го узла запоминания запросов соединен с а-м входом

91499364 О

b.-ro элемента ИЛИ второй группы изапоминания запросов соответственно Ь-м входом а-го элемента ИЛИ четвер-выходы элементов ИЛИ второй и четвертой группы, выходы элементов ИЛИ пер- .той групп образуют первый и второй вой и второй групп образуют первый ,вьпсоды блокировки матрицы узлов за- и третий выходы сброса матрицы узловпоминания запросов соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Модуль многокаскадной коммутационной системы | 1990 |

|

SU1793443A1 |

| Матричный распределитель | 1987 |

|

SU1580377A1 |

| Матричный коммутатор | 1985 |

|

SU1309294A1 |

| Соединитель многокаскадной коммутационной системы | 1984 |

|

SU1226643A1 |

| Модуль многокаскадной коммутационной системы | 1975 |

|

SU769741A1 |

| Устройство для обмена информацией | 1980 |

|

SU955014A1 |

| Устройство для формирования и анализа семантических сетей | 1989 |

|

SU1619289A1 |

| Коммутирующее устройство | 1973 |

|

SU478439A1 |

| Устройство коммутации | 1989 |

|

SU1709311A1 |

| Устройство поиска степени оптимальности размещения в кластерных многопроцессорных системах | 2022 |

|

RU2791419C1 |

Изобретение относится к вычислительной технике ,в частности, к автоматическим и цифровым коммутационным системам, обеспечивающим параллельное и приоритетное распределение информации между элементами многопроцессорных ЭВМ. Целью изобретения является сокращение времени настройки в режиме свободного поиска каналов. Цель достигается тем, что практически остается постоянно минимальной скорость настройки на групповые каналы, когда одновременно устанавливаются связи как между, например, десятью, так и между шестнадцатью внешними абонентами, устройство дополнительно содержит матрицу из узлов запоминания запросов, каждый из которых содержит входы и выходы сброса и блокировки, причем выходы сброса и блокировки подключены к своим входам сброса и блокировки всех последующих узлов запоминания волн, а выходы сброса и блокировки узлов запоминания волн соединены через соответствующие элементы ИЛИ с выходами сброса и блокировки по горизонтали и вертикали устройства. 2 з.п.ф-лы, 3 ил.

16 а

IS

18

Фаг,1

Фи9.2

А/г. 5

Составитель Ю. Грецкий Редактор В.Петраш , Техред И.Ходаиич

Заказ 4695/48

Тираж 668

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

П 6

Корректор Н. Король

Подписное

| Авторское свидетельство СССР, № 760074, кц, G 06 F 15/16, 1980, Авторское свидетельство СССР 1363454, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-08-07—Публикация

1987-04-07—Подача