Изобретение относится к радиотехнике и может быть использовано к ичфропых устройствах обработки час- г отно модулирова)1ных аналог овых сиг iKsnon,

Цель изобретения -- повышение точности детектирования.

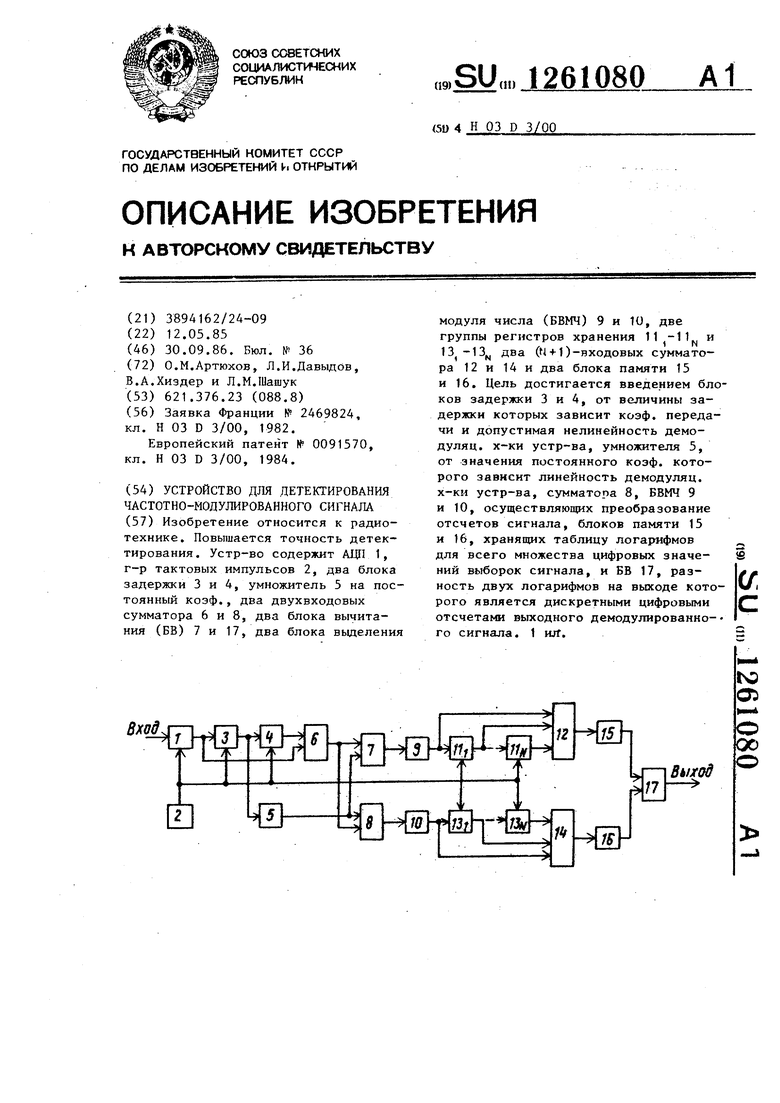

1а чертеже представлена электрическая структурная схема устройства juiH детектирования частотно-модулированного сигнала.

Устройство содержит аналого-цифровой преобразователь (ЛЦП) 1, генератор 2 тактовых импульсов, первы 3 и второй 4 блоки задержки, умножитель 5 на постоянный коэффициент, тгериый двухвходовый сумматор 6, первый блок 7 вычитания, второй двувходовый сумматор 8, первый 9 и вто рой 10 блоки вьщелення модуля числа

первую I pyiiny регистров ll,-11,j хранения первый ( +1)-входовый сумматор 12, вторую группу регистров 13,-1.3, хранения, второй () входовый сумматор 14, первый 13 и BTopofi 16 блоки памяти и второй бло 17 вычитания,

Устройство для детектирования чатотно-модулированных сигналов работет следующим образом.

При подаче на вход устройства частотно-модулированного сигнала Л11П 1 преобразует входной непрерыв- Hbii i сигнал в последовательность его дискретных цифровых отсчетов. Период этой последовательности отсчетов задает генератор 2 тактовых импульсов. Частота тактовых импульсов равна 4f, где f - центральная частота или любая другая частота, лежаща в полосе; девиации частотно-модулированного сигнала.

Цифровые отсчеты с выхода А1Щ 1 поступают на вход первого блока 3 здержки, а затем на вход вторэго блока А задержки. Блоки 3 и 4 задерж-- ки имеют одинаковое время задержки, кратное периоду частоты генератора тактовых импульсов. Величина задержки выбирается из условия получения необходимого коэффициента передачи и допустимой нелинейности демодуля- ционной характеристики устройства. Блоки 3 и 4 задержки могут быть выполнены на сдвиговых регистрах. Незадержанный отсчет сигнала складывается в первом двухвходовом сумматоре 6 с задержанным. Цифровые отсче

5

0

5

0

5

0

ТЫ сигнала, задержанные с помспцт.К первого блока 3 задержки, умножаются на постоянный коэ(х{|ициент К умножителем 5. От значения постоянного )ициента К зависит линейность демодуляционной характеристики уст. ройства. При линейность небольшая. В качестве умножителя 5 может быть использовано постсжнное запоми- наы цее устройство, в которое :ены все возможные результаты умножения отсчетов сигнала на значе/иге К. При К-2 и нелинейность демодуляционной характеристики возрастает, однако умножитель 5 в этом случае можно свести к соответствующим образом организованным перемычкам. При в качестве умножителя 5 можно использовать сумматор. После выполнения, операций вычитания и первом блоке 7 вычитания и сложения во втором двухвходовом сумматоре 8 осуществляется выделение модулей чисел в блоках выделения модулей чисел.

Конструктивное выполнение бло- ;ков 9 и 10 выделения модулей числа

может быть сведено к соответствующим образом организованным перемычкам, так как достаточно при да.г1Т1Нгй- ших преобразованиях просто учитывать знаковый разряд. Если отрицательные числа представлены в дополнительном коде, то в качестве блоков вьщеления модулей чисзта может быть использован преобразователь дополнительного кода в прямой, ()- входовый сумматор 12 и первая группа из одинаковых регистров 11, -11 хранения позволяет получить сумму нескольких результатов преобразования отсчетов сигнала, получаемых с выхода блока 9 выделения модуля числа, что эквивалентно их усреднению. Ана5 логично (N+1)-входовой сумматор 14 и группа из одинаковых регистров 13 - 13 хранения позволяют получить сумму нескольких результатов преобразования отсчетов сигнала, получаемых с

0 выхода блока 10 выделения модуля числа, что эквивалентно их усреднению. Такое усреднение позволяет улучшить отноигение сигнал/шум на выходе устройства. Так как в результате усреднения происходит низкочастотная фильтрация сигнала, максимальное количество регистров хранения определяется верхней граничной

55

.12610804

частотой модулированного си1 нала.t |Лсоз 2П () (t,--TVh ч ,s . V; .

При дискретизации синусоидального (f, +Af) (t +Т)+ Ч j К 2г.. л I

сигнала возможны отсчеты с нулевым« ()тJ |. значением, логарифмирование которых

невозможно, поэтому минимальное эна- 5 Образуем функции z иг и- .y;u ;i

чение для , в этом случае сумми-выражений руются два соседних отсчета, отстоящих друг от друга на угол ТГ/2.KY,. (Y + 2, (2) Если ОДТ1Н из них равен нулю, то второй имеет максимальное значение. KY -(Y + Y . ). (3)

It Oi 2i

Таким образом, результат суммирования на выходах ( N + 1)-входовых сум- где - константа; маторов 12 и 14 уже всегдаi t,n - порядковый номер триады,

будет отличен от нуля. Значения вы- Получим: борок сигнала с выходов (N-«-1)-Bxo-

довых сумматоров 12 и t4 поступают i « oi У на входы соответствующих блоков

и 16 памяти, в которых хранится таб- ei оп ,, лица логарифмов для всего множества

цифровых значений выборок сигнала. -(Y +Y,, )| +|KY - Разность двух логарифмов, получаемая .

на выходе второго блока 17 вычитания, Х, j ,, оь h 1

есть дискретные цифровые отсчеты

демодулированного сигнала.При этом формирование триад выРабота устройства, может быть опи- борок для выражений (2) и (3) просана аналитически.изводится так, что сдвиг между одПусть частотно-модулированньп сиг-ноименными выборками в соседних тринал представлен в видеадах составляет период дискретизации,

это соответствует фазовому сдвигу,

А cos 2IT(f + f)t « Т

° близкому к - , меящу парами выборок:

где А - амплитуда;Y Y Y Y Y Y

Ч „ - начальный фазовый угол; «t of..i) ,, i(iri -ц (

f. - центральная частота;„ .,ч

Воспользуемся равенством (1) и преAf - отклонение от центральной35 образуем (4) и (5) к ваду частоты.

Три любые выборки сигнала, нзя- |K+2cos 21Г( +д) ((Y M|Y I + тые равномерно через интервал Т меж- ° . и ч I

ду ними, кратный периоду дискрети-

зации, записываются следующим обра- 40 ЗОМ1,z,--|K-2cos(2ir(,+(,f)Tj| (IYJ t

V...(f.,.n(t,-m-fJ, IV,,| ...HVJ ).(7)

Г Введем условие

Y, A () ,,«

Y,, A ()()+4; .Т .----,(8)

0

Докажем справедливость следующего j, ш О 1 2,. равенства50 .

J - Функции .2 и Zj при , i . 2 KY t(, )Y {К12соз 2ГТ(+af)Т}|,(1) не имеют нулевых значений, и можно

выполнить следующее преобразование:

Действительно, используя основныеК тг f

формулы тригонометрии, получим --(2m+O (-1)

(9)

KY (,)KA cosl2TT(.uf) |(2m-H) (-if

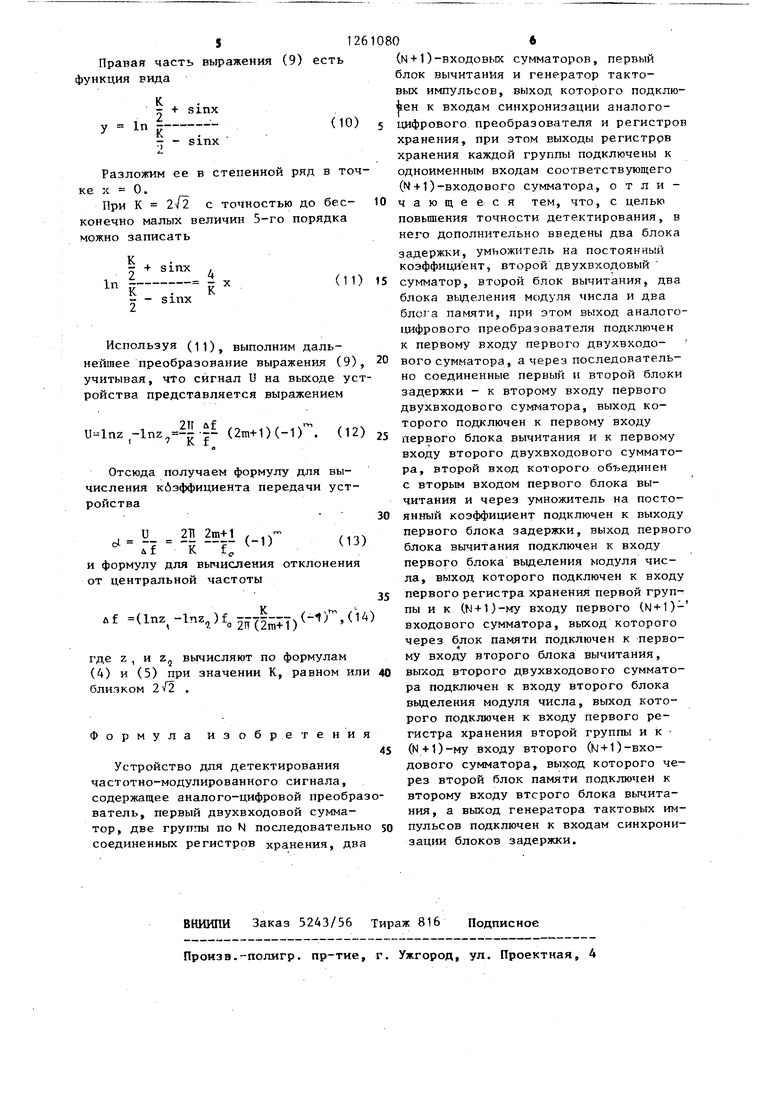

Правая часть выражения функция вида

In

ь

к

- - sinx

12610806

(9) есть (N + 1)-BxofloBbix сумматоров, первый блок вычитания и генератор тактовых импульсов, выход которого подклю- sinx ен к входам синхронизации аналого: (10) 5 цифрового преобразователя и регистров

хранения, при этом выходы регистррв хранения каждой группы подключены к одноименным входам соответствующего ()-входового сумматора, о т л и - 10 чающееся тем, что, с целью повьшения точности детектирования, в него дополнительно введены два блока задержки, умножитель на постоянный sinx ,коэффициент, второй двухвходовый

In ; ;; X(11) 15 сумматор, второй блок вычитания, два

блока выделения модуля числа и два блст а памяти, при этом выход аналого- цифрового преобразователя подключен к первому входу первого двухвходо- нейшее преобразование выражения (9), 20 вого сумматора, а через последовательРазложим ее в степенной ряд в точке х О .

При К 2/2 с точностью до бесконечно малых величин 5-го порядка можно записать

К .

2

К

- - sinx

Используя (11), выполним дальучитывая, что сигнал U на выходе устройства представляется выражением

U-lnz -1пг,-П- (2т+1)(-1). (12)

Отсюда получаем формулу для вычисления кбзффициента передачи устройства

у 211 2т+1 , .- Л к ,

(13)

и формулу для вычисления отклонения от центральной частоты

Af (lnz -1пг„)

К

ч ° (2п1+1)

(-1),(14)

и 2„

где Z

(4) и (5) при

близком 2/2 .

вычисляют по формулам значении К, равном или

Формула изобретения

Устройство для детектирования частотно-модулированного сигнала, содержащее аналого-цифровой преобразователь, первый двухвходовой сумма45

тор, две группы по N последовательно соединенных регистров хранения, два

В1ШИПИ Заказ 5243/56 Тираж 816 Подписное Произа.-полягр, пр-тие, г. Ужгород, ул. Проектная, 4

но соединенные первый и второй блоки задержки - к второму входу первого двухвходового сумматора, выход которого подключен к первому входу

первого блока вычитания и к первому входу второго двухвходового сумматора, второй вход которого объединен с вторым входом первого блока вычитания и через умножитель на постоянный коэффициент подключен к выходу первого блока задержки, выход первого блока вычитания подключен к входу первого блока вьщеления модуля числа, выход которого подключен к входу

первого регистра хранения первой группы и к (N + 1)-My входу первого (N + 1)- входового сумматора, выход которого через блок памяти подключен к первому входу второго блока вычитания,

выход второго двухвходового сумматора подключен к входу второго блока выделения модуля числа, выход которого подключен к входу первого регистра хранения второй группы и к

(N+D-My входу второго (М + 1)-входового сумматора, выход которого через второй блок памяти подключен к второму входу второго блока вычитания , а выход генератора тактовых импульсов подключен к входам синхронизации блоков задержки.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ДЕМОДУЛЯЦИИ ДИСКРЕТНЫХ СИГНАЛОВ В МНОГОЛУЧЕВОМ КАНАЛЕ СВЯЗИ И ДЛЯ ОЦЕНКИ ПАРАМЕТРОВ КАНАЛА | 2004 |

|

RU2271070C2 |

| Цифровой генератор периодической функции | 1987 |

|

SU1432491A1 |

| Цифровой согласованный фильтр | 1988 |

|

SU1566468A1 |

| Специализированный процессор для цифровой фильтрации | 1989 |

|

SU1631558A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1987 |

|

SU1481893A1 |

| Устройство для воспроизведения дополнительных цветных телевизионных изображений | 1989 |

|

SU1817257A1 |

| Коррелятор | 1988 |

|

SU1705835A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1259259A1 |

| Цифровой фильтр с линейной дельта-модуляцией | 1986 |

|

SU1424119A1 |

| Цифровой фильтр | 1982 |

|

SU1125746A1 |

Изобретение относится к радиотехнике. Повышается точность детектирования. Устр-во содержит АЩ 1, г-р тактовых импульсов 2, два блока задержки 3 и 4, умножитель 5 на постоянный коэф., два двухвходовых сумматора 6 и 8, два блока вычитания (БВ) 7 и 17, два блока выделения модуля числа (БВМЧ) 9 и 10, две группы регистров хранения 11 -П., и 13 -13 два (И -1-1) -входовых сумматора 12 и 14 и два блока памяти 15 и 16. Цель достигается введением блоков задержки 3 и 4, от величины задержки которых зависит коэф. передачи и допустимая нелинейность демо- дуляц. х-ки устр-ва, умножителя 5, от значения постоянного коэф. которого зависит линейность демодуляц. х-ки устр-ва, сумматора 8, БВМЧ 9 и 10, осуществляющих преобразование отсчетов сигнала, блоков памяти 15 и 16, хранящих таблицу логарифмов для всего множества цифровых значений выборок сигнала, и БВ 17, разность двух логарифмов на выходе которого является дискретными цифровыми отсчетами выходного демодулированно- го сигнала. 1 иЛ. а С Вход Be/jrod

| СПОСОБ ЗУБОФРЕЗЕРОВАНИЯ | 2011 |

|

RU2469824C2 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ травления железа | 1950 |

|

SU91570A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-09-30—Публикация

1985-05-12—Подача